Documente Academic

Documente Profesional

Documente Cultură

Arquitectura SMP MPP

Încărcat de

Alfredo MontoyaDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Arquitectura SMP MPP

Încărcat de

Alfredo MontoyaDrepturi de autor:

Formate disponibile

2.3.

2 Arquitectura MPP

Ya que el problema es el hecho de contar con memoria compartida y sus limitaciones, se propuso un esquema de una mquina paralela que consta de varias unidades de procesamiento bsicamente independientes. En efecto cada una de estas unidades, conocida como ``nodo'', es prcticamente una computadora en s misma, contando con su propio procesador, memoria no compartida, y que se comunica con las dems unidades de procesamiento a travs de un canal provisto exclusivamente para este propsito. Este tipo de mquinas se conocen como computadoras masivamente paralelas o mquinas MPP (Massively Parallel Processing, procesamiento masivamente paralelo). Un diagrama de una arquitectura MPP genrica se muestra en la figura (1.2).

Figura 1.2:Arquitectura MPP

Una mquina MPP presenta una serie de consideraciones importantes derivadas de su arquitectura, que se deben tomar en cuenta al escribir programas que pretendan aprovechar su naturaleza multiprocesador. Obviamente la caracterstica ms importante es el hecho de que, en cada nodo, cada procesador opera bsicamente como una computadora independiente, ejecutando su propio cdigo independiente de los dems procesadores, y teniendo un rea de memoria con datos tambin independientes. Desde luego, para que esta organizacin redunde en un mayor desempeo, se requiere colaboracin entre los nodos. Como se mencion, una mquina MPP debe contar con un canal que permita a los nodos comunicarse entre s, a fin de intercambiar datos y coordinar sus operaciones. Ya que el objetivo principal de una mquina MPP es obtener alto rendimiento, se busca que este canal de comunicaciones sea lo ms eficiente posible, en trminos tanto de ancho de banda como de tiempo de latencia. En la mayora de los casos este canal ser un bus propietario, diseado por el fabricante del equipo MPP. Para tener acceso a informacin fuera de su propia rea de memoria, los nodos se comunican entre s, regularmente empleando un esquema de paso de mensajes. Esto resuelve el problema de saturacin del bus de comunicaciones, pues ste slo se emplea cuando se est realizando comunicacin entre los nodos. De esta manera se tiene una arquitectura que puede escalarse a varios cientos o miles de procesadores (las mquinas MPP ms grandes en la actualidad tienen alrededor de 10 mil procesadores). Sin embargo el tener varias secciones de memoria independientes complica la programacin en este tipo de arquitecturas. En una arquitectura MPP la

distribucin de trabajo entre los nodos es una consideracin vital al disear cualquier aplicacin. Se debe tomar en cuenta la sincronizacin de datos entre los nodos, y en toda comunicacin entre ellos debe realizarse explcitamente por medio de llamadas al mecanismo de paso de mensajes.

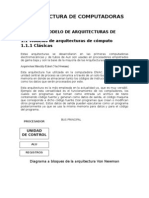

2.3.1 Arquitectura SMP

El enfoque ms sencillo para una mquina con mltiples procesadores es el esquema SMP (Symmetrical Multiprocessing, multiproceso simtrico). Una arquitectura SMP es bsicamente una expansin de una arquitectura tradicional pero con la adicin de varios procesadores que comparten todos los dems recursos del sistema (memoria principal, almacenamiento secundario, perifricos de entrada y salida). En esta arquitectura no se establece distincin entre los procesadores; todos son jerrquicamente iguales y pueden ejecutar tareas indistintamente. De esta caracterstica viene el nombre de ``simtrica''. Un diagrama de una arquitectura SMP genrica se muestra en la figura (1.1).

Figura 1.1:Arquitectura SMP

En general una arquitectura SMP tiene un equivalente en uniprocesador, y naturalmente un sistema SMP puede ejecutar simultneamente varios programas o aplicaciones, que normalmente podran ejecutarse en el sistema uniprocesador, de manera independiente. Sin embargo, para el uso de aplicaciones que aprovechen los mltiples procesadores para expeditar la realizacin de clculos, nos interesa que dichos procesos no sean totalmente independientes, buscando entonces que cuenten con manera de comunicarse para distribuirse informacin, compartir y consolidar resultados. Ya que un sistema SMP los procesadores comparten todos los perifricos y recursos, el esquema ms obvio para comunicarse en una arquitectura SMP es el uso de memoria compartida. Como el nombre lo indica, en este esquema los procesadores tienen acceso a un espacio de direcciones comn; esto puede ser todo el espacio de direcciones o nicamente un rea designada para memoria compartida, permitiendo a cada proceso contar con un rea exclusiva para sus requerimientos. La memoria compartida es un esquema conceptualmente simple de utilizar. Sin embargo presenta ciertas limitaciones. Una de ellas, ya que se puede tener a dos o ms procesadores manipulando la misma rea de memoria, es que se puede caer en inconsistencias donde un procesador espera un dato que ha sido modificado por otro. Esto tambin puede provocar condiciones de competencia (``race conditions'') y atoramientos (``deadlocks''), que son problemas clsicos de la sincronizacin de procesos, pero que no pueden dejar de tomarse en cuenta en una arquitectura SMP. Estas condiciones pueden resolverse utilizando mecanismos de sincronizacin de procesos, como semforos, monitores y secciones crticas.

La limitacin ms importante de la arquitectura SMP, en trminos del rendimiento mximo que puede alcanzarse, es la posibilidad de saturacin de los buses del sistema. Ya que todos los procesadores tienen acceso al mismo bus de memoria, y en general a todos los perifricos que se encuentran comunicados comnmente por buses, conforme se incrementa el nmero de procesadores se incrementa tambin el trfico en dichos buses. Esto causa una saturacin que finalmente termina por negar el incremento de rendimiento obtenido teniendo varios procesadores. Por esta razn una arquitectura SMP difcilmente puede escalar ms all de algunas decenas de procesadores.

S-ar putea să vă placă și

- Programación de microcontroladores paso a paso: Ejemplos prácticos desarrollados en la nubeDe la EverandProgramación de microcontroladores paso a paso: Ejemplos prácticos desarrollados en la nubeÎncă nu există evaluări

- Arquitectura SMP y MPPDocument4 paginiArquitectura SMP y MPPManuel71110Încă nu există evaluări

- UF0852 - Instalación y actualización de sistemas operativosDe la EverandUF0852 - Instalación y actualización de sistemas operativosEvaluare: 5 din 5 stele5/5 (1)

- Arquitecturas MPP & SMPDocument7 paginiArquitecturas MPP & SMPMagaly CedroÎncă nu există evaluări

- UF0853 - Explotación de las funcionalidades del sistema microinformáticoDe la EverandUF0853 - Explotación de las funcionalidades del sistema microinformáticoÎncă nu există evaluări

- Arquitectura SMP, MPP, SPPDocument4 paginiArquitectura SMP, MPP, SPPZuzan PeñaÎncă nu există evaluări

- Procesamiento ParaleloDocument9 paginiProcesamiento ParaleloCarlos EQÎncă nu există evaluări

- La Arquitectura SMPDocument4 paginiLa Arquitectura SMPliracruzgustavoÎncă nu există evaluări

- Arquitectura MPPDocument2 paginiArquitectura MPPBereb RosqueroÎncă nu există evaluări

- Arquitectura SMPDocument2 paginiArquitectura SMPAldo Buchon GarciaÎncă nu există evaluări

- Multiprocesamiento ParaleloDocument9 paginiMultiprocesamiento ParaleloElmerCuencaBalabarca0% (1)

- Grupo 7 Arquitectura Del SMPDocument4 paginiGrupo 7 Arquitectura Del SMPtoxic_gabriel1207Încă nu există evaluări

- Multiprocesadores SimétricosDocument9 paginiMultiprocesadores SimétricosRobin PereiraÎncă nu există evaluări

- MPP y SMPDocument5 paginiMPP y SMPEfra26100% (1)

- La Arquitectura SMPDocument5 paginiLa Arquitectura SMPKevin Hernandez RamosÎncă nu există evaluări

- Multi Pro Ces AdoresDocument5 paginiMulti Pro Ces AdoreslalometallicaÎncă nu există evaluări

- Arquitectura MIMDDocument8 paginiArquitectura MIMDHernan CastroÎncă nu există evaluări

- Multiprocesamiento Paralelo 3 - 3parte 1PDocument6 paginiMultiprocesamiento Paralelo 3 - 3parte 1PTomiko FelizÎncă nu există evaluări

- Arquitectura MIMDDocument6 paginiArquitectura MIMDpdelacruzrÎncă nu există evaluări

- Memoria CompartidaDocument5 paginiMemoria CompartidaRolando HuayllaniÎncă nu există evaluări

- Procesamiento ParaleloDocument35 paginiProcesamiento ParaleloJEFFERSON MUÑOZ PARDOÎncă nu există evaluări

- Definicion de NUMA y OtrosDocument41 paginiDefinicion de NUMA y OtrosRamón Moreno MalavéÎncă nu există evaluări

- SMP (Symmetric Multi-Processing Ó Multiproceso Simétrico)Document2 paginiSMP (Symmetric Multi-Processing Ó Multiproceso Simétrico)Markos MartinÎncă nu există evaluări

- UNIPROCESADORES y MultiprocesadoresDocument21 paginiUNIPROCESADORES y MultiprocesadoresLuis Soriano OsoresÎncă nu există evaluări

- 4.5 Casos de EstudioDocument5 pagini4.5 Casos de EstudioSilvio Dresser0% (1)

- Procesamiento ParaleloDocument6 paginiProcesamiento ParaleloResendiz AguilaÎncă nu există evaluări

- MimdDocument11 paginiMimddysanÎncă nu există evaluări

- Tendencias de Los Sistemas Operativos DistribuidosDocument7 paginiTendencias de Los Sistemas Operativos Distribuidosbaghead8Încă nu există evaluări

- Multiprocesamiento Simétrico y Micro Núcleos-FinalDocument13 paginiMultiprocesamiento Simétrico y Micro Núcleos-FinalOscar CobbÎncă nu există evaluări

- 1.1 Modelo de Arquitecturas de CómputoDocument18 pagini1.1 Modelo de Arquitecturas de CómputoJuan HernandezÎncă nu există evaluări

- Arquitectura de ComputadorasDocument8 paginiArquitectura de ComputadorasSorel TorresÎncă nu există evaluări

- Actividad 1.1.1Document14 paginiActividad 1.1.1luisÎncă nu există evaluări

- Procesos Concurrentes - Sistemas OperativosDocument10 paginiProcesos Concurrentes - Sistemas OperativosMICHAELÎncă nu există evaluări

- MultiprocesadoresDocument7 paginiMultiprocesadoresmorris starÎncă nu există evaluări

- Programacion en ParaleloDocument6 paginiProgramacion en ParaleloJoshep DÎncă nu există evaluări

- MPPDocument1 paginăMPPchicharo09Încă nu există evaluări

- Memoria Compartida DistribuidaDocument11 paginiMemoria Compartida DistribuidaRoger VaaÎncă nu există evaluări

- 3-Arquitectura de Microcontroladores 2023Document38 pagini3-Arquitectura de Microcontroladores 2023Ulises martin PellizaÎncă nu există evaluări

- 1 Tipos de ArquitecturasDocument9 pagini1 Tipos de ArquitecturasKenia CruzÎncă nu există evaluări

- Sistemas Distribuidos HardwareDocument24 paginiSistemas Distribuidos HardwareFreddy Bernardo MÎncă nu există evaluări

- MultiprocesamientoDocument10 paginiMultiprocesamientoWiler Falcon CarbajalÎncă nu există evaluări

- Arquitecturas Paralelas Existentes en El MercadoDocument4 paginiArquitecturas Paralelas Existentes en El MercadoEmma Collin100% (1)

- MultiprocesadoresDocument17 paginiMultiprocesadoresmorris starÎncă nu există evaluări

- 53 Unidad6 Coherencia de CacheDocument12 pagini53 Unidad6 Coherencia de CacheDoracelia Gazga LoveÎncă nu există evaluări

- Arquitectura ParalelaDocument37 paginiArquitectura ParalelaHitsuji KuroiÎncă nu există evaluări

- Taller Nº2 OrganizacionDocument12 paginiTaller Nº2 OrganizacionMartinezMelloÎncă nu există evaluări

- Trabajo Practico Nº3 de Sistemas Operativos IIDocument42 paginiTrabajo Practico Nº3 de Sistemas Operativos IICamila ToledoÎncă nu există evaluări

- Sistemas Multiprocesador yDocument10 paginiSistemas Multiprocesador yIsmael ChoixÎncă nu există evaluări

- Computo ParaleloDocument12 paginiComputo ParaleloErickSobrevillaResendizÎncă nu există evaluări

- Configuraciones de MCDDocument12 paginiConfiguraciones de MCDSergio RiveraÎncă nu există evaluări

- 00881-Tema 3.3 Multiples ProcesadoresDocument45 pagini00881-Tema 3.3 Multiples ProcesadoresAbraham SanchezÎncă nu există evaluări

- SO MultiprocesadorDocument34 paginiSO MultiprocesadorGabino Arel FernandezÎncă nu există evaluări

- Arquitectura de ComputadorasDocument53 paginiArquitectura de Computadorastilsma100% (3)

- Procesamiento ParaleloDocument23 paginiProcesamiento ParaleloAlejandro Pérez García0% (1)

- 1 Sistemas Operativos Distribuidos DiegoDocument9 pagini1 Sistemas Operativos Distribuidos DiegoDiego NogueraÎncă nu există evaluări

- Evidencia de AprendizajeDocument5 paginiEvidencia de AprendizajeFelipe GonzalezÎncă nu există evaluări

- Resumen Investigación 1.1 - Modelos de Arquitecturas de CómputoDocument8 paginiResumen Investigación 1.1 - Modelos de Arquitecturas de CómputoluisÎncă nu există evaluări

- Arquitectura de Computadoras - Memoria Compartida y DistribuidaDocument15 paginiArquitectura de Computadoras - Memoria Compartida y DistribuidaJuan Carlos Gonzalez GutierrezÎncă nu există evaluări

- Características de Los MultiprocesadoresDocument3 paginiCaracterísticas de Los MultiprocesadoresAle ReyVá100% (1)

- 2 Arquitectura Interna MicrocontroladorDocument4 pagini2 Arquitectura Interna MicrocontroladorMauricio SanchezÎncă nu există evaluări

- Cuadro SinopticoDocument2 paginiCuadro SinopticoAlfredo MontoyaÎncă nu există evaluări

- Crear Claves de Inicio de Sesión de SQL ServerDocument11 paginiCrear Claves de Inicio de Sesión de SQL ServerAlfredo MontoyaÎncă nu există evaluări

- Arquitectura Cliente ServidorDocument2 paginiArquitectura Cliente ServidorAlfredo MontoyaÎncă nu există evaluări

- Requisitos de Hardware y Software para La Instalación de SQL Server 2008Document3 paginiRequisitos de Hardware y Software para La Instalación de SQL Server 2008Alfredo MontoyaÎncă nu există evaluări

- Modelo Vista ControladorDocument3 paginiModelo Vista ControladorAlfredo MontoyaÎncă nu există evaluări

- Tuneup UtilitiesDocument7 paginiTuneup UtilitiesAlfredo MontoyaÎncă nu există evaluări

- Banco de PreguntasDocument14 paginiBanco de PreguntasMichael LòpezÎncă nu există evaluări

- Introducción Al ASUS ROG Gaming Center - Soporte Técnico Oficial - ASUS EspañaDocument20 paginiIntroducción Al ASUS ROG Gaming Center - Soporte Técnico Oficial - ASUS EspañaMinervaMontoyaDÎncă nu există evaluări

- Historia de Los Dispositivos de AlmacenamientoDocument16 paginiHistoria de Los Dispositivos de AlmacenamientoLeón Manuel Sías CalderónÎncă nu există evaluări

- Sistemas Digitales - Semana 16Document14 paginiSistemas Digitales - Semana 16Bryan RamosÎncă nu există evaluări

- Formularios ComtelDocument6 paginiFormularios ComtelJoseLuisAmpueroÎncă nu există evaluări

- Actividad 3 - Redes y Medios de TransmisionDocument2 paginiActividad 3 - Redes y Medios de TransmisionLuis Fernando Torres RodriguezÎncă nu există evaluări

- 4a. Unidad Amplificadores Operacionales y 555Document44 pagini4a. Unidad Amplificadores Operacionales y 555TeOmachineÎncă nu există evaluări

- Cuestionario 3 EvDocument3 paginiCuestionario 3 EvSka's Sks'sÎncă nu există evaluări

- Clase 7Document58 paginiClase 7MaxÎncă nu există evaluări

- Colores en C++Document5 paginiColores en C++jack-y07Încă nu există evaluări

- Taller de Ejercicios de Diodos en Serie Y Paralelo: Ejemplos de AplicaciónDocument7 paginiTaller de Ejercicios de Diodos en Serie Y Paralelo: Ejemplos de AplicaciónJuan Sebastian Cortes AguileraÎncă nu există evaluări

- Esquema Del Arduino UnoDocument11 paginiEsquema Del Arduino Unodaniel felipe sandovalÎncă nu există evaluări

- Laboratorio - 8 - LTyA - Acoplamiento de Impedancias - 20211021 1Document3 paginiLaboratorio - 8 - LTyA - Acoplamiento de Impedancias - 20211021 1Alex AtencioÎncă nu există evaluări

- Capítulo 9 Análisis de Fallas en Amplificadores de AudioDocument14 paginiCapítulo 9 Análisis de Fallas en Amplificadores de AudioYoni Cativa100% (4)

- Unidad III Administracion de Memoria Ekipo5Document29 paginiUnidad III Administracion de Memoria Ekipo5Josh Alonso JimenezÎncă nu există evaluări

- Convertidores de Potencia de CCDocument5 paginiConvertidores de Potencia de CCChristianÎncă nu există evaluări

- Super PosicionDocument2 paginiSuper PosicionGuillermo SkanÎncă nu există evaluări

- Fundamentos de Redes HFCDocument58 paginiFundamentos de Redes HFCCPavGÎncă nu există evaluări

- PSo CDocument17 paginiPSo CErick Poumián PalomecÎncă nu există evaluări

- PME 32 ConvocatoriaDocument15 paginiPME 32 ConvocatoriaBoris Alexander Ascencio CoilaÎncă nu există evaluări

- Silabo 2007 01 Micro ProcesadoresDocument4 paginiSilabo 2007 01 Micro ProcesadoresEdgar CALPAÎncă nu există evaluări

- Instituto Gubernamental Mixto HibuerasDocument15 paginiInstituto Gubernamental Mixto HibuerasDarwinJosephCastilloÎncă nu există evaluări

- Contador Asíncrono Descendente Con Biestables Tipo TDocument3 paginiContador Asíncrono Descendente Con Biestables Tipo TEvelyn MoranÎncă nu există evaluări

- Catálogo KZ ColombiaDocument34 paginiCatálogo KZ ColombiaSamuel Rios SuárezÎncă nu există evaluări

- Arquitectura y Mantenimiento Basico de Equipos Informaticos de OficinaDocument99 paginiArquitectura y Mantenimiento Basico de Equipos Informaticos de OficinaRupert LopezÎncă nu există evaluări

- AA - 2 COMPONENTES INTERNOS PC Maria TorresDocument5 paginiAA - 2 COMPONENTES INTERNOS PC Maria TorresDarwin Felipe OspinaÎncă nu există evaluări

- Guía de Electrónica BásicaDocument5 paginiGuía de Electrónica BásicaAlets ContrerasÎncă nu există evaluări

- Circuito Practico Con UJT PDFDocument1 paginăCircuito Practico Con UJT PDFSamuel JACOBBOÎncă nu există evaluări

- Guia de Alineacion de Modems AxesstelDocument20 paginiGuia de Alineacion de Modems Axesstelomarfernandez35100% (2)