Documente Academic

Documente Profesional

Documente Cultură

CMOS N-Well Process

Încărcat de

Subir MaityDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

CMOS N-Well Process

Încărcat de

Subir MaityDrepturi de autor:

Formate disponibile

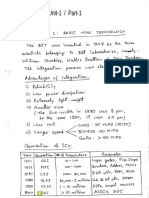

Fabrication of CMOS

CMOS N-well process

CMOS n-well process

The n-well CMOS process starts with a moderately doped (impurity concentration less than 1015 cm-3) p-type silicon substrate. Then, an oxide layer is grown on the entire surface. The first lithographic mask defines the n-well region. Donor atoms, usually phosphorus, are implanted through this window in the oxide. This defines, the active areas of the nMOS and pMOS transistors. Thin gate oxide is grown on top of the active regions. The thickness and the quality of the gate oxide are critical fabrication parameters, since they affect the characteristics of the MOS transistor, and its reliability.

CMOS n-well process

The polysilicon layer is deposited using chemical vapour deposition (CVD) and patterned by dry (plasma) etching. The created polysilicon lines will function as the gate electrodes of the nMOS and the pMOS transistors and their interconnects. Also, the polysilicon gates act as self-aligned masks for the source and drain implantations that follow this step.

CMOS n-well process

Using a set of two masks, the n+ and p+ regions are implanted into the substrate and into the n- well, respectively. The ohmic contacts to the substrate and to the n-well are implanted in this process step.

CMOS n-well process

An insulating silicon dioxide layer is deposited over the entire wafer using CVD. Then, the contacts are defined and etched away to expose the silicon or polysilicon contact windows.

CMOS n-well process

Metal is deposited over the entire chip surface using metal evaporation, and the metal lines are patterned through etching. Since the wafer surface is nonplanar, the quality and the integrity of the metal lines created in this step are very critical and are essential for circuit reliability.

CMOS n-well process

The final step is to deposit the passivation layer over the chip, except for wire-bonding pad areas.

S-ar putea să vă placă și

- Lab Report VLSIDocument24 paginiLab Report VLSIK Eerti Vyas0% (2)

- VLSI Micro-Project Report Group A PDFDocument14 paginiVLSI Micro-Project Report Group A PDFganesh SawantÎncă nu există evaluări

- Cmos Process FlowDocument29 paginiCmos Process FlowPushparaj Karu100% (1)

- CMOS FabricationDocument7 paginiCMOS FabricationSubir MaityÎncă nu există evaluări

- Complementary MetalDocument5 paginiComplementary MetalesaidanÎncă nu există evaluări

- Vlsi NotesDocument11 paginiVlsi NotesShowcase MarathiÎncă nu există evaluări

- Fabrication of MosfetDocument19 paginiFabrication of Mosfetnarayana89% (9)

- Unit 2Document33 paginiUnit 2Venky VellankiÎncă nu există evaluări

- Unit 2 Fabrication ProcessDocument8 paginiUnit 2 Fabrication Processbhupendra1977Încă nu există evaluări

- CMOS Fabrication Technologies and Process Design RulesDocument14 paginiCMOS Fabrication Technologies and Process Design RulesPrashant SinghÎncă nu există evaluări

- Understanding About CMOS Fabrication TechnologyDocument8 paginiUnderstanding About CMOS Fabrication TechnologyAjay Kumar MattupalliÎncă nu există evaluări

- CMOS Fabrication Process StepsDocument17 paginiCMOS Fabrication Process StepsNoman Ali35Încă nu există evaluări

- VLSI Unit 2 Technology - SDocument52 paginiVLSI Unit 2 Technology - SIndrajeet GautamÎncă nu există evaluări

- Chapter 1: Cmos Circuits - A Brief IntroductionDocument3 paginiChapter 1: Cmos Circuits - A Brief IntroductionbhannuÎncă nu există evaluări

- Making TransistorsDocument23 paginiMaking TransistorsRANGAM NAGARAJUÎncă nu există evaluări

- Vlsi Design UNIT-1: Lecture-3Document11 paginiVlsi Design UNIT-1: Lecture-3Erica WhiteheadÎncă nu există evaluări

- 2CMOSFabricationMNIT (DEc2006)Document46 pagini2CMOSFabricationMNIT (DEc2006)Arjun YadavÎncă nu există evaluări

- Nmos FabricationDocument45 paginiNmos FabricationDr-GopalÎncă nu există evaluări

- CMOS Fabrication ProcessDocument10 paginiCMOS Fabrication ProcessJohnMatthewBancilÎncă nu există evaluări

- Mod 2a Fabrication & Design RulesDocument73 paginiMod 2a Fabrication & Design RulesVijayalaxmi N CÎncă nu există evaluări

- Vlsi PDFDocument81 paginiVlsi PDFShruthiÎncă nu există evaluări

- FEOL Wafer Processing GuideDocument17 paginiFEOL Wafer Processing GuidekarthikÎncă nu există evaluări

- CMOS Process: Material Mainly Taken From UMBC, Kang and CampbellDocument38 paginiCMOS Process: Material Mainly Taken From UMBC, Kang and CampbellSmitha KollerahithluÎncă nu există evaluări

- MOS and VLSI Technology OverviewDocument54 paginiMOS and VLSI Technology OverviewAndrews austinÎncă nu există evaluări

- Lecture1 3 CMOS nWELL and TwinTub ProcessDocument33 paginiLecture1 3 CMOS nWELL and TwinTub ProcessSrikanth Soma100% (8)

- IC Fabrication - 2Document6 paginiIC Fabrication - 2yuga.m.padhyeÎncă nu există evaluări

- MOS and CMOS Process OverviewDocument36 paginiMOS and CMOS Process OverviewashishÎncă nu există evaluări

- VLSI Circuits Lecture on CMOS Fabrication ProcessesDocument36 paginiVLSI Circuits Lecture on CMOS Fabrication ProcessesBernard Mkumbwa Jr.Încă nu există evaluări

- Vlsi Unit-IDocument45 paginiVlsi Unit-Isuneelanubolu7Încă nu există evaluări

- Lecture CMOS NWELL and TwinTub ProcessDocument33 paginiLecture CMOS NWELL and TwinTub Processilias ahmedÎncă nu există evaluări

- Cmos Metal GateDocument56 paginiCmos Metal GateSubin AlexÎncă nu există evaluări

- CMOS Process FlowDocument39 paginiCMOS Process FlowYashaswa JainÎncă nu există evaluări

- BASIC VLSI DESIGN .PptsDocument32 paginiBASIC VLSI DESIGN .PptsNarayana Rao RevallaÎncă nu există evaluări

- NMOS Fabrication: Step 1: Processing The SubstrateDocument5 paginiNMOS Fabrication: Step 1: Processing The Substratechinthala santhosh srkÎncă nu există evaluări

- Fabrication Mod 2Document16 paginiFabrication Mod 2albin shajanÎncă nu există evaluări

- CMOS Process FlowDocument35 paginiCMOS Process Flowag21937570Încă nu există evaluări

- Understanding About CMOS Fabrication TechnologyDocument4 paginiUnderstanding About CMOS Fabrication TechnologyJayesh RaghuwanshiÎncă nu există evaluări

- Bec010 Vlsi - NotesDocument109 paginiBec010 Vlsi - NotesFarukh ZafarÎncă nu există evaluări

- Unit 5 - VLSI Design - WWW - Rgpvnotes.inDocument12 paginiUnit 5 - VLSI Design - WWW - Rgpvnotes.intanishachaturvedi2025Încă nu există evaluări

- NMOS FabricationDocument18 paginiNMOS FabricationDhaval Doshi100% (1)

- Lecture 030 - Deep Submicron (DSM) Cmos TechnologyDocument14 paginiLecture 030 - Deep Submicron (DSM) Cmos TechnologywatelzbuddyÎncă nu există evaluări

- Complementary Metal-Oxide-Semiconductor (CMOS) (PronouncedDocument3 paginiComplementary Metal-Oxide-Semiconductor (CMOS) (PronouncedMeiling MizukiÎncă nu există evaluări

- Unit 1 Basic MOS Technology: Figure 1. Moore's LawDocument18 paginiUnit 1 Basic MOS Technology: Figure 1. Moore's LawSushruth SastryÎncă nu există evaluări

- 7.6.2. Poly-Silicon Gate TechnologyDocument14 pagini7.6.2. Poly-Silicon Gate TechnologyHarshad KulkarniÎncă nu există evaluări

- Analog Digital VLSI Design TechniquesDocument78 paginiAnalog Digital VLSI Design TechniqueshkajaiÎncă nu există evaluări

- VLSI Module-2 PPT For FabricationDocument13 paginiVLSI Module-2 PPT For FabricationPhanindra ReddyÎncă nu există evaluări

- FUNDAMENTALS of CMOS VLSI 5th SEM ECE PDFDocument190 paginiFUNDAMENTALS of CMOS VLSI 5th SEM ECE PDFVarunKaradesaiÎncă nu există evaluări

- CMOS Fabrication Process: 40 Steps to Build TransistorsDocument27 paginiCMOS Fabrication Process: 40 Steps to Build TransistorsspvenuÎncă nu există evaluări

- VLSI CMOS Fabrication TechnologyDocument15 paginiVLSI CMOS Fabrication TechnologyRamanaButterflyÎncă nu există evaluări

- Nmos FabricationDocument4 paginiNmos FabricationAshadur RahamanÎncă nu există evaluări

- Faculty of Engineering Lab Sheet Processing and Fabrication Technology EEN3106Document15 paginiFaculty of Engineering Lab Sheet Processing and Fabrication Technology EEN3106KarimovaRaikhanovnaÎncă nu există evaluări

- CMOS Fabrication Steps - Best VLSI Training - VLSI FOR ALL-5Document5 paginiCMOS Fabrication Steps - Best VLSI Training - VLSI FOR ALL-5ESWAR TERLIÎncă nu există evaluări

- Isolation: CMOS Processing TechnologyDocument15 paginiIsolation: CMOS Processing TechnologyAshwani RanaÎncă nu există evaluări

- CMOS Fabrication: (With Extended Comments)Document26 paginiCMOS Fabrication: (With Extended Comments)srivardhana7Încă nu există evaluări

- Microsoft Powerpoint - Vlsi Design AspectDocument89 paginiMicrosoft Powerpoint - Vlsi Design AspectAKASHDIP DUTTAÎncă nu există evaluări

- MINOR2 DfinalocxDocument32 paginiMINOR2 DfinalocxVenkatesh KumarÎncă nu există evaluări

- Lecture 2 - CMOS and FabDocument49 paginiLecture 2 - CMOS and FabSai SadiqÎncă nu există evaluări

- MOS Integrated Circuit DesignDe la EverandMOS Integrated Circuit DesignE. WolfendaleÎncă nu există evaluări

- Plasma Etching Processes for CMOS Devices RealizationDe la EverandPlasma Etching Processes for CMOS Devices RealizationNicolas PossemeÎncă nu există evaluări

- Plasma Etching Processes for Interconnect Realization in VLSIDe la EverandPlasma Etching Processes for Interconnect Realization in VLSINicolas PossemeÎncă nu există evaluări