Documente Academic

Documente Profesional

Documente Cultură

Semafor Bun

Încărcat de

Cristi SzaboDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Semafor Bun

Încărcat de

Cristi SzaboDrepturi de autor:

Formate disponibile

library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.

ALL; entity state_machine_vhdl is PORT( clock : IN std_logic; reset : IN std_logic; --magistrala Nord-Sud Nr : OUT std_logic; Ng : OUT std_logic; Ny : OUT std_logic; --magistrala Est-Vest Er : OUT std_logic; Eg : OUT std_logic; Ey : OUT std_logic); end state_machine_vhdl;

architecture Behavioral of state_machine_vhdl is TYPE t_state is (red, green, yellow); SIGNAL present_state, next_state : t_state := green; SIGNAL sensor_count : std_logic_vector (3 downto 0); COMPONENT proiect_counter_down PORT( clk : IN std_logic; reset : IN std_logic;

count : OUT std_logic_vector (3 downto 0) ); END COMPONENT; begin Inst_proiect_counter_down:proiect_counter_down PORT MAP( clk => clock, reset => reset, count => sensor_count ); PROCESS(present_state, sensor_count) BEGIN CASE present_state IS WHEN green => next_state <= yellow; Nr <= '0'; Ng <= '1'; Ny <= '0';

Er <= '1'; Eg <= '0'; Ey <= '0'; WHEN red => Nr <= '1'; Ng <= '0'; Ny <= '0';

Er <= '0'; Eg <= '1'; Ey <= '0'; next_state <= green; WHEN yellow => next_state <= red; Nr <= '0'; Ng <= '0'; Ny <= '1';

Er <= '0'; Eg <= '0'; Ey <= '1'; IF (sensor_count = "0000") then next_state <= green; elsif (sensor_count = "0101") then next_state <= red; elsif (sensor_count = "1011") then next_state <= yellow;

END IF; END CASE; END PROCESS; PROCESS(clock,next_state) BEGIN if (clock'EVENT and clock = '1') then

present_state <= next_state; end if; END PROCESS; end Behavioral;

SIMULARE:

S-ar putea să vă placă și

- 3 Program CodeDocument15 pagini3 Program Codergkusumba100% (1)

- VHDL Hex Counter LabDocument12 paginiVHDL Hex Counter LabYX GohÎncă nu există evaluări

- Multiplicacion Sumas Sucesivas Factores de 4 BitsDocument4 paginiMultiplicacion Sumas Sucesivas Factores de 4 BitsRoberto Carlos QuispeÎncă nu există evaluări

- Lab Manual 10Document8 paginiLab Manual 10ThoughtsÎncă nu există evaluări

- Sumador BCD CodigoDocument1 paginăSumador BCD Codigojjimenezmolina00Încă nu există evaluări

- FFTDocument40 paginiFFTsreekuttymsÎncă nu există evaluări

- N Bit Adder: VHDL CodeDocument3 paginiN Bit Adder: VHDL Codeabhay kumarÎncă nu există evaluări

- Top CTRL MotorDocument1 paginăTop CTRL MotorVictor RamosÎncă nu există evaluări

- INFORME PRACTICA No 2Document30 paginiINFORME PRACTICA No 2MAURICIO REYES ROSEROÎncă nu există evaluări

- Lab Report: Name: Abdul Rehman Khan STD No: 184311 Lab Assistant: MR Oluwatayomi Rereloluwa AdegboyeDocument20 paginiLab Report: Name: Abdul Rehman Khan STD No: 184311 Lab Assistant: MR Oluwatayomi Rereloluwa AdegboyeSikandar AliÎncă nu există evaluări

- Interface Digital and Analog I/O Devices (Arduino Interfacing)Document29 paginiInterface Digital and Analog I/O Devices (Arduino Interfacing)Raggy TannaÎncă nu există evaluări

- Three-Phase Motor Control With STM32F401RET6U: B L D CDocument34 paginiThree-Phase Motor Control With STM32F401RET6U: B L D Cbokic88Încă nu există evaluări

- Lab 13Document11 paginiLab 13ubaidÎncă nu există evaluări

- Lampiran_04Document20 paginiLampiran_04naf2345Încă nu există evaluări

- Programas VHDLDocument7 paginiProgramas VHDLLuisDuránÎncă nu există evaluări

- Assignment 1: 8 Bit Ring CounterDocument12 paginiAssignment 1: 8 Bit Ring CounterAarohi VoraÎncă nu există evaluări

- MIPSDocument5 paginiMIPSSynnon PageÎncă nu există evaluări

- Ee529 Lab Asg4Document10 paginiEe529 Lab Asg4dd23015Încă nu există evaluări

- IoT Assignment - Measure Sensor ValuesDocument21 paginiIoT Assignment - Measure Sensor ValuesParamShahÎncă nu există evaluări

- VHDL Exercises for 4-Bit Counter, 8-Bit Pattern Matching & Serial to Parallel ConverterDocument8 paginiVHDL Exercises for 4-Bit Counter, 8-Bit Pattern Matching & Serial to Parallel ConverterHamza BadrÎncă nu există evaluări

- MemoriaSRAM Chasi GutierrezDocument16 paginiMemoriaSRAM Chasi GutierrezJonathan Chasi0% (1)

- FPGA-BASED N-BIT SERIAL ADDERDocument9 paginiFPGA-BASED N-BIT SERIAL ADDERayeshaÎncă nu există evaluări

- VHDL Code for QDR SRAM Controller and ComponentsDocument14 paginiVHDL Code for QDR SRAM Controller and ComponentsAli SubhiÎncă nu există evaluări

- Design Example 5.5Document10 paginiDesign Example 5.5MaheshÎncă nu există evaluări

- V HDL SampleDocument5 paginiV HDL Sampleppat2006Încă nu există evaluări

- 4-bit CSA/CLA Block Diagram and VHDL CodeDocument4 pagini4-bit CSA/CLA Block Diagram and VHDL CodeMaitri SenÎncă nu există evaluări

- Structural VHDL Program For TDocument8 paginiStructural VHDL Program For TUditha MuthumalaÎncă nu există evaluări

- AIM - Design Synthesize and Stimulate 2 4 and 3 8 Decoder Activity 1 - 2 4 DECODER:-Vhdl CodeDocument6 paginiAIM - Design Synthesize and Stimulate 2 4 and 3 8 Decoder Activity 1 - 2 4 DECODER:-Vhdl Codekshitij_gaur13Încă nu există evaluări

- LED Blinking Lab Manual ChapterDocument30 paginiLED Blinking Lab Manual Chapterराजस करंदीकरÎncă nu există evaluări

- VHDL CodesDocument53 paginiVHDL CodesANOOP MISHRAÎncă nu există evaluări

- VerilogDocument22 paginiVerilogSyurga FathonahÎncă nu există evaluări

- Sensor User Manual ITG-3200 Gyro BreakoutDocument7 paginiSensor User Manual ITG-3200 Gyro BreakoutRosana FariaÎncă nu există evaluări

- Beginning FPGA Programming - Partie51Document5 paginiBeginning FPGA Programming - Partie51ali alilouÎncă nu există evaluări

- HDL Description of AluDocument8 paginiHDL Description of AluRavi HattiÎncă nu există evaluări

- Implementar en VHDL el sumador parametrizado y la ALUDocument11 paginiImplementar en VHDL el sumador parametrizado y la ALUseb wood21Încă nu există evaluări

- IoT Practical File BETN1EC18004Document34 paginiIoT Practical File BETN1EC18004Hashtag BloggersÎncă nu există evaluări

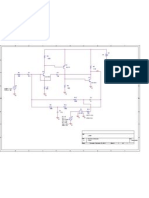

- Name: Omkar Nandu Patil USN: 2JI18EC110 Roll No. /DIV: 52/A Sub: Embedded SystemDocument22 paginiName: Omkar Nandu Patil USN: 2JI18EC110 Roll No. /DIV: 52/A Sub: Embedded SystemOMKAR PATILÎncă nu există evaluări

- E Cad Lab ManualDocument51 paginiE Cad Lab ManualRajesh DoradlaÎncă nu există evaluări

- Generic Component VHDLDocument5 paginiGeneric Component VHDLmussadaqhussain8210Încă nu există evaluări

- MDS I ManualDocument41 paginiMDS I ManualPanku RangareeÎncă nu există evaluări

- VHDL Codes for Logic Gates and Sequential CircuitsDocument42 paginiVHDL Codes for Logic Gates and Sequential CircuitsNaresh KumarÎncă nu există evaluări

- Generics and Configurations in VHDLDocument34 paginiGenerics and Configurations in VHDLAnil YadavÎncă nu există evaluări

- Electronics Design Lab Manual - VLSI Prog-V3Document14 paginiElectronics Design Lab Manual - VLSI Prog-V3shanmugasundatamÎncă nu există evaluări

- Memory and Register VHDL ModulesDocument9 paginiMemory and Register VHDL ModulesShaqer ZohaÎncă nu există evaluări

- VHDL Örnekler2Document5 paginiVHDL Örnekler2Ömer KüllaçÎncă nu există evaluări

- ECAD LAB2 (Master Copy)Document57 paginiECAD LAB2 (Master Copy)B.n. Srinivasa RaoÎncă nu există evaluări

- Digital Lab Cs 6211 VHDL ProgramsDocument13 paginiDigital Lab Cs 6211 VHDL ProgramsMurugan GÎncă nu există evaluări

- MP 2,3,4Document5 paginiMP 2,3,4tj millarÎncă nu există evaluări

- Sequential Circuits and Seven Segment Display: Lab Assignment 10Document7 paginiSequential Circuits and Seven Segment Display: Lab Assignment 10Ahmed UzairÎncă nu există evaluări

- Example VHDL Entity - 0 To 9 Counter: VHDL Model VHDL Test BenchDocument1 paginăExample VHDL Entity - 0 To 9 Counter: VHDL Model VHDL Test BenchsumtingwongdumgaiÎncă nu există evaluări

- Aim: Design Mod 8 Down CounterDocument3 paginiAim: Design Mod 8 Down CounterAtit PatelÎncă nu există evaluări

- 8x8 FIFO Buffer VHDL DesignDocument2 pagini8x8 FIFO Buffer VHDL DesignIgnacioMartíÎncă nu există evaluări

- CED19I032Document13 paginiCED19I032Pranavram VÎncă nu există evaluări

- VHDL Lab FileDocument25 paginiVHDL Lab FileAshish KumarÎncă nu există evaluări

- ks0013 Rotary Encoder ModuleDocument3 paginiks0013 Rotary Encoder ModuleSundaram NatarajanÎncă nu există evaluări

- ECE371 Lab1Report Group2Document9 paginiECE371 Lab1Report Group2Le HieuÎncă nu există evaluări

- Team Members for Chess Panel ProjectDocument31 paginiTeam Members for Chess Panel ProjectMahmoud El-tabeyÎncă nu există evaluări

- Correction TPDocument4 paginiCorrection TPHichem GuedriÎncă nu există evaluări

- Arduino Measurements in Science: Advanced Techniques and Data ProjectsDe la EverandArduino Measurements in Science: Advanced Techniques and Data ProjectsÎncă nu există evaluări

- Digital LED Thermometer with Microcontroller AVR ATtiny13De la EverandDigital LED Thermometer with Microcontroller AVR ATtiny13Evaluare: 5 din 5 stele5/5 (1)

- Tutela Şi Curatela În Dreptul Internaţional Privat: Aspecte ComparativeDocument8 paginiTutela Şi Curatela În Dreptul Internaţional Privat: Aspecte ComparativeCristi SzaboÎncă nu există evaluări

- PWM Signal GeneratorsDocument15 paginiPWM Signal GeneratorsCristi SzaboÎncă nu există evaluări

- L7700 IP Power SupplyDocument29 paginiL7700 IP Power SupplyCristi SzaboÎncă nu există evaluări

- Electric MachinesDocument8 paginiElectric MachinesCristi SzaboÎncă nu există evaluări

- Esquema Arduino UNO R3Document1 paginăEsquema Arduino UNO R3stangne1Încă nu există evaluări

- Cod ReleeeDocument2 paginiCod ReleeeCristi SzaboÎncă nu există evaluări

- Cod InvertorDocument2 paginiCod InvertorCristi SzaboÎncă nu există evaluări

- Capitolul 1Document18 paginiCapitolul 1Cristi SzaboÎncă nu există evaluări

- Cod Invertor HbridgeDocument1 paginăCod Invertor HbridgeCristi SzaboÎncă nu există evaluări

- Sunpower Solar Inverter: Owner'S ManualDocument88 paginiSunpower Solar Inverter: Owner'S ManualVadapalli Anantha Srinivasa KumarÎncă nu există evaluări

- EAS 199 Fall 2011 Basic Pulse Width ModulationDocument7 paginiEAS 199 Fall 2011 Basic Pulse Width ModulationCristi SzaboÎncă nu există evaluări

- Coduri Placa MXDocument7 paginiCoduri Placa MXCristi SzaboÎncă nu există evaluări

- Microcontroller Based Novel Dc-to-Ac Grid Connected Inverter TopologyDocument5 paginiMicrocontroller Based Novel Dc-to-Ac Grid Connected Inverter TopologyIDESÎncă nu există evaluări

- Driver CircuitDocument30 paginiDriver CircuitCristi SzaboÎncă nu există evaluări

- 1.IRFP460 2.diode 1N4007 3.capacitors 1000uF/50V 1000uF/25V 4.optocoupler MCT2E 5.transistors 2N2222 CK100 6.resistorsDocument4 pagini1.IRFP460 2.diode 1N4007 3.capacitors 1000uF/50V 1000uF/25V 4.optocoupler MCT2E 5.transistors 2N2222 CK100 6.resistorsJay MjÎncă nu există evaluări

- FiguraDocument1 paginăFiguraCristi SzaboÎncă nu există evaluări