Documente Academic

Documente Profesional

Documente Cultură

Ese 570 Mos Inverters: Static Characteristics

Încărcat de

Vipul MistryDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Ese 570 Mos Inverters: Static Characteristics

Încărcat de

Vipul MistryDrepturi de autor:

Formate disponibile

ESE 570 MOS INVERTERS: STATIC

CHARACTERISTICS

Kenneth R. Laker, University of Pennsylvania

1

A

B = A

IDEAL INVERTER VOLTAGE TRANSFER

CHARTERISTIC (VTC)

Kenneth R. Laker, University of Pennsylvania

2

A B

0

0 1

1

V

in

V

out

V

DD

V

DD

V

th

=

V

DD

/2

Logic 1

output

Logic 0

output

Kenneth R. Laker, University of Pennsylvania

3

LOAD

+

-

V

L

I

D

I

L

C

out V

out

V

in

V

in

V

out

V

OH

V

OH

V

th

V

OL

V

out

=

V

in

V

IL

V

IH

dV

out

dV

in

=-1

dV

out

dV

in

=-1

V

OH

-> max output voltage when

output is 1

V

OL

-> min output voltage when

output is 0

V

IL

-> max input voltage which

can be interpreted as 0

ACTUAL INVERTER VOLTAGE TRANSFER

CHARTERISTIC (VTC)

V

IH

-> min input voltage which

can be interpreted as 1

V

DD

Kenneth R. Laker, University of Pennsylvania

4

V

OH

-> max output voltage when output is 1

V

OL

-> min output voltage when output is 0

V

IL

-> max input voltage which can be interpreted as 0

V

IH

-> min input voltage which can be interpreted as 1

NOISE IMMUNITY AND NOISE MARGINS

interconnect interconnect

V

OH

V

OL

V

IL

V

OH

V

IH

V

OL

NOISE

NOISE

max allowable

0 voltage

min allowable

1 voltage

Kenneth R. Laker, University of Pennsylvania

5

V

OH

-> max output voltage when output is 1

V

OL

-> min output voltage when output is 0

V

IL

-> max input voltage which can be interpreted as 0

V

IH

-> min input voltage which can be interpreted as 1

V

in

V

IH

V

IL

Transition Region

V

OH

V

out

V

OL

NM

H

NM

L

NM

H

= V

OH

- V

IH

NM

L

= V

IL

- V

OL

NOISE IMMUNITY AND NOISE MARGINS

JUSTIFICATION FOR V

IL

, V

IH

:

LET: V

out

= f(V

in

), V

out

= f(V

in

+ V

noise

)

V

out

'

f(V

in

) +

dV

out

dV

in

V

noise

+ H. O. t e r ms

Perturbed Output = Nominal Output + Gain x Ext. Perturbation

0

0

V

DD

Kenneth R. Laker, University of Pennsylvania

6

FIVE CRITICAL VOLTAGES: V

OL

, V

OH

, V

IL

, V

IH

, V

th

determine:

--> DC Output Voltage Behavior

--> Noise Margins

--> Width and Location of Transition Region

POWER DISSIPATION AND DIE AREA

Power Dissipation -> HEAT

T

j

T

a

+ P

T

j

-> junction Temp

T

a

-> ambient Temp

-> Thermal Resistance

P -> Power Dissipated

P --> P

DC

, P

dynamic

P

DC

= V

DD

I

DC

ASSUME: V

in

= 1 50% of Op Time, 0 50% of Op Time

P

DC

V

DD

2

I

DC

(V

in

"0") + I

DC

(V

in

"1")

[ ]

DIE AREA --> MIN W x L and routing --> limited by design rules

Min Die Area => W/L -> 1

Kenneth R. Laker, University of Pennsylvania

7

RESISTIVE-LOAD INVERTER

CUTOFF: V

in

= V

GS

< V

T0,n

, I

D

= 0

LINEAR: V

in

= V

GS

> V

T0,n

,

V

out

= V

DS

< V

in

- V

t0,n

I

D

k

n

2

2(V

in

V

T0, n

) V

out

V

out

2

[ ]

SATURATION:

V

in

= V

GS

> V

T0,n

V

out

= V

DS

> V

in

- V

T0,n

I

D

k

n

2

(V

in

V

T0, n

)

2

Where:

k

n

n

C

ox

W

L

Let (for hand calculations) = 0

= V

DS

V

BS

= 0 => V

T,n

= V

T0,n

+

-

V

L

I

D

I

L

V

out

V

in

R

L

V

in

= V

GS

I

L

= I

D

V

DD

Units

RESISTOR R

L

:

V

in

V

out

V

OH

V

OH

V

OL

V

IL

V

IH

dV

out

dV

in

=-1

dV

out

dV

in

=-1

V

T0,n

A B

C

V

out

= V

in

- V

T0,n

LIN

SAT

CALCULATION OF V

OH

:

V

out

V

DD

R

L

I

L

V

in

< V

T0,n

=> nMOS Cut-off

A

I

D

= I

L

= 0 => V

OH

= V

DD

Kenneth R. Laker, University of Pennsylvania

8

A

V

DD

V

out

I

L

= 0

R

L

+

-

V

L

I

D

I

L

V

out

V

in

R

L

V

in

= V

GS

I

L

= I

D

V

DD

= V

DS

V

in

V

out

V

OH

V

OH

V

OL

V

IL

V

IH

dV

out

dV

in

=-1

dV

out

dV

in

=-1

V

T0,n

A B

C

V

out

= V

in

- V

T0,n

LIN

SAT

V

in

V

out

V

OH

V

OH

V

OL

V

IL

V

IH

dV

out

dV

in

=-1

dV

out

dV

in

=-1

V

T0,n

A

B

C

V

out

= V

in

- V

T0,n

LIN

SAT

9

10

Kenneth R. Laker, University of Pennsylvania

where V

out

= V

OL

V

DD

V

OL

R

L

k

n

2

2(V

DD

V

T0, n

) V

OL

V

OL

2

[ ]

where V

in

= V

OH

= V

DD

I

L

= I

D

V

OL

2

2 V

DD

V

T0, n

+

1

k

n

R

L

_

,

V

OL

+

2

k

n

R

L

V

DD

0

V

OL

V

DD

V

T0,n

+

1

k

n

R

L

t V

DD

V

T0,n

+

1

k

n

R

L

_

,

2

2

k

n

R

L

V

DD

0 < V

OL

< V

T0,n

C

V

DD

V

out

I

L

I

D

R

L

+

-

V

L

I

D

I

L

V

out

V

in

R

L

V

in

= V

GS

I

L

= I

D

V

DD

= V

DS

I

D

k

n

2

2(V

in

V

T0, n

) V

out

V

out

2

[ ]

CALCULATION OF V

OL

:

C

I

L

V

DD

V

OL

R

L

out

Kenneth R. Laker, University of Pennsylvania

11

CALCULATION OF V

IL

:

B

dV

out

dV

in

1 @ V

in

= V

IL

=> V

out

V

OH

I

L

= I

D

Differentiate wrt to V

in

, i.e.

1

R

L

dV

out

dV

in

k

n

(V

in

V

T0, n

)

V

IL

V

T0, n

+

1

k

n

R

L

V

DD

V

out

(V

in

V

IL

)

R

L

k

n

2

(V

IL

V

T0, n

)

2

V

out

(V

in

V

IL

) V

DD

1

2k

n

R

L

Find V

out

(when V

in

= V

IL

):

B

V

DD

I

D

V

out

R

L

I

L

= V

DS

+

-

V

L

I

D

I

L

V

out

V

in

R

L

V

in

= V

GS

I

L

= I

D

V

DD

Kenneth R. Laker, University of Pennsylvania

12

CALCULATION OF V

IH

:

C

C

dV

out

dV

in

1

@ V

in

= V

IH

=> V

out

V

OL

I

L

= I

D

V

DD

V

out

R

L

k

n

2

2(V

in

V

T0, n

) V

out

V

out

2

[ ]

Differentiate wrt to V

in

, i.e.

1

R

L

dV

out

dV

in

k

n

2

2(V

in

V

T0, n

)

dV

out

dV

in

+ 2V

out

2V

out

dV

out

dV

in

1

]

1

-1

-1

-1

V

IH

V

IH

V

T0,n

+ 2V

out

1

k

n

R

L

V

DD

V

out

I

D

R

L

I

L

= V

DS

+

-

V

L

I

D

I

L

V

out

V

in

R

L

V

in

= V

GS

I

L

= I

D

V

DD

CALCULATION OF V

IH

:

C

C

Kenneth R. Laker, University of Pennsylvania

13

Find V

out

(V

in

= V

IH

):

V

DD

V

out

R

L

k

n

2

2(V

IH

V

T0,n

) V

out

V

out

2

[ ]

where

V

IH

V

T0,n

+ 2V

out

1

k

n

R

L

V

DD

V

out

R

L

k

n

2

2(V

T0,n

+ 2V

out

1

k

n

R

L

V

T0,n

) V

out

V

out

2

1

]

1

V

IH

V

T0,n

+ 2

2

3

V

DD

k

n

R

L

1

k

n

R

L

V

out

(V

in

V

IH

)

2

3

V

DD

k

n

R

L

I

L

R

L

I

D

V

DD

V

out

CALCULATION OF V

th

:

Kenneth R. Laker, University of Pennsylvania

14

V

in

= V

out

= V

th

=> V

DS

= V

GS

> V

GS

- V

T0,n

B

V

DD

V

out

R

L

k

n

2

(V

in

V

T0, n

)

2

I

L

= I

D

V

DD

V

th

R

L

k

n

2

(V

th

V

T0,n

)

2

V

th

V

th

V

th

2

2 V

T0,n

1

k

n

R

L

_

,

V

th

+ V

T0, n

2

2V

DD

k

n

R

L

0

V

th

V

T0, n

1

k

n

R

L

t V

T0,n

1

k

n

R

L

_

,

2

+

2 V

DD

k

n

R

L

V

T0, n

2

Kenneth R. Laker, University of Pennsylvania

15

SUMMARY - RESISTIVE LOAD INVERTER

V

OH

= V

DD

V

OL

V

DD

V

T0,n

+

1

k

n

R

L

t V

DD

V

T0,n

+

1

k

n

R

L

_

,

2

2

k

n

R

L

V

DD

V

IH

V

T0,n

+ 2

2

3

V

DD

k

n

R

L

1

k

n

R

L

V

out

(V

in

V

IH

)

2

3

V

DD

k

n

R

L

V

IL

V

T0, n

+

1

k

n

R

L

V

out

(V

in

V

IL

) V

DD

1

2k

n

R

L

V

th

V

T0, n

1

k

n

R

L

+ V

T0,n

1

k

n

R

L

_

,

2

+

2 V

DD

k

n

R

L

V

T0, n

2

V

in

V

out

k

n

R

L

= 8V

-1

5V

5V

k

n

R

L

= 2V

-1

k

n

R

L

= 4V

-1

V

DD

= 5V

V

T0,n

= 1 V

Units

POWER DISSIPATION - RESISTIVE LOAD INVERTER

P

DC

V

DD

2

I

DC

(V

in

"0") + I

DC

(V

in

"1")

[ ]

Kenneth R. Laker, University of Pennsylvania

16

WHEN V

in

= V

OH

:

WHEN V

in

= V

OL

: DRIVER nMOS in CUT-OFF

I

L

= I

D

= 0 => P(V

in

= 0) = 0

P

DC

(average)

V

DD

2

V

DD

V

OL

R

L

R

L

I

D

I

L

= 0

V

DD

V

DD

I

L

V

out

V

out

C

R

L

A

Kenneth R. Laker, University of Pennsylvania

17

EXAMPLE 5.1

Consider the following inverter design problem:

GIVEN: V

DD

= 5 V, k

n

= 30 A/V

2

and V

T0,n

= 1.0 V

Determine the W/L ratio of the driver transistor and the value

of the load resistor R

L

to realize V

OL

= 0.2 V.

For V

out

= V

OL

=> V

in

= V

OH

= V

DD

V

DD

V

OL

R

L

k

n

'

2

W

L

2(V

DD

V

T0,n

) V

OL

V

OL

2

[ ]

5 0.2

R

L

30x10

6

2

W

L

2(5 1)0.2 (0.2)

2

[ ]

W

L

R

L

2.05x10

5

NO UNIQUE W/L, R

L

V

DD

I

L

I

D

V

out

R

L

C

W

L

R

L

2.05x10

5

Kenneth R. Laker, University of Pennsylvania

18

(W/L) - RATIO

R

L

[k] P

DC

(average) [W]

1

2

3

4

5

6

205.0

102.5

68.4

51.3

41.0

34.2

58.5

117.1

175.4

233.9

292.7

350.8

Metal 1

n

+

Polysilicon (doped)

V

DD

GND

V

out

V

in

n

+

resistor

20 - 100 /sq.

EXAMPLE 5.1 Cont.

Kenneth R. Laker, University of Pennsylvania

19

EXAMPLE 5.2

Consider a resistive-load inverter with

V

DD

= 5 V, k

n

= 20 A/V

2

, V

T0n

= 0.8 V, R

L

= 200 k, W/L = 2

Calculate the critical voltages (V

OL

, V

OH

, V

IL

, V

IH

) on the VTC

and determine the noise margins.

V

OH

=V

DD

= 5 V

k

n

= k

n

(W/L) = 40 A/V

2

=> k

n

R

L

= 8 V

-1

V

OL

V

DD

V

T0,n

+

1

k

n

R

L

t V

DD

V

T0,n

+

1

k

n

R

L

_

,

2

2

k

n

R

L

V

DD

V

OL

=0.147 V

V

IL

V

T0, n

+

1

k

n

R

L

V

IL

=0.925 V

Consider a resistive-load inverter with

V

DD

= 5 V, k

n

= 20 A/V

2

, V

T0n

= 0.8 V, R

L

= 200 k, W/L = 2

Calculate the critical voltages (V

OL

, V

OH

, V

IL

, V

IH

) on the VTC

and determine the noise margins.

EXAMPLE 5.2 Cont.

Kenneth R. Laker, University of Pennsylvania

20

V

IH

V

T0,n

+ 2

2

3

V

DD

k

n

R

L

1

k

n

R

L

V

IH

=1.97 V

V

OH

=V

DD

= 5 V

V

OL

=0.147 V

V

IL

=0.925 V

NM

H

= V

OH

- V

IH

= 5V - 1.97V = 3.03V

NM

L

= V

IL

- V

OL

= 0.93V - 0.15V = 0.78V

GOOD DESIGN => NM

L

> V

DD

/4 = 1.25 V

Kenneth R. Laker, University of Pennsylvania

21

SATURATED ENHANCEMENT-LOAD INVERTER

V

BS,d

= 0 => V

T,d

= V

T0,n

V

BS,L

= - V

out

< 0 => V

T,L

= V

T0,n

LOAD:

V

GS,L

= V

DS,L

=> V

DS,L

> V

GS,L

- V

T,L

SAT cond. is ALWAYS SATISFIED

I

L

k

n

'

2

W

L

_

,

L

V

GS,L

V

T. L

( )

2

k

n

'

2

W

L

_

,

L

V

DD

V

out

V

T .L

( )

2

+

-

I

D

V

out

V

in

= V

DS,d

I

L

= I

D

I

L

V

in

= V

GS,d

V

DD

V

in

V

out

V

OH

V

OH

V

OL

V

IL

V

IH

dV

out

dV

in

=-1

dV

out

dV

in

=-1

V

T0,n

A B

C

V

out

= V

in

- V

T0,n

LIN

SAT

V

sb

0

Kenneth R. Laker, University of Pennsylvania

Load -> Sat, Driver -> Lin

k

n

'

2

W

L

_

,

L

V

DD

V

out

V

T . L

( )

2

k

n

'

2

W

L

_

,

d

V

in

V

T0, n

( )

2

22

V

in

V

out

V

OH

V

OH

V

OL

V

IL

V

IH

dV

out

dV

in

=-1

dV

out

dV

in

=-1

V

T0,n

A B

C

V

out

= V

in

- V

T0,n

LIN

SAT

Load -> Sat, Driver -> Sat

k

n

'

2

W

L

_

,

L

V

DD

V

out

V

T . L

( )

2

k

n

'

2

W

L

_

,

d

2[V

in

V

T0, n

]V

out

V

out

2

( )

+

-

I

D

V

out

V

in

= V

DS,d

I

L

= I

D

I

L

V

in

= V

GS,d

V

DD

B

C

V

OH

< V

DD

V

OL

> 0

Load -> Sat, Driver -> Cutoff

I

L

k

n

'

2

W

L

_

,

L

V

DD

V

out

V

T. L

( )

2

0

A

V

IL

V

IH

, V

OL

V

sb

0

V

OH

Kenneth R. Laker, University of Pennsylvania

23

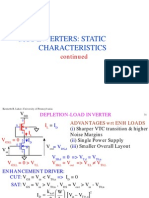

V

GS,L

= 0 > V

T,L

V

SB,d

= 0 => V

T,d

= V

T0,n

V

SB,L

= V

out

=> V

T,L

= V

T0,L

ADVANTAGES wrt ENH LOADS

(i) Sharper VTC transition & higher

Noise Margins

(ii) Smaller Overall Layout

ENHANCEMENT DRIVER:

CUT: V

GS

= V

in

< V

T0,n

=> I

D

= 0

SAT: V

GS

= V

in

> V

T0,n

, V

DS

= V

out

> V

in

- V

T0,n

I

D

k

n,d

'

2

W

L

_

,

d

V

in

V

T0, n

[ ]

2

LIN: V

GS

= V

in

> V

T0,n

, V

DS

= V

out

< V

in

- V

T0,n

I

D

k

n,d

'

2

W

L

_

,

d

2(V

in

V

T0, n

) V

out

(V

out

)

2

[ ]

+

-

I

D

V

in

I

L

V

GS,L

= 0

V

DD

DEPLETION-LOAD INVERTER

I

L

= I

D

= V

DS,d

V

out

V

sb

0

24

V

in

V

out

V

OH

V

OH

V

OL

V

IL

V

IH

dV

out

dV

in

=-1

dV

out

dV

in

=-1

V

T0,n

A

D

E

V

out

= V

in

- V

T0,n

LIN

SAT

C

LIN

SAT

V

DD

+ V

T,L

B

F

Kenneth R. Laker, University of Pennsylvania

V

OH

-> A DRVR - Cut-off; LOAD - LIN

V

OL

- > C DRVR - LIN; LOAD - SAT

V

IL

-> B DRVR - SAT; LOAD - LIN

V

IH

-> C DRVR - LIN; LOAD - SAT

V

th

-> D DRVR - SAT; LOAD - SAT

VTC PARATMETERS

25

Kenneth R. Laker, University of Pennsylvania

26

DESIGN OF DEPLETION LOAD INVERTERS

V

OL

V

OH

V

T0,n

V

OH

V

T0, n

( )

2

k

n, L

'

W/L ( )

L

k

n,d

'

W/L ( )

d

V

T,L

(V

OL

)

[ ]

2

V

OH

= V

DD

V

OH

V

T0, n

V

OH

V

T0,n

( )

2

1

k

R

V

T , L

(V

OL

)

[ ]

2

Solving for k

R

(given V

OL

):

k

R

k

n,d

'

W/L ( )

d

k

n, L

'

W/L ( )

L

V

T,L

(V

out

)

[ ]

2

2(V

OH

V

T0,n

) V

OL

V

OL

( )

2

where V

in

= V

OH

= V

DD

V

OL

V

in

V

out

k

R

= 10

5V

5V

k

R

= 2

k

R

= 4

V

DD

= 5V

V

T0,n

= 1 V

V

T0,L

= -3V

k

n,d

= k

n,L

= 40 A/V

2

k

R

k

n,d

'

W/L ( )

d

k

n, L

'

W/L ( )

L

where

Kenneth R. Laker, University of Pennsylvania

27

TYPICAL VTCs FOR DEPLETION LOAD INVERTERS FOR

DIFFERENT k

R

VALUES

In GENERAL:

k

n, d

'

k

n, L

'

28

CMOS INVERTER - STATIC CHARACTERISTICS

V

in

= V

GSn

= V

GSp

+ V

DD

V

out

= V

DSn

= V

DSp

+ V

DD

Kenneth R. Laker, University of Pennsylvania

G

B

S

D

G B

S

D

V

DD

V

in

V

out

V

SS

CUTOFF LINEAR SATURATED

V

GSp

> V

T0p

V

GSp

< V

T0p

V

GSp

< V

T0p

p-device V

in

< V

T0p

+ V

DD

V

in

< V

T0p

+ V

DD

V

in

> V

T0p

+ V

DD

V

DSp

> V

GSp

- V

T0p

V

DSp

< V

GSp

- V

T0p

V

out

> V

in

- V

T0p

V

out

< V

in

- V

T0p

V

GSn

< V

T0n

V

GSn

> V

T0n

V

GSn

> V

T0n

n-device V

in

> V

T0n

V

in

> V

T0n

V

in

< V

T0n

V

DSn

< V

GSn

- V

T0n

V

DSn

> V

GSn

- V

T0n

V

out

< V

in

- V

T0n

V

out

> V

in

- V

T0n

I

Dp

I

Dn

V

SBp

= 0

V

SBn

= 0

V

in

= V

gsn

= V

gsp

+ V

DD

V

out

= V

dsn

= V

dsp

+ V

DD

E

I

dsn

V

out

= 0

V

DD

29

I

dsn

I

dsp

V

out

B

V

DD

I

dsp

V

out

A

= 0

V

DD

C

I

dsn

I

dsp

V

out

V

DD

Kenneth R. Laker, University of Pennsylvania

D

I

dsn

I

dsp

V

out

V

DD

V

in

- V

T0n

E

C

D

A

B

I

Dp

= 0

I

Dp

I

Dp

I

Dp

I

Dn

I

Dn

I

Dn

I

Dn

= 0

G

B

S

D

G B

S

D

V

DD

V

in

V

out

V

SS

I

dsp

I

dsn

I

Dp

I

Dn

V

DD

V

DD

V

out

V

in

V

DD

/2

V

DD

/2 V

Tn

V

DD

V

Tp

+

A B D

E

C

V

out

= V

in

- V

Tp

V

out

= V

in

- V

Tp

- V

T0p

LIN

LIN

SAT

V

in

- V

T0p

V

T0n

V

DD

+V

T0p

SAT

V

in

A B

C

D

E

V

out

Kenneth R. Laker, University of Pennsylvania

30

I

dsp

V

out

A

= 0

V

DD

I

Dp

= I

Dn

= 0

V

OH

= V

DD

I

Dp

= I

Dn

= 0

V

OL

= 0

CALCULATE V

OL

CALCULATE V

OH

A

E

I

dsn

V

out

= 0

V

DD

E

I

Dn

= 0

I

Dp

= 0

0

0

0 0

Kenneth R. Laker, University of Pennsylvania

31

I

dsn

I

dsp

V

out

B

V

DD

CALCULATE V

IL

k

n

'

2

W

L

_

,

n

V

GSn

V

T0 n

( )

2

k

p

'

2

W

L

_

,

p

2 V

GSp

V

T0 p

( )

V

DSp

V

DSp

2

[ ]

I

Dp

= I

Dn

k

n

'

2

W

L

_

,

n

V

in

V

T0 n

( )

2

k

p

'

2

W

L

_

,

p

2 V

in

V

DD

V

T0 p

( )

V

out

V

DD

( )

V

out

V

DD

( )

2

[ ]

V

GSn

= V

in

, V

GSp

= V

in

- V

DD

, V

DSp

= V

out

- V

DD

B

I

Dn

I

Dp

G

B

S

D

G B

S

D

V

DD

V

in

V

out

V

SS

I

dsp

I

dsn

I

Dp

I

Dn

k

n

'

2

W

L

_

,

n

V

in

V

T0 n

( )

2

k

p

'

2

W

L

_

,

p

2 V

in

V

DD

V

T0 p

( )

V

out

V

DD

( )

V

out

V

DD

( )

2

[ ]

Kenneth R. Laker, University of Pennsylvania

32

DIFFERENTIATING wrt V

in

k

n

'

W

L

_

,

n

V

in

V

T0 n

( ) k

p

'

W

L

_

,

p

V

out

V

DD

( ) + V

in

V

DD

V

T0 p

( )

dV

out

dV

in

V

out

V

DD

( )

dV

out

dV

in

1

]

1

(-1)

(-1)

V

IL

V

IL

V

IL

2 V

out

+ V

T0 p

V

DD

+ k

R

V

T0 n

1+ k

R

k

n

'

W

L

_

,

n

V

IL

V

T0 n

( ) k

p

'

W

L

_

,

p

2V

out

V

IL

+ V

T0 p

V

DD

[ ]

SOLVING FOR V

IL

k

R

k

n

'

W/L ( )

n

k

p

'

W/L ( )

p

where

(5.59)

(5.62)

SOLVE Eqs (5.59) and (5.62) for V

out

and V

IL

Kenneth R. Laker, University of Pennsylvania

33

I

Dp

= I

Dn

D

I

dsn

I

dsp

V

out

V

DD

CALCULATE V

IH

k

n

'

2

W

L

_

,

n

2 V

GSn

V

T0 n

( )V

DSn

V

DSn

2

[ ]

k

p

'

2

W

L

_

,

p

V

GSp

V

T0 p

( )

2

V

GSn

= V

in

, V

DSn

= V

out

,V

GSp

= V

in

- V

DD

k

n

'

2

W

L

_

,

n

2 V

in

V

T0 n

( )V

out

V

out

2

[ ]

k

p

'

2

W

L

_

,

p

V

in

V

DD

V

T0 p

( )

2

D

G

B

S

D

G B

S

D

V

DD

V

in

V

out

V

SS

I

dsp

I

dsn

I

Dp

I

Dn

I

Dp

I

Dn

k

n

'

2

W

L

_

,

n

2 V

in

V

T0 n

( )V

out

V

out

2

[ ]

k

p

'

2

W

L

_

,

p

V

in

V

DD

V

T0 p

( )

2

Kenneth R. Laker, University of Pennsylvania

34

DIFFERENTIATING wrt V

in

SOLVING FOR V

IH

V

IH

V

DD

+ V

T0 p

+ k

R

2V

out

+ V

T0 n

( )

1 + k

R

k

R

k

n

'

W/L ( )

n

k

p

'

W/L ( )

p

where

k

n

'

W

L

_

,

n

V

in

V

T0 n

( )

dV

out

dV

in

+ V

out

V

out

dV

out

dV

in

1

]

1

k

p

'

W

L

_

,

p

V

in

V

DD

V

T0 p

( )

(-1)

(-1)

V

IH

V

IH

(5.64)

(5.67)

SOLVE Eqs. (5.64) and (5.67) for V

out

and V

IH

Kenneth R. Laker, University of Pennsylvania

35

CALCULATE V

th

I

Dp

= I

Dn

C

I

dsn

I

dsp

V

out

V

DD

k

n

'

2

W

L

_

,

n

V

in

V

T0 n

( )

2

k

p

'

2

W

L

_

,

p

V

in

V

DD

V

T0 p

( )

2

k

n

'

2

W

L

_

,

n

V

GSn

V

T0 n

( )

2

k

p

'

2

W

L

_

,

p

V

GSp

V

T0 p

( )

2

V

GSn

= V

in

, V

GSp

= V

in

- V

DD

C

G

B

S

D

G B

S

D

V

DD

V

in

V

out

V

SS

I

dsp

I

dsn

I

Dp

I

Dn

I

Dp

I

Dn

k

n

'

2

W

L

_

,

n

V

in

V

T0 n

( )

2

k

p

'

2

W

L

_

,

p

V

in

V

DD

V

T0 p

( )

2

SOLVING for V

th

= V

in

V

in

V

th

V

T0 n

+

1

k

R

V

DD

+ V

T0 p

( )

1+

1

k

R

_

,

Kenneth R. Laker, University of Pennsylvania

36

NOTE THAT

V

th

= V

in

= V

out

V

DD

V

DD

V

out

V

in

V

DD

/2

V

DD

/2 V

Tn

V

DD

V

Tp

+

A B D

E

C V

out

V

in

- V

T0n

- V

T0p

LIN

LIN

SAT

V

in

- V

T0p

V

T0n

V

DD

+V

T0p

SAT

V

in

A B

C

D

E

V

in

- V

out

V

in

V

out

V

DD

V

th

V

T0n

V

DD

+ V

T0p

I

Dp

= I

Dn

I

D

= 0, V

in

< V

T0n

I

D

= 0, V

in

> V

DD

+ V

T0p

I

D

= MAX, V

in

= V

th

POWER SUPPLY CURRENT VS V

IN

Kenneth R. Laker, University of Pennsylvania

37

Kenneth R. Laker, University of Pennsylvania

38

DESIGN OF CMOS INVERTERS

V

in

V

th

V

T0 n

+

1

k

R

V

DD

+ V

T0 p

( )

1+

1

k

R

_

,

SOLVING FOR k

R

FOR IDEAL INVERTER

V

th

1

2

V

DD

k

R

V

DD

+ V

T0 p

V

th

V

th

V

T0 n

_

,

2

k

R

( )

ideal

0. 5V

DD

+ V

T0 p

0. 5V

DD

V

T0 n

_

,

2

IF V

T0

= V

T0n

= - V

T0p

=>

k

R

( )

symmetric

inverter

1

k

R

k

n

'

W/L ( )

n

k

p

'

W/L ( )

p

n

C

ox

W/L ( )

n

p

C

ox

W/L ( )

p

n

W/L ( )

n

p

W/L ( )

p

Kenneth R. Laker, University of Pennsylvania

39

k

R

( )

symmetric

inverter

1

FOR SYMMETRIC INVERTER

W/L ( )

n

W/L ( )

p

230cm

2

/Vs

580cm

2

/Vs

W/L ( )

p

2.5 W/L ( )

n

V

IL

1

8

3 V

DD

2V

T0

( )

V

IH

1

8

5 V

DD

2V

T0

( )

V

T0

= V

T0n

= -V

T0p

NOTE: V

IL

+ V

IH

= V

DD

solve eqs. (5.59) and (5.62)

solve eqs. (5.64) and (5.67)

NM

H

= V

OH

- V

IH

= V

DD

- V

IH

= (3/8)V

DD

- (2/8)V

T0

NM

L

= V

IL

- V

OL

= V

IL

= (3/8)V

DD

+ (2/8)V

T0

+

Kenneth R. Laker, University of Pennsylvania

40

POWER DISSIPATION CONSIDERATIONS

P

DC

V

DD

2

I

DC

(V

in

"0") + I

DC

(V

in

"1")

[ ]

P(V

in

0) + P(V

in

1)

2

WHEN V

in

= V

OH

:

WHEN V

in

= V

OL

:

I

L

= I

D

= 0 => P(V

in

= 0) = 0

I

dsp

V

out

A

= 0

V

DD

E

I

dsn

V

out

= 0

V

DD

I

L

= I

D

= 0 => P(V

in

= 1) = 0

P

DC

= 0

A

E

I

Dp

= 0

I

Dn

= 0

DIE AREA CONSIDERATIONS

n

+

Polysilicon

n-Well

p

+

Metal 1

Contact/via

COLOR LEGEND

V

DD

GND V

out

V

in

V

DD

GND

V

out

V

in

Kenneth R. Laker, University of Pennsylvania

41

Pseudo-nMOS Inverter

V

DD

V

out

V

in

s

s

d

d

g

g

b

b

V

in

= V

GSn

V

out

= V

DSn

= V

DSp

+ V

DD

V

GSp

= - V

DD

< V

T0p

=> pMOS load always turned ON

V

DSp

= V

out

- V

DD

> V

GSp

- V

T0p

= -V

DD

- V

T0p

0 V

out

< - V

T0p

V

DSp

= V

out

- V

DD

< V

GSp

- V

T0p

= -V

DD

- V

T0p

(LIN)

(SAT)

V

out

> - V

T0p

V

OH

= V

DD

V

OL

> 0

P

DC

> 0

Kenneth R. Laker, University of Pennsylvania

42

S-ar putea să vă placă și

- Solutions) Mastering Physics HW30Document7 paginiSolutions) Mastering Physics HW30Adam BoltronÎncă nu există evaluări

- Solution Manual for an Introduction to Equilibrium ThermodynamicsDe la EverandSolution Manual for an Introduction to Equilibrium ThermodynamicsÎncă nu există evaluări

- Llab 3 Report Ece 331Document14 paginiLlab 3 Report Ece 331ToànNguyễnKhánh100% (1)

- Transfer Function for π Filter CircuitDocument7 paginiTransfer Function for π Filter CircuitBarney StinsonÎncă nu există evaluări

- 4 WarmupDocument9 pagini4 WarmupkrishaÎncă nu există evaluări

- ECE102 F11 Summary HighlightsDocument24 paginiECE102 F11 Summary HighlightsLolÎncă nu există evaluări

- DIGITAL SIGNAL PROCESSING LAB REPORTDocument8 paginiDIGITAL SIGNAL PROCESSING LAB REPORTHAMZA ALIÎncă nu există evaluări

- NUS EE2005 Homework Solution for Current Mirror CircuitDocument7 paginiNUS EE2005 Homework Solution for Current Mirror CircuitKL ChiangÎncă nu există evaluări

- 000 SOLN Chapte1 PDFDocument13 pagini000 SOLN Chapte1 PDFVivekBardiaÎncă nu există evaluări

- DOST-ASTI Electric Manual PDFDocument17 paginiDOST-ASTI Electric Manual PDFJB NavarroÎncă nu există evaluări

- Fundamental of Power Electronics Week 8 Assignment SolutionsDocument4 paginiFundamental of Power Electronics Week 8 Assignment SolutionsDeep Gandhi100% (1)

- Network Selected QuestionsDocument13 paginiNetwork Selected Questionsmisho_16100% (1)

- Solns - 1 CmosDocument15 paginiSolns - 1 Cmosramprakash_rampelliÎncă nu există evaluări

- Small Signal Model MOSFETDocument8 paginiSmall Signal Model MOSFETRAHUL100% (1)

- Experiment 6 Zener DiodeDocument8 paginiExperiment 6 Zener DiodeAyeshaÎncă nu există evaluări

- Chapter SixDocument5 paginiChapter Sixyunus memonÎncă nu există evaluări

- Analog CircuitsDocument52 paginiAnalog CircuitsrohanvermaaaaaÎncă nu există evaluări

- Solving Differential Equation Using Operational AmplifierDocument15 paginiSolving Differential Equation Using Operational AmplifierPalash DubeyÎncă nu există evaluări

- Laboratory Exercise 2: Discrete-Time Systems: Time-Domain RepresentationDocument3 paginiLaboratory Exercise 2: Discrete-Time Systems: Time-Domain RepresentationbichchaukmtÎncă nu există evaluări

- Bode Plots Nilson Sidra App E StudentDocument19 paginiBode Plots Nilson Sidra App E StudentSaied Aly SalamahÎncă nu există evaluări

- Week-09 Assignment Q1. Which of The Following Is/are TrueDocument5 paginiWeek-09 Assignment Q1. Which of The Following Is/are TrueDeep GandhiÎncă nu există evaluări

- Experimental Validation of Mesh Analysis MethodDocument7 paginiExperimental Validation of Mesh Analysis MethodRimsha ShakoorÎncă nu există evaluări

- Laplace Transform ExamplesDocument19 paginiLaplace Transform Exampleshamza abdo mohamoudÎncă nu există evaluări

- 3 Amplifier Common Mode Rejection Ratio Part I FullDocument9 pagini3 Amplifier Common Mode Rejection Ratio Part I FullUjjWal MahAjanÎncă nu există evaluări

- Experiment 12-Resonance Lab ReportDocument8 paginiExperiment 12-Resonance Lab ReportShahzad JameelÎncă nu există evaluări

- Differential and Multistage AmplifiersDocument30 paginiDifferential and Multistage AmplifierskhsniperÎncă nu există evaluări

- Diode Equivalent Circuits GuideDocument42 paginiDiode Equivalent Circuits Guidegirishkumardarisi254Încă nu există evaluări

- Unit 3 Discrete Time Fourier Transform Questions and Answers - Sanfoundry PDFDocument3 paginiUnit 3 Discrete Time Fourier Transform Questions and Answers - Sanfoundry PDFzohaibÎncă nu există evaluări

- Eca Lab ManualDocument78 paginiEca Lab ManualNageswariah.MÎncă nu există evaluări

- Project Report Digital Clock: Abu Dhabi UniversityDocument11 paginiProject Report Digital Clock: Abu Dhabi UniversityAbbas RajpootÎncă nu există evaluări

- Lab Requirements of Ece: Infrastructure Requirement As Per Aicte NormsDocument4 paginiLab Requirements of Ece: Infrastructure Requirement As Per Aicte NormsecessecÎncă nu există evaluări

- FM Balanced Slope DetectorDocument5 paginiFM Balanced Slope DetectorPujjalPandeyÎncă nu există evaluări

- Digital ElectronicsDocument102 paginiDigital Electronicsdurga0% (1)

- Question Bank Digital ElectronicsDocument12 paginiQuestion Bank Digital ElectronicsUrvin MistryÎncă nu există evaluări

- ECE102 - F12 ProSet 7 PDFDocument37 paginiECE102 - F12 ProSet 7 PDFlokeshwarrvrjcÎncă nu există evaluări

- Solid Sate Electronic Devices (Code: EE2411) - AY2021-S2Document12 paginiSolid Sate Electronic Devices (Code: EE2411) - AY2021-S2Huy Khang NguyễnÎncă nu există evaluări

- EE320 Electronic NotesDocument331 paginiEE320 Electronic NotesAngel Pérez Santiago100% (1)

- Introduction To VHDL - 2014FSDocument74 paginiIntroduction To VHDL - 2014FSĐoàn Vũ Phú VinhÎncă nu există evaluări

- Final Exam ECE 1312 Question Sem-2 2013-2014Document9 paginiFinal Exam ECE 1312 Question Sem-2 2013-2014Fatihah Aina100% (1)

- 08-Com101 AMDocument11 pagini08-Com101 AMHồng HoanÎncă nu există evaluări

- Discrete Time SystemsDocument19 paginiDiscrete Time SystemsGoodÎncă nu există evaluări

- IIUM Electronics ECE 1312/ECE 1231 Final Exam Sem 1 (2012 - 2013)Document8 paginiIIUM Electronics ECE 1312/ECE 1231 Final Exam Sem 1 (2012 - 2013)Ridhwan Asri100% (1)

- NAND Gate DDL Complete PDFDocument4 paginiNAND Gate DDL Complete PDFSarkaraliÎncă nu există evaluări

- M Lab Report 5Document9 paginiM Lab Report 5marryam nawazÎncă nu există evaluări

- 8.4 A Case Study: Using LCD Module On DE2 BoardDocument19 pagini8.4 A Case Study: Using LCD Module On DE2 BoardMas Shari0% (1)

- Devices and Circuits Ii: Lecture GoalsDocument3 paginiDevices and Circuits Ii: Lecture GoalsMạnh Cường TrầnÎncă nu există evaluări

- Solid Sate Electronic Devices (Code: 402401) - AY1516-S2Document12 paginiSolid Sate Electronic Devices (Code: 402401) - AY1516-S2MINH NGUYỄN THẾÎncă nu există evaluări

- EE222 - LAB 4 Simple Boolean Function Implementation: Noa Saula s11112442Document20 paginiEE222 - LAB 4 Simple Boolean Function Implementation: Noa Saula s11112442Noa SaulaÎncă nu există evaluări

- EE233 Lab1Document20 paginiEE233 Lab1NguyenThanhSang0404Încă nu există evaluări

- LIC FLEXI Lab Manual Second Experiment Student Copy-3Document5 paginiLIC FLEXI Lab Manual Second Experiment Student Copy-3Vignesh RamakrishnanÎncă nu există evaluări

- ECD Lab EEC 752Document17 paginiECD Lab EEC 752juhi99360% (5)

- First and Second Order Filter Transfer Functions ExplainedDocument59 paginiFirst and Second Order Filter Transfer Functions ExplainedDeepthiÎncă nu există evaluări

- Engineering Prob & Stat Lecture Notes 6Document12 paginiEngineering Prob & Stat Lecture Notes 6EICQ/00154/2020 SAMUEL MWANGI RUKWAROÎncă nu există evaluări

- A Network Theorem Dual to Miller's TheoremDocument5 paginiA Network Theorem Dual to Miller's TheoremSiddhant Jain0% (1)

- Sepic Converter Design and Operation: by Gregory SharpDocument21 paginiSepic Converter Design and Operation: by Gregory SharpSingam SridharÎncă nu există evaluări

- Mos Inverters: Static Characteristics: ContinuedDocument41 paginiMos Inverters: Static Characteristics: Continuedshoebhussain01Încă nu există evaluări

- MOS Inverters Dynamic CharacteristicsDocument78 paginiMOS Inverters Dynamic CharacteristicsSuraj KumarÎncă nu există evaluări

- Ee 560 Mos Inverters: Static Characteristics: ContinuedDocument37 paginiEe 560 Mos Inverters: Static Characteristics: ContinuedLucas WeaverÎncă nu există evaluări

- Ese570 Mos Theory p206Document41 paginiEse570 Mos Theory p206premkumar8719Încă nu există evaluări

- Notes CMOS Inverter StaticDocument5 paginiNotes CMOS Inverter StaticVipul MistryÎncă nu există evaluări

- 2514e0314058 2 PDFDocument4 pagini2514e0314058 2 PDFVipul MistryÎncă nu există evaluări

- 8086 Microprocessor OverviewDocument2 pagini8086 Microprocessor OverviewVipul MistryÎncă nu există evaluări

- Gruham DevelopersDocument2 paginiGruham DevelopersVipul MistryÎncă nu există evaluări

- Fundamentals of Image Processing Chapter 2Document8 paginiFundamentals of Image Processing Chapter 2Vipul MistryÎncă nu există evaluări

- AVR Development Board Features and Programming GuideDocument17 paginiAVR Development Board Features and Programming GuideVipul MistryÎncă nu există evaluări

- Real Time Road Sign Recognition System For Autonomous CarDocument14 paginiReal Time Road Sign Recognition System For Autonomous CarVipul MistryÎncă nu există evaluări

- Maths Class XDocument29 paginiMaths Class XtusharmetroÎncă nu există evaluări

- Image Restoration Chapter05 Handouts 2 FineDocument47 paginiImage Restoration Chapter05 Handouts 2 FineVipul MistryÎncă nu există evaluări

- FAQ PatentsDocument10 paginiFAQ PatentsVipul MistryÎncă nu există evaluări

- DCTDocument11 paginiDCTIlija FilipovicÎncă nu există evaluări

- Laboratory Manual: Embedded SystemsDocument74 paginiLaboratory Manual: Embedded SystemsVipul MistryÎncă nu există evaluări

- Research Methodology UTU SyllabusDocument2 paginiResearch Methodology UTU SyllabusVipul MistryÎncă nu există evaluări

- HDL DESCRIBES DIGITAL CIRCUITSDocument29 paginiHDL DESCRIBES DIGITAL CIRCUITSmuktikantaÎncă nu există evaluări

- Chapter 4: Delay of CMOS Logic GatesDocument8 paginiChapter 4: Delay of CMOS Logic Gatesswathi bnÎncă nu există evaluări

- C-Mos FDC (Floppy Disk Controller)Document3 paginiC-Mos FDC (Floppy Disk Controller)Bos QuÎncă nu există evaluări

- Sharp LC 22sb280utDocument18 paginiSharp LC 22sb280utGloria ManzanoÎncă nu există evaluări

- FinalDocument18 paginiFinalSamarth Can WinÎncă nu există evaluări

- Lecture (05) Boolean Algebra and Logic Gates: By: Dr. Ahmed ElshafeeDocument12 paginiLecture (05) Boolean Algebra and Logic Gates: By: Dr. Ahmed ElshafeevenkateshÎncă nu există evaluări

- System Verilog Quick RefDocument133 paginiSystem Verilog Quick Refraghavendra100% (5)

- Ch05 PowerDocument50 paginiCh05 PowerĐạt Nguyễn ThànhÎncă nu există evaluări

- Memories NotesDocument52 paginiMemories NotesDetroitÎncă nu există evaluări

- Combinational LogicDocument44 paginiCombinational LogicgayathriÎncă nu există evaluări

- Microelectronics MCQs-AnswersDocument4 paginiMicroelectronics MCQs-AnswersKimberly TaboraÎncă nu există evaluări

- Memory Organisation: Types, Hierarchy and Access MethodsDocument37 paginiMemory Organisation: Types, Hierarchy and Access MethodsRAJITHA RAMACHANDRANÎncă nu există evaluări

- 80V To 150V Non-Isolated DC/DC: Controllers, Monolithics & MOSFET DriversDocument4 pagini80V To 150V Non-Isolated DC/DC: Controllers, Monolithics & MOSFET DriversDuc VoquangÎncă nu există evaluări

- The Evolution of DSP ProcessorsDocument9 paginiThe Evolution of DSP Processorsumesh2byd9055Încă nu există evaluări

- Low-Frequency Dual Econoscillator: General Description FeaturesDocument6 paginiLow-Frequency Dual Econoscillator: General Description FeaturesrobertomanfrediÎncă nu există evaluări

- Soft Core Implementation On FPGADocument65 paginiSoft Core Implementation On FPGAArnab BhattacharjeeÎncă nu există evaluări

- Unit-2: Basic Computer Organization and DesignDocument55 paginiUnit-2: Basic Computer Organization and DesignaaÎncă nu există evaluări

- Spartan 6 Memory ResourcesDocument30 paginiSpartan 6 Memory ResourcesSugar BluesÎncă nu există evaluări

- Signal Conditioning Circuit DesignDocument3 paginiSignal Conditioning Circuit DesignRajÎncă nu există evaluări

- Lab 2 Logic Synthesis with Design CompilerDocument26 paginiLab 2 Logic Synthesis with Design Compiler陳美如Încă nu există evaluări

- Introduction to MicroprocessorsDocument11 paginiIntroduction to MicroprocessorsSupriya NairÎncă nu există evaluări

- VLSI System DesignDocument91 paginiVLSI System DesigneleenaamohapatraÎncă nu există evaluări

- Nuvoton N76E003AT20 Minimum System Board Nu-Link Programming Development BoardDocument10 paginiNuvoton N76E003AT20 Minimum System Board Nu-Link Programming Development BoardKokhito BlackHoleÎncă nu există evaluări

- z87 Deluxe Dram QVL 201406Document1 paginăz87 Deluxe Dram QVL 201406cipyyyyÎncă nu există evaluări

- Performance Analysis of Wallace Tree Multiplier With Kogge Stone Adder Using 15-4 CompressorDocument5 paginiPerformance Analysis of Wallace Tree Multiplier With Kogge Stone Adder Using 15-4 Compressoranil kumarÎncă nu există evaluări

- Cs 302 Short NotesDocument7 paginiCs 302 Short Notesbaghira12Încă nu există evaluări

- 5601 Edge Connector Breakout Board For The BBC Microbit Datasheet v1 2Document3 pagini5601 Edge Connector Breakout Board For The BBC Microbit Datasheet v1 2dborcic61Încă nu există evaluări

- Cadence SOC EncounterDocument222 paginiCadence SOC Encountereeshgarg0% (1)

- CHIP INPUT AND OUTPUT CIRCUITSDocument27 paginiCHIP INPUT AND OUTPUT CIRCUITSSrilatha KolliÎncă nu există evaluări

- 25AA640A 25LC640A 64K SPI Bus Serial EEPROM 200018-2449118Document39 pagini25AA640A 25LC640A 64K SPI Bus Serial EEPROM 200018-2449118ManunoghiÎncă nu există evaluări