Documente Academic

Documente Profesional

Documente Cultură

Datasheet 74192

Încărcat de

phongbui135Descriere originală:

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Datasheet 74192

Încărcat de

phongbui135Drepturi de autor:

Formate disponibile

SN54/74LS192

SN54/74LS193

PRESETTABLE BCD/DECADE

UP/DOWN COUNTER

PRESETTABLE 4-BIT BINARY PRESETTABLE BCD / DECADE

UP/DOWN COUNTER UP/ DOWN COUNTER

PRESETTABLE 4-BIT BINARY

UP/ DOWN COUNTER

The SN54/74LS192 is an UP/DOWN BCD Decade (8421) Counter and the

SN54/74LS193 is an UP/DOWN MODULO-16 Binary Counter. Separate LOW POWER SCHOTTKY

Count Up and Count Down Clocks are used and in either counting mode the

circuits operate synchronously. The outputs change state synchronous with

the LOW-to-HIGH transitions on the clock inputs.

Separate Terminal Count Up and Terminal Count Down outputs are

provided which are used as the clocks for a subsequent stages without extra J SUFFIX

logic, thus simplifying multistage counter designs. Individual preset inputs CERAMIC

allow the circuits to be used as programmable counters. Both the Parallel CASE 620-09

16

Load (PL) and the Master Reset (MR) inputs asynchronously override the 1

clocks.

• Low Power . . . 95 mW Typical Dissipation

• High Speed . . . 40 MHz Typical Count Frequency

• Synchronous Counting N SUFFIX

• Asynchronous Master Reset and Parallel Load PLASTIC

CASE 648-08

• Individual Preset Inputs 16

• Cascading Circuitry Internally Provided 1

• Input Clamp Diodes Limit High Speed Termination Effects

D SUFFIX

CONNECTION DIAGRAM DIP (TOP VIEW) SOIC

16

VCC P0 MR TCD TCU PL P2 P3 1 CASE 751B-03

16 15 14 13 12 11 10 9

ORDERING INFORMATION

NOTE:

The Flatpak version SN54LSXXXJ Ceramic

has the same pinouts SN74LSXXXN Plastic

(Connection Diagram) as SN74LSXXXD SOIC

the Dual In-Line Package.

1 2 3 4 5 6 7 8

P1 Q1 Q0 CPD CPU Q2 Q3 GND LOGIC SYMBOL

11 15 1 10 9

PIN NAMES LOADING (Note a)

HIGH LOW

PL P0 P1 P2 P3

CPU Count Up Clock Pulse Input 0.5 U.L. 0.25 U.L. 5 CPU TCU 12

CPD Count Down Clock Pulse Input 0.5 U.L. 0.25 U.L.

MR Asynchronous Master Reset (Clear) Input 0.5 U.L. 0.25 U.L.

4 CPD TCD 13

PL Asynchronous Parallel Load (Active LOW) Input 0.5 U.L. 0.25 U.L.

MR Q0 Q1 Q2 Q3

Pn Parallel Data Inputs 0.5 U.L. 0.25 U.L.

Qn Flip-Flop Outputs (Note b) 10 U.L. 5 (2.5) U.L.

TCD Terminal Count Down (Borrow) Output (Note b) 10 U.L. 5 (2.5) U.L. 14 3 2 6 7

TCU Terminal Count Up (Carry) Output (Note b) 10 U.L. 5 (2.5) U.L.

VCC = PIN 16

NOTES:

a. 1 TTL Unit Load (U.L.) = 40 µA HIGH/1.6 mA LOW. GND = PIN 8

b. The Output LOW drive factor is 2.5 U.L. for Military (54) and 5 U.L. for Commercial (74)

b. Temperature Ranges.

FAST AND LS TTL DATA

5-1

SN54/74LS192 • SN54/74LS193

STATE DIAGRAMS

0 1 2 3 4 LS192 LOGIC EQUATIONS 0 1 2 3 4

FOR TERMINAL COUNT

TCU = Q0 ⋅ Q3 ⋅ CPU

15 5 15 5

TCD = Q0 ⋅ Q1 ⋅ Q2 ⋅ Q3 ⋅ CPD

14 6 14 6

LS193 LOGIC EQUATIONS

FOR TERMINAL COUNT

13 7 13 7

TCU = Q0 ⋅ Q1⋅ Q2⋅ Q3 ⋅ CPU

TCD = Q0 ⋅ Q1 ⋅ Q2 ⋅ Q3 ⋅ CPD

12 11 10 9 8 12 11 10 9 8

COUNT UP

COUNT DOWN

LS192 LS193

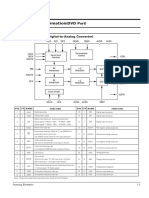

LOGIC DIAGRAMS

P0 P1 P2 P3

PL 11 15 1 10 9

(LOAD)

5

CPU 12 TCU

(UP COUNT) (CARRY

OUTPUT)

SD SD SD SD

Q Q Q Q

T T T T

CD Q CD Q CD Q CD Q

13 TCD

CPD 4

(BORROW

(DOWN OUTPUT)

COUNT) 14

MR

(CLEAR) 3 2 6 7

Q0 Q1 Q2 Q3

VCC = PIN 16 LS192

GND = PIN 8

= PIN NUMBERS

FAST AND LS TTL DATA

5-2

SN54/74LS192 • SN54/74LS193

LOGIC DIAGRAMS (continued)

P0 P1 P2 P3

PL 11 15 1 10 9

(LOAD)

5

CPU TCU

12

(UP COUNT) (CARRY

OUTPUT)

SD SD SD SD

Q Q Q Q

T T T T

CD Q CD Q CD Q CD Q

13 TCD

CPD 4

(BORROW

(DOWN OUTPUT)

COUNT) 14

MR

(CLEAR) 3 2 6 7

Q0 Q1 Q2 Q3

LS193

VCC = PIN 16

GND = PIN 8

= PIN NUMBERS

FAST AND LS TTL DATA

5-3

SN54/74LS192 • SN54/74LS193

FUNCTIONAL DESCRIPTION

The LS192 and LS193 are Asynchronously Presettable The Terminal Count Up (TCU) and Terminal Count Down

Decade and 4-Bit Binary Synchronous UP / DOWN (Revers- (TCD) outputs are normally HIGH. When a circuit has reached

able) Counters. The operating modes of the LS192 decade the maximum count state (9 for the LS192, 15 for the LS193),

counter and the LS193 binary counter are identical, with the the next HIGH-to-LOW transition of the Count Up Clock will

only difference being the count sequences as noted in the cause TCU to go LOW. TCU will stay LOW until CPU goes

State Diagrams. Each circuit contains four master/slave HIGH again, thus effectively repeating the Count Up Clock,

flip-flops, with internal gating and steering logic to provide but delayed by two gate delays. Similarly, the TCD output will

master reset, individual preset, count up and count down go LOW when the circuit is in the zero state and the Count

operations. Down Clock goes LOW. Since the TC outputs repeat the clock

Each flip-flop contains JK feedback from slave to master waveforms, they can be used as the clock input signals to the

such that a LOW-to-HIGH transition on its T input causes the next higher order circuit in a multistage counter.

slave, and thus the Q output to change state. Synchronous Each circuit has an asynchronous parallel load capability

switching, as opposed to ripple counting, is achieved by permitting the counter to be preset. When the Parallel Load

driving the steering gates of all stages from a common Count (PL) and the Master Reset (MR) inputs are LOW, information

Up line and a common Count Down line, thereby causing all present on the Parallel Data inputs (P0, P3) is loaded into the

state changes to be initiated simultaneously. A LOW-to-HIGH counter and appears on the outputs regardless of the

transition on the Count Up input will advance the count by one; conditions of the clock inputs. A HIGH signal on the Master

a similar transition on the Count Down input will decrease the Reset input will disable the preset gates, override both Clock

count by one. While counting with one clock input, the other inputs, and latch each Q output in the LOW state. If one of the

should be held HIGH. Otherwise, the circuit will either count by Clock inputs is LOW during and after a reset or load operation,

twos or not at all, depending on the state of the first flip-flop, the next LOW-to-HIGH transition of that Clock will be

which cannot toggle as long as either Clock input is LOW. interpreted as a legitimate signal and will be counted.

MODE SELECT TABLE

MR PL CPU CPD MODE

H X X X Reset (Asyn.)

L L X X Preset (Asyn.)

L H H H No Change

L H H Count Up

L H H Count Down

L = LOW Voltage Level

H = HIGH Voltage Level

X = Don’t Care

= LOW-to-HIGH Clock Transition

FAST AND LS TTL DATA

5-4

SN54/74LS192 • SN54/74LS193

GUARANTEED OPERATING RANGES

Symbol Parameter Min Typ Max Unit

VCC Supply Voltage 54 4.5 5.0 5.5 V

74 4.75 5.0 5.25

TA Operating Ambient Temperature Range 54 – 55 25 125 °C

74 0 25 70

IOH Output Current — High 54, 74 – 0.4 mA

IOL Output Current — Low 54 4.0 mA

74 8.0

DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

Limits

S b l

Symbol P

Parameter Min Typ Max U i

Unit T

Test C

Conditions

di i

Guaranteed Input HIGH Voltage for

VIH Input HIGH Voltage 2.0 V

All Inputs

54 0.7 Guaranteed Input

p LOW Voltage

g for

VIL Input LOW Voltage V

74 0.8 All Inputs

VIK Input Clamp Diode Voltage – 0.65 – 1.5 V VCC = MIN, IIN = – 18 mA

54 2.5 3.5 V VCC = MIN,, IOH = MAX,, VIN = VIH

VOH Output HIGH Voltage

74 2.7 3.5 V or VIL per Truth Table

54, 74 0.25 0.4 V IOL = 4.0 mA VCC = VCC MIN,

VOL Output LOW Voltage VIN = VIL or VIH

74 0.35 0.5 V IOL = 8.0 mA per Truth Table

20 µA VCC = MAX, VIN = 2.7 V

IIH Input HIGH Current

0.1 mA VCC = MAX, VIN = 7.0 V

IIL Input LOW Current – 0.4 mA VCC = MAX, VIN = 0.4 V

IOS Short Circuit Current (Note 1) – 20 – 100 mA VCC = MAX

ICC Power Supply Current 34 mA VCC = MAX

Note 1: Not more than one output should be shorted at a time, nor for more than 1 second.

AC CHARACTERISTICS (TA = 25°C)

Limits

S b l

Symbol P

Parameter Min Typ Max U i

Unit T

Test C

Conditions

di i

fMAX Maximum Clock Frequency 25 32 MHz

tPLH CPU Input to 17 26

ns

tPHL TCU Output 18 24

tPLH CPD Input to 16 24

ns

tPHL TCD Output 15 24 50V

VCC = 5.0

tPLH 27 38 CL = 15 pF

Clock to Q ns

tPHL 30 47

tPLH 24 40

PL to Q ns

tPHL 25 40

tPHL MR Input to Any Output 23 35 ns

FAST AND LS TTL DATA

5-5

SN54/74LS192 • SN54/74LS193

AC SETUP REQUIREMENTS (TA = 25°C)

Limits

S b l

Symbol P

Parameter Min Typ Max U i

Unit T

Test C

Conditions

di i

tW Any Pulse Width 20 ns

ts Data Setup Time 20 ns

VCC = 5

5.0

0V

th Data Hold Time 5.0 ns

trec Recovery Time 40 ns

DEFINITIONS OF TERMS

SETUP TIME (ts) is defined as the minimum time required for tion. A negative HOLD TIME indicates that the correct logic

the correct logic level to be present at the logic input prior to the level may be released prior to the PL transition from

PL transition from LOW-to-HIGH in order to be recognized and LOW-to-HIGH and still be recognized.

transferred to the outputs.

RECOVERY TIME (trec) is defined as the minimum time

HOLD TIME (th) is defined as the minimum time following the required between the end of the reset pulse and the clock

PL transition from LOW-to-HIGH that the logic level must be transition from LOW-to-HIGH in order to recognize and

maintained at the input in order to ensure continued recogni- transfer HIGH data to the Q outputs.

FAST AND LS TTL DATA

5-6

SN54/74LS192 • SN54/74LS193

AC WAVEFORMS

tW

CPU or CPD 1.3 V 1.3 V

tPLH

tPHL

Q 1.3 V 1.3 V

Figure 1

CPU or CPD 1.3 V Pn 1.3 V

tPHL tPLH tPHL tPLH

TCU or TCD 1.3 V Qn 1.3 V

NOTE: PL = LOW

Figure 2 Figure 3

Pn 1.3 V

PL 1.3 V

tw

tW trec

PL 1.3 V

tPLH tPHL CPU or CPD 1.3 V

tPHL

1.3 V

Qn

Q 1.3 V

Figure 4 Figure 5

Pn 1.3 V 1.3 V

th(H) th(L)

ts(H) ts(L) MR 1.3 V

PL 1.3 V

tW trec

CPU or CPD 1.3 V

Qn Q=P Q=P

tPHL

* The shaded areas indicate when the input is permitted Q 1.3 V

* to change for predictable output performance

Figure 6 Figure 7

FAST AND LS TTL DATA

5-7

S-ar putea să vă placă și

- PSoC SD Card ComponentDocument6 paginiPSoC SD Card ComponentAbishek PonrajÎncă nu există evaluări

- S3a New Spindle Driver PDFDocument35 paginiS3a New Spindle Driver PDFHubertvcÎncă nu există evaluări

- (Help - Working in Simulink Environment - Tutorial - (Fuzzy Logic Toolbox™ - ) )Document10 pagini(Help - Working in Simulink Environment - Tutorial - (Fuzzy Logic Toolbox™ - ) )llonllonÎncă nu există evaluări

- Examen en Electronica 3Document7 paginiExamen en Electronica 3Erick MartinezÎncă nu există evaluări

- MKL28ZRM PDFDocument1.401 paginiMKL28ZRM PDFcris del cidÎncă nu există evaluări

- Amity Park: The GameDocument5 paginiAmity Park: The GameJosua No marcyÎncă nu există evaluări

- Analog Communications Lab ManualDocument137 paginiAnalog Communications Lab Manualsiva100% (1)

- Mainboard ESC Model P4M800PRO MDocument29 paginiMainboard ESC Model P4M800PRO MHo Thanh BinhÎncă nu există evaluări

- Final Test 6-1 Grammar, Vocabulary, Reading, Listening and WritingDocument3 paginiFinal Test 6-1 Grammar, Vocabulary, Reading, Listening and WritingosamyyÎncă nu există evaluări

- Ecs D1f-Ad Rev 1.0Document30 paginiEcs D1f-Ad Rev 1.0Yenco Barliza Diaz0% (1)

- SN74LS193Document11 paginiSN74LS193HeartBraveÎncă nu există evaluări

- 74LS190Document8 pagini74LS190jaja558Încă nu există evaluări

- 74LS192Document9 pagini74LS192jaja558Încă nu există evaluări

- Onsms12244 1Document8 paginiOnsms12244 1HeartBraveÎncă nu există evaluări

- SN54/74LS160A SN54/74LS161A SN54/74LS162A SN54/74LS163A: Low Power SchottkyDocument5 paginiSN54/74LS160A SN54/74LS161A SN54/74LS162A SN54/74LS163A: Low Power Schottkygd8uj123Încă nu există evaluări

- 74ls163 DatasheetDocument6 pagini74ls163 DatasheetFernando LMÎncă nu există evaluări

- SN74LS175 Quad D Flip-Flop: LOW Power SchottkyDocument8 paginiSN74LS175 Quad D Flip-Flop: LOW Power SchottkyDita RanantaÎncă nu există evaluări

- 74LS161-3Document6 pagini74LS161-3Mohammd EssaÎncă nu există evaluări

- Presettable BCD/Decade and Binary Up/Down CountersDocument10 paginiPresettable BCD/Decade and Binary Up/Down CountersnukachÎncă nu există evaluări

- 4 X 4 Register File Open-Collector SN54/74LS170: Low Power SchottkyDocument4 pagini4 X 4 Register File Open-Collector SN54/74LS170: Low Power SchottkyEden K.CÎncă nu există evaluări

- 74LS290Document7 pagini74LS290jaja558Încă nu există evaluări

- 74LS174Document3 pagini74LS174jaja558Încă nu există evaluări

- Datasheet Ic 74hc165aDocument9 paginiDatasheet Ic 74hc165aNayla AzzahraÎncă nu există evaluări

- 74LS164Document4 pagini74LS164jaja558Încă nu există evaluări

- Synchronous 4-Bit Binary CounterDocument17 paginiSynchronous 4-Bit Binary Counteryogendra.shethÎncă nu există evaluări

- 74LS173Document4 pagini74LS173jaja558Încă nu există evaluări

- D D D D D D D D D D D: Description/ordering InformationDocument16 paginiD D D D D D D D D D D: Description/ordering InformationJay rayÎncă nu există evaluări

- MC74HC161A MotorolaDocument12 paginiMC74HC161A MotorolaMed SamiÎncă nu există evaluări

- SN54/74LS669 4-BIT UP/DOWN COUNTERDocument4 paginiSN54/74LS669 4-BIT UP/DOWN COUNTERzequinhawins100% (1)

- SN54/74LS194A 4-bit bidirectional universal shift registerDocument4 paginiSN54/74LS194A 4-bit bidirectional universal shift registerwolfstarprojectsÎncă nu există evaluări

- 74LS155Document4 pagini74LS155jaja558Încă nu există evaluări

- 74LS375Document3 pagini74LS375jaja558Încă nu există evaluări

- 74LS47Document3 pagini74LS47jaja558Încă nu există evaluări

- 74 Ls 47Document3 pagini74 Ls 47Joelo D' CartonÎncă nu există evaluări

- D D D D: SN54165, SN54LS165A, SN74165, SN74LS165A Parallel-Load 8-Bit Shift RegistersDocument23 paginiD D D D: SN54165, SN54LS165A, SN74165, SN74LS165A Parallel-Load 8-Bit Shift RegistersВиктор АгарковÎncă nu există evaluări

- Sn74ls165a PDFDocument16 paginiSn74ls165a PDFRachid RifaiÎncă nu există evaluări

- Decodificador Sn74ls139rev6Document8 paginiDecodificador Sn74ls139rev6Fran GómezÎncă nu există evaluări

- SN54ALS169B, SN54AS169A, SN74ALS169B, SN74AS169A Synchronous 4-Bit Up/Down Binary CountersDocument9 paginiSN54ALS169B, SN54AS169A, SN74ALS169B, SN74AS169A Synchronous 4-Bit Up/Down Binary CountersGregorito Torrejano MunevarÎncă nu există evaluări

- M54/M74HC190 M54/M74HC191: 4 Bit Synchronous Up/Down CountersDocument14 paginiM54/M74HC190 M54/M74HC191: 4 Bit Synchronous Up/Down Countersroshan kumarÎncă nu există evaluări

- High-Performance Silicon-Gate CMOS: Semiconductor Technical DataDocument8 paginiHigh-Performance Silicon-Gate CMOS: Semiconductor Technical DataMario ArámbulaÎncă nu există evaluări

- D D D D D D D D D D D D: TLV5618A 2.7-V TO 5.5-V LOW-POWER DUAL 12-BIT Digital-To-Analog Converter With Power DownDocument23 paginiD D D D D D D D D D D D: TLV5618A 2.7-V TO 5.5-V LOW-POWER DUAL 12-BIT Digital-To-Analog Converter With Power DownJulio Rafael GamboaÎncă nu există evaluări

- Power Switching Regulators: Semiconductor Technical DataDocument16 paginiPower Switching Regulators: Semiconductor Technical DataAkramÎncă nu există evaluări

- AK4384 AsahiKaseiMicrosystemsDocument24 paginiAK4384 AsahiKaseiMicrosystemstaninavcoÎncă nu există evaluări

- TLC 1514Document40 paginiTLC 1514Hoii ClarkÎncă nu există evaluări

- 45D011_ATMELDocument21 pagini45D011_ATMELkami samaÎncă nu există evaluări

- MC14553B 3-Digit BCD Counter: PDIP-16 P Suffix CASE 648Document12 paginiMC14553B 3-Digit BCD Counter: PDIP-16 P Suffix CASE 648suriantoÎncă nu există evaluări

- 45DB011Document19 pagini45DB011mohamed saadaÎncă nu există evaluări

- D D D D D D D: SN54HC574, SN74HC574 Octal Edge-Triggered D-Type Flip-Flops With 3-State OutputsDocument25 paginiD D D D D D D: SN54HC574, SN74HC574 Octal Edge-Triggered D-Type Flip-Flops With 3-State OutputsДрагиша Небитни ТрифуновићÎncă nu există evaluări

- SG3526Document11 paginiSG3526RocioLLactaMartinezÎncă nu există evaluări

- Samsung DVD Mini Component Max-945dDocument70 paginiSamsung DVD Mini Component Max-945dRicardo CardenasÎncă nu există evaluări

- SN5474LS95B 4-Bit Shift RegisterDocument6 paginiSN5474LS95B 4-Bit Shift RegisterhayssamÎncă nu există evaluări

- AK4384 DAC DatasheetDocument24 paginiAK4384 DAC Datasheetchuma_riescoÎncă nu există evaluări

- Reference Information: (DVD Part) 1-1 IC DsecriptionsDocument14 paginiReference Information: (DVD Part) 1-1 IC Dsecriptionsjose peresÎncă nu există evaluări

- MC14489DW PDFDocument21 paginiMC14489DW PDFИван АлексиевÎncă nu există evaluări

- IP4003 4-Ch Motor Drive Ic: DescriptionsDocument21 paginiIP4003 4-Ch Motor Drive Ic: DescriptionsvetchboyÎncă nu există evaluări

- 128-Megabit 2.7-Volt Dual-Interface Dataflash At45Db1282 PreliminaryDocument35 pagini128-Megabit 2.7-Volt Dual-Interface Dataflash At45Db1282 PreliminarymhasansharifiÎncă nu există evaluări

- AD5620 AnalogDevicesDocument28 paginiAD5620 AnalogDevicesPablo AllosiaÎncă nu există evaluări

- 74LS153 PDFDocument3 pagini74LS153 PDFdzul hidayatÎncă nu există evaluări

- Order SG3525A/D PWM controllerDocument8 paginiOrder SG3525A/D PWM controllerMaxÎncă nu există evaluări

- TB6564AHQ (THB6064AH) : PWM Chopper-Type Bipolar Stepping Motor Driver ICDocument39 paginiTB6564AHQ (THB6064AH) : PWM Chopper-Type Bipolar Stepping Motor Driver ICTran Duc IOTÎncă nu există evaluări

- Chapter 12 - LCD and KeyboardDocument27 paginiChapter 12 - LCD and KeyboardAnkit KumarÎncă nu există evaluări

- PACSystems RX3i Mid-Range Controller FeaturesDocument53 paginiPACSystems RX3i Mid-Range Controller FeaturesRenan LouzadaÎncă nu există evaluări

- Ade XL User GuideDocument2 paginiAde XL User GuideFaiq Khalid LodhiÎncă nu există evaluări

- Accenture - Sustaining Success in The Digital Era - The New Challenge For CableDocument16 paginiAccenture - Sustaining Success in The Digital Era - The New Challenge For CableAndrey PritulyukÎncă nu există evaluări

- Alternador Delco RemyDocument1 paginăAlternador Delco RemyJuan Carlos SoHeÎncă nu există evaluări

- MADYA COMPUTER SERVICE CENTER OFFERS LAPTOPS, PCs AND MOREDocument2 paginiMADYA COMPUTER SERVICE CENTER OFFERS LAPTOPS, PCs AND MOREcl3o.frÎncă nu există evaluări

- Ec342 - Electromagnetic Waves and Wave GuidesDocument3 paginiEc342 - Electromagnetic Waves and Wave GuidessubhazÎncă nu există evaluări

- DSP Chapter 4 Sampling of Continuous-time SignalsDocument29 paginiDSP Chapter 4 Sampling of Continuous-time SignalsShah HussainÎncă nu există evaluări

- EBT435 Polymer in Electronic Applications: Plteh@unimap - Edu.myDocument21 paginiEBT435 Polymer in Electronic Applications: Plteh@unimap - Edu.myTarani TharanÎncă nu există evaluări

- Instruction Manual: CT10X Barcode ScannerDocument75 paginiInstruction Manual: CT10X Barcode ScannerLuis Y.M.Încă nu există evaluări

- EDA Companies and Tools GuideDocument9 paginiEDA Companies and Tools GuideLaxmanaa GajendiranÎncă nu există evaluări

- SBGR Ils-T-Rwy-28r Iac 20220908Document1 paginăSBGR Ils-T-Rwy-28r Iac 20220908jcndrckz4qÎncă nu există evaluări

- 12 Com123n TXDocument7 pagini12 Com123n TXCauVong JustinÎncă nu există evaluări

- PS01509 LoRaWAN AT Command SpecificationDocument46 paginiPS01509 LoRaWAN AT Command SpecificationleonardoÎncă nu există evaluări

- City". We Implemented Using PIC Microcontroller and RF ModuleDocument56 paginiCity". We Implemented Using PIC Microcontroller and RF ModuleSai RakeshÎncă nu există evaluări

- SyncServer-S200-Enterprise Class GPS Network Time ServerDocument2 paginiSyncServer-S200-Enterprise Class GPS Network Time ServersandmanpayneÎncă nu există evaluări

- Pruef Messtechnik en PDFDocument40 paginiPruef Messtechnik en PDFFCO ANTONIO CHACONÎncă nu există evaluări

- HP ELITEBOOK 8740W Inventec Armani 6050A2266501Document61 paginiHP ELITEBOOK 8740W Inventec Armani 6050A2266501Gerardo Mediabilla0% (2)

- Am Monitors Headphones12Document40 paginiAm Monitors Headphones12dejan89npÎncă nu există evaluări

- Rohit Arora Specimen FileDocument5 paginiRohit Arora Specimen FileHimesh JainÎncă nu există evaluări

- Interruptor Digital Schneider Ihp PDFDocument2 paginiInterruptor Digital Schneider Ihp PDFMiguel MontalvánÎncă nu există evaluări

- CB1 Panelboard #1 (Front) : Voltage Maximum Amp Rating Per Input Terminal BlockDocument5 paginiCB1 Panelboard #1 (Front) : Voltage Maximum Amp Rating Per Input Terminal Blockjoseph mendezÎncă nu există evaluări

- High Efficiency 10A Synchronous Buck Converter: Features General DescriptionDocument1 paginăHigh Efficiency 10A Synchronous Buck Converter: Features General Descriptionmohd nasirÎncă nu există evaluări

- ABB OVR Recloser and PCD Training - Rev FDocument13 paginiABB OVR Recloser and PCD Training - Rev FChristianM.LeandroYauriÎncă nu există evaluări

- Ty Rcub20 (v4)Document1 paginăTy Rcub20 (v4)YarinaÎncă nu există evaluări

- Sucursal Colón Quito Sucursal Sur Quito Centro de Servicios Técnicos Sucursal Mayor Guayaquil Sucursal Sur Guayaquil Principal QuitoDocument6 paginiSucursal Colón Quito Sucursal Sur Quito Centro de Servicios Técnicos Sucursal Mayor Guayaquil Sucursal Sur Guayaquil Principal QuitoTamara SuconotaÎncă nu există evaluări

- Zigbee Based Car Security SystemDocument23 paginiZigbee Based Car Security SystemvijitizerÎncă nu există evaluări

- Novatek nt96655 Data SheetDocument56 paginiNovatek nt96655 Data Sheetapi-432313169Încă nu există evaluări

- Circuit Fundamentals and Basic Electronics: Z R J Z J ZDocument4 paginiCircuit Fundamentals and Basic Electronics: Z R J Z J ZTarun JoshiÎncă nu există evaluări

- Eddy Current Testing Technology - 2nd Edition - Sample PDFDocument22 paginiEddy Current Testing Technology - 2nd Edition - Sample PDFParanthaman Jayaraman100% (1)