Documente Academic

Documente Profesional

Documente Cultură

Lect11 Seq

Încărcat de

kaushik_gupta_4Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Lect11 Seq

Încărcat de

kaushik_gupta_4Drepturi de autor:

Formate disponibile

Lecture 11:

Sequential

Circuit

Design

CMOS VLSI Design CMOS VLSI Design

4th Ed.

11: Sequential Circuits 2

Outline

Sequencing

Sequencing Element Design

Max and Min-Delay

Clock Skew

Time Borrowing

Two-Phase Clocking

CMOS VLSI Design CMOS VLSI Design

4th Ed.

11: Sequential Circuits 3

Sequencing

Combinational logic

output depends on current inputs

Sequential logic

output depends on current and previous inputs

Requires separating previous, current, future

Called state or tokens

Ex: FSM, pipeline

CL

clk

in out

clk clk clk

CL CL

Pipeline Finite State Machine

CMOS VLSI Design CMOS VLSI Design

4th Ed.

11: Sequential Circuits 4

Sequencing Cont.

If tokens moved through pipeline at constant speed,

no sequencing elements would be necessary

Ex: fiber-optic cable

Light pulses (tokens) are sent down cable

Next pulse sent before first reaches end of cable

No need for hardware to separate pulses

But dispersion sets min time between pulses

This is called wave pipelining in circuits

In most circuits, dispersion is high

Delay fast tokens so they dont catch slow ones.

CMOS VLSI Design CMOS VLSI Design

4th Ed.

11: Sequential Circuits 5

Sequencing Overhead

Use flip-flops to delay fast tokens so they move

through exactly one stage each cycle.

Inevitably adds some delay to the slow tokens

Makes circuit slower than just the logic delay

Called sequencing overhead

Some people call this clocking overhead

But it applies to asynchronous circuits too

Inevitable side effect of maintaining sequence

CMOS VLSI Design CMOS VLSI Design

4th Ed.

11: Sequential Circuits 6

Sequencing Elements

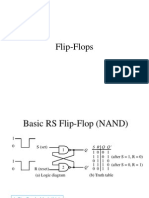

Latch: Level sensitive

a.k.a. transparent latch, D latch

Flip-flop: edge triggered

A.k.a. master-slave flip-flop, D flip-flop, D register

Timing Diagrams

Transparent

Opaque

Edge-trigger

D

F

l

o

p

L

a

t

c

h

Q

clk clk

D Q

clk

D

Q (latch)

Q (flop)

D

F

l

o

p

L

a

t

c

h

Q

clk clk

D Q

clk

D

Q (latch)

Q (flop)

CMOS VLSI Design CMOS VLSI Design

4th Ed.

11: Sequential Circuits 7

Latch Design

Pass Transistor Latch

Pros

+ Tiny

+ Low clock load

Cons

V

t

drop

nonrestoring

backdriving

output noise sensitivity

dynamic

diffusion input

D Q

|

Used in 1970s

CMOS VLSI Design CMOS VLSI Design

4th Ed.

11: Sequential Circuits 8

Latch Design

Transmission gate

+ No V

t

drop

- Requires inverted clock D Q

|

|

CMOS VLSI Design CMOS VLSI Design

4th Ed.

11: Sequential Circuits 9

Latch Design

Inverting buffer

+ Restoring

+ No backdriving

+ Fixes either

Output noise sensitivity

Or diffusion input

Inverted output

D

|

|

X

Q

D Q

|

|

CMOS VLSI Design CMOS VLSI Design

4th Ed.

11: Sequential Circuits 10

Latch Design

Tristate feedback

+ Static

Backdriving risk

Static latches are now essential

because of leakage

|

|

|

|

Q D

X

CMOS VLSI Design CMOS VLSI Design

4th Ed.

11: Sequential Circuits 11

Latch Design

Buffered input

+ Fixes diffusion input

+ Noninverting

|

|

Q D

X

|

|

CMOS VLSI Design CMOS VLSI Design

4th Ed.

11: Sequential Circuits 12

Latch Design

Buffered output

+ No backdriving

Widely used in standard cells

+ Very robust (most important)

- Rather large

- Rather slow (1.5 2 FO4 delays)

- High clock loading

|

|

Q

D

X

|

|

CMOS VLSI Design CMOS VLSI Design

4th Ed.

11: Sequential Circuits 13

Latch Design

Datapath latch

+ smaller

+ faster

- unbuffered input

|

|

|

|

Q

D

X

CMOS VLSI Design CMOS VLSI Design

4th Ed.

11: Sequential Circuits 14

Flip-Flop Design

Flip-flop is built as pair of back-to-back latches

D Q

|

|

|

|

X

D

|

|

|

|

X

Q

Q

|

|

|

|

CMOS VLSI Design CMOS VLSI Design

4th Ed.

11: Sequential Circuits 15

Enable

Enable: ignore clock when en = 0

Mux: increase latch D-Q delay

Clock Gating: increase en setup time, skew

D Q

L

a

t

c

h

D Q

en

en

|

|

L

a

t

c

h

D

Q

|

0

1

en

L

a

t

c

h

D Q

| en

D

Q

|

0

1

en

D Q

| en

F

l

o

p

F

l

o

p

F

l

o

p

Symbol Multiplexer Design Clock Gating Design

CMOS VLSI Design CMOS VLSI Design

4th Ed.

11: Sequential Circuits 16

Reset

Force output low when reset asserted

Synchronous vs. asynchronous

D

|

|

|

|

Q

Q

|

|

|

|

reset

D

|

|

|

|

|

|

Q

|

|

D

reset

|

|

Q

|

|

D

reset

reset

|

|

reset

S

y

n

c

h

r

o

n

o

u

s

R

e

s

e

t

A

s

y

n

c

h

r

o

n

o

u

s

R

e

s

e

t

S

y

m

b

o

l F

l

o

p

D Q

L

a

t

c

h

D Q

reset reset

| |

|

|

Q

reset

CMOS VLSI Design CMOS VLSI Design

4th Ed.

11: Sequential Circuits 17

Set / Reset

Set forces output high when enabled

Flip-flop with asynchronous set and reset

D

|

|

|

|

|

|

Q

|

|

reset

set

reset

set

CMOS VLSI Design CMOS VLSI Design

4th Ed.

11: Sequential Circuits 18

Sequencing Methods

Flip-flops

2-Phase Latches

Pulsed Latches

F

l

i

p

-

F

l

o

p

s

F

l

o

p

L

a

t

c

h

F

l

o

p

clk

|

1

|

2

|

p

clk clk

L

a

t

c

h

L

a

t

c

h

|

p

|

p

|

1

|

1

|

2

2

-

P

h

a

s

e

T

r

a

n

s

p

a

r

e

n

t

L

a

t

c

h

e

s

P

u

l

s

e

d

L

a

t

c

h

e

s

Combinational Logic

Combinational

Logic

Combinational

Logic

Combinational Logic

L

a

t

c

h

L

a

t

c

h

T

c

T

c

/2

t

nonoverlap

t

nonoverlap

t

pw

Half-Cycle 1 Half-Cycle 1

CMOS VLSI Design CMOS VLSI Design

4th Ed.

11: Sequential Circuits 19

Timing Diagrams

F

l

o

p

A

Y

t

pd

Combinational

Logic

A Y

D Q

clk

clk

D

Q

L

a

t

c

h

D Q

clk

clk

D

Q

t

cd

t

setup

t

hold

t

ccq

t

pcq

t

ccq

t

setup

t

hold

t

pcq

t

pdq

t

cdq

t

pd

Logic Prop. Delay

t

cd

Logic Cont. Delay

t

pcq

Latch/Flop Clk->Q Prop. Delay

t

ccq

Latch/Flop Clk->Q Cont. Delay

t

pdq

Latch D->Q Prop. Delay

t

cdq

Latch D->Q Cont. Delay

t

setup

Latch/Flop Setup Time

t

hold

Latch/Flop Hold Time

Contamination and

Propagation Delays

CMOS VLSI Design CMOS VLSI Design

4th Ed.

11: Sequential Circuits 20

Max-Delay: Flip-Flops

F

1

F

2

clk

clk clk

Combinational Logic

T

c

Q1 D2

Q1

D2

t

pd

t

setup

t

pcq

( )

setup

sequencing overhead

pd c pcq

t T t t s +

CMOS VLSI Design CMOS VLSI Design

4th Ed.

11: Sequential Circuits 21

Max Delay: 2-Phase Latches

T

c

Q1

L

1

|

1

|

2

L

2

L

3

|

1

|

1

|

2

Combinational

Logic 1

Combinational

Logic 2

Q2 Q3 D1 D2 D3

Q1

D2

Q2

D3

D1

t

pd1

t

pdq1

t

pd2

t

pdq2

( )

1 2

sequencing overhead

2

pd pd pd c pdq

t t t T t = + s

CMOS VLSI Design CMOS VLSI Design

4th Ed.

11: Sequential Circuits 22

Max Delay: Pulsed Latches

T

c

Q1 Q2 D1 D2

Q1

D2

D1

|

p

|

p

|

p

Combinational Logic

L

1

L

2

t

pw

(a) t

pw

> t

setup

Q1

D2

(b) t

pw

< t

setup

T

c

t

pd

t

pdq

t

pcq

t

pd

t

setup

( )

setup

sequencing overhead

max ,

pd c pdq pcq pw

t T t t t t s +

CMOS VLSI Design CMOS VLSI Design

4th Ed.

11: Sequential Circuits 23

Min-Delay: Flip-Flops

hold cd ccq

t t t >

CL

clk

Q1

D2

F

1

clk

Q1

F

2

clk

D2

t

cd

t

hold

t

ccq

CMOS VLSI Design CMOS VLSI Design

4th Ed.

11: Sequential Circuits 24

Min-Delay: 2-Phase Latches

1, 2 hold nonoverlap cd cd ccq

t t t t t >

CL

Q1

D2

D2

Q1

|

1

L

1

|

2

L

2

|

1

|

2

t

nonoverlap

t

cd

t

hold

t

ccq

Hold time reduced by

nonoverlap

Paradox: hold applies

twice each cycle, vs.

only once for flops.

But a flop is made of

two latches!

CMOS VLSI Design CMOS VLSI Design

4th Ed.

11: Sequential Circuits 25

Min-Delay: Pulsed Latches

hold cd ccq pw

t t t t > +

CL

Q1

D2

Q1

D2

|

p

t

pw

|

p

L

1

|

p

L

2

t

cd

t

hold

t

ccq

Hold time increased

by pulse width

CMOS VLSI Design CMOS VLSI Design

4th Ed.

11: Sequential Circuits 26

Time Borrowing

In a flop-based system:

Data launches on one rising edge

Must setup before next rising edge

If it arrives late, system fails

If it arrives early, time is wasted

Flops have hard edges

In a latch-based system

Data can pass through latch while transparent

Long cycle of logic can borrow time into next

As long as each loop completes in one cycle

CMOS VLSI Design CMOS VLSI Design

4th Ed.

11: Sequential Circuits 27

Time Borrowing Example

L

a

t

c

h

L

a

t

c

h

L

a

t

c

h

Combinational Logic

Combinational

Logic

Borrowing time across

half-cycle boundary

Borrowing time across

pipeline stage boundary

(a)

(b)

L

a

t

c

h

L

a

t

c

h

Combinational Logic

Combinational

Logic

Loops may borrow time internally but must complete within the cycle

|

1

|

2

|

1

|

1

|

1

|

2

|

2

CMOS VLSI Design CMOS VLSI Design

4th Ed.

11: Sequential Circuits 28

How Much Borrowing?

Q1

L

1

|

1

|

2

L

2

|

1

|

2

Combinational Logic 1

Q2 D1 D2

D2

T

c

T

c

/2

Nominal Half-Cycle 1 Delay

t

borrow

t

nonoverlap

t

setup

( )

borrow setup nonoverlap

2

c

T

t t t s +

2-Phase Latches

borrow setup pw

t t t s

Pulsed Latches

CMOS VLSI Design CMOS VLSI Design

4th Ed.

11: Sequential Circuits 29

Clock Skew

We have assumed zero clock skew

Clocks really have uncertainty in arrival time

Decreases maximum propagation delay

Increases minimum contamination delay

Decreases time borrowing

CMOS VLSI Design CMOS VLSI Design

4th Ed.

11: Sequential Circuits 30

Skew: Flip-Flops

F

1

F

2

clk

clk clk

Combinational Logic

T

c

Q1 D2

Q1

D2

t

skew

CL

Q1

D2

F

1

clk

Q1

F

2

clk

D2

clk

t

skew

t

setup

t

pcq

t

pdq

t

cd

t

hold

t

ccq

( )

setup skew

sequencing overhead

hold skew

pd c pcq

cd ccq

t T t t t

t t t t

s + +

> +

CMOS VLSI Design CMOS VLSI Design

4th Ed.

11: Sequential Circuits 31

Skew: Latches

Q1

L

1

|

1

|

2

L

2

L

3

|

1

|

1

|

2

Combinational

Logic 1

Combinational

Logic 2

Q2 Q3 D1 D2 D3

( )

( )

sequencing overhead

1 2 hold nonoverlap skew

borrow setup nonoverlap skew

2

,

2

pd c pdq

cd cd ccq

c

t T t

t t t t t t

T

t t t t

s

> +

s + +

2-Phase Latches

( )

( )

setup skew

sequencing overhead

hold skew

borrow setup skew

max ,

pd c pdq pcq pw

cd pw ccq

pw

t T t t t t t

t t t t t

t t t t

s + +

> + +

s +

Pulsed Latches

CMOS VLSI Design CMOS VLSI Design

4th Ed.

11: Sequential Circuits 32

Two-Phase Clocking

If setup times are violated, reduce clock speed

If hold times are violated, chip fails at any speed

In this class, working chips are most important

No tools to analyze clock skew

An easy way to guarantee hold times is to use 2-

phase latches with big nonoverlap times

Call these clocks |

1

, |

2

(ph1, ph2)

CMOS VLSI Design CMOS VLSI Design

4th Ed.

11: Sequential Circuits 33

Safe Flip-Flop

Past years used flip-flop with nonoverlapping clocks

Slow nonoverlap adds to setup time

But no hold times

In industry, use a better timing analyzer

Add buffers to slow signals if hold time is at risk

D

|

2

X

Q

Q

|

1

|

2

|

1

|

1

|

1

|

2

|

2

CMOS VLSI Design CMOS VLSI Design

4th Ed.

11: Sequential Circuits 34

Adaptive Sequencing

Designers include timing margin

Voltage

Temperature

Process variation

Data dependency

Tool inaccuracies

Alternative: run faster and check for near failures

Idea introduced as Razor

Increase frequency until at the verge of error

Can reduce cycle time by ~30%

D Q

ERR

|

p

|

p

D

Q

X

ERR

X

CMOS VLSI Design CMOS VLSI Design

4th Ed.

11: Sequential Circuits 35

Summary

Flip-Flops:

Very easy to use, supported by all tools

2-Phase Transparent Latches:

Lots of skew tolerance and time borrowing

Pulsed Latches:

Fast, some skew tol & borrow, hold time risk

S-ar putea să vă placă și

- WAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksDe la EverandWAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksÎncă nu există evaluări

- Lect11 SeqDocument35 paginiLect11 Seqs.b.v.seshagiri1407Încă nu există evaluări

- Introduction To Cmos Vlsi Design: Sequential CircuitsDocument48 paginiIntroduction To Cmos Vlsi Design: Sequential CircuitsGaurang ChaudhariÎncă nu există evaluări

- Microprocessor System Design: A Practical IntroductionDe la EverandMicroprocessor System Design: A Practical IntroductionÎncă nu există evaluări

- Skew DesignDocument29 paginiSkew DesignAshok KoyyalamudiÎncă nu există evaluări

- CPE/EE 427, CPE 527 VLSI Design I Sequential Circuits: - Combinational Logic - Sequential LogicDocument25 paginiCPE/EE 427, CPE 527 VLSI Design I Sequential Circuits: - Combinational Logic - Sequential LogicKamal Kumar Kalra0% (1)

- CMOS Sequential Circuit Design Lec.-1Document22 paginiCMOS Sequential Circuit Design Lec.-1Parag ParandkarÎncă nu există evaluări

- Sub-System Design 5Document177 paginiSub-System Design 5Abdullah Gubbi100% (1)

- VLSI Chapter01b Circui&layout PDFDocument48 paginiVLSI Chapter01b Circui&layout PDFJay SharmaÎncă nu există evaluări

- Appendix PowerDocument29 paginiAppendix PowerPham VietÎncă nu există evaluări

- Introduction To Cmos Vlsi Design: Circuits & LayoutDocument47 paginiIntroduction To Cmos Vlsi Design: Circuits & Layoutnehanice123_68509352Încă nu există evaluări

- Lecture27 - Flip Flops: Jagannadha Naidu KDocument0 paginiLecture27 - Flip Flops: Jagannadha Naidu Khim92Încă nu există evaluări

- Lect17 SeqDocument18 paginiLect17 SeqorengeneralÎncă nu există evaluări

- Lect 0Document56 paginiLect 0darshan_077Încă nu există evaluări

- Lect11 SeqDocument35 paginiLect11 SeqHOD ECE SSCETÎncă nu există evaluări

- CMOS Logic StructuresDocument23 paginiCMOS Logic StructuressuprabhuÎncă nu există evaluări

- Introduction To Cmos Vlsi Design: Circuits & LayoutDocument47 paginiIntroduction To Cmos Vlsi Design: Circuits & LayoutmlwececehodÎncă nu există evaluări

- Sequential Circuit DesignDocument35 paginiSequential Circuit DesignArun AvÎncă nu există evaluări

- Introduction To Cmos Vlsi Design: Circuits & LayoutDocument54 paginiIntroduction To Cmos Vlsi Design: Circuits & LayoutKalai OmprakashÎncă nu există evaluări

- Debugging Clock Trees Will Now Be Easier: Cadence Cdnlive! 2007 Emea Conference in MunichDocument22 paginiDebugging Clock Trees Will Now Be Easier: Cadence Cdnlive! 2007 Emea Conference in MunichSandeep PatilÎncă nu există evaluări

- Two Phase Non-Overlapping Clock DriverDocument9 paginiTwo Phase Non-Overlapping Clock DriverVictor ChangÎncă nu există evaluări

- CH 04 Delay Part 01Document25 paginiCH 04 Delay Part 01muneeb.abrarÎncă nu există evaluări

- Debugging Clock Trees Will Now Be Easier: Cadence Cdnlive! 2007 Emea Conference in MunichDocument22 paginiDebugging Clock Trees Will Now Be Easier: Cadence Cdnlive! 2007 Emea Conference in MunichSumanth VarmaÎncă nu există evaluări

- Static Timing Analysis Static Timing AnalysisDocument49 paginiStatic Timing Analysis Static Timing AnalysisRajesh DurisalaÎncă nu există evaluări

- CS 211: Computer Architecture: Instructor: Prof. Bhagi NarahariDocument82 paginiCS 211: Computer Architecture: Instructor: Prof. Bhagi NarahariElizabeth AliazÎncă nu există evaluări

- Clocking MITDocument16 paginiClocking MITkumarguptav91Încă nu există evaluări

- Lecture 17Document31 paginiLecture 17KoteswaraRaoBÎncă nu există evaluări

- Design For TestabilityDocument26 paginiDesign For TestabilityDenise NelsonÎncă nu există evaluări

- Plls and DllsDocument21 paginiPlls and DllsmihaiM500Încă nu există evaluări

- Zipper Cmos Logic CircuitDocument15 paginiZipper Cmos Logic CircuitShreerama Samartha G BhattaÎncă nu există evaluări

- Introduction To Cmos Vlsi DesignDocument40 paginiIntroduction To Cmos Vlsi DesignAdiseshuMiddeÎncă nu există evaluări

- Introduction To Cmos Vlsi DesignDocument40 paginiIntroduction To Cmos Vlsi Designmniyas_1Încă nu există evaluări

- Clocking Part 2Document4 paginiClocking Part 2Dmitry LeyzerovichÎncă nu există evaluări

- Sequential Circuits 2Document12 paginiSequential Circuits 2Hari DharanÎncă nu există evaluări

- 5.2 CMOS Logic Gate Design: Serial or Parallel in Rs Transisto of NoDocument15 pagini5.2 CMOS Logic Gate Design: Serial or Parallel in Rs Transisto of NoRaj AryanÎncă nu există evaluări

- Ca2 FastAddersDocument29 paginiCa2 FastAddersBala BeliveÎncă nu există evaluări

- Timing Issues in FPGA Synchronous Circuit Design: ECE 428 Programmable ASIC DesignDocument33 paginiTiming Issues in FPGA Synchronous Circuit Design: ECE 428 Programmable ASIC DesignVarun KondagunturiÎncă nu există evaluări

- Chapter 7Document60 paginiChapter 7Sunil KumarÎncă nu există evaluări

- 6.xi Constraints 1762Document187 pagini6.xi Constraints 1762Khubaib AhmedÎncă nu există evaluări

- Lecture10 Layout FabricationDocument60 paginiLecture10 Layout Fabricationbkvuvce8170Încă nu există evaluări

- Avoiding Metastability in FPGA Devices: David Landoll Applications Architect Mentor Graphics CorpDocument32 paginiAvoiding Metastability in FPGA Devices: David Landoll Applications Architect Mentor Graphics CorpPooja KhareÎncă nu există evaluări

- Sequential LogicDocument68 paginiSequential LogicbabahussainÎncă nu există evaluări

- Vlsi TechnologyDocument60 paginiVlsi TechnologyPrasad NagavaraÎncă nu există evaluări

- Nanomap: An Integrated Design Optimization Flow For A Hybrid Nanotube/Cmos Dynamically Reconfigurable ArchitectureDocument27 paginiNanomap: An Integrated Design Optimization Flow For A Hybrid Nanotube/Cmos Dynamically Reconfigurable Architectureசக்தி இலக்கியா சத்தீஸ்வரன்Încă nu există evaluări

- Digital Design Gta Esg: - Sequential CircuitDocument34 paginiDigital Design Gta Esg: - Sequential CircuitCeyhan İleriÎncă nu există evaluări

- Data Path Design (Adder and Multiplier)Document76 paginiData Path Design (Adder and Multiplier)Karthik RamasamyÎncă nu există evaluări

- Delay in VLSIDocument27 paginiDelay in VLSIlevan100% (1)

- Digital Design and System Implementation Overview of Physical ImplementationsDocument4 paginiDigital Design and System Implementation Overview of Physical ImplementationsGuganesan PerumalÎncă nu există evaluări

- References: (Used For Creation of The Presentation Material)Document35 paginiReferences: (Used For Creation of The Presentation Material)Kumar BsnspÎncă nu există evaluări

- VLSI: Design FlowDocument37 paginiVLSI: Design FlowCGÎncă nu există evaluări

- Timing Closure Today: Lou Scheffer Cadence San Jose, CADocument104 paginiTiming Closure Today: Lou Scheffer Cadence San Jose, CASuhas ShirolÎncă nu există evaluări

- Chapter #10: Finite State Machine ImplementationDocument32 paginiChapter #10: Finite State Machine Implementationphani_abkÎncă nu există evaluări

- VLSI Design: Circuits & LayoutDocument48 paginiVLSI Design: Circuits & LayoutVel Murugan KTÎncă nu există evaluări

- Finite State Machine Implementation: Prith Banerjee Ece C03 Advanced Digital Design Spring 1998Document31 paginiFinite State Machine Implementation: Prith Banerjee Ece C03 Advanced Digital Design Spring 1998Sai PrashanthÎncă nu există evaluări

- Chapter 6 Soc EncounterDocument222 paginiChapter 6 Soc EncounterSumanth VarmaÎncă nu există evaluări

- Introduction To Cmos Vlsi Design: Circuit FamiliesDocument34 paginiIntroduction To Cmos Vlsi Design: Circuit FamiliesManjula G RayÎncă nu există evaluări

- Flip FlopsDocument25 paginiFlip FlopsNagul MeeraÎncă nu există evaluări

- 11 Clock SkewDocument35 pagini11 Clock SkewMaheshÎncă nu există evaluări

- VLSI Design I VLSI Design I VLSI Design I VLSI Design IDocument23 paginiVLSI Design I VLSI Design I VLSI Design I VLSI Design ISaksham sangwanÎncă nu există evaluări

- Reliability Analysis and Optimization of Power-Gated IcsDocument12 paginiReliability Analysis and Optimization of Power-Gated Icskaushik_gupta_4Încă nu există evaluări

- Mtech 2 SemDocument6 paginiMtech 2 Semkaushik_gupta_4Încă nu există evaluări

- Accurate Current Estimation For Interconnect Reliability AnalysisDocument11 paginiAccurate Current Estimation For Interconnect Reliability Analysiskaushik_gupta_4Încă nu există evaluări

- M Tech Vlsi SyllabusDocument29 paginiM Tech Vlsi Syllabuskaushik_gupta_4100% (1)

- DFTDocument13 paginiDFTGeethanjali RajegowdaÎncă nu există evaluări

- Electus Distribution Reference Data Sheet: RESCODE PDFDocument2 paginiElectus Distribution Reference Data Sheet: RESCODE PDFFarshad yazdi100% (2)

- Power Estimation Methods For Sequential Logic Circuits: Pedram, M. DespainDocument13 paginiPower Estimation Methods For Sequential Logic Circuits: Pedram, M. DespainHeejung SoÎncă nu există evaluări

- Esd Protection Device and Circuit Design For Advanced Cmos TechnologiesDocument240 paginiEsd Protection Device and Circuit Design For Advanced Cmos TechnologiesNorbinkoNotoricko100% (2)

- ECE 334 Lecture Chapter 16 InverterDocument20 paginiECE 334 Lecture Chapter 16 InverterSaied Aly SalamahÎncă nu există evaluări

- A New Low Voltage, High PSRR, Cmos Bandgap Voltage ReferenceDocument4 paginiA New Low Voltage, High PSRR, Cmos Bandgap Voltage ReferenceBodhayan PrasadÎncă nu există evaluări

- PIC6F506Document114 paginiPIC6F506Rick TowÎncă nu există evaluări

- Lect3-Transistors PPDocument20 paginiLect3-Transistors PPpavithraÎncă nu există evaluări

- Lect0 IntroDocument60 paginiLect0 IntroRofyda SaadÎncă nu există evaluări

- HT658S SpecificationDocument6 paginiHT658S SpecificationwoodksdÎncă nu există evaluări

- BTM 112Document9 paginiBTM 112Andrei GrigoroiuÎncă nu există evaluări

- NV10Document39 paginiNV10Marian BaciuÎncă nu există evaluări

- Low-Power High-Speed Full Adder For Portable Electronic ApplicationsDocument2 paginiLow-Power High-Speed Full Adder For Portable Electronic ApplicationsArvind ChakrapaniÎncă nu există evaluări

- 3.unit 01Document73 pagini3.unit 01sanjayÎncă nu există evaluări

- ASIC Design Flow How To Design Your Own Chip: Frank K. G UrkaynakDocument77 paginiASIC Design Flow How To Design Your Own Chip: Frank K. G UrkaynakpdnoobÎncă nu există evaluări

- Designing Memory Array Subsystems CH 12 PDFDocument87 paginiDesigning Memory Array Subsystems CH 12 PDFrao rehÎncă nu există evaluări

- 18CSS201J AdeDocument148 pagini18CSS201J AdeNilesh bibhutiÎncă nu există evaluări

- A 650-pW 205 C Temperature Range Voltage Reference With Curvature-Based Temperature and BJT-Enhanced Process Compensation TechniquesDocument4 paginiA 650-pW 205 C Temperature Range Voltage Reference With Curvature-Based Temperature and BJT-Enhanced Process Compensation TechniquesBalaramamurty SannidhiÎncă nu există evaluări

- More Than 7000 Electrical & Electronics Engineering BooksDocument220 paginiMore Than 7000 Electrical & Electronics Engineering BooksHicham Elyassami50% (10)

- Duhamel's PrincipleDocument14 paginiDuhamel's Principlerexan16Încă nu există evaluări

- Lecture 03 - Deep Submicron (DSM) Cmos TechnologyDocument27 paginiLecture 03 - Deep Submicron (DSM) Cmos TechnologyAlexandre KennedyÎncă nu există evaluări

- AP2132Document12 paginiAP2132Jose Barroso GuerraÎncă nu există evaluări

- Prerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)Document2 paginiPrerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)SaurabhMoharirÎncă nu există evaluări

- A Brief History of Electronics Complete)Document8 paginiA Brief History of Electronics Complete)Maram AhmedÎncă nu există evaluări

- Rfid Based Car Parking Security System Using Microcontroller Ic89c52 IJERTV4IS031045Document5 paginiRfid Based Car Parking Security System Using Microcontroller Ic89c52 IJERTV4IS031045Tummuri ShanmukÎncă nu există evaluări

- VLSI Assignment 3Document2 paginiVLSI Assignment 3RIONA RACHEL JACOBÎncă nu există evaluări

- CMOS Process FlowDocument35 paginiCMOS Process Flowag21937570Încă nu există evaluări

- Chinese Nuclear Missile Guidance SystemsDocument12 paginiChinese Nuclear Missile Guidance SystemsshahpinkalÎncă nu există evaluări

- Ec6601 Vlsi DesignDocument12 paginiEc6601 Vlsi DesignKalai OmprakashÎncă nu există evaluări

- (Lecture Notes in Computer Science 7606 Theoretical Computer Science and General Issues) Sven Rosinger, Wolfgang Nebel (Auth.), José L. Ayala, Delong Shang, Alex Yakovlev (Eds.)-Integrated Circuit AndDocument265 pagini(Lecture Notes in Computer Science 7606 Theoretical Computer Science and General Issues) Sven Rosinger, Wolfgang Nebel (Auth.), José L. Ayala, Delong Shang, Alex Yakovlev (Eds.)-Integrated Circuit AndYehuda GiayÎncă nu există evaluări

- A 3.4dB NF K-Band LNA in 65nm CMOS TechnologyDocument4 paginiA 3.4dB NF K-Band LNA in 65nm CMOS TechnologyJeong-geun KimÎncă nu există evaluări

- Verilog HDL: ModuleDocument9 paginiVerilog HDL: ModuleM Usman RiazÎncă nu există evaluări