Documente Academic

Documente Profesional

Documente Cultură

DCT700 ph0

Încărcat de

waltech2005Descriere originală:

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

DCT700 ph0

Încărcat de

waltech2005Drepturi de autor:

Formate disponibile

5

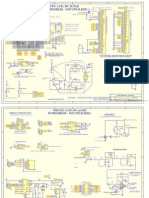

DCT700 Phase 0

Revision History

D

Main Board Schematic

Table of Contents

D

Schematic A

Rev. .00

REV.1

MODIFICATION RECORDS

Initial Proto Rev.

DMR SD_284 , DMR SD_286 , DMR SD_287, DMR SD_288, DMR SD_289, DMR SD_290, DMR SD_291, DMR SD_292, DMR SD_293, DMR SD_294, DMR BCST_1, DMR BCST_2, DMR SD_295, DMR SD_297

Sheet 1 2 3 4 5 6 7 8

Rev. .00 .00 .00 .00 .00 .00 .00 .00 .00 .00 .00 .00 .00 .00

Description

DCT700 Phase 0 Title Sheet DCT.SCH. Top level connections DIGITAL.SCH ANALOG.SCH PWR.SCH POR.SCH Hierarchical Grouping Hierarchical Analog Grouping Power Distribution Power On Reset QUAKE_RP Digital I/O

Ref

1 1 1 1

REV.2

DMR SD_299, DMR SD_301, DMR SD_303, DMR SD_304

REV.3

DMR SD_307-1, DMR SD_311-1, DMR SD_309, DMR SD_312, DMR BCST_3, DMR BCST_4

100 200 300 400

REV.4

DMR SD_317,DS_321,BCST_021,SD_326,SD_330,SD_332,SD_335,SD_341,SD_342,BCST_022

QUAKE_RP_DIGITAL.SCH

PLATFORM_FLASH & SRAM.SCH DDR_SDRAM.SCH SECURITY.SCH MC1.7, Battery, and TVPC 7114 Analog I/O

REV.A

Release for mass production(REV.A=REV.4)

9 10 11

C

900 200/400 700/800 1100 500/600

QUAKE_RP_ANALOG.SCH VIDEO_AUDIO.SCH AFE.SCH.

12 13 14

Baseband / Remod Output

Analog front end.

TUNER_UPSTREAM.SCH

Tuner, Upstream Amp & Diplexer

Acceptable Dielectric Material for 10 uF Multilayer Chip Capacitors. For power supply bypass applications (not AC signals).

Dielectric Material & Size Y5V X7R X5R X6S Y5V X7R X5R X6S Y5V X7R X5R X6S Y5V X7R X5R X6S 0805 1206 1206 1206 0805 1206 1206 1206 0805 1206 1206 0805 0805 1206 1206 0805 Voltage Rating 10V 6.3V 10V 10V 10V 6.3V 10V 10V 10V 6.3V 10V 6.3V 10V 6.3V 10V 6.3V Cap change at applied voltage. -85% -10% -10% -28% -75% -3% -2% -15% -65% -2% -2% -15% -20% <1% <1% -2% Acceptable for use? NO YES YES NO NO YES YES YES NO YES YES YES YES YES YES YES

PCB Requirements

Place all terminating resistors as close to source as possible. The series terminating resistors will have a value of 0, 33, or 51 Ohms.

Applied Voltage 5V

3.3V

C

B

C

B

2.5V

Notes :

1. 2. These schematics are grouped heirachically by function Each page in the schematics is assigned a set of reference designators (Ref) This reference is the starting designator for all parts on the page

Matt Chiang Raph Chang 9-24-03' 9-24-03'

1.2V

DCT_2

REVISION

INCORP

APVD

DESCRIPTION

D

A

C031282 Release for mass production of

D

THIS DOCUMENT CONTAINS PROPRIETARY DATA AND IS INTENDED ONLY TO CONVEY INFORMATION TO CUSTOMERS, PROSPRECTIVE CUSMERS, AND VENDORS. IT SHALL NOT BE COPIED, REPRODUCED, COMMUNICATED TO OTHERS, OR USED AS A BASIS FOR THE MANUFACTURE OR SALE OF APPARATUS WITHOUT THE WRITTEN PERMISSION OF GENERAL INSTRUMENT CORPORATION.

A

Phase 1

Sheet_02

Atlanta, Georgia, U.S.A. Title

Taipei, Taiwan R.O.C.

SCHEMATIC,MAIN,DCT700 P0

Document Number 864684-049 Date: Friday, September 26, 2003 Sheet 1 of 14 File Name Rev A

ECO NUMBER

REV

328-039-001

REVISION

1

5 4

2

3

3

2

4

1

+5V DIGITAL R2 3.3K_s R3 100_s DIAG_TXD R4 1K_s 1 2

D

J1 3 2 1 D header_3_pins

D

3 Q3 2sc2712 D +3.3V R5 1K_s Q4 2sc2712 1 R7 10K_s 3

TP1 TESTPIN ANALOG 2T 1 1T 2 S 3 hsp_242v2 D J6 T S hsp_241v1y D 1 2 3 COMP_OUT COMP_OUT LINE_OUT_LEFT LINE_OUT_RIGHT LINE_OUT_LEFT LINE_OUT_RIGHT CH3/4_SEL CH3/4_SEL MANF_TXD CH3/4_SEL MANF_RXD MANF_TXD MANF_RXD

TP2 TP3 TESTPIN TESTPIN

J5

R8 1K_s R6 3.3K_s DIAG_RXD 3

D1 mmbd4148

S1 QUAKE_SHIELD GND GND GND GND GND GND TP6 TP10 TESTPIN 1 TP4 TP8 TESTPIN J4 conn_f_female_007 185243-007-99 2 3 WRPROT_1 WRPROT_3 TP5 TP9 TESTPIN TP7 TESTPIN WRPROT_GND

C

6 5 4 3 2 1

REMOD_OUT

WRPROT_1 WRPROT_3

D A

HARD_RESETB

HARD_RESETB

Sheet_04 D2 hlmp_1401 YELLOW - POWER R10 PWR_LEDB R11 PWR_LED PWR_LED 4.7K_s 2 1 3 330_s Q1 2sc2712 D3 led RED - MESSAGE MSG_LEDB 3 330_s Q2 2sc2712 2

B

+3.3V

D R13 MSG_LED

B

R12 1 2

MSG_LED 4.7K_s

D +5V POWER IR_IN R14 IR_IN

See option Table 3

J3 1 2 3 conn_power_jack1 D R15 Sheet_05 0_s 3 GND(VCC) VDC_IN 5 4 D4 gp1um281yk MTG2 MTG1 VCC(GND) 1

4.7K_s

Table 3

VOUT

D4 MIM-5383H4 SFH5110-38

R15

INSTALL

R16

DNI

R17

INSTALL

R18

DNI

DNI

INSTALL

DNI

INSTALL

R17 R18

0_s 0_s

R16 Sheet_03 0_s

A

C1 0.1U_s

A

<Variant Name>

Atlanta, Georgia, U.S.A. Title

Taipei, Taiwan R.O.C.

DCT.SCH

Document Number 864684-049 Date: Friday, September 26, 2003

5 4 3 2 1

File Name Sheet 2 of 14

Rev A

QUAKE_RP_ DIGITAL_1

SECURITY_1 SYS_RESETB SPI_MOSI SPI_MISO MC_SPI_CSB SPI_CLK MC_CLK27 MC_CLK40 SPI_MOSI SPI_MISO MC_SPI_CSB SPI_CLK MC_CLK27 MC_CLK40 POR_RESETB SPI_MOSI SPI_MISO MC_SPI_CSB SPI_CLK MC_CLK27 MC_CLK40 POR_RESETB POR_RAM_ENB SRAM_VBATT MC_IRQB WRPROT_1 WRPROT_3 SYS_RESETB WRPROT_1 WRPROT_3 WRPROT_1 WRPROT_3

MANF_TXD MANF_RXD

MANF_TXD MANF_RXD

POR_RAM_ENB SRAM_VBATT

POR

MC_IRQB

MC_IRQB

INFO_SYNC INFO_DATA INFO_CLK HARD_RESETB HARD_RESETB HARD_RESETB EJTAG_RESETB POR_RESETB POR_IRQB EJTAG_RESETB POR_RESETB POR_IRQB EJTAG_RESETB POR_RESETB POR_IRQB PKT_CLK PKT_DATA PKT_SYNC

INFO_SYNC INFO_DATA INFO_CLK

INFO_SYNC INFO_DATA INFO_CLK

PKT_SYNC PKT_DATA PKT_CLK

Sheet_10

Sheet_06

PLATFORM_FLASH & SRAM_1 EBI_DATA_[15:0] EBI_ADDR_[24:0] EBI_RDB EBI_R/WB

B

EBI_DATA_[15:0] EBI_ADDR_[24:0] EBI_RDB EBI_R/WB

EBI_DATA_[15:0] EBI_ADDR_[24:0] EBI_RDB EBI_R/WB

B

SRAM_VBATT POR_RAM_ENB DDR_SDRAM_1 SD_CSB_0 SD_CLKE SD_CLKB SD_CLK SD_BA_1 SD_BA_0 SD_CASB SD_RASB SD_WEB SD_LDQS_0 SD_UDQS_1 SD_LDM SD_UDM SD_ADDR_[12:0] SD_DATA_[15:0] Sheet_09 IR_IN CH3/4_SEL SD_CSB_0 SD_CLKE SD_CLKB SD_CLK SD_BA_1 SD_BA_0 SD_CASB SD_RASB SD_WEB SD_LDQS_0 SD_UDQS_1 SD_LDM SD_UDM SD_ADDR_[12:0] SD_DATA_[15:0] SD_CSB_0 SD_CLKE SD_CLKB SD_CLK SD_BA_1 SD_BA_0 SD_CASB SD_RASB SD_WEB SD_LDQS_0 SD_UDQS_1 SD_LDM SD_UDM SD_ADDR_[12:0] SD_DATA_[15:0] IR_IN CH3/4_SEL SYS_RESETB ROM_CSB FLASH1_CSB SRAMLB_CSB SRAMUB_CSB SEL_FLASH1/ROMB ROM_CSB FLASH1_CSB SRAMLB_CSB SRAMUB_CSB SEL_FLASH1/ROMB ROM_CSB FLASH1_CSB SRAMLB_CSB SRAMUB_CSB SEL_FLASH1/ROMB SYS_RESETB SYS_RESETB

IR_IN CH3/4_SEL SYS_RESETB

Sheet_08

MSG_LED PWR_LED

MSG_LED PWR_LED

MSG_LED PWR_LED

Sheet_07

San Diego, California, USA. Title

Taipei, Taiwan, R.O.C.

DIGITAL.SCH

Size C Document Number 864684-049 Sheet

1

File Name 3 of 14

Rev A

Date: Friday, September 26, 2003

5 4 3 2

AFE QAM_IF+ QAM_IFQAM_IF+ QAM_IFIB_IF_POS IB_IF_NEG QAM_AGCI OOB_IF_POS OOB_IF_NEG OOB_AGC

QUAKE_RP_ANALOG

VIDEO_AUDIO.SCH

IB_IF_POS IB_IF_NEG QAM_AGCI OOB_IF_POS OOB_IF_NEG OOB_AGC

IB_IF_POS IB_IF_NEG QAM_AGCI DIG_COMPOSITE OOB_IF_POS OOB_IF_NEG OOB_AGC AUDIO_LEFT_NEG AUDIO_LEFT_POS OOB_VCO_POS OOB_VCO_NEG AUDIO_RIGHT_NEG AUDIO_RIGHT_POS

DIG_COMPOSITE

DIG_COMPOSITE COMP_OUT COMP_OUT REMOD_OUT LINE_OUT_RIGHT LINE_OUT_LEFT COMP_OUT REMOD_OUT LINE_OUT_RIGHT LINE_OUT_LEFT

AUDIO_LEFT_POS AUDIO_LEFT_NEG AUDIO_RIGHT_NEG AUDIO_RIGHT_POS

REMOD_OUT AUDIO_LEFT_NEG AUDIO_LEFT_POS AUDIO_RIGHT_NEG AUDIO_RIGHT_POS LINE_OUT_RIGHT LINE_OUT_LEFT

OOB_VCO_POS OOB_VCO_NEG

OOB_VCO_POS OOB_VCO_NEG

OOB_TAP

OOB_TAP CH3/4_SEL CH3/4_SEL CH3/4_SEL

Sheet_13

Sheet_12

TUNER_UPSTREAM.SCH TX_DAC+ TX_DACUS_CTL_DATA US_CTL_CLK US_CTL_CSB TX_OEN TUNER_SDA TUNER_SCLK TX_DAC+ TX_DACUS_CTL_DATA US_CTL_CLK US_CTL_CSB TX_OEN TUNER_SDA TUNER_SCLK TX_DAC+ TX_DACUS_CTL_DATA US_CTL_CLK US_CTL_CSB TX_OEN TUNER_SDA TUNER_SCLK OOB_TAP QAM_IF+

2

OOB_TAP

2

QAM_AGCT

QAM_AGCT

QAM_AGCT

QAM_IF-

Sheet_11

Sheet_14

San Diego, California, USA. Title

Taipei, Taiwan, R.O.C.

ANALOG.SCH

Size C Document Number 864684-049 Sheet

E

File Name 4 of 14

Rev A

Date: Friday, September 26, 2003

A B C D

Table 1 Reference Designator C113

Vendor and PN United Chemi-Con KMF25VB471M10X16 KZE25VB471M10X16 United Chemi-Con KMF16VB471M10X12 KMF25VB471M10X16 KZE series United Chemi-Con KMF16VB471M10X12 KMF25VB471M10X16 KZE16VB471M10X12

Motorola MCN

ESR max. at 20 deg C and 100 kHz 0.19 ohms 0.038 ohms 0.25 ohms 0.19 ohms Do not use. 0.25 ohms 0.19 ohms 0.053 ohms

Notes

507629-001 496616-002 507630-001 507629-001 Do not use. 507630-001 507629-001 496616-001

C101, C102

C105, C106

C121 = 1000pF C121 = 1000pF C121 = 1000pF

4

Input DC Power Filter and Protection

Overcurrent protection

F100 fuse2a VDC_IN 503458-001 2

+1.25V DC-DC Converter

+12V_UNREG +12V_UNREG Q100 FDC640P 8 7 6 5 D R102 17.4K_s 1% D D C103 1000P_s R101 47K_s See table 1 See table 1 1 2 3 DRAIN DRAIN DRAIN DRAIN GATE SOURCE 506626-001 6 5 4 L100 22uh_1_9a 1 1 501238-001 R100 1K_s 2 1 + C102 2 470uf_21 Low ESR

Reverse voltage protection

D105 mbrs340 1 138194-000 C115 100uf_07 2 1

EMI Filter

L102 32uh_2a 502130-001

Surge Protection

+12V_UNREG 1 2 3 4 D

U100 LM3485 ISENSE VIN GND PGATE NC PWRGND FB ADJ 495633-001-26

VOUT = VFB*(1+R1/R2) VFB = 1.242V nominal VOUT = 1.242V*(1 + 1K/47K) = 1.268V

+1.2V

1 + D104 1smb20a 488524-001

C114 0.1U_s

C113 470uf_22

C112 0.1U_s

C111 1000P_s

+ C101 470uf_21 Low ESR

D100 mbrs340 138194-000 2

C122 180P_s

C100 100P_s

Low ESR See table 1

+3.4V LDO Voltage Regulator

+12V_UNREG 1 +5V

+5V DC-DC Converter

+12V_UNREG U101 LM3485 1 2 3 4 VIN ISENSE PGATE GND NC PWRGND FB ADJ 495633-001-26 8 7 6 5 D 1 1 R105 17.4K_s 1% R103 10K_s 1% + C121 1000P_s C106 470uf_21 2 2 1 + C105 470uf_21 Low ESR D See table 1 R104 3.24K_s 1% See table 1 C104 100P_s Q101 FDC640P 1 2 3 DRAIN DRAIN DRAIN DRAIN GATE SOURCE 506626-001 6 5 4 L101 22uh_1_9a 501238-001 +12V_UNREG

R107 1K_s

R108 1K_s

C118 0.1U_s 2 R109 20_s 1 3 D 4 Q102 2SD2118 +3.3V D

VOUT = VFB*(1+R1/R2) VFB = 1.242V nominal VOUT = 1.242V*(1 + 10K/3.24K) = 5.075V

+5V

C120 1000P_s 8 7 R111 2.8K_s 1%

U104 TL431CD

2 3 6

VOUT = VFB*(1+R1/R2) VFB = 2.5V nominal VOUT = 2.5V*(1 + 1K/2.8K) = 3.393V

C116 C117 0.1U_s 10U_c 467639-001 6.3V X5R 1206 See table page 1.

D101 mbrs340 138194-000 2 D

Low ESR C107 1000P_s

R110 1K_s 1%

Collector tab of 2SD2118 must be heat sinked to copper on PCB.

2

-5V Charge Pump (20 mA max)

U103B 74vhc14dt 3 4 2 10U_c +3.3V R113 0_s +2.5VREF R114 20_s 1 3 1 2 Q104 2sa1162 2 1 3 Q103 mmbt2222a +2.5V 112004-014 U103A 74vhc14dt 2 5 7 D103 mbr0520lt U103C 74vhc14dt 6 D U103D 74vhc14dt 9 D C110 100P_s R106 100K_s 8 1 14 467639-001 6.3V X5R 1206 See table page 1. C109 1 D102 -5V mbr0520lt 2 C108 467639-001 6.3V X5R 1206 See table page 1.

+5V

+2.5V Voltage Regulator (50 mA nominal)

+5V

10U_c

R112 100_s

D U103E 74vhc14dt

1

11

10

U103F 74vhc14dt 13 12 San Diego, California, USA. Title Taipei, Taiwan, R.O.C.

PWR.SCH

Size C Document Number 864684-049

E

File Name Sheet 5 of 14

Rev A

Date: Friday, September 26, 2003

A B C D

DC Input Power Supply Voltage Monitor

Power UP threshold = 8.536V nom. Power DOWN threshold = 6.889V nom.

+12V_UNREG +3.3V

R166 3.3K_s +2.5VREF +2.5VREF

R157 3.3K_s

R155 20K_s 1% 7 6 + -

R152 10K_s R154 47.5K_s R153 100K_s PG1 D151 bat54alt1 2 3 1 HARD_RESETB 2 D150 bat54alt1 1 3 2 R151 3.3K_s 11 +2.5VREF C150 4700P_s 10 3 POR_IRQB +12V_UNREG R150 10K_s +3.3V

1 U150A LM339AD 128008-010

2 3 6 U151 TL431CD

8 7

R156 10K_s 1%

12

+ -

13 U150D LM339AD 128008-010

POR_RESETB

D D

3

3.3V Voltage Monitor

Power UP threshold = 2.989 V nom. Power DOWN threshold = 2.894 V nom.

R158 100K_s +3.3V +12V_UNREG R159 3.3K_s PG2 C151 0.1U_s D

12

EJTAG_RESETB

R160 5 3.3K_s R161 20K_s 1% +2.5VREF 4 + -

+3.3V

2 U150B LM339AD 128008-010

12 D R163 1K_s R164 10K_s 1% R165 8.06K_s 1% 9 8 + 3

1.2V Voltage Monitor

Power UP threshold = 1.125 V nom. Power DOWN threshold = 1.113 V nom.

+1.2V R162 100K_s

+12V_UNREG

+2.5VREF

14 U150C LM339AD 128008-010

12 D

San Diego, California, USA. Title

Taipei, Taiwan, R.O.C.

POR.SCH

Size C Document Number 864684-049

E

File Name Sheet 6 of 14

Rev A

Date: Friday, September 26, 2003

A B C D

U200B POR_RESETB SYS_RESETB T2 T1 SYS_RSTI_N SYS_RSTO_N

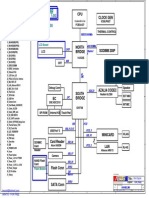

Quake MI_MADDR00 MI_MADDR01 MI_MADDR02 MI_MADDR03 MI_MADDR04 MI_MADDR05 MI_MADDR06 MI_MADDR07 MI_MADDR08 MI_MADDR09 MI_MADDR10 MI_MADDR11 MI_MADDR12 MI_MDBUS00 MI_MDBUS01 MI_MDBUS02 MI_MDBUS03 MI_MDBUS04 MI_MDBUS05 MI_MDBUS06 MI_MDBUS07 MI_MDBUS08 MI_MDBUS09 MI_MDBUS10 MI_MDBUS11 MI_MDBUS12 MI_MDBUS13 MI_MDBUS14 MI_MDBUS15 MI_BANK_O0 MI_BANK_O1 MI_CS_N0 MI_CS_N1 MI_RAS_N MI_CAS_N MI_WE_N AF6 AE6 AD6 AF5 AE5 AC5 AD5 AC6 AB7 AC7 AD7 AB8 AC8 AE14 AF14 AE13 AF13 AF12 AE12 AF11 AE11 AC11 AD11 AC12 AD12 AD13 AC13 AD14 AC14 AF7 AE7 AD8 AE8 AF8 AE9 AF9 SD_ADDR_0 SD_ADDR_1 SD_ADDR_2 SD_ADDR_3 SD_ADDR_4 SD_ADDR_5 SD_ADDR_6 SD_ADDR_7 SD_ADDR_8 SD_ADDR_9 SD_ADDR_10 SD_ADDR_11 SD_ADDR_12 SD_DATA_0 SD_DATA_1 SD_DATA_2 SD_DATA_3 SD_DATA_4 SD_DATA_5 SD_DATA_6 SD_DATA_7 SD_DATA_8 SD_DATA_9 SD_DATA_10 SD_DATA_11 SD_DATA_12 SD_DATA_13 SD_DATA_14 SD_DATA_15 SD_BA_0 SD_BA_1 SD_CSB_0 SD_RASB SD_CASB SD_WEB

SD_ADDR_[12:0] U200D Quake ATA_DATA00 ATA_DATA01 ATA_DATA02 ATA_DATA03 ATA_DATA04 ATA_DATA05 ATA_DATA06 ATA_DATA07 ATA_DATA08 ATA_DATA09 ATA_DATA10 ATA_DATA11 ATA_DATA12 ATA_DATA13 ATA_DATA14 ATA_DATA15 ATA_DRQ ATA_IOW ATA_IOR ATA_IOCHRDY ATA_DACK ATA_INTRQ ATA_DA0 ATA_DA1 ATA_DA2 LK_SEL0 LK_SEL1 LK_SEL2 LK_SEL3 LK_SEL4 (656_IN_CLK) LK_LD0 (656IN_D0) LK_LD1 (656IN_D1) LK_LD2 (656IN_D2) LK_LD3 (656IN_D3) LK_LD4 (656IN_D4) LK_LD5 (656IN_D5) LK_LD6 (656IN_D6) LK_LD7 (656IN_D7) LK_KD0 LK_KD1 LK_KD2 LK_KD3 SCI_TXD0 SCI_RXD0 SCI_TXD1 SCI_RXD1 SCI_TXD2 SCI_RXD2 SCI_TXD3 SCI_RXD3 USB_A_DATAP USB_A_DATAN USB_A_PWR_ON_N USB_A_PWR_ERR_N USB_B_DATAP USB_B_DATAN USB_B_PWR_ON_N USB_B_PWR_ERR_N IR_OUT IR_IN GPT_INCAP0 GPT_INCAP1 GPT_INCAP2 GPT_PWMA GPT_PWMB I2C_SDA I2C_SCL DMX_DBG_RXD DMX_DBG_TXD SPI_SCK SPI_MISO SPI_MOSI SPI_PCS0 SPI_PCS1 SPI_PCS2 SPI_PCS3 SFTM_PWRCLKP SFTM_PWRCLKN SFTM_DIB_DATAP SFTM_DIB_DATAN HSI_PKTDAT HSI_PKTSYN HSI_PKTCLK MCO_PKTDAT MCO_PKTSYN MCO_PKTCLK DO_POD_DATA (DRX) DO_POD_CLK (CRX) MCI_PKTDAT MCI_PKTSYN MCI_PKTCLK MENC_PKTDAT MENC_PKTSYN MENC_PKTCLK ATA_CS0 ATA_CS1 CCIR656_A00 CCIR656_A01 CCIR656_A02 CCIR656_A03 CCIR656_A04 CCIR656_A05 CCIR656_A06 CCIR656_A07 CCIR656_A08 CCIR656_A09 CCIR656_A10 CCIR656_A11 CCIR656_A12 CCIR656_A13 CCIR656_A14 CCIR656_A15 CCIR656_ACLK CCIR656_B00 CCIR656_B01 CCIR656_B02 CCIR656_B03 CCIR656_B04 CCIR656_B05 CCIR656_B06 CCIR656_B07 CCIR656_BCLK AUD_I2SO_DATA AUD_I2SO_LRCLK AUD_I2SO_CLK UO_POD_Q (QTX) UO_POD_I (ITX) UO_POD_C (CTX) UO_POD_E (ETX) AUD_COMP_CLK AUD_COMP_LRCLK AUD_COMP_DATA AUD_MCLK AUD_REQ_N HSI_DATA0 HSI_DATA1 AB2 AB4 AC2 AD1 AE1 AE2 AD3 AF3 AC4 AE3 AF2 AF1 AD2 AC3 AC1 AB3 AB1 AA4 AA3 AA2 AA1 Y4 Y1 Y3 Y2 W4 W5 Y26 Y25 Y24 Y23 Y22 AA26 AA25 AA24 AA22 AB26 AB25 AB24 AB23 AC26 AC25 AC24 AA23 R1 P4 P3 P2 P1 N4 N3 N2 N1 M2 M3 M4 C26 A26 B24 B25 B21 D20 A21 C21 E20 A15 B15 A19 B19 C19 RP200 V4 V3 V2 C25 D23 W3 W2 W1 L2 L3 L4 1 2 3 4 33_4_s 8 7 6 5 INFO_DATA INFO_SYNC INFO_CLK INFO_DATA INFO_SYNC INFO_CLK

QUAKE Digital CP

EBI_R/WB EBI_RDB

R201 R202

33_s 33_s

E1 E2 D6 D7 G5 C8 E5 F5 T3 K3 K4 J5 C9 R4 C4 C3 C2 C1 D4 D3 D2 D1 E4 E3 A8 B8 A7 B7 C7 A6 B6 C6 A5 B5 A4 B4 A3 B9 B3 D9 F4 F3 F2 F1 G4 G3 G2 G1 H4 H3 H2 H1 J4 J3 J2 J1 A2 A1 C5 B2 B1 K1 K2 H5 D8 A9

CP_R_WN CP_RD_N CP_DSACK_N CP_DATA_STRB_N CP_BERR_N CP_ADDR_STRB_N CP_SIZE0 CP_SIZE1 EXTI0 EXTI1 EXTI2 EXTI3 EXTI4 NMI_N CP_ADDR00 CP_ADDR01 CP_ADDR02 CP_ADDR03 CP_ADDR04 CP_ADDR05 CP_ADDR06 CP_ADDR07 CP_ADDR08 CP_ADDR09 CP_ADDR10 CP_ADDR11 CP_ADDR12 CP_ADDR13 CP_ADDR14 CP_ADDR15 CP_ADDR16 CP_ADDR17 CP_ADDR18 CP_ADDR19 CP_ADDR20 CP_ADDR21 CP_ADDR22 CP_ADDR23 CP_ADDR24 CP_ADDR25 CP_DATA00 CP_DATA01 CP_DATA02 CP_DATA03 CP_DATA04 CP_DATA05 CP_DATA06 CP_DATA07 CP_DATA08 CP_DATA09 CP_DATA10 CP_DATA11 CP_DATA12 CP_DATA13 CP_DATA14 CP_DATA15

PWR_LED MSG_LED

+3.3V

SD_DATA_[15:0]

GPIO_11 is dedicated for F/W to determine the number of DRAM chips installed on a QUAKE platform. Default is 1 chip = pull down, for 2 chips a pullup is required

MC_IRQB QUAKE has internal PU for EXTI[4:0]. POR_IRQB EBI_ADDR_0 EBI_ADDR_1 EBI_ADDR_2 EBI_ADDR_3 EBI_ADDR_4 EBI_ADDR_5 EBI_ADDR_6 EBI_ADDR_7 EBI_ADDR_8 EBI_ADDR_9 EBI_ADDR_10 EBI_ADDR_11 EBI_ADDR_12 EBI_ADDR_13 EBI_ADDR_14 EBI_ADDR_15 EBI_ADDR_16 EBI_ADDR_17 EBI_ADDR_18 EBI_ADDR_19 EBI_ADDR_20 EBI_ADDR_21 EBI_ADDR_22 EBI_ADDR_23 EBI_ADDR_24

QUAKE has internal PD for GPIO[23:00].

LK_SEL[3:0] are outputs. LK_SEL4 has internal PD.

AE20 AF20 AD19 AE19 AC18 AF18 AC17 AD17 AE17 AF17 AF16 AE16 AD16 AF19 AD18 AE18 AC19 D15 C15 AF21 AE21 AD20 AC20 A10 B10

QUAKE has internal PD for LK_LD[7:0]

EBI_ADDR_[24:0] EBI_DATA_[15:0]

MI_WMASK0 MI_WMASK1 MI_DQS0 MI_DQS1 MI_DQS2 MI_DQS3 MI_CKE MI_CLK MI_CLK_N

AD10 AB10 AF10 AC10 AE10 AB11 AB9 AC9 AD9

SD_LDM SD_UDM SD_LDQS_0 SD_UDQS_1

QUAKE has internal PD for LK_KD[3:0]

EBI_DATA_0 EBI_DATA_1 EBI_DATA_2 EBI_DATA_3 EBI_DATA_4 EBI_DATA_5 EBI_DATA_6 EBI_DATA_7 EBI_DATA_8 EBI_DATA_9 EBI_DATA_10 EBI_DATA_11 EBI_DATA_12 EBI_DATA_13 EBI_DATA_14 EBI_DATA_15

SD_CLKE SD_CLK SD_CLKB

MANF_TXD MANF_RXD

TDO TDI TCK TMS TRST_N EJTAG_SEL_N

AE26 AD24 AF26 AE25 AD25 AF25

EJTAG_TDO R205 33_s EJTAG_TDI EJTAG_TCK EJTAG_TMS EJTAG_TRSTB QUAKE has internal PD/PU for TDI, TCK, TMS & TRST_N. TDO is output

QUAKE has internal PU for SCI_RXD[3:0] J200 header_7pins_2rows 1 3 5 7 9 11 13 2 4 6 8 10 12 14

QUAKE has internal PU for USB inputs.

B13 A13 C11 B11 D13 C13 A12 D11 A11 AC16 AD23 D10 AD15 AD21 AE15 AE23 AF23 AE24 AF24

ROM_CSB FLASH1_CSB SRAMLB_CSB SRAMUB_CSB EBI_CSB_6 EBI_CSB_7 EBI_CSB_8

CP_CS_N0 CP_CS_N1 CP_CS_N2 CP_CS_N3 CP_CS_N4 CP_CS_N5 CP_CS_N6 CP_CS_N7 CP_CS_N8 CP_BOOTSEL_CS0_N

OUTENB_N TCC

AF15 AC22 D

TP204

TP205

EJTAG_RESETB

+3.3V

QFE_XTI QFE_XTO CLK27_VCXO_I CLK27_VCXO_O PCRDAC CLK54_OUT CP_CLK40_OUT CLK27_OUT CP_CLK27_OUT

L26 K22 A20 B20 D19 V1 L1 U4 D5

PHY_XTALI PHY_XTALO CLK27_I CLK27_O CLK27_PCR_DAC

D IR_IN QUAKE has internal PD for GPT_INCAP[2:0], GPT_PWMA & GPT_PWMB. R203 33_s MC_CLK40

SEL_FLASH1/ROMB

SEL_FLASH1/ROMB

CLK40_OUT CLK27_OUT

MC_CLK40

R204

33_s

MC_CLK27

MC_CLK27

TP203 27MHz SPI_CLK SPI_MISO SPI_MOSI MC_SPI_CSB R200

33_s U3 T4 U1 U2 AC23 QUAKE has internal PU AF4 for SPI_PCS[3:0]. AE4 D12 E12 B12 C12

QUAKE Digital I/O

CH3/4_SEL

AD26 AD4 M1 R2 U5 T5 R5 P5 V25 V24 V23 W26 W25 W24 W23 AC21 AC15 C10 V26 U23 B22 R3 A22 D21

GPIO00 GPIO01 GPIO02 GPIO03 GPIO04 GPIO05 GPIO06 GPIO07 GPIO08 GPIO09 GPIO10 GPIO11 GPIO12 GPIO13 GPIO14 GPIO15 GPIO16 GPIO17 GPIO18 GPIO19 GPIO20 GPIO21 GPIO22 GPIO23

PKT_DATA PKT_SYNC PKT_CLK

27 MHz VCXO

TP230 Ground guard these components and all associated traces, including traces to Quake and connect ground guard to digital ground. Place ground vias every 0.25 inches. TP206 R227 4.7K_s CLK27_PCR_DAC 1 1 1 R226 4.7K_s R225 4.7K_s R224 4.7K_s 1 C223 1000P_s 2 D220 1sv322 2 R223 100K_s C221 0.01U_s D D 1 R221 100_s 2 R222 51_s 1 C220 22P_s 2 D CLK27_O Y220 27mhz 2 1 CLK27_I

35.84 MHz XO

Ground guard these components and all associated traces, including traces to QUAKE and connect ground guard to analog ground. Place ground vias every 0.25 inches.

R210 47K_s R220 100K_s PHY_XTALI PHY_XTALO C212 15P_s Y210 35_84mhz_sm C211 15P_s +3.3V L210 2.7uH_c_1210 INFO_DATA INFO_SYNC INFO_CLK MC_CLK40 C210 68P_s A D J201 1 2 3 4 5 6

C225 0.1U_s 2 D 2 D

C224 0.1U_s

BER Test Header

C222 47P_s 2 D

A TP207

DNI

header_6_pins

San Diego, California, USA. Title

Taipei, Taiwan, R.O.C.

QUAKE_DIGITAL.SCH

Size C Document Number 864684-049 Sheet 7 of 14 File Name Rev A

Date: Friday, September 26, 2003

ROM Socket Daughter card interface

+3.3V J300 SEL_FLASH1/ROMB TP319 TP320 TP318

D

TP351 1

BOOT BLOCK FLASH

EBI_ADDR_[24:1] TP350 ROM_CSB 1 TP345 TP343 TP341 TP339 TP337 TP335 TP333 TP331 TP302 EBI_ADDR_24 EBI_ADDR_23 EBI_ADDR_22 EBI_ADDR_21 EBI_ADDR_20 EBI_ADDR_19 EBI_ADDR_18 EBI_ADDR_17 EBI_ADDR_16 EBI_ADDR_15 EBI_ADDR_14 EBI_ADDR_13 EBI_ADDR_12 EBI_ADDR_11 EBI_ADDR_10 EBI_ADDR_9 EBI_ADDR_8 EBI_ADDR_7 EBI_ADDR_6 EBI_ADDR_5 EBI_ADDR_4 EBI_ADDR_3 EBI_ADDR_2 EBI_ADDR_1 SYS_RESETB FLASH1_CSB EBI_RDB EBI_R/WB U300 C4 C5 A6 B5 B6 D1 C1 B1 A1 C2 A2 B2 C3 A3 A7 C6 B7 A8 C7 B8 C8 D8 B4 D7 F8 B3 A21 A20 A19 A18 A17 A16 A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 RP/ CE/ OE/ WE/ EBI_DATA_[15:0]

D

1 1 1 1 1 1 1 1

1 1 1

TP317 TP315 TP313

TP316 TP314 TP312 TP310 TP308 TP306 TP304

1 1

TP311 TP309

1 TP307 1 TP305 1 TP303 TP301

SEL_FLASH1/ROMB EBI_ADDR_10 EBI_ADDR_11 EBI_ADDR_18 EBI_ADDR_19 EBI_ADDR_17 EBI_ADDR_15 EBI_ADDR_4 EBI_ADDR_1 EBI_ADDR_9 EBI_ADDR_6 EBI_ADDR_5 EBI_RDB EBI_DATA_8 EBI_ADDR_14 EBI_ADDR_16 EBI_DATA_7 EBI_DATA_6 EBI_DATA_3 EBI_DATA_1

TP352

1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41

2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 42

EBI_ADDR_20 ROM_CSB EBI_ADDR_13 EBI_ADDR_3 EBI_ADDR_2 EBI_ADDR_7 EBI_DATA_12 EBI_DATA_11 EBI_DATA_10 EBI_DATA_9 EBI_DATA_15 EBI_DATA_14 EBI_DATA_13 EBI_ADDR_12 EBI_ADDR_8 EBI_DATA_5 EBI_DATA_4 EBI_DATA_2 EBI_DATA_0

1 1 1 1 1 1 1 1 1

TP344 1 TP342 1 TP340 1 TP338 1 TP336 1 TP334 1 TP332 1 TP330 1

hdr42_21x2_50_sm

FLE-121-01-G-DV-A (SAMTEC) D

D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 WP/ VCC VCCQ VPP GND GND

E2 D2 F3 E4 D4 F6 E6 D6 F2 E3 D3 F4 E5 D5 F7 E7 A5 F5 E1 A4 E8 F1

EBI_DATA_15 EBI_DATA_14 EBI_DATA_13 EBI_DATA_12 EBI_DATA_11 EBI_DATA_10 EBI_DATA_9 EBI_DATA_8 EBI_DATA_7 EBI_DATA_6 EBI_DATA_5 EBI_DATA_4 EBI_DATA_3 EBI_DATA_2 EBI_DATA_1 EBI_DATA_0

DNI: (Install only for the Proto, EPR and PPR)

D SYS_RESETB FLASH1_CSB EBI_RDB EBI_R/WB

+3.3V

Layout Note: Remapping connector signals is allowed for layout optimization if necessary.

NOTE: All test pads should be placed at the bottom layer

C300 0.1U_s 2 D

1 C302 0.01U_s

Intel_GE28F320C3BD70 xxxxxx-xxx-xx

The placement of C302 should be near the E1 and F5 of U300.

TABLE 1: MEMORY OPTIONS

C

SIZE

TYPE/VENDOR

BOOT BLOCK(U300) uBGA package only

32 MBIT

Intel_ GE28F320C3BD70 ST_M28W320ECB70_ZB1

SRAM

+3.3V

DNI R311 R312

B

10K_s EBI_DATA_0 10K_s EBI_DATA_1 DNI 10K_s EBI_DATA_2 10K_s EBI_DATA_3 DNI 10K_s EBI_DATA_4 10K_s EBI_DATA_5 DNI 10K_s EBI_DATA_6 10K_s EBI_DATA_7 10K_s EBI_DATA_8 EBI_DATA_9 EBI_DATA_10 EBI_DATA_11 EBI_DATA_12

R302 DNI R303 R304 R305 R306 R307 R308 DNI R309 R310 RP300 1 2 3 4 10000_4 RP301 DNI DNI

10K_s SRAM_VBATT 10K_s

SRAM_VBATT E1 D6 1 1

121.5MHz => EBI_DATA_[3:2] = 10 MIPS SPEED SETTING

R314 R315 R316 R317 R318 R319

10K_s 10K_s 10K_s 10K_s 10K_s 10K_s

162MHz => EBI_DATA_[6..4] = 010

The placement of C303 should be near the D6 and E1 of U301.

8 7 6 5 SRAM_CSB

A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15 A16 nc17 /OE /CS1 ncCS2 /WE nc1 nc2 nc3

VCC1 VCC2

R313

10K_s

DDR SDRAM SPEED SETTING

R300 10K_s 2

C301 0.1U_s

U301 C303 0.01U_s EBI_ADDR_1 EBI_ADDR_2 EBI_ADDR_3 EBI_ADDR_4 EBI_ADDR_5 EBI_ADDR_6 EBI_ADDR_7 EBI_ADDR_8 EBI_ADDR_9 EBI_ADDR_10 EBI_ADDR_11 EBI_ADDR_12 EBI_ADDR_13 EBI_ADDR_14 EBI_ADDR_15 EBI_ADDR_16 EBI_ADDR_17 EBI_RDB A3 A4 A5 B3 B4 C3 C4 D4 H2 H3 H4 H5 G3 G4 F3 F4 E4 D3 A2 B5 A6 G5 H1 H6 G2

I/O15 I/O14 I/O13 I/O12 I/O11 I/O10 I/O9 I/O8 I/O7 I/O6 I/O5 I/O4 I/O3 I/O2 I/O1 I/O0 /UB /LB GND1 GND2 nc4

G1 F1 F2 E2 D2 C2 C1 B1 G6 F6 F5 E5 D5 C6 C5 B6 B2 A1 D1 E6 E3

EBI_DATA_15 EBI_DATA_14 EBI_DATA_13 EBI_DATA_12 EBI_DATA_11 EBI_DATA_10 EBI_DATA_9 EBI_DATA_8 EBI_DATA_7 EBI_DATA_6 EBI_DATA_5 EBI_DATA_4 EBI_DATA_3 EBI_DATA_2 EBI_DATA_1 EBI_DATA_0 SRAMUB_CSB SRAMLB_CSB SRAMUB_CSB SRAMLB_CSB

EBI_R/WB 8 7 6 5 EBI_DATA_[15..13] to be used by F/W to detect HW configurations. EBI_DATA_[15..13] EBI_DATA_[15..13] D 111 = 000 = Quake Installed Quake RP Installed R301 POR_RAM_ENB POR_RAM_ENB 1K_s 2 1 3 Q300 2sc2712

EBI_DATA_13 EBI_DATA_14 EBI_DATA_15

1 2 3 4 10000_4

CY62137VLL 481396-001-69

RESET CONFIGURATION: cp_data00 RC: ebi_config Bit cp_data01 RC: boot_config Bit cp_data02 RC: Memory Clock Speed Select Bus Bit 0 cp_data03 RC: Memory Clock Speed Select Bus Bit 1 cp_data04 RC: MIPS Clock Speed Select Bus Bit 0 cp_data05 RC: MIPS Clock Speed Select Bus Bit 1 cp_data06 RC: MIPS Clock Speed Select Bus Bit 2 cp_data07 RC: USB Normal Clock Source Select cp_data08 RC: Internal clk27 Alternate Source Select cp_data09 RC: MIPS After Reset Delay Enable cp_data10 RC: Staggered Reset Off Select cp_data11 RC: Slip ckt control cp_data12 RC: PLL By-Pass Select

5 4 3 2

San Diego, California, USA. Title

Taipei, Taiwan, R.O.C.

PLATFORM_FLASH & SRAM.SCH

Size C Document Number 864684-049 Sheet

1

File Name 8 of 14

Rev A

Date: Friday, September 26, 2003

SD_ADDR_[6..0] SD_ADDR_10

RP400 SD_ADDR_10 SD_ADDR_0 SD_ADDR_1 SD_ADDR_2 SD_ADDR_3 SD_ADDR_4 SD_ADDR_6 SD_ADDR_5 1 2 3 4 5 6 7 8 33_8 RP401 SD_LDQS_0 SD_LDM SD_WEB SD_CASB SD_RASB SD_CSB_0 SD_BA_0 SD_BA_1 SD_LDQS_0 SD_LDM SD_WEB SD_CASB SD_RASB SD_CSB_0 SD_BA_0 SD_BA_1 1 2 3 4 5 6 7 8 33_8 SD_DATA_[7..0] RP402 SD_DATA_0 SD_DATA_1 SD_DATA_2 SD_DATA_3 SD_DATA_4 SD_DATA_5 SD_DATA_6 SD_DATA_7 SD_ADDR_7 SD_ADDR_8 SD_ADDR_9 SD_ADDR_11 SD_ADDR_12 1 2 3 4 5 6 7 8 R408 R409 R410 R411 R412 33_8 16 15 14 13 12 11 10 9 33_s 33_s 33_s 33_s 33_s DDR_DATA_0 DDR_DATA_1 DDR_DATA_2 DDR_DATA_3 DDR_DATA_4 DDR_DATA_5 DDR_DATA_6 DDR_DATA_7 DDR_ADDR_7 DDR_ADDR_8 DDR_ADDR_9 DDR_ADDR_11 DDR_ADDR_12 +2.5V SD_DATA_8 SD_DATA_9 SD_DATA_10 SD_DATA_11 SD_DATA_12 SD_DATA_13 SD_DATA_14 SD_DATA_15 R413 R415 R416 R417 R418 R419 R420 R421 33_s 33_s 33_s 33_s 33_s 33_s 33_s 33_s DDR_DATA_8 DDR_DATA_9 DDR_DATA_10 DDR_DATA_11 DDR_DATA_12 DDR_DATA_13 DDR_DATA_14 DDR_DATA_15 DDR_CK DDR_CKB SD_CLK SD_CLKB SD_CLK SD_CLKB R414 R428 20_s 20_s DDR_CK DDR_CKB R404 121_s R406 121_s DDR_UDQS_1 DDR_LDQS_0 DDR_WEB DDR_CASB DDR_RASB DDR_CSB_0 DDR_BA_0 DDR_BA_1 DDR_CLKE DDR_UDM DDR_LDM C408 10P_s 51 16 21 22 23 24 26 27 44 45 46 47 20 19 50 UDQS LDQS WE CAS RAS CS BA0 BA1 CKE CK CK UDM LDM DNU DNU 16 15 14 13 12 11 10 9 DDR_LDQS_0 DDR_LDM DDR_WEB DDR_CASB DDR_RASB DDR_CSB_0 DDR_BA_0 DDR_BA_1 2 16 15 14 13 12 11 10 9 DDR_ADDR_10 DDR_ADDR_0 DDR_ADDR_1 DDR_ADDR_2 DDR_ADDR_3 DDR_ADDR_4 DDR_ADDR_6 DDR_ADDR_5

16 MBYTES UNIFIED DDR_SDRAM

+2.5V

1 C405 0.1U_s 2

C409 0.01U_s 2

C410 1000P_s

C411 1U_s 2

C403 1000P_s 2

C404 0.01U_s 2

467639-001 C401 6.3V X5R 10U_c 1206 See table page 1

D

D 1 3 15 18 33 55 61 9 VDD VDDQ VDDQ VDD VDD VDDQ VDDQ VDDQ

U400 DDR_DATA_0 DDR_DATA_1 DDR_DATA_2 DDR_DATA_3 DDR_DATA_4 DDR_DATA_5 DDR_DATA_6 DDR_DATA_7 DDR_DATA_8 DDR_DATA_9 DDR_DATA_10 DDR_DATA_11 DDR_DATA_12 DDR_DATA_13 DDR_DATA_14 DDR_DATA_15 2 4 5 7 8 10 11 13 54 56 57 59 60 62 63 65 DQ0 DQ1 DQ2 DQ3 DQ4 DQ5 DQ6 DQ7 DQ8 DQ9 DQ10 DQ11 DQ12 DQ13 DQ14 DQ15

SD_ADDR_7 SD_ADDR_8 SD_ADDR_9 SD_ADDR_11 SD_ADDR_12 SD_DATA_[15..8]

A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10/AP A11 A12 NC (A13)

29 30 31 32 35 36 37 38 39 40 28 41 42 17

DDR_ADDR_0 DDR_ADDR_1 DDR_ADDR_2 DDR_ADDR_3 DDR_ADDR_4 DDR_ADDR_5 DDR_ADDR_6 DDR_ADDR_7 DDR_ADDR_8 DDR_ADDR_9 DDR_ADDR_10 DDR_ADDR_11 DDR_ADDR_12

+2.5V

8M x16

Place caps near U202 (DDR_SDRAM)

R401 1K_s 1%

C406 0.01U_s 10% 50V X7R

R402 10K_s R407 121_s R405 121_s

R403 10K_s

VREF

49

SD_VREF

C400 0.01U_s 10% 50V X7R

R400 1K_s 1%

C

C407 10P_s

Place this cap close to the U200 D (QUAKE)

SD_CLKE SD_UDQS_1 SD_UDM SD_CLKE SD_UDQS_1 SD_UDM R422 R423 R424 33_s 33_s 33_s DDR_CLKE DDR_UDQS_1 DDR_UDM

Place this cap close to the U202

MICRON - MT46V8M16TG-6T D

LAYOUT NOTES:

1. DDR_DATA[15:0] lines and strobes should be the shortest (and most direct) trace lengths as possible. 2. CK & CKB traces again should be the shortest possible lengths, with CK & CKB being adjacent to each other on ALL layers. 3. DDR_ADDR[15:0], & control signals are not as critical as layout items 1 and 2. 4. NO data or data strobe traces should exceed 2 inches in length. (The 2 inches includes traces to and from series termination resistors) Less critical signals should be less than 3 inches. Clock traces can be up to 3 inches, but should be as short as possible. Route DQS and clock pair signal traces FIRST when laying out the board. 5. Trace length variations are as follows: Data, DQS signal traces have no more than 0.5 inch variation Address, DQM, control signal traces have no more than 1.0 inch variation Clock traces should be as closely matched as possible. 6. Clock traces should be on same layer(s) and should be spaced 5 mils from each other, with other signal traces spaced 10 mils away. 7. Number of vias for data and DQS lines should be restricted to maximum of 2 per signal trace. Other signals should be restricted to no more than 3 vias per signal trace. Micro-vias (14 mil through hole) can be used for signals, with larger (20 mil minimum through hole) used for power and grounds. 8. Trace widths for signals should be 5-6 mils. Power and ground signals should have minimum 10 mil traces from pins to vias (that drop down to power/ground planes) 8a. DDR_VREF signal should be 20mil trace. 9. DDR section of board should keep all signals that are NOT part of the DDR interface outside of defined area on ALL layers. 10. Decoupling capacitors should be used in accordance with the DDR manufacturer's recommendations. Bulk bypass capacitors should be located nearby DDR memory. 11. Power and ground pins should have dedicated traces to VIA, with adjacent power and ground pins using common trace only when distance to via is less than .2 inch from any one pin/ball. In this case a more robust trace should be used to connect more than one pin to the via. (15 mil trace minimum)

6 34 48 52 58 64 66 12

VSSQ VSS VSS VSSQ VSSQ VSSQ VSS VSSQ

NC NC NC NC

53 43 25 14

San Diego, California, USA. Title

Taipei, Taiwan, R.O.C.

DDR_SDRAM.SCH

Size C Document Number 864684-049 Sheet

1

File Name 9 of 14

Rev A

Date: Friday, September 26, 2003

5 4 3 2

+3.3V Bypass 1 1 1 1 1 1 1 1 1 1 1 C909 0.1U_s 2 C915 47P_s

C900 4700P_s 2 2

C901 0.1U_s 2

C902 0.1U_s 2

C903 4700P_s 2

C904 0.1U_s 2

C905 4700P_s 2

C906 0.1U_s 2

C907 47P_s 2

C908 4700P_s 2

+3.3V

D

D

D

+3.3V U900 R922 10K_s SYS_RESETB SYS_RESETB 2 D912 bat54alt1 1 3 SPI_CLK MC_SPI_CSB SPI_MOSI +3.3V SPI_CLK MC_SPI_CSB SPI_MOSI RP901 5 6 7 8 D WRPROT_1 WRPROT_3 470_4 49 51 76 77 78 81 82 83 84 85 86 87 88 89 92 94 100 +3.3V 99 61 62 63 64 65 66 67 68 73 74 75 VBATT 1 16 17 C911 0.1U_s 1 1 2 D902 1n4148w D VB900 TESTPIN D911 1n4148w FUSE1 FUSE0 MIERROR MCLKI MIVAL MDI7 MDI6 MDI5 MDI4 MDI3 MDI2 MDI1 PKTDATAIN/MDI0 PKTSTARTIN/MISTAT PKTCLKIN/BITCLK SYNC_CLK CLK_27 CTRL_CLK_27 TAD7 TAD6 TAD5 TAD4 TAD3 TAD2 TAD1 TAD0 TESTCLK TESTWRB TESTSEL GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND VBATT GNDBATT MC1_7C FUSE1RTN FUSE0RTN 50 52 MC_RESETB 97 1 2 3 4 3 2 1 22 23 24 25 9 TVPC_DETECTB RESETB SCLK SPL_CSB MOSI TMROEB TMS TCK TDI 6 14 21 30 46 47 54 71 79 90 96 31 41 60 69 VDD3 VDD3 VDD3 VDD3 VDD3 VDD3 VDD3 VDD3 VDD3 VDD3 VDD3 VDD3 VDD3 VDD3 VDD3

POR_RESETB

POR_RESETB

TVPC_SIO TVPC_CLOCK TVPC_RESETB TVPC_5V_SENSE TVPC_3V_SENSE MISO

10 8 11 13 12 4 5 26 SPI_MISO MC_IRQB TD900 TDO

SPI_MISO MC_IRQB

MC1.7

UP_INTB TDO

R903 470K_s

R904 470K_s

MOERROR MCLKO MOVAL

45 44 43

D D INFO_DATA INFO_SYNC INFO_CLK MC_CLK40 MC_CLK27 INFO_DATA INFO_SYNC INFO_CLK MC_CLK40 MC_CLK27

MDO7 MDO6 MDO5 MDO4 MDO3 MDO2 MDO1 PKTDATAOUT/MDO0 PKTSTARTOUT/MOSTRT PKTCLKOUT

40 39 38 37 36 35 34 33 32 28

RP900 MC_PKTDATA MC_PKTSTART MC_PKTCLK 1 2 3 4 33_4_s 8 7 6 5 PKT_DATA PKT_SYNC PKT_CLK PKT_DATA PKT_SYNC PKT_CLK

+3.3V

CLK27M TEST_PAD

R926 TESTOUT3 TESTOUT2 TESTOUT1 TESTOUT0 55 56 57 58

51_s R914 4.7K_s

POR_RAM_ENB

1 D901 1n5711 3

VB901 TESTPIN

PDUNDERB VSUPPLY VBATT_EN

18 19 98 1

SRAM_VBATT

D SRAM_VBATT

7 15 20 27 29 42

+ C910 100uf_07 2

48 53 59 70 72 80 91 93 95

C913 0.1U_s 2 2

1 + C914 10u_50v

Low Leakage Cap

D D D

B

BTV 3 1

BT905 3_0V_BR2032T3L_B 2

VB902 TESTPIN

JET R906

VB903 TESTPIN D

620_s

DNI BTV 3 1 BTV 3 1 BTV 3 1 BTV

1

A

BT903 3_0V_BR2335T3L_B 123002-020-99 2 2 JET

BT904 3_0V_BR2450A_GB 414816-003-99 JET 2

BT906 3_0V_BR2330A_GA JET 2

BT907 106007-002

JET

San Diego, California, USA. Title

Taipei, Taiwan, R.O.C.

SECURITY.SCH

Size C Document Number 864684-049 Sheet

1

File Name 10 of 14

Rev A

Date: Friday, September 26, 2003

5 4 3 2

+2.5V

AB5 AB6

+3.3V C427 0.1U_s

AB12 AB13

C428 0.1U_s

Place bypass capacitors of +3.3v, +2.5v, and +1.2V near IC's pin on bottom side. QUAKE pin numbers for each cap are indicated.

AB14 AB15 AB17 AB18

AB21 AB22 W22

E8 E9 E10

E15 E18

G22 J22 L22 N22 R22

K5 L5

V5 Y5

+1.2V

C482 0.1U_s

D AB22 E8 E9 E10 E15 E18 G22 J22 K5 L5 L22 N22 R22 C441 0.01U_s V5 W22 Y5 AA5 AB16 AB19 AB20 E6 E7 E11 E21 E22 M5 N5 U22 V22 E14 E19 M22 L23 G23 J25 OOB_AGC R24 P26 K23 DO_ADC3_NSUPA DO_ADC3_PSUPA_SHA DO_ADC3_NSUPA_SHA DO_ADC3_PSUPA QFE_XTAL_PSUPA QFE_XTAL_NSUPA QFE_ADC_ASUB UO_DAC_ASUB UO_DAC_BG_NSUPA UO_DAC_NSUPA N23 P22 L25 L24 E25 E26 E24 1 2 3 4 D 8 7 6 5 U200A Quake RP410 1000_4 C442 0.1U_s C443 0.1U_s C444 0.01U_s C445 0.1U_s C446 0.01U_s C447 0.1U_s C448 0.01U_s

4

+3.3V

+3.3V L415 ferrite_0603

L402 10uH_c_1008

1 L425 ferrite_0603 1

A17 (DAC B)

C432 0.1U_s

U200C AB21 VDD12 AB18 VDD12 AB17 VDD12 AB15 VDD12 AB14 VDD12 AB5 AB6 AB12 AB13 D17 A17 B18 D16 A16 E13 C20 M26 N24 K24 H26 VDD25 VDD25 VDD25 VDD25

Quake VDD12 VDD12 VDD12 VDD33 VDD33 VDD33 VDD33 VDD33 VDD33 VDD33 VDD33 VDD33 VDD33 VDD33 VDD33 VDD33

VDD12 VDD12 VDD12 VDD12 VDD12 VDD12 VDD12 VDD12 VDD12 VDD12 VDD12 VDD12 VDD12

AB16 AA5

QUAKE Power

AB19 AB20

C421 0.1U_s

E6 E7

C422 0.1U_s

E11

E21 E22

M5 N5

U22 V22

C425 0.01U_s C426 0.1U_s

+3.3V

ANA_3.3V

2 C440 0.1U_s D

C419 0.1U_s

C420 0.01U_s

C423 0.01U_s

C424 0.01U_s

C434 467639-001 6.3V X5R 10U_c 1206 See table page 1 A

DAC A, C & D not used.

+3.3V D SDC_AVDD +3.3VA0 +3.3VA1 +3.3VA2 +3.3VA3 +3.3VA4 C453 0.1U_s +3.3VA5 +3.3VA6 2 C454 0.1U_s +3.3VA7

QVD_AVDD_A QVD_AVDD_B QVD_AVDD_BIAS QVD_AVDD_C QVD_AVDD_D SDC_AVDD XTAL_CLK27_PSUPA

SDC_AGND XTAL_CLK27_NSUPA

+3.3V

L418 ferrite_0603 1 L419 ferrite_0603 1 L420 ferrite_0603

3

BTSC_ADC2_PSUPA BTSC_ADC2_NSUPA_SHA BTSC_ADC2_PSUPA_SHA BTSC_ADC2_NSUPA DI_ADC1_PSUPA_SHA DI_ADC1_PSUPA DI_ADC1_NSUPA DI_ADC1_NSUPA_SHA

Signal Opitimize

Place these parts near QUAKE.

RP412 470_4 8 7 6 5

+3.3V

QUAKE Analog

RP411 1000_4 8 7 6 5 IB_IF_POS IB_IF_NEG 1 2 3 4 K26 K25 A23 A25 OOB_IF_POS OOB_IF_NEG R25 R26 C23 T25 T24 DI_ADC1_VIP DI_ADC1_VIN DI_RFAGC_SDV DI_AGC_SDV DO_ADC3_VIP DO_ADC3_VIN DO_AAGC_SD DO_LO_BP DO_LO_BN AUD_LEFT_POS AUD_LEFT_NEG AUD_RIGHT_POS AUD_RIGHT_NEG AF22 AE22 AD22 AUD_I2SI_CLK AUD_I2SI_LRCLK AUD_I2SI_DATA TNR_RFTE0 TNR_RFTD TNR_RFTCK U24 U25 U26 1 2 3 4 TUNER_SDA TUNER_SCLK

UO_IOUTP UO_IOUTN

F26 E23

TX_DAC+ TX_DAC-

1 L421 ferrite_0603 1 L422 ferrite_0603 1 L423 ferrite_0603 1 L424 ferrite_0603 1

2 C455 0.1U_s

+3.3VA8 F24 C472 1U_s F25

UO_DAC_PSUPA UO_VBIAS

QAM_AGCI 1 1

OOB_VCO_POS OOB_VCO_NEG C456 0.1U_s C457 0.1U_s 2

2 C484 0.1U_s

+3.3VA9 +1.2VA1 +1.2VA2

C14 D14 A14 B14

T26 T22 D22 G24 D25 F22 L11 L12 L13 L14 L15 L16 M11 M12 M13 M14

DO_LO_VBB DO_LO_VDDB QFE_VPP VDD_PLL UO_DAC_PSUPD UO_QUIET_PSUPD VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS

DO_LO_BGND DO_LO_VSSB QFE_PGND VSS_PLL UO_DAC_NSUPD UO_QUIET_NSUPD VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS

R23 T23 C22

AUDIO_LEFT_POS AUDIO_LEFT_NEG AUDIO_RIGHT_POS AUDIO_RIGHT_NEG

D R475 470_s

2 C485 0.1U_s

+1.2VA3 +1.2VA4

G25 G26 D24 T16 T15 T14 T13 T12 T11 R16 R15 R14 R13 R12 A

QAM_AGCT 1

QVD_DV_A_P QVD_DV_B_P QVD_DV_C_P QVD_DV_D_P UO_PWR0_GATEB UO_PWR1_CLK UO_PWR2_DATA UO_PWR3

E17 B17 E16 B16 D26 C24 A24 B26

Place no traces or parts between AUDIO_LEFT_POS/AUDIO_LEFT_NEG and AUDIO_RIGHT_POS/AUDIO_RIGHT_NEG. Keep traces close in length and route traces next to one another. Surround each pair with DGND. Surround video trace DIG_COMPOSITE with DGND.

DIG_COMPOSITE

DAC A, C & D not used.

US_CTL_CSB US_CTL_CLK US_CTL_DATA

+1.2VA5 C486 0.1U_s

C475 0.1U_s

N25 N26

BTSC_ADC2_VIP BTSC_ADC2_VIN

D J24 J23 AVD_ADC1_VIP AVD_ADC1_VIN UO_RF_SD_OUT B23 TX_OEN

2 C487 0.1U_s

D18

AUD_DIGAUD (UO_IREFD) UO_DAC_BG_PSUPA QFE_ADC_VBGOUT QFE_EXT_IREF QVD_RBIAS QVD_VREF QVD_AVSS_BIAS QVD_AVSS_BIAS2

VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS

L410 ferrite_0603 +1.2V 1 L411 ferrite_0603

2

DI_ADC1_VREFN DI_ADC1_VREFP DI_ADC1_VCM BTSC_ADC2_VREFN BTSC_ADC2_VREFP BTSC_ADC2_VCM DO_ADC3_VREFN DO_ADC3_VREFP DO_ADC3_VCM

J26 H22 H23 M24 M23 M25 P24 P23 P25

2 C435 0.1U_s

M15 M16 N11 N12 N13 N14 N15 N16 P11 P12 P13 P14 P15 P16 R11

F23 H24 H25 D R472 8.06K_s 1% C473 0.1U_s R473 30.1K_s 1% R474 562_s 1% C474 0.1U_s C18 A18 C17 C16

L401 10uH_c_1008 ANA_1.2V C450 467639-001 10U_c 6.3V X5R 1206 See table page 1 A

1 L412 ferrite_0603 1 L413 ferrite_0603 1 L414 ferrite_0603 1

2 C436 0.1U_s

C492 C481 C493 C463 C464 C465 C466 C467 C471 1U_s 1U_s 1U_s 1U_s 1U_s 1U_s 1U_s 1U_s 1U_s

2 C437 0.1U_s

A D

2 C438 0.1U_s

2 C439 0.1U_s

VIDEO DAC CALCULATIONS Ioutfs = 17.4 mA with Rbias = 628 ohms Choose Rbias = 562 ohms Rload = 75 ohms (see video page) Dwhite = 364 (9 bit value) NTSC Dsync = 14 (9 bit value) NTSC Vout p-p = Ioutfs * (628 ohms / Rbias) * Rload * ((Dwhite - Dsync)/511) = 1 Vp-p

San Diego, California, USA. Title

Taipei, Taiwan, R.O.C.

QUAKE_ANALOG.SCH

Size Custom

A B C D

Document Number 864684-049

E

File Name Sheet 11 of 14

Rev A

Date: Friday, September 26, 2003

Audio DAC Filter and Output Amp

+5V R731 100K_s C721 22P_s 1 2 R727 8.25K_s 1% 1 R728 8.25K_s 1% D R729 47.5K_s 1% C720 270P_s 2 R730 47.5K_s 1% U700A NJM4580 128006-129-26 1 1% 1

Video DAC Filter and Output Amp

C719 0.1U_s +5V D DAC_AUD_LEFT R713 3.3K_s C739 100P_s D C718 0.1U_s C723 1 22P_s 2 2 DIG_COMPOSITE D 2 1 1 L700 6.8uH_c_0805 R702 20_s 1 R704 1K_s 1% C704 10P_s 1 2 R706 887_s 1% 3 3 2 1 LINE_OUT_LEFT REMOD_VIDEO R703 1.2K_s 2 3 Q702 2sc2712 R708 75_s 1% C707 100P_s D R705 510_s U700B NJM4580 128006-129-26 7 8 -5V 1 R707 1K_s 8 2

D

AUDIO_LEFT_POS

3 2

+ 4

2 Vrms at 0 dBFS.

-5V

C702 0.1U_s

AUDIO_LEFT_NEG

Place no traces or parts between AUDIO_LEFT_POS and AUDIO_LEFT_NEG. Keep traces close in length and route traces next to one another. Surround the pair of traces with digital ground plane.

R732 100K_s

1%

Q701 2sc2712 2

COMP_OUT

R735 100K_s C724 22P_s 1 2

1% +5V R700 102_s 1%

C700 270P_s 2

C701 150P_s 2

R701 280_s 1%

Q700 2sc2712

AUDIO_RIGHT_POS

R733 8.25K_s 1% 1 R734 8.25K_s 1%

R736 47.5K_s 1% R737 47.5K_s 1%

5 6

D DAC_AUD_RIGHT

+ -

C725 270P_s 2

2 Vrms at 0 dBFS.

-5V 1%

R714 3.3K_s C745 100P_s D

LINE_OUT_RIGHT C703 0.1U_s

AUDIO_RIGHT_NEG

2 D

Place no traces or parts between AUDIO_RIGHT_POS and AUDIO_RIGHT_NEG. Keep traces close in length and route traces next to one another. Surround the pair of traces with digital ground plane.

R738 100K_s

C726 22P_s 1 2

Video/Audio RF Modulator (Remod)

L803 4.7uH_c_0805 1 R806 150_s RES\1%\0603 3 2

REMOD_VIDEO

10%

2

F800 1 3 tps4_5mb2 C810 0.01U_s R804 2 2K_POT 118874-513-14

R805 560_s A 1

Loop Filter must be as close as possible to pins 14&15

C808 R803 2.2K_s

R807 10K_s CH3/4_SEL C815 0.1U_s U800 R741 2K_s 1% DAC_AUD_LEFT REMOD_AUDIO R742 2K_s 1% DAC_AUD_RIGHT R810 1K_s C821 1000P_s R743 1.3K_s 1% 3 1 Y800 R809 2 50K_POT C818 Must be X7R 1U A 4MHz C816 27P_s A 1 2 3 4 6 7 8 9 CHS PSS LOP XTAL PREEM AUDIO SPLFLT PS/LO

A 0.047U_s

C809 0.022U_s C807 0.01U_s 1 L801 120nH_c_0603 2 L800 150nH_c_0603 1 2 C803 7P_s R802 470_s C804 36P_s A L1119 10uH_c_1008 A C802 43P_s A A A R800 470_s L804 3.3uH_c_1210 R801 27_s C800 0.01U_s REMOD_OUT

2 Vrms at 0 dBFS.

1.132 Vrms at 0 dBFS

X7R

C820 0.1U_s A

SFS PLLFLT TVOUT VIDEO TVOVCC VCCA GND GND

16 15 13 10 14 11 5 12

C805 9P_s +5V

2 Vrms at 0 dBFS.

mc44bc375u C817 750P_s 5%, NPO

Lowpass filter, F3dB = 159 kHz

D C819 0.022U_s R808 7.5K_s A

C814 A 1000P_s

C813 0.01U_s

C812 0.1U_s

C1142 +

C822 D800 smbj13 2 0.1U_s

MC44BC375U data sheet: 85% FM modulation at 1 kHz with 205 mVrms input at pin 7, with pre-emphasis. Pre-emphasis gain at 1 kHz = 0.87 dB. 100% modulation = +/- 25 kHz. To achieve +/- 50 kHz FM modulation (200%) without pre-emphasis, the nominal input level at pin 7 is: 2*(205 mVrms)*(0.87 dB)/(85%) = 534 mVrms. The digital audio level at the top end of R853 must be greater than 534 mVrms in order to achieve alignment. Target value = 566 mVrms for analog channel and 1132 mVrms for digital channel.

Change to surface mount. TDK part NLFV25T-100K.

10uf_01 2

A A A

San Diego, California, USA. Title

Taipei, Taiwan, R.O.C.

AUDIO_VIDEO.SCH

Size C Document Number 864684-049 Sheet

1

File Name 12 of 14

Rev A

Date: Friday, September 26, 2003

5 4 3 2

+5VA_OOB +5V L1106 10uH_c_1008 +5VA_IB 1 1 1 C1109 + 501442-002 10V Y5V 0805 See table page 1.

QAM IF SAW Filter and AGC Amp

C1107 0.1U_s 2 2

C1108 0.01U_s 2

10uf_01

60 MHz Lowpass Filter

A C1104 0.01U_s 1 2 R1101 499_s 1% L1104 1.5uH_c_0603 10% L1102 1.5uH_c_0603 10% L1100 1.5uH_c_0603 10% IB_IF_POS TP1100 IB_IF_POS 1 1 1 1 R1100 1K_s 1% IB_IF_NEG

4

TP1104 10 14 AGC_VCC F1100 QAM_IF+ QAM_IFTUNER_IF 1 2 IN ING CHIP POUT1 POUT2 3 4 5 SAW_IF_POS SAW_IF_NEG 1 16 IF_IN+ IF_INU1100 12 VCC 5 VCC

DRV_AMP_VCC

IF_OUTIF_OUT+

9 8 C1105 0.01U_s 1 2 R1102 499_s 1% 2

C1103 5P_s 2 L1105 1.5uH_c_0603 10%

C1102 9P_s 2 L1103 1.5uH_c_0603 10%

C1101 9P_s L1101 1.5uH_c_0603 10% 2

C1100 5P_s

x6964m A QAM_AGCI 1 C1110 0.1U_s TP1103 QAM_AGCI 2 A 11 3 4 AGC_IN AGC_SW

LA7783

469774-001-28

AGC_OUT1 AGC_OUT2

13 6

Inductors are TDK MLF1608 series

TP1102 AGND

TP1101 IB_IF_NEG Table 1 C1100 C1102 L1100 L1102 L1104

DELAY_ADJ GND GND GND

C1101 Do not install C1103 Do not install L1101 0 ohm resistor L1103 0 ohm resistor L1105 0 ohm resistor R1100 1000 ohms 1% R1101 R1102 499 ohms 1%

15

+5VA_OOB

+5VA_OOB

3

149188-018 F1101

OOB Tuner

5 4 3

POUT2 POUT1 SOUT

CHIP IN

2 1

saf49_10mc220z

L1108 100nH_c_0603 L1109 100nH_c_0603 1 C1121 0.01U_s 2 1 C1120 0.01U_s A 1 19 20 21 22 14 Keep the bypass capacitors very close to the pins of the LA7784 1 1 C1123 0.1U_s 2 2 TP1105 OOB_IF_POS

2

A 70 to 130 mhz LPF. Helps to reduce LO leakage and also reject signals above 130 MHz. C1133 9P_s 1 2 L1112 220nH_c_0603 OOB_TAP 1 2 L1110 should be changed by new part number 1 1 C1128 0.01U_s 1 2 C1130 6P_s 2 R1105 75_s 1 27 23 2 24 C1129 0.01U_s 16 17 A A 9 C1131 5P_s 1 2

R1103 51_s R1104 51_s 4 5 C1127 0.01U_s 2 A

VCC_MIX_LO

VCC_POST_AMP

VCC_LNA

VCC_DRIVER

VCC_LNA

IF_IN1

IF_IN2

VCC_IF

L1111 100nH_c_0603

L1110 120nH_c_0603

C1124 1000P_s 2

C1122 0.1U_s

26

MIX_OUT1 MIX_OUT2 RF_IN1 RF_IN2 LO_IN1 LO_IN2

L1112 should be changed by new part number

C1134 11P_s 2 A

C1132 12P_s

U1101 LA7784

471105-001-32 OUT1 OUT2 12 13

C1125 0.1U_s 1 2

OOB_IF_POS

NC_GND

NC_GND

NC_GND

NC_GND

180 MHz Lowpass Filter

R1109 23.7_s 1% L1117 27nH_c_0603 L1115 27nH_c_0603 L1113 27nH_c_0603 C1135 0.01U_s 1 2

AGC_IN

NC_GND

C1126 0.1U_s 1 2 GND GND

Note 3

OOB_IF_NEG TP1106 OOB_IF_NEG

GND

GND

GND

GND

OOB_VCO_POS

TP1107 AGND

10

11

15

18

25

See note 3

R1110 23.7_s 1%

C1140 27P_s

C1139 47P_s

C1138 47P_s

C1137 27P_s

R1107 49.9_s 1%

See note 3

C1136 0.01U_s 1 2 A

OOB_VCO_NEG

L1118 27nH_c_0603

L1116 27nH_c_0603

L1114 27nH_c_0603

Inductors are TDK MLG1608 series

Notes :

TP1108 OOB_AGC OOB_AGC 1 C1141 0.1U_s 2

1. Use 0603 chip caps and resistors. 2. LA7784 Batwings must be connected to ground. 3. Keep these 2 traces very close to each other. Don't route under bypass caps. Don't place any trace between them.

1

28

San Diego, California, USA. Title

Taipei, Taiwan, R.O.C.

AFE.SCH

Size C Document Number 864684-049 File Name Sheet

E

Rev A 13 of 14

Date: Friday, September 26, 2003

A B C D

15.8, 1% 35.7, 1%

+5V_TUNER

C525 1000P_s A 1

R519 120_s R520 1.2K_s C524 120P_s 1 Q501 2sc5227_5 1 1 L511 150nH_c_0603 2

L513 120nH_c_0603

L512 390nH_c_1008

C526 470P_s OOB_TAP C527 2P_s

R522 4.7_s

R521 470_s

A 16 15 14 13 S501 A

E500

70 MHz Highpass Filter

C536 33P_s C534 22P_s C532 22P_s 1 QAM_AGCT C535 390P_s 1 1 C533 150P_s R501 1K_s 3 C501 0.1U_s

TUNER1 TDEZ1X002A +5V_TUNER RF_IN AGC OPEN +5V 2 10 13 14 15 16 A A C538 27P_s C540 18P_s SCLK SDA R500 5 6 7 SCL SDA AS 150_s GND IF11 QAM_IFA GND GND GND GND GND GND IF+ 9 4 1 1 2 L500 1uH_c_1008 C500 0.1U_s 1 2 3 4 GND GND GND GND

RF_conn

GND GND GND GND

GND GND GND GND GND GND GND GND

12 11 10 9

Place close to the ALPS TUNER

A 5 6 7 8 QAM_IF+ Diplexer shield

R523 1M_2010

L517 100nH_c_1008

L516 120nH_c_1008

2 12 A

42 MHz Lowpass Filter

3

L518 390nH_c_1008 1 2 1

L519 390nH_c_1008 2 1

L520 270nH_c_1008 2 1

L521 270nH_c_1008 2 1 C542 39P_s UPSTREAM

8 A L522 27uH_r 21 D500 smbj13 2 A +5V SCLK SDA L523 10uH_c_1008 1 1 + C557 470u_10v 2 2 C556 0.1U_s +5V_TUNER 467639-001 6.3V X5R 1206 C558 10U_c

C537 100P_s

C539 100P_s

C541 82P_s

Place these parts near QUAKE.

TUNER_SCLK TUNER_SDA R504 R505 470_s 470_s R502 R503

Place these parts near tuner IC.

470_s 470_s

C564 100P_s

C563 100P_s

C560 100P_s

C559 100P_s

C555 1000P_s

C554 1000P_s

C553 1000P_s

A R526 0_s

A

2

Option Table 1

R603 R604 Anadigics ARA2018 Sanyo LA7791T Microtune MT1530 35.7, 1% 13.0, 1% 15.8, 1% L608 L609 180nH 56nH 82nH L606 L607 220nH 56nH 100nH L604 L605 180nH 56nH 82nH C614 56pF 120pF 120pF C613 100pF 330pF 220pF C612 100pF 330pF 220pF C611 56pF 120pF 120pF R600 93.1, 1% 26.1, 1% 31.6, 1% C603 15pF 6800 pF DNI C604

D

270pF 0.1uF 0.1uF

+5V_US 12 18 5

Upstream Amp

U600 la7791t /SHDN TXEN VIN+ GND2 VCC2 C608 0.01U_s NC VOUT+ C609 0.01U_s 6 2 VINVOUTVCC1 GND1 NC GND GND VCM NC DGND SCLK SDA /CS 20 19 17 16 15 14 13 7 10 9 8 RP600 A US_CTL_CSB US_CTL_DATA US_CTL_CLK C610 0.1U_s 1 2 3 4 33_4_S 8 7 6 5 C604 A

+5V_US C602

JET

0.1U_s A

C615 0.01U_s TX_DAC+

L608 56nH_c_0603

L606 56nH_c_0603

L604 56nH_c_0603

R601 0_s R600 26.1_s

TX_OEN

C603 6800P_s SEE OPTION TABLE 1

C616 0.01U_s TX_DAC-

C614 120P_s L609 56nH_c_0603 SEE OPTION TABLE 1

C613 330P_s L607 56nH_c_0603

C612 330P_s L605 56nH_c_0603

C611 120P_s

A +5V_US

1 T600 6 2 3 C601 0.1U_s 4 458pt_1087 463131-001 A C600 1000P_s UPSTREAM

0.1U_s

R602 0_s

4 11 3 1 +5V_US

SEE OPTION TABLE 1

Inductors are TDK MLG1608 series

R604 13_s 1%

1

R603 13_s 1% A

A A

1

SEE OPTION TABLE 1

C607 0.01U_s 2 2

C606 0.01U_s 2

1 C605 0.01U_s DNI San Diego, California, U.S.A. Title Taipei, Taiwan R.O.C.

+5V

L610 10uH_c_1008

+5V_US

+ C617 470u_10v 2

TUNER_UPSTREAM.SCH

A Document Number 864684-049 Date: Friday, September 26, 2003

B C D E

File Name Sheet 14 of 14

Rev A

S-ar putea să vă placă și

- 6L80E ManualDocument6 pagini6L80E ManualLeysser Josue67% (3)

- Offshore Electrical Engineering ManualDe la EverandOffshore Electrical Engineering ManualEvaluare: 4 din 5 stele4/5 (9)

- 17-4658 LT-650Document436 pagini17-4658 LT-650jose juanÎncă nu există evaluări

- Notebook Cce w52 Ecs U50si1 - 37gu50100-C1 IDocument32 paginiNotebook Cce w52 Ecs U50si1 - 37gu50100-C1 IRicardo GonçalvesÎncă nu există evaluări

- Service Manual For DELL Inspiron 8600 576d026223 Dell Inspiron 8600 (Compal)Document58 paginiService Manual For DELL Inspiron 8600 576d026223 Dell Inspiron 8600 (Compal)Ricardo OlivaresÎncă nu există evaluări

- LCD Monitor - DC - XL2720TZ - 20130805 - 144041 - 5E.23A01.011 (4H.23A01.S11)Document12 paginiLCD Monitor - DC - XL2720TZ - 20130805 - 144041 - 5E.23A01.011 (4H.23A01.S11)pasmanteriabella100% (1)

- Philips 32pfl5404 Chassis Tpm3.1e La (ET)Document84 paginiPhilips 32pfl5404 Chassis Tpm3.1e La (ET)varimasÎncă nu există evaluări

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsDe la EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsÎncă nu există evaluări

- Dga 1000 PartsDocument20 paginiDga 1000 Partswaltech2005Încă nu există evaluări

- 2003-2009 Renault Megane II Fuse Box Diagram Fuse DiagramDocument12 pagini2003-2009 Renault Megane II Fuse Box Diagram Fuse Diagramwaltech2005100% (1)

- PCM Windstar 97Document3 paginiPCM Windstar 97waltech2005100% (1)

- TR200 Surface Tester ManualDocument3 paginiTR200 Surface Tester Manualprasadjoshi781429Încă nu există evaluări

- Service Manual: MODEL: MACRO830/1400/2400Document38 paginiService Manual: MODEL: MACRO830/1400/2400Osmar ContreirasÎncă nu există evaluări

- U50SI1 Schematics Rev:C: ContentDocument32 paginiU50SI1 Schematics Rev:C: ContentshibilvÎncă nu există evaluări

- U 50 Si 1Document32 paginiU 50 Si 1wotanelÎncă nu există evaluări

- 08.wiring DiagramDocument8 pagini08.wiring Diagramconnectingeurope8479Încă nu există evaluări

- Philips Chassis Tpm5.2e-LaDocument59 paginiPhilips Chassis Tpm5.2e-Larolandas1970Încă nu există evaluări

- Acer Jm31 Inventec GerberDocument36 paginiAcer Jm31 Inventec GerberWade DyerÎncă nu există evaluări

- Philips Chassis Tpm9.1e LaDocument91 paginiPhilips Chassis Tpm9.1e LaDejan Miladinovic100% (2)

- gs11 - New sc2 - MaDocument16 paginigs11 - New sc2 - MaMitesh ChauhanÎncă nu există evaluări

- Delta Dac-19m008 Tea1532 Oz964 Dac12m035Document55 paginiDelta Dac-19m008 Tea1532 Oz964 Dac12m035Carlos A. TorresÎncă nu există evaluări

- Solar Panel Inverter Schematic V2.3Document6 paginiSolar Panel Inverter Schematic V2.3Amanda PalmgrenÎncă nu există evaluări

- DRV 8801Document27 paginiDRV 8801Rian PermanaÎncă nu există evaluări

- Hawkboard Schematics v1Document11 paginiHawkboard Schematics v1Sam KhawseÎncă nu există evaluări

- Hws 13642Document3 paginiHws 13642dhieward100% (2)

- HP Compaq Presario CQ62 FOXCONN Safina RevMVDocument40 paginiHP Compaq Presario CQ62 FOXCONN Safina RevMVLolitassAssÎncă nu există evaluări

- q45 - rampAPPLE 台式G5线路图.bakDocument74 paginiq45 - rampAPPLE 台式G5线路图.bakmarkbillupsÎncă nu există evaluări

- Samsung Hlp4663wx Xaa CH l62b-n AtlantisDocument80 paginiSamsung Hlp4663wx Xaa CH l62b-n AtlantisVinicius MarcosÎncă nu există evaluări

- ®MCI Electronics WWW - Olimex.cl: 3V3 3V3 RssiDocument1 pagină®MCI Electronics WWW - Olimex.cl: 3V3 3V3 Rssiefx8100% (1)

- PHILIPS LCD Ch-10.1L LLA-32PFL3605D-40PFL3605D PDFDocument71 paginiPHILIPS LCD Ch-10.1L LLA-32PFL3605D-40PFL3605D PDFAlecsandro BatistaÎncă nu există evaluări

- 32HFL4441D27Document126 pagini32HFL4441D27Jim HarmkeÎncă nu există evaluări

- LQ043T3DX02 SP 122805 PDFDocument25 paginiLQ043T3DX02 SP 122805 PDFrootyÎncă nu există evaluări

- Olevia LT26HVX LCD TV Service ManualDocument35 paginiOlevia LT26HVX LCD TV Service ManualFrancisco OrozcoÎncă nu există evaluări

- LCD Grafico Wg12864aDocument25 paginiLCD Grafico Wg12864aseykarimÎncă nu există evaluări

- Compal La-4241p Jhxxx-Rev 0.4Document49 paginiCompal La-4241p Jhxxx-Rev 0.4Neo ValeÎncă nu există evaluări

- LCD Monitor - DC - XL2420TX - 20120302 - 150546 - 5E.1M001.002 (4H.1M001.A00)Document11 paginiLCD Monitor - DC - XL2420TX - 20120302 - 150546 - 5E.1M001.002 (4H.1M001.A00)pasmanteriabellaÎncă nu există evaluări

- Samsung Np300 Scala3-14r Gl1.1 Eco 0925Document51 paginiSamsung Np300 Scala3-14r Gl1.1 Eco 0925Hernan Acosta75% (4)

- Compal La-9981p r0.2 SchematicsDocument56 paginiCompal La-9981p r0.2 SchematicsLeandro OliveiraÎncă nu există evaluări

- 100G - CFPZR10 - Sofp1-Zr-80Document84 pagini100G - CFPZR10 - Sofp1-Zr-80lina zhengÎncă nu există evaluări

- JVC Gr-Df470us SCHDocument54 paginiJVC Gr-Df470us SCHsonny_boy35_51147747Încă nu există evaluări

- LCD Grafico 128X64 KS108 VerdeDocument12 paginiLCD Grafico 128X64 KS108 VerdeFrancisco SantosÎncă nu există evaluări

- Asus EeePC 1000HE Schematic DiagramsDocument48 paginiAsus EeePC 1000HE Schematic DiagramsMicu Adrian DanutÎncă nu există evaluări

- 5 KVA UPS Docs (HI-REL) PDFDocument53 pagini5 KVA UPS Docs (HI-REL) PDFMohan Kulkarni75% (4)

- Asus Eepc SCHDocument48 paginiAsus Eepc SCHFlorin CarareÎncă nu există evaluări

- 1000HE - MB: Clock Gen CPUDocument48 pagini1000HE - MB: Clock Gen CPUEmidio SouzaÎncă nu există evaluări

- PHILIPS Chassis QM14.3E LA PDFDocument98 paginiPHILIPS Chassis QM14.3E LA PDFboroda2410Încă nu există evaluări

- Acer I5 47501306462469980Document67 paginiAcer I5 47501306462469980fdsaq12Încă nu există evaluări

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2De la EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Încă nu există evaluări

- Power Systems-On-Chip: Practical Aspects of DesignDe la EverandPower Systems-On-Chip: Practical Aspects of DesignBruno AllardÎncă nu există evaluări

- Power Supply Projects: A Collection of Innovative and Practical Design ProjectsDe la EverandPower Supply Projects: A Collection of Innovative and Practical Design ProjectsEvaluare: 3 din 5 stele3/5 (2)

- Radio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142De la EverandRadio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142Încă nu există evaluări

- Arduino Measurements in Science: Advanced Techniques and Data ProjectsDe la EverandArduino Measurements in Science: Advanced Techniques and Data ProjectsÎncă nu există evaluări

- Transistor Electronics: Use of Semiconductor Components in Switching OperationsDe la EverandTransistor Electronics: Use of Semiconductor Components in Switching OperationsEvaluare: 1 din 5 stele1/5 (1)

- Beginning Digital Electronics through ProjectsDe la EverandBeginning Digital Electronics through ProjectsEvaluare: 5 din 5 stele5/5 (1)

- Digital Signal Processing Using the ARM Cortex M4De la EverandDigital Signal Processing Using the ARM Cortex M4Evaluare: 1 din 5 stele1/5 (1)

- Nissan Altima: Motor 3.5L Vq35De CODIGOS P0011 y P0021Document9 paginiNissan Altima: Motor 3.5L Vq35De CODIGOS P0011 y P0021waltech2005Încă nu există evaluări

- Checklists 1yrDocument2 paginiChecklists 1yrAdi BauÎncă nu există evaluări

- Mos Field Effect Transistor: Switching N-Channel Power Mos FetDocument9 paginiMos Field Effect Transistor: Switching N-Channel Power Mos Fetwaltech2005Încă nu există evaluări

- Pic 16f870 Data SheetDocument172 paginiPic 16f870 Data SheetPedro BugueñoÎncă nu există evaluări

- TL 489 CDocument5 paginiTL 489 Cwaltech2005Încă nu există evaluări

- Cad System For UlaDocument7 paginiCad System For Ulawaltech2005Încă nu există evaluări

- AW 50-42 Valve BodyDocument8 paginiAW 50-42 Valve BodyHR Mecanica Integral75% (4)

- Instructors' Solutions For Mathematical Methods For Physics and Engineering by RileyDocument512 paginiInstructors' Solutions For Mathematical Methods For Physics and Engineering by Rileyastrowiz8813% (8)

- ND BRG GuideDocument32 paginiND BRG Guidemohammed barghothiÎncă nu există evaluări

- Risk Assesment-Rebar Loading & UnloadingDocument1 paginăRisk Assesment-Rebar Loading & Unloadingmainraj rajÎncă nu există evaluări

- Fundamentals of The Automotive Cabin Climate Control SystemDocument6 paginiFundamentals of The Automotive Cabin Climate Control SystemSeddik MaarfiÎncă nu există evaluări

- Chapter 11Document38 paginiChapter 11Ismail HussainÎncă nu există evaluări

- A Project Report On Financial Performance Evaluation With Key Ratios at Vasavadatta Cement Kesoram Industries LTD Sedam Gulbarga PDFDocument82 paginiA Project Report On Financial Performance Evaluation With Key Ratios at Vasavadatta Cement Kesoram Industries LTD Sedam Gulbarga PDFK Sagar Kondolla100% (1)

- LCD and TV Repair GuideDocument195 paginiLCD and TV Repair GuideUlisesMartin79% (14)

- Full Analyse of JULIADocument19 paginiFull Analyse of JULIArenan55026Încă nu există evaluări

- 7749289-TheClandestineChemist 'Snotebook PDFDocument28 pagini7749289-TheClandestineChemist 'Snotebook PDFTonÎncă nu există evaluări

- Engine - Activity - Lab - Sheet Rev.ADocument5 paginiEngine - Activity - Lab - Sheet Rev.AAvery KarevÎncă nu există evaluări

- Apache MyFaces Trinidad - Skin SelectorsDocument25 paginiApache MyFaces Trinidad - Skin SelectorsJorge LavadoÎncă nu există evaluări

- History of UASDocument44 paginiHistory of UASAswin BalasubramaniamÎncă nu există evaluări

- Truebluepower: Advanced Lithium-Ion Battery TB17Document2 paginiTruebluepower: Advanced Lithium-Ion Battery TB17Milad YadollahiÎncă nu există evaluări

- Moi PDFDocument3 paginiMoi PDFSACHINÎncă nu există evaluări

- 5.2.1 Red AlertsDocument4 pagini5.2.1 Red AlertsCursedDiamondsÎncă nu există evaluări

- Case/Duct System (Automobile)Document7 paginiCase/Duct System (Automobile)Tran xuan ThuyÎncă nu există evaluări

- Liebherr Hydraulic Components For Heavy Duty On Highway Engines Application Flyer Es WebDocument4 paginiLiebherr Hydraulic Components For Heavy Duty On Highway Engines Application Flyer Es WebDaniel Castillo PeñaÎncă nu există evaluări

- Foundation Engineering Shot NotesDocument21 paginiFoundation Engineering Shot NotesSejal VermaÎncă nu există evaluări

- Sample Letters To DEPDocument7 paginiSample Letters To DEPSJLibraryÎncă nu există evaluări

- Brochure Tialoc Chemical Resistant Piping Systems: Page 1 of 20Document20 paginiBrochure Tialoc Chemical Resistant Piping Systems: Page 1 of 20Fernando Cesar PérezÎncă nu există evaluări

- Belden 9463 PDFDocument3 paginiBelden 9463 PDFtr0184Încă nu există evaluări

- Quantum Multiport PackerDocument1 paginăQuantum Multiport Packersmithyry2014Încă nu există evaluări

- Cloud Whitebook Cloud White BookDocument60 paginiCloud Whitebook Cloud White BookeevengÎncă nu există evaluări

- En 19Document3 paginiEn 19Sanjay GoreÎncă nu există evaluări

- Edgen Murray ProductsDocument20 paginiEdgen Murray Productsafiqaziz86Încă nu există evaluări

- Unit - 2 Diff Amp Objective QuestionsDocument3 paginiUnit - 2 Diff Amp Objective QuestionsRaviÎncă nu există evaluări

- BB Session - Me132p - Lecture 2 KD and DofDocument31 paginiBB Session - Me132p - Lecture 2 KD and Dofkris garciaÎncă nu există evaluări

- CS412, Fall 2010, Assignment 1: SolutionDocument8 paginiCS412, Fall 2010, Assignment 1: SolutionpeacekentÎncă nu există evaluări