Documente Academic

Documente Profesional

Documente Cultură

16/32 BIT Microcontroller: TLCS-900

Încărcat de

Cesar SaucedoDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

16/32 BIT Microcontroller: TLCS-900

Încărcat de

Cesar SaucedoDrepturi de autor:

Formate disponibile

TLCS-900

16/32 BIT MICROCONTROLLER TLCS-900 Family TOSHIBA

CES_16BIT_V1.2 *

TOSHIBA

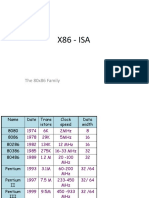

TLCS-900 64-bit 32-bit

CPU-CORE LINE UP

R5900 R3900 R1900 TLCS-900/H2 R3000A

R4400 R4600

16-bit

68000 ASSP 68HC000

TLCS-900/L1 TLCS-900/L TLCS-870 Std/ X/ C

TLCS-900/H TLCS-900

8-bit 4-bit

68HC11 68HC05

TLCS-90

Z80 ASSP

TLCS-47E/47/470470A

ALLIANCE

CES_16BIT_V1.2

TOSHIBA ORIGINAL

*

ALLIANCE TOSHIBA

TLCS-900

The Family Key Features

CPU-core : 16/32 Bit High-speed processing,

Min. inst. exec. time:

200ns (@10MHz) - TLCS-900,900/L 160ns (@12.5MHz) - TLCS-900/H,900/L1 50ns ((@20MHz) - TLCS-900/H2

Large linear address space (16M bytes) Powerful instruction set

Regular instruction sets and many addressing modes

Many bit-processing operations Powerful real-time processing

using register banks

High-speed data transfer using DMA For systems using both 8- and 16-bit buses

dynamic bus sizing function

CES_16BIT_V1.2

TOSHIBA

TLCS-900

CPU CORES

CES_16BIT_V1.2

TOSHIBA

TLCS-900

The Road Map

[MIPS] TLCS-900/H2 4 times performance of TLCS-900/H

PERFORMANCE

10

High performance

TLCS-900/H TLCS-900/L1

Mnemonic Compatible

Z80

TLCS-900

TLCS-900/L

* TLCS-900,900/L,900/H devices will be

object compatible with TLCS-900/H2 Family.

Standard

TLCS-90 Upward Compatible

Low Power

8-bit

16-bit

32-bit

CES_16BIT_V1.2

TOSHIBA

TLCS-900

The Family Key Features

ITEM Max. operating frequency (external) Min. instruction cycle time uDMA Speed MULA instruction Dynamic Bus Sizing

H2 20 MHz (@10 MHz) 50 nsec 0,25 usec 0.6 usec 8/16/32 Bit

H & L1 12.5 MHz (@25 MHz) 160 nsec

Stand.& L 10 MHz (@20 MHz) 200 nsec

0,64 usec 1,6 usec 1.52 usec 3.1 usec 8/16 Bit

CES_16BIT_V1.2

TOSHIBA

TLCS-900

LOW VOLTAGE OPERATION

CES_16BIT_V1.2

TOSHIBA

TLCS-900

TLCS-900/L Low power consumption

ICC [mA] 50 40 30 20 10 TLCS-900 (TMP96CM40F)

1 2 TLCS-900/L (TMP93CM40F) Ta = 25 oC

(5V,20MHz)

(5V,20MHz)

(3V,12.5MHz)

CES_16BIT_V1.2

TOSHIBA

TLCS-900

TLCS-900/L1 Low power consumption

ICC [mA] 20 15

19 mA

1 3 1 2

(3V,16MHz, Ta = 25 oC)

6 mA

10 5

3 mA

TLCS-900/H 0.6um

TLCS-900/L1 0.6 um

TLCS-900/L1 0.4 um

CES_16BIT_V1.2

TOSHIBA

TLCS-900

Gear Power Consumption per Software

Icc [mA]

10 Prescaler

1 2 3

<TMP93CM40F> Vcc = 3 V Ta = 25 oC

8 6

Gear Ratio

1/1

fc

fc/16 fc/8 Selector fc/4 fc/2 fc

4 2

1/2 1/4 1/8 1/16 4 6 8 10 12 14 [MHz]

fc

CES_16BIT_V1.2 *

TOSHIBA

TLCS-900

TLCS-900/L : DUAL CLOCK SYSTEM

Reset Reset Release IDLE mode 1 or 2 Software Interrupt NORMAL mode (20MHz) Clock Gear Release Software Software Interrupt Software Release IDLE mode 1 or 2 SLOW mode (32kHz) Software STOP mode

Software

CES_16BIT_V1.2

TOSHIBA

TLCS-900

The operation modes

TLCS-900/L : 4 types of Stand-by mode

Operation mode NORMAL RUN IDLE2 IDLE1 STOP CPU A/D C Peripheral I/O

(Timer,SIO)

[mA]

<TMP93CM40F>

(

Oscillator

10

Vcc=3V Ta =25 C

o x x x x

o o x x x

o = operate x = stop

o o o x x

o o o

8 Normal Icc 6

RUN

o x

2

IDLE2

IDLE1 STOP 4 6 8 10 fc 12 14 [MHz]

CES_16BIT_V1.2

TOSHIBA

TLCS-900

HIGH SPEED OPERATION

CES_16BIT_V1.2

TOSHIBA

TLCS-900

TLCS-900/H Performance 2 x TLCS-900

Method

Dual bus 32 bit ALU 4bit barrel Shifter Operand Size

Improving Target

Instruction

8bit

TLCS-900 4

16bit

4

32bit

4

Trasnfer Oper. LD reg,reg Arithmetic Oper.

reg,reg MULA reg,reg Logical Oper. RLC 4,reg

2 TLCS-900/H 2 4

C-compiler Performance Improvement

7

2 19

4 31

Filter Calculation Graphical Processing Floating Point Operation

14

14

16

< Comparison table of states >

CES_16BIT_V1.2 *

TOSHIBA

TLCS-900

THE 32 BIT TLCS-900/H2 CSIC like RISC

CES_16BIT_V1.2

TOSHIBA

TLCS-900

Core comparison H V H2

CSIC like RISC

High Performance with RISC Technology

900/H2 900/H

Minimum Execution Instruction Time 50ns Internal Clock Frequency Clock Per Instruction Internal Data bus External Data bus Performance Ratio 20MHz 1 CPI 32 32 4

160ns 12.5MHz 2 CPI 16 16 1 TOSHIBA

CES_16BIT_V1.2

TLCS-900

CPU - CORE Architecture

CES_16BIT_V1.2

TOSHIBA

TLCS-900

The register configuration (1)

Maximum Mode

Optimum for systems with program capacity above 64K bytes

Program counter: 32 bits (lower 24 bits are output as address bus)

Large capacity data space

16Mbyte addressing can be specified by any general-purpose register

32-bit transfer / arithmetic can be executed by general-purpose register High Speed image processing/address calculation,etc

CES_16BIT_V1.2

TOSHIBA

TLCS-900

The register configuration (1)

XWA XBC XDE XHL XIX XIY XIZ XSP W WW B B B D D D H H H IX IY IZ SP F MAXIMUM MODE Program & Data : 16M A C E L A C E L A C E L 4 BANKS

(For System Mode) (For Normal Mode)

SR PC

16 bits 32 bits

CES_16BIT_V1.2

TOSHIBA

TLCS-900

The register configuration (2)

Minimum Mode

Optimum for systems with program capacity less than 64K bytes

Program counter: 16 bits

Large number of bank registers

16 bits x 4 registers x 8 banks

Large data capacity

Expandable up to 16M bytes Accessible to data area above 64K bytes using XIX, XIY, XIZ, XSP registers

Capable of addressing with WA, BC, DE, HL, registers.

CES_16BIT_V1.2

TOSHIBA

TLCS-900

The register configuration (2)

MINIMUM MODE Program : 64K Data : 16M WW W WW B B W B A A W B W B B AD D D B C C D D B CH H H D D E E H H D E H H L L H L IX IY IZ SP A C E L A C E L A C E L A C E L A C E L

XIX XIY XIZ XSP

8 BANKS

(For System Mode) (For Normal Mode)

SR PC

16 bits 32 bits

CES_16BIT_V1.2 *

TOSHIBA

TLCS-900

Instruction set examples

Filter operation instruction

MULA: 16 Bits x 16 Bits/32 Bits-32Bits (3.1us @ 20MHz) (signed multiplication-addition arithmetic) MINC: Modulo increment...For circulating buffer pointer increment (Increments lower n bit only. 1 <= n <= 16) MDEC: Modulo decrement...For circulating buffer pointer decrement (Decrements lower n bit only. 1 <= n <= 16)

Logical operation instructions

AND/OR/XOR: And/or/exclusive-or of 8, 16, and 32 bits

CES_16BIT_V1.2

TOSHIBA

TLCS-900

Instruction set examples

continued.......

Bit operation instructions

BIT/SET/RES/CHG: Bit test/set/reset/invert LDCF/STCF: and any given bit Transfer between carry flag ANDCF: And of carry flag and any given bit ORCF: Or of carry flag and any given bit XORCF: Exclusive-or of carry flag and any given bit BS1: Searches bit pattern for 1.

CES_16BIT_V1.2

TOSHIBA

TLCS-900

High -Speed Processing

Family 900 & 900/L 10 MHz Instruction LD r, #8 LD XHL, xrr AND XHL, (mem) ADD HL, rr SET b, (mem) MUL HL, #16 DIV XHL, #8 MULA rr CALL #24 JP #24 200ns 400ns 400ns 700ns 800ns 2.6s 3.0s 3.1s 1.2 s 700 ns

900/H & 900/L1 12.5 MHz 160 ns 160 ns 320 ns 160 ns 560 ns 1.2 s 1.84 s 1.52 s 800 ns 480 ns

900/H2 20 MHz

Function

50 ns 50 ns 100 ns 50 ns 200 ns 450 ns 650 ns 600 ns 200 ns 100 ns

8-bit transfer 32-bit transfer 16-bit operation 32-bit operation bit set 16 bits * 16 bits 32 bits / 16 bits 16*16 +32 bits Direct Call Direct Jump

CES_16BIT_V1.2

TOSHIBA

TLCS-900

The memory map

000000H

Built-in I/O

000080H 000100H

(n)

256 byte

64k byte

16M byte

Internal RAM

(n n) 008000H 008200H (8100H 900/L)

Reset//Interrupt entry Internal ROM

(R) (-R) (R+) (R+d) (R+R) (n n n)

010000H

FFFFFFH

900/L 256 byte reserved

CES_16BIT_V1.2

TOSHIBA

TLCS-900

The Interrupt (1)

Priority level (0 to 7) can be set for each interrupt source. Non-maskable interrupts

Software interrupts (SWI0 to 7) NMI pins Watchdog timer Privileged or undefined instruction violation

Maskable interrupts

External pins (INT 0,1,2,..) Internal I/Os: DMA Timer SIO A/D converter

CES_16BIT_V1.2

TOSHIBA

TLCS-900

High-speed DMA

DMA implemented using CPU block executed directly from microcode Speed equivalent to DMA controller

1- 2- byte transfer: 1.6us (@20MHz) TLCS-900,900/L 640ns (@25MHz) TLCS-900/H

Supports 4-channels, 16Mbyte address space Maximum number of transfer blocks: 64k words Many transfer modes:

1) I/O to memory : bytes 2) I/O to memory : bytes 3) memory to I/O : bytes 4) memory to I/O : bytes 5) I/O to I/O : bytes (R+ (R(R) (R)

CES_16BIT_V1.2

TOSHIBA (R)

TLCS-900

The Interrupt (2)

Interrupt Data transfer uDMA Read interrupt vector clear interrupt request F/F PC=V+8000H Count = count-1 - Push PC, - PUSHSR - SR<IFF2~0> > accept int level +1 - SR<SYM> =1

YES YES

Count = 0

NO

uDMA start Vector match

Interrupt service routine

RETI (POP SR) POP PC)

NO

END

CES_16BIT_V1.2

TOSHIBA

TLCS-900

PERIPHERALS

CES_16BIT_V1.2

TOSHIBA

TLCS-900

The Peripherals

ROM/ OTP/FLASH

CPU Core

Interrupt Controller Clock Gear Oscillator/ Dual Clock

Bus Controller

RAM

Display driver

Watchdog Timer

8 Bit Timers

16 Bit Timers (Capture / Compare)

DMA Controller

DRAM Controller

J-TAG Interface

UART I2C Bus

Interface

10-Bit A/D Converter

D/A Converter

CAN*

Stepper Motor / Pattern Generator

Chip Select/ Wait Controller

I/O Ports

* Under Development

CES_16BIT_V1.2 *

TOSHIBA

TLCS-900

The chip select image

/CS0

000000H 7F00H B0C1,0=00 8000H B2C1,0=00 400000H B0C1,0=01 800000H B0C1,0=10 C00000H B0C1,0=11 FFFFFFH B1C1,0=11 B2C1,0=11 B1C1,0=10 B2C1,0=10 B1C1,0=01 B2C1,0=01 B1C1,0=00

/CS1

/CS2

CES_16BIT_V1.2

TOSHIBA

TLCS-900

The Prescaler

Example of cycle at 20MHZ T1 (8/fc) 0.4 sec T256 (2048/fc) 102.4sec T0 T1 T2 T4 T8 T16 T32 T256

0 Oscillator circuit 1/4

3 4 5 6 9 bit prescalor

1/2

System Clock } o2

o1

PWM prescaler 0 1 2 3 4

Example of PWM cycle at 20MHz P1 (4/fc) 200ns P16 (64/fc) 3.2sec

P1

CES_16BIT_V1.2 *

P4

P16

TOSHIBA

TLCS-900

8 Bit Timer

By cascading two 8-bit timers, a 16-bit timer can be configured.

8-bit interval timer mode (x2) 16-bit interval timer mode (x1) 8-bit programmable square wave

(PPG: variable duty with variable cycle) output mode (x1)

TO pin

T1 8/f c pin 32/f c 128/f c

S e l e c t o r

Selector

8

S e l 8/fc e 128/fc c t 2048/f co r

bit upcounter

bit upcounter

8-bit PWM

(Pulse width Modulation):Variable duty with constant cycle) output mode (x1)

INT

8 Bit comparator 0 Timer REG0

8 Bit comparator 1 Timer REG1

INTERNAL DATA BUS

CES_16BIT_V1.2

TOSHIBA

TLCS-900

16 Bit Timers /event counters

q q q q q q

16 bit interval timer mode 16-bit event counter mode 16-bit programmable square wave output (PPG) mode Frequency measurement mode TFF1 Pulse width measurement mode TTIO TTI1 Time difference measurement mode

8/f c 32/f c 128/f c S e l e c t o r

INTERNAL DATA BUS

Capture 0

Capture 1

Capture Control

F/F Control Circuit

TTO0 TTO1 INT INT

x A timer event counter consists of the following:

16 Bit Counter

16-bit up counter two 16-bit timer registers two 16-bit capture registers two comparators capture input control timer F/F and its control circuit

Comparator 0

Comparator 1

Timer Reg 0

Timer Reg 1

INTERNAL DATA BUS

CES_16BIT_V1.2

TOSHIBA

TLCS-900

A/D Converter

4 to 16 channel 8 or 10 bit resolution (by Product) Successive approximation system High speed conversion

16s to 3 s (by product)

AN0 (P53) AN1 (P52) AN2 (P51) AN3 (P50)

A n a l o g M u x

INTERNAL DATA BUS

A/D Converter Control Circuit

ADREG 0

4 conversion modes

Single channel mode Channel scan mode Single mode Repeat mode Flag/Interrupt operation

Comparator

+ -

ADREG 1 ADREG2 ADREG 3

A/D Result Converter Reg.

VREF AGND

D/A/Converter

CES_16BIT_V1.2

TOSHIBA

TLCS-900

Serial I/O

UART mode (x2): 7/8 & 9 bit modes, internal BRG/timer O clock Max. baud rate: 500 kbps@ 16MHz using o1 Synchronous (I/O interface) mode: 8 bits internal/external clock

Max clock: 1.25Mbps

I2C-Bus Interface

Serial I/O Data Formats

Mode 0 (I/O interface mode)

Bit 0 1 2 3 4 5 6 7

Transfer direction

Mode 1 (7-bit UART mode)

start start Bit 0 Bit 0 1 1 2 2 3 3 4 4 5 5 6 6 stop parity stop

Mode 2 (8-bit UART mode)

start start Bit 0 Bit 0 1 1 2 2 3 3 4 4 5 5 6 6 7 7 stop parity stop

Mode 3 (9-bit UART mode)

start start Bit 0 Bit 0 1 1 2 2 3 3 4 4 5 5 6 6 7 7 8 Bit 8 stop stop (wake-up)

Bit 8 = 1, address (select mode) Bit 8 = 0, data

CES_16BIT_V1.2

TOSHIBA

TLCS-900

The pattern generator

q q

2 channels, 4bits/channel General purpose pattern generation

b7 1-2 excitation b3 SA03

PG03

Hardware stepper motor control

(eg. 4-phase 1-step/2-step excitation)

Normal Rotation

b6

P63/PG03 (P67/PG13)

1/2 excitation

PG03

P62/PG02 P66/PG12)

Reverse Rotation

b2

SA03

Internal Bus

b5

PG03

P61/PG01 (P65/PG11)

b1

Difference between PG0 & PG1

SA03

PG0

Trigger Signal From Timer 4

PG1

From Timer 5

b4

PG03

P60/PG00 (P64/PG10)

b0

SA03

CES_16BIT_V1.2

TOSHIBA

TLCS-900

The Watch dog timer

WDTOUT ______ RESET INTWD WDMOD<RESET>

fc/216

fc/216

fc/216

(216 /fc, 218 /fc 220

/fc, 222 /fc)

fc/216

Generates NMI to CPU WDTOUT signal for application 22 - stage binary counter choice of 4 outputs

Watchdog timer out control

WDMOD <WDTP1,0>

Selector

enable Reset fc/4

Q R S

o fc/2)

Watchdog timer 22-stage binary counter

Reset

Reset

examples: 216 /fc = 32,768 states

(approx. 3.3ms @ 20MHz); 222 /fc = 2M states (approx. 210ms @ 20MHz)

Reset HALT Instruction (Stop or Idle mode) 4EH 1BH Write Write Watchdog Timer control register

INTERNAL BUS

WDMOD <WDTE>

CES_16BIT_V1.2

TOSHIBA

TLCS-900

THE ROAD MAP

CES_16BIT_V1.2

TOSHIBA

TLCS-900

Standard family line up

TMP96PM40F TMP96C141BF

20MHz 80-pin

MNEMONIC COMPATIBLE

TMP96CM40F

20MHz 80-pin 32K ROM 1K RAM

ROM less 1K RAM

TMP96C041BF

TMP96C031ZF

20MHz 64-pin ROM/RAM less

TLCS-90 8-Bit MCU

20MHz 80-pin ROM/RAM less

Small package

CES_16BIT_V1.2

TOSHIBA

TLCS-900

TLCS-900/L- DEVELOPMENT TREND

LARGE MEMORY

TMP93PW40F TMP93CW41DF TMP93CW40DF TMP93PS40F TMP93CS41F TMP93CS40F TMP93PS42F TMP93CS42F TMP93Px44F TMP93CS45F TMP93Cx44F

20MHz 32KROM/less 100-pin 2K RAM 80 PIN 64K/128K ROM 2K/4K RAM 2 x UART + 1 x I2C 128K ROM /romless 4K RAM 100-pin

TMP93PW46AF TMP93CW46AF

128K ROM 100-pin 4K RAM 5 ch UART

TMP93PW20AF TMP93CS20F

LCD 40x4 64K ROM 144-pin

64K ROM, 2K RAM 100 PIN

TMP93CM41F TMP93CM40F

TMP93PW32F TMP93CS32F

64K ROM, 2K RAM 64-pin

LOW PIN COUNT

CES_16BIT_V1.2 *

TOSHIBA

TLCS-900

TLCS-900/H Development trend

256K Flash

25MHz 100-pin ROM typ 64K/128K ROM, 2K/ 4K RAM

256K Flash TMP95FY54AF* TMP95PS54F TMP95CS54F

CAN

TMP95FY64F TMP93PW64F TMP95C265F TMP95Cx64F

64K ROM

100-pin

TLCS-900/H CPU CORE TMP95C061BF

25MHz 100-pin ROM/RAM less

TMP95C063F

25MHz 100-pin ROM/RAM less

TMP95C001F

* UNDER DEVELOPMENT 25MHz 64 pin MPU type

CES_16BIT_V1.2

TOSHIBA

TLCS-900

TLCS-900/L1 Development trend

256K Flash 3 x PWM TMP91FY14F* TMP91PP8xF* TMP91CP8xF* CAN TMP91CW14F*

48K ROM 2K RAM 80/100-pin

128K ROM 100-pin 4K RAM

TMP91FY13F* TLCS-900/L1 CPU CORE TMP91CW13F*

128K ROM 100-pin 4K RAM

256K Flash, 3V

TMP91PW12F* TMP91CW12F* irDA

128K ROM 100-pin 4K RAM

TMP91PW10F TMP91CU10F

96K ROM 100-pin 3K RAM 3 ch. SIO/UART * UNDER DEVELOPMENT

CES_16BIT_V1.2 *

TMP91PW11F TMP91CW11F

128K ROM 100-pin 4K RAM 6 ch. SIO

TOSHIBA

TLCS-900

TLCS-900/H2 Development trend

Flash CAN

TMP94FxxxF** TMP94PS40AF** TMP94CS40AF**

64K ROM 160-pin 2K RAM

TLCS-900/H2 CPU CORE

TMP94C241AF

ROM -less 160-pin 2K RAM

TMP94C251F

ROM -less 144-pin 2K RAM

** Under Planning

CES_16BIT_V1.2 *

TOSHIBA

TLCS-900

THE PRODUCTS

CES_16BIT_V1.2

TOSHIBA

TLCS-900

TMP96C141 group

TLCS-900 core

Min. Instruction Exec. Time = 200ns (@20MHz)

20MHz WDT ROM (32K byte) RAM (1K byte) Int. I/Os Ports 900 CPU core 4 channel 10-bit A/D C 6 channel Timer/ counter 2 channel Serial I/O (SYNC. or UART)

Analog Inputs

Address Space

Program : 16M Byte Data : 16M Byte

Timer Output Timer Input SIO0 SIO1

DMA : 1.6s / 2Byte Dynamic Bus Sizing Peripherals

16bit Timer x 2ch Capture x4, Compare x4 Serial I/O : 2ch. ( Clocked I/O or UART)

CS/WAIT

CS/WAIT Controller (3Blocks)

Memory variation

Type ROM (byte) I/Os RAM (byte)

Package : QFP80

CES_16BIT_V1.2

TMP96C141BF 47 TMP96CM40F 32K 1024 TMP96PM40F 32k(OTP) 65 TMP96C041BF * 47

1024 65 1024 -

TOSHIBA

TLCS-900

TMP93Cx40F group

TLCS-900/L core Min. Instruction Exec. Time

200ns(@20MHz)

20MHz 32KHz Clock Gear ROM (64K byte) WDT Int. I/Os Ports RAM (2K byte) 900/L CPU core 8ch 10-bit A/D C 6 channel Timer/ 2 counter channel Serial I/O Analog Inputs

Linear address space

Program/Data:16M Byte

Timer Outpu Timer Input SIO0 SIO1

Dynamic Bus Sizing Low Power Operation

Clock Gear Dual Clock 4 stand-by modes

CS/WAIT

(SYNC. or UART) CS/WAITController (3Blocks)

Memory variation

Type ROM (byte) RAM (byte) 2048 2048 64k 64k(OTP) 4096 128k 128k(OTP) TMP93CM40F 32k TMP93CM41F TMP93CS40F/DF 2048 TMP93PS40F/DF 2048 TMP93CW41F TMP93CW40F 4096 TMP93PW40F 4096

10bit A/D Converter 2 UARTS/SIO Package :

100 pin LQFP 100 pin VQFP

CES_16BIT_V1.2

TOSHIBA

TLCS-900

TMP93Cx32F

TLCS-900/L core Low Power Operation

Clock Gear 4 stand-by mode

20MHz Clock Gear ROM (64K byte) RAM (2K byte) 900/L CPU core 6 channel 10-bit A/D C 4 channel 8 bit Timer 2 channel 16 bit Timer 2 channel Serial I/O (SYNC. or UART) Analog Inputs

Timer Output Timer Input Pulse Output Timer/Counter Input SIO0 SIO1

10bit A/D Converter LED drive : 2ch x 10 mA Package : 64 pin QFP

WDT Interrupt I/Os Ports

6. ch, Conv. Time = 8s, External trigger

Memory variation

Type ROM(byte) RAM(byte)

TMP93CS32F 64K 2048 TMP93PW32F 128K(OTP)

4096

CES_16BIT_V1.2

TOSHIBA

TLCS-900

TMP93CS20F

TLCS-900/L core LCD driver

40 seg. X 4 com.

20MHz 32KHz WDT Interrupt I/ Os 88 Ports 900/L CPU core Clock Gear ROM (64K byte) RAM (2K byte) 8ch 10-bit A/D C 6 channel Timer/ 2 counter channel Serial I/O Analog Input

10bit A/D Converter

Conv. Time = 8 s External trigger 32 kHz Timer

Timer Output Timer Input SIO0 SIO1

Low Power Operation

Clock-Gear function Dual-clock (20MHz,32kHz) 4 stand-by mods

LCD Driver

(SYNC. or UART) 32 Serial Bus kHz Timer Interface

SBI I/O

Package :

144 QFP (20 x 20 x 1.4t)

Memory variation

Type ROM(byte) RAM(byte) 2048 128K(OTP)

TMP93CS20F64K TMP93PW20AF 4096

CES_16BIT_V1.2

TOSHIBA

TLCS-900

TMP95C061BF

TLCS-900/H core

Min.Instruction Exec.Time=160ns(@25MHz)

Interrupt 900/H CPU core 4 channel 8 bit Timer 2 channel 16 bit Timer Pattern Output 4bit Pattern Generator (2ch) 2 channel Serial I/O (SYNC. or UART) DRAM controller (1ch.) Timer Output Timer Input Pulse Output Timer/Counter Input SIO0 SIO1 25MHz WDT 4 channel 10-bit A/D C Analog Inputs

Easy Bus Interface

Separate bus (Address / Data) DRAM Controller

Memory Access Time

(@25MHz,0-WAIT) ROM :100ns DRAM: 70ns

Package : 100pin QFP

RAS

CAS

CES_16BIT_V1.2

TOSHIBA

TLCS-900

TMP95Cx64F

TLCS-900/H Core A/D converter : 10bit

External trigger

25MHz WDT 2 ch. 8Bit D/A C 81 Ports ROM (64K byte) RAM (2K byte) 8 channel 10-bit A/D 8C channel 8 bit Timer 2 channel 16 bit 3 Timer channel Serial I/O (SYNC. or UART) Analog Inputs

8 Bit D/A converter UART/SIO : 3 channel

Baud-rate clock input pin

Analog Output

Interrupt

I/Os

Package

100 pin LQP

900/H CPU core

Timer Output Timer Input Pulse Output Timer/Counte Input SIO0 SIO1 SIO3

CS/WAIT

CS/WAIT Controller (3Blocks)

Memory variation

Type ROM(byte) 64K RAM(byte)

TMP95CS64F TMP95CW64F TMP95PW64F TMP95FY64F TMP95C265F CES_16BIT_V1.2

2K 128K 128K(OTP) 256K(FLASH) 2K

4K 4K 8K

TOSHIBA

TLCS-900

TMP91CW10F

TLCS-900/L1 core

Vcc = 2.7V, @16MHz Vcc = 2.0V @10MHz

20MHz 32KHz WDT ROM 128KByte) 10bit A/D C (8ch) 8 BIT Timer (8ch) 16 BIT Timer (2ch) SIO (UART) (3ch) SIO SIO SIO Analog Input

CS/WAIT RAM (4KByte) CS/WAIT Controller (3Block) Int. 80 Ports 900/L1 Core DMA

A/D C : 10 bit x 8ch.

20 usec (@2.7V, @25MHz)

Low Power Operation

Clock Gear Dual Clock 4 stand-by modes

Package :

100 pin LQFP

Input/ Output

Memory variation

Type ROM(byte) RAM(byte)

TMP91CU10F TMP91PW10F 4K CES_16BIT_V1.2 *

96K 3K 128(OTP)

TOSHIBA

TLCS-900

TMP94C241BF

TLCS-900/H2 core

50ns (@20MHz)

10MHz PLL ROM (64K byte) WDT RAM (2K byte) 900/H2 CPU core

Dynamic Bus Sizing

8/16/32bit bus

8 channel 10-bit A/D 4C channel 8 bit Timer 4 channel 16 bit 2 Timer channel Serial I/O (SYNC. or UART) DRAM controller (2ch.)

Analog Inputs

DMA

(8ch) : 300ns / 4 Byte

Timer Output Timer Input Timer/Counte Input SIO0 SIO1

PLL

Xin x4 internal clock

Interrupt

I/Os 81 Ports

Internal I/O

2 ch. DRAM controller 16bit Timer (4ch), 8ch Capture 8ch Compare

CS/WAIT

CS/WAIT Controller (6 Blocks) 2 ch. 8-Bit D/A C

RAS CAS

Package

160Pin-QFP 144Pin QFP (ext. 16 Bit BUS)

Memory variation

Type ROM(byte) 64K RAM(byte) 2048 2048 2048

TMP94C251F TMP94C241F TMP94CS40F** *

CES_16BIT_V1.2

TOSHIBA

TLCS-900

16-BIT MICROCONTROLLERS WITH FLASH MEMORY ON BOARD

CES_16BIT_V1.2

TOSHIBA

TLCS-900

FLASH MCU ROAD MAP

0.4um high-speed

3.3V TX19 TMP1940* 512K TMP1942** 512K

0.25um LV/HS

TMP194x ** 1.8V TX19

32-bit

3.3V 900/H2 TMP94Fxxx** CAN

0.4um

5V 900/L1

* : UNDER DEVELOPMENT ** : PLANNING

0.4um LP/LV

TMP91Fxxx ** 3V to 1.8V 900/L1 TMP91Fxxx ** 5V 900/L1

16-bit

3V TMP91FY13* 900/L1 256K TMP95FY64 256K

TMP91FY14* 256K

5V 900/H

TMP95FY54A* 256K, CAN

8-bit

5V 870/C

TMP86FS41* 60K

TMP86FSxx max.64KB

TMP88Fxxx ** 5V 870/C

5V 870/X

1998

1999

00

01

02

CES_16BIT_V1.2

TOSHIBA

TLCS-900

TMP95FY64F

TLCS-900/H core On chip Flash :

25MHz WDT 8bit D/A (2ch) CS/WAIT Controller (4Block) Int. 81 Ports Flash EEPROM (256KByte) RAM (8KByte) 900/H Core DMA Boot ROM (2K Byte) 10bit A/D C (8ch) 8 BIT Timer (8ch) 16 BIT Timer (2ch) SIO (UART) (3ch) SIO SIO SIO Analog Input

256K (16K x 1, 8K x 2, 32K x 1, 64K x 3 Blocks)

Analog Output

A/D C : 10 bit x 8 ch.

with external trigger

D/A Converter

8 bit x 2 channeI

SIO/UART x 3 ch.

External Baudrate generator

Type

Input/ Output

Memory variation

ROM(byte) RAM(byte)

Package :

100 pin LQFP

USP 4,382,279 owned by BULL CP8

TMP95CS64F TMP95CW64F TMP95C265F TMP95PW64F 4K TMP95FY64F 8K *

64K 2K 128K 4K 2K 128K (OTP) 256(FLASH)

CES_16BIT_V1.2

TOSHIBA

TLCS-900

TMP91FY13F

TLCS-900/L1 core

2.7 to 3.3 V operation

16MHz 32KHz WDT 32 kHz Timer CS/WAIT Controller (3Block) Int. 81 I/Os I2C (1ch) Flash EEPROM (256KByte) RAM (8KByte) 900/H Core DMA Boot ROM (2K Byte)

Under Development

10bit A/D C (12ch) 8 BIT Timer (4ch) 16 BIT Timer (3ch) UART (3ch) Synch. (2ch)

Analog Input

On chip Flash, 3V :

256K (16K x 1, 8K x 2, 32K x 1, 64K x 3 Blocks)

A/D C : 10 bit x 12 ch.

with external trigger

32 kHz Timer SIO

UART x 3 ch. Synch. x 2 ch. I2C Bus x 1 ch.

Memory variation

Type ROM(byte) RAM(byte)

Package :

120 pin LQFP

TMP91CY13F TMP91FY13F 4K

256K 4K 256(FLASH)

CES_16BIT_V1.2

TOSHIBA

TLCS-900

TMP91FY14F

25MHz 32KHz 32 kHz Timer CS/WAIT Controller (3Block) Int. PWM 12 Bit (3ch) WDT

Under Development

TLCS-900/L1 core

5V operation

On chip Flash :

256K (16K x 1, 8K x 2, 32K x 1, 64K x 3 Blocks)

Flash EEPROM (256KByte) RAM (4KByte) 900/H Core DMA Boot ROM (2K Byte)

10bit A/D C (16ch) 8 BIT Timer (6ch) 16 BIT Timer (4ch) UART/ Synchr. (4ch)

Analog Input

ROM correction A/D C : 10 bit x 16 ch.

with external trigger

32 kHz Timer PWM : 12 Bit x 3 ch. SIO

UART/Synch. x 4 ch.

Memory variation

Type ROM(byte) RAM(byte)

Package :

100 pin LQFP

TMP91CW13F 128K 4K TMP91FY13F 256(FLASH)

4K

CES_16BIT_V1.2

TOSHIBA

TLCS-900

ON BOARD PROGRAMMING

3 types of Programming to support various process of development > Trial : Programming by EPROM Writer Prepare sockets for EPROM writer > Evaluation : ON Board Programming by PC Easy Mode set using Programming Tool > Shipment : ON Board Programming by Programming Tool Insert PC card with new data into Programming Tool

On Board Programming(Evaluation)

PC

On Board Programming(Shipment)

UART

RxD TxD

New Data file

Flash E2PROM

RS-232C

Programming Tool

PC card

New Data file

Mode set

TMP95FY64

Target System

CES_16BIT_V1.2

TOSHIBA

TLCS-900

ON BOARD PROGRAMMING

Boot Procedure suitable for on board programming

Three Mode to support Effective Development of Software Checksum : Release Software engineer from complicated

Past-record Management of Program Programming in the lump : Can Reprogram efficiently using Erase in the lump RAM Loader : Insure Security against illegal Reading and Cope flexibly with each users Boot Sequence Command Control Method

TMP95FW86 TMP95FY64F

Start System Boot

CES_16BIT_V1.2

HOST

command

inform transmission error inform writing error

error code

Checksum Programming Erasing in output checksum the lump result Programming

RAM loader check password download user boot to RAM execute user boot

TOSHIBA

TLCS-900

On Chip TCAN Controller MCU

CES_16BIT_V1.2

TOSHIBA

TLCS-900

TCAN FEATURES

TCAN features short list

2.0B active Full-CAN Controller 16 Mailboxes (15 Receive&Transmit+1 Rec.-only) Baudrate up to 1MBit / s Extended Prescaler Bit Timing Parameter like AN82527 Built in Time-Stamp Counter Readable Error Counters Warning Level IRQ, Error passive IRQ, Bus-off IRQ Local Loop Back Test Mode (Self Acknowledge) Built-in mechanism for internal Re-Arbitration Sleep Mode Wake-up on CAN-bus activity

CES_16BIT_V1.2

TOSHIBA

TLCS-900

CAN MCU ROAD MAP

Under planning 900/H2 128KB lash 4KB RAM FULL-CAN 900/H2 128KB MROM 4KB RAM FULL-CAN

Memory Size(bit)

128K

Standard TMP95PS54F 64KB OTP, 2KB RAM, FULL-CAN with LCD

900/H2 96KB Flash 3KB RAM FULL-CAN

64K

TMP95CS54F TMP95FY54AF 64KB 256KB MROM Flash 2KB RAM 4KB RAM FULL-CAN FULL-CAN TMP91PP82 48KBOTP TMP91CM80F 2KB RAM 32KB FULL-CAN MROM 1KB RAM 8 Mailboxes

TMP95CW54AF

TMP91CP82F 48KB MROM 2KB RAM FULL-CAN

Engine/AT

Wide range Flash -40 to 110 degree

900/L1 64KB 2KB RAM FULL-CAN

DUAL CAN**

16K for EPS 1998 1999 Year

*

* : UNDER DEVELOPMENT ** : PLANNING

2000

2001

CES_16BIT_V1.2

TOSHIBA

TLCS-900

TMP95CS54F

24MHz WDT ROM

Under development

TLCS-900/H core On chip Flash CAN

2.0B, FULL CAN 16 Mailboxes Time stamp

8ch 10-bit A/D C

Analog Input

Timer/ Counter Interrupt

RAM 1 ch.SEI 900/H CPU core

Internal I/O

10 Bit A/D C x 8ch. SIO/UART x 2 ch. Timer (16Bit x2, 8Bit x8) SEI x 1 ch.

Type ROM(byte)

2 ch. SIO/UART

Tx Rx Tx Rx

Input/Output ports

FULL CAN

Package :

100 pin LQFP

Memory variation

RAM(byte)

TMP95CS54F 64K 2K TMP95PS54F 64K (OTP) 2K TMP95FY54AF 256K(FLASH) 4K CES_16BIT_V1.2 *

TOSHIBA

TLCS-900

The round picture

Pin and S/W compatible 16 Bit MCUs

TMP95PW64F

TMP95FY64F

* UNDER DEVELOPMENT

The OTP TMP95CS64F The TMP95C265F ROM The ROMless

TLCS-900/H CPU CORE

*TMP95FY54AF

CES_16BIT_V1.2

The CAN

*

The FLASH TMP95CS54F The CAN TMP95PS54F The CAN OTP TOSHIBA

TLCS-900

TMP91CP8xF

Under development

TLCS-900/L1 core, 5V CAN

2.0B, FULL CAN 16 (8) Mailboxes Time stamp

16MHz WDT

ROM

12ch 10-bit A/D C 1 ch.SEI

An

Timer/ Counter Interrupt I/O ports

RAM

Internal I/O

A/D C : 10 bit x 12 ch. SIO/UART x 2 ch. Timer (16Bit x2, 8Bit x4) PWM : 16 Bit x 4 ch. SEI x 1 ch. ABZ phase measurement x 1ch.

900/H CPU core

2 ch. SIO/UART

T R T R

PWM

ABZ

FULL CAN

Memory variation

Type ROM(byte) RAM(byte) 48 48K (OTP)

Package :

80 pin QFP 100 pin QFP

TMP91CP80FCP82F 2K TMP91PP80F/PP82F 2K *

CES_16BIT_V1.2

TOSHIBA

TLCS-900

Starter-Kit TOPAS-900

Features

Toshiba s C compiler, assembler, linker Toshiba s Windows UDE debugger Program development using high level language Simple program download to the TLCS-900 board C level program test with UDE debugger/ROM monitor Single Step, Breakpoints, Symbolic Debugging Easy switch to Toshiba emulator (RTE model 15/25)

Supported MCU s

TLCS-900/L standard : TMP93CS41F TLCS-900/H FLASH : TMP95FY64F TLCS-900/H CAN : TMP95CS54F TOSHIBA

CES_16BIT_V1.2

TLCS-900

TOPAS900 CAN : Starter kit for CAN MCU

CAN I board

PC

Connectors

RS-232 8 SRAM 128 kB SRAM 128 kB Flash 256 kB

CPU terminals

TMP95PS54

CAN TxRx

16

CAN BUS

CAN II board

CAN TxRx LEDs/ Switches 16 Flash 256 kB

Connectors

CPU terminals Highcurrent drive

TMP95PS54

IPD TA8063

CES_16BIT_V1.2

TOSHIBA

S-ar putea să vă placă și

- SH69P26K PDFDocument43 paginiSH69P26K PDFMarcos Gomes Missel83% (12)

- LC863224ADocument21 paginiLC863224AJose SintuÎncă nu există evaluări

- TMP91C815F - 16bit Microcontroller TLCS-900 L1 SeriesDocument277 paginiTMP91C815F - 16bit Microcontroller TLCS-900 L1 SerieskeirgalÎncă nu există evaluări

- 8-Bit Microcontroller Technical SpecificationsDocument20 pagini8-Bit Microcontroller Technical Specificationsmiloud1911Încă nu există evaluări

- LC 863548 B, 863528 BDocument17 paginiLC 863548 B, 863528 BRashid BasironÎncă nu există evaluări

- Ordering CMOS IC LC863232/28/24/20/16A MicrocontrollerDocument20 paginiOrdering CMOS IC LC863232/28/24/20/16A MicrocontrollerRudyXPÎncă nu există evaluări

- LC863548B 2Document18 paginiLC863548B 2jenengÎncă nu există evaluări

- LC8635 XX CDocument17 paginiLC8635 XX CFagh AbdoulÎncă nu există evaluări

- 8-Bit Single Chip Microcontroller LC87F67C8ADocument27 pagini8-Bit Single Chip Microcontroller LC87F67C8AAlbert GTÎncă nu există evaluări

- DatasheetDocument17 paginiDatasheetErnesto SuarezÎncă nu există evaluări

- Dsaih000128973 PDFDocument112 paginiDsaih000128973 PDFMarkoÎncă nu există evaluări

- LC863432CDocument18 paginiLC863432Cjose gomezÎncă nu există evaluări

- 16Mb H-Die SDRAM Specification: Revision 1.5 August 2004Document12 pagini16Mb H-Die SDRAM Specification: Revision 1.5 August 2004AleksandarPetrovicÎncă nu există evaluări

- At 90 Can 128Document428 paginiAt 90 Can 128Mahmoud AlÎncă nu există evaluări

- Introduction To Digital Signal Processors (DSPS) : Prof. Brian L. EvansDocument30 paginiIntroduction To Digital Signal Processors (DSPS) : Prof. Brian L. Evansdayoladejo777Încă nu există evaluări

- Doc4180 PDFDocument127 paginiDoc4180 PDFrdx_fxÎncă nu există evaluări

- Amm Cheet PrintDocument7 paginiAmm Cheet PrintjokerÎncă nu există evaluări

- LC 863532 CDocument17 paginiLC 863532 CHelmi HashimÎncă nu există evaluări

- 8086/88 Device SpecificationsDocument22 pagini8086/88 Device SpecificationsAyush PurohitÎncă nu există evaluări

- 128Mb Synchronous DRAM MemoryDocument13 pagini128Mb Synchronous DRAM MemoryMihaela CaciumarciucÎncă nu există evaluări

- LC877364ADocument26 paginiLC877364AAlbert GTÎncă nu există evaluări

- PIC16F1703Document338 paginiPIC16F1703Anonymous 3GwpCKÎncă nu există evaluări

- TrackerDocument93 paginiTrackerashutosh kumarÎncă nu există evaluări

- Micro Detv Chino Lc863232bDocument21 paginiMicro Detv Chino Lc863232bNeto GarciaÎncă nu există evaluări

- MB90360E SeriesDocument60 paginiMB90360E SeriesOlga PlohotnichenkoÎncă nu există evaluări

- Unit 21 PDFDocument45 paginiUnit 21 PDFNishanth VallabhadasuÎncă nu există evaluări

- Samsung SCX 1150 MFP Service ManualDocument66 paginiSamsung SCX 1150 MFP Service ManualwcualumniÎncă nu există evaluări

- S K K B: Uresh UmarDocument141 paginiS K K B: Uresh UmarAnshu PatelÎncă nu există evaluări

- 1K-16K UNI/O Serial EEPROM Family Data SheetDocument48 pagini1K-16K UNI/O Serial EEPROM Family Data Sheetikaro181083Încă nu există evaluări

- 8051 BookDocument124 pagini8051 Bookpraveen_kodgirwarÎncă nu există evaluări

- General Description: 16/32-Bit ARM Microcontroller With 10-Bit ADC and External Memory InterfaceDocument40 paginiGeneral Description: 16/32-Bit ARM Microcontroller With 10-Bit ADC and External Memory InterfaceAlexander PrivaloffÎncă nu există evaluări

- LC 863224Document21 paginiLC 863224ban4444Încă nu există evaluări

- HY57V641620E (L - S) T (P) Series (Rev1.0)Document13 paginiHY57V641620E (L - S) T (P) Series (Rev1.0)Hans PeterÎncă nu există evaluări

- MSP430 Microcontroller Architecture GuideDocument128 paginiMSP430 Microcontroller Architecture GuideasdsdÎncă nu există evaluări

- LPC2138Document39 paginiLPC2138yuvaraja_703Încă nu există evaluări

- U34 - Dram Hy57v641620ftp7Document13 paginiU34 - Dram Hy57v641620ftp7qwertyuÎncă nu există evaluări

- ARM920T-based Microcontroller AT91RM9200: FeaturesDocument41 paginiARM920T-based Microcontroller AT91RM9200: Featuresnskprasad89Încă nu există evaluări

- Datasheet MB90803/F804Document88 paginiDatasheet MB90803/F804richdushÎncă nu există evaluări

- Toshiba T1950 T1950CS T1950CT - Maintenance Manual AddendumToshiba T1950 T1950CS T1950CT - Maintenance Manual AddendumDocument18 paginiToshiba T1950 T1950CS T1950CT - Maintenance Manual AddendumToshiba T1950 T1950CS T1950CT - Maintenance Manual Addendumdeath914Încă nu există evaluări

- Sprs 276 KDocument255 paginiSprs 276 Ktheomen3007Încă nu există evaluări

- AT90USB1286Document39 paginiAT90USB1286Alan_88Încă nu există evaluări

- MP 2Document30 paginiMP 2ayan hazarikaÎncă nu există evaluări

- RTL 8186Document50 paginiRTL 8186Maria Alejandra DalcolmoÎncă nu există evaluări

- 90PWM216 316 A0307Document349 pagini90PWM216 316 A0307Fariha NaazÎncă nu există evaluări

- SAM4S Datasheet PDFDocument1.163 paginiSAM4S Datasheet PDFDaniel TelloÎncă nu există evaluări

- 24 LC 16Document12 pagini24 LC 16Sebastian QuaroneÎncă nu există evaluări

- Toshiba Microcontrollers For Dslrs/DvcsDocument24 paginiToshiba Microcontrollers For Dslrs/DvcsMitesh ChauhanÎncă nu există evaluări

- sprs698f DSDocument177 paginisprs698f DSaalvarcaÎncă nu există evaluări

- 8-Bit Microcontroller With 256K Bytes In-System Programmable Flash Atmega1281/25 61/V Atmega640/128 0/2560/V Advance InformationDocument24 pagini8-Bit Microcontroller With 256K Bytes In-System Programmable Flash Atmega1281/25 61/V Atmega640/128 0/2560/V Advance Informationmike_helplineÎncă nu există evaluări

- B 810 A 176 DDocument165 paginiB 810 A 176 DOsama YaseenÎncă nu există evaluări

- MB 91305Document90 paginiMB 91305Bin WangÎncă nu există evaluări

- UM10120Document297 paginiUM10120kiran6014Încă nu există evaluări

- PIC18F458PPTDocument58 paginiPIC18F458PPTdgkanade72Încă nu există evaluări

- MSP430 Update PresentationDocument118 paginiMSP430 Update PresentationNguyên ThảoÎncă nu există evaluări

- STM32 Microcontroller General Oct2012Document69 paginiSTM32 Microcontroller General Oct2012dcesentherÎncă nu există evaluări

- LPC 18 XXDocument2 paginiLPC 18 XXMalik_123pkÎncă nu există evaluări

- R5F364AEDFADocument85 paginiR5F364AEDFAJulio Chuquilin BecerraÎncă nu există evaluări

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationDe la EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationÎncă nu există evaluări

- Verbs Pronunciation in Past TenseDocument5 paginiVerbs Pronunciation in Past TenseCesar SaucedoÎncă nu există evaluări

- Configuracion SwitchDocument4 paginiConfiguracion SwitchCesar SaucedoÎncă nu există evaluări

- Configuracion Router 1 (1.5.1)Document4 paginiConfiguracion Router 1 (1.5.1)Cesar SaucedoÎncă nu există evaluări

- Configuracion SwitchDocument4 paginiConfiguracion SwitchCesar SaucedoÎncă nu există evaluări

- How to Use a Multimeter Safely and AccuratelyDocument11 paginiHow to Use a Multimeter Safely and AccuratelyCesar SaucedoÎncă nu există evaluări

- BitacoraDocument29 paginiBitacoraCesar SaucedoÎncă nu există evaluări

- Configuracion SwitchDocument4 paginiConfiguracion SwitchCesar SaucedoÎncă nu există evaluări

- Todero"U I Ines: ZX PectrumDocument77 paginiTodero"U I Ines: ZX PectrumEleodor Paul CirlugeaÎncă nu există evaluări

- 8 Bit Transfer Instructions (Instruction Set)Document15 pagini8 Bit Transfer Instructions (Instruction Set)yudha bhirawa anoragaÎncă nu există evaluări

- White Paper: Unlimited Code and Data Support For The Zilog® Z80 & Z180 Family of MicroprocessorsDocument4 paginiWhite Paper: Unlimited Code and Data Support For The Zilog® Z80 & Z180 Family of MicroprocessorskmyisusÎncă nu există evaluări

- MPF-I Experiment ManualDocument148 paginiMPF-I Experiment ManualIonut TomaÎncă nu există evaluări

- Advanced Machine Code ProgrammingDocument259 paginiAdvanced Machine Code Programminglordbubsy100% (2)

- (Macmillan Computer Science Series) Roger Hutty (Auth.) - Z80 Assembly Language Programming For Students-Macmillan Education UK (1981)Document139 pagini(Macmillan Computer Science Series) Roger Hutty (Auth.) - Z80 Assembly Language Programming For Students-Macmillan Education UK (1981)angelÎncă nu există evaluări

- CoBra Hardware Manual Rev.1.0Document63 paginiCoBra Hardware Manual Rev.1.0Cristian CotetÎncă nu există evaluări

- 1 History of MicroprocessorDocument80 pagini1 History of MicroprocessorRaghav GuptaÎncă nu există evaluări

- Embedded Systems and Its ScopeDocument81 paginiEmbedded Systems and Its Scopenanobala15Încă nu există evaluări

- Manual de Partes Z80-60 PDFDocument350 paginiManual de Partes Z80-60 PDFJuan Diego ArizabalÎncă nu există evaluări

- Interview With Sean Ellis Re: Graphic Adventure Creator: PreambleDocument8 paginiInterview With Sean Ellis Re: Graphic Adventure Creator: PreambleMarcos MarcosÎncă nu există evaluări

- Great Moments in Microprocessor HistoryDocument11 paginiGreat Moments in Microprocessor Historyrandima fernandoÎncă nu există evaluări

- P7 ArduinoDocument1 paginăP7 ArduinoSanto MulyonoÎncă nu există evaluări

- HD44780 CommandsDocument3 paginiHD44780 CommandsPhani ChakravarthiÎncă nu există evaluări

- DR/ Hassan Shehata: Microprocessor Assignments 1, 2,3Document6 paginiDR/ Hassan Shehata: Microprocessor Assignments 1, 2,3manhagÎncă nu există evaluări

- Z80 Assembly Language Programming 1979 Leventhal PDFDocument642 paginiZ80 Assembly Language Programming 1979 Leventhal PDFacsabo_14521769Încă nu există evaluări

- MOSDocument992 paginiMOSULAGANATHAN MÎncă nu există evaluări

- CrackingCodeZXSpectrum PDFDocument270 paginiCrackingCodeZXSpectrum PDFManolo GarciaÎncă nu există evaluări

- Mostek Circuits and Systems Product Guide 1980Document82 paginiMostek Circuits and Systems Product Guide 1980Edd Whatley100% (2)

- Z80 Instruction Set SummaryDocument4 paginiZ80 Instruction Set SummarykpoxphuongÎncă nu există evaluări

- Programming The M68000 1983 Addison-Wesley Publishing CompanyDocument84 paginiProgramming The M68000 1983 Addison-Wesley Publishing CompanyAFK MasterÎncă nu există evaluări

- ZX Spectrum 128 Service ManualDocument65 paginiZX Spectrum 128 Service Manuallugo76Încă nu există evaluări

- Z80 IsDocument16 paginiZ80 IsDang KhueÎncă nu există evaluări

- UM0077Document411 paginiUM0077creativeÎncă nu există evaluări

- Programming in Z80 Assembly LanguageDocument129 paginiProgramming in Z80 Assembly LanguageTrevor100% (1)

- AehowtoDocument98 paginiAehowtow54u4wÎncă nu există evaluări

- z80 DocumentedDocument52 paginiz80 Documentedfernwaribolo100% (1)

- Z80 Microprocessor Architecture Chapter SummaryDocument30 paginiZ80 Microprocessor Architecture Chapter SummaryhowlerbrÎncă nu există evaluări

- z80 DocumentedDocument51 paginiz80 DocumentedchipdudeÎncă nu există evaluări