Documente Academic

Documente Profesional

Documente Cultură

Basics of Electronics and Microprocessor MCQ's

Încărcat de

rohi89Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Basics of Electronics and Microprocessor MCQ's

Încărcat de

rohi89Drepturi de autor:

Formate disponibile

BASICS OF ELECTRONICS AND MICROPROCESSOR

1. A___________is a programmable integrated device having computing and decision making capabilities. A. multiprocessor. B. multicontroller. C. microprocessor. D. macroprocessor. ANSWER: C 2. In ALP,Binary instructions are abbreviated as ________. A. Assembly language. B. Machine language. C. Binary patterns. D. Mnemonics. ANSWER: D 3. In 8086, Data bus contains _________lines. A. 20 B. 8 C. 32 D. 16 ANSWER: D 4. How many building blocks are present in a microcomputer system? A. 4 B. 6 C. 8 D. 10 ANSWER: A 5. Which bus is unidirectional? A. Data bus. B. Control bus. C. System bus. D. Address bus. ANSWER: D 6. Multiplex is a combination of _________. A. data & control bus B. control& address bus C. address& data bus D. data& control bus ANSWER: C

7. Which among the following are the pointer registers? A. base pointer & stack pointer. B. Index pointer & decision pointer. C. service pointer & stack pointer. D. stack pointer & index pointer. ANSWER: A 8. How many internal register are there in 8086 micro processor? A. 14 B. 13 C. 18 D. 16 ANSWER: B 9. Maximum capacity of four memory segments provide _________bytes of active memory. A. 255 B. 256k C. 512k D. 164k ANSWER: B 10. The size used for data storage is __________kbytes. A. 128 B. 1024 C. 256 D. 512 ANSWER: A 11. Instruction pointer is similar to _________. A. program counter. B. micro controller. C. status counter. D. instruction code. ANSWER: A 12. Which of the following functions are used for data manipulation? A. word multiply,divide, input/output B. translate. C. byte multiply. D. word operations. ANSWER: A 13. AL operations are used for ___________. A. arithmetic & linear B. Arithmetic & logic. C. arithmetic &long

D. none of the above ANSWER: B 14. BX stands for_________________. A. translate. B. byte addition C. byte multiply. D. byte divide. ANSWER: A 15. CISC stands for __________________. A. Complex Instruction System Computer. B. Complex Instruction Set Car. C. Complex Instruction Set Computer. D. None of the above. ANSWER: C 16. Collection of instruction are called___________. A. mnemonics. B. instruction tags. C. instruction sets. D. opcodes. ANSWER: C 17. Format for instruction set is___________. A. mnemonics opcode operand. B. data opcode operand. C. opcode data operand. D. opcode operand mnemonics. ANSWER: A 18. Which mnemonis copy bytes to destination? A. MOV. B. POP. C. LEA. D. LES. ANSWER: A 19. Which of the following operation is used to copy specified mode to top of the stack____________. A. POP. B. LES. C. PUSH. D. LDS. ANSWER: C 20. A__________ copy word from stack to all register.

A. POP. B. OUT. C. IN. D. XCHG. ANSWER: A 21. A operation used to exchange byte or exchange word is__________. A. IN B. XGHG C. PUSH D. LEA ANSWER: B 22. An ___________load DS register and other specified register from memory. A. LDS. B. LES. C. DSL. D. LEA. ANSWER: A 23. RISC stands for__________. A. Reduced Integrated Set Computer. B. Resource Instruction Set Computer. C. Resource Instruction System Computer. D. Reduced Instruction Set Computer. ANSWER: D 24. A _________operation is used to compare two specified byte. A. CEP B. CMP C. AAS D. CBB ANSWER: B 25. A________ shift bit left 0 in LSB. A. SHL B. SHR C. SLH D. SSL ANSWER: A 26. An_________and operands to update flags but dont change operands. A. TEST. B. AND. C. NAND. D. NOR.

ANSWER: A 27. An___________ASCII adjust after multiplication. A. AAA. B. AMA. C. AMI. D. AAM. ANSWER: D 28. ____________is used to a procedure or subprogram save return address on stack. A. CALL. B. CLC. C. CLD. D. CLI. ANSWER: A 29. An ____________ jump if flag CF=1. A. JNSE. B. JNSC. C. JNS. D. JNC. ANSWER: B 30. A__________ loop through a sequence of instruction while ZF=1. A. LOOPNE. B. LOOPNZ. C. LOOPE/LOOPZ. D. LOOPNE/LOOPNZ. ANSWER: C 31. An_________________ jump if not signed. A. JNSE. B. JNSC. C. JNS. D. JNC. ANSWER: C 32. The ________________ used to set carry flag=1. A. STE B. STC C. STP D. SCT ANSWER: B 33. A________________ is used to do anything until interrupt is reset. A. HLT.

B. HALT. C. HLTE. D. HALTE. ANSWER: A 34. A __________ is used for not a program. A. NOT. B. NO. C. ESC. D. NOP. ANSWER: D 35. The __________ used for clear interrupt enable control flag to 0. . A. ENB. B. CLT. C. CIE. D. IEF. ANSWER: B 36. Out of 16, ________ flags can be implemented. A. 12 B. 13 C. 10 D. 9 ANSWER: D 37. The___________ indicates conditions that are provided as results of executes as logical instructions. A. Sign flag. B. Overflow flag. C. Status flag. D. Zero flag. ANSWER: C 38. Three important flag bits together are called ___________. A. union flag. B. controlled flag. C. parity flag. D. carry flag. ANSWER: B 39. An ___________ is set if there is any carry out from lower nibble to higher nibble. A. auxiliary carry B. carry flag C. carry auxiliary flag D. parity flag

ANSWER: A 40. A_______is reset, any request at INTR is ignored. A. trap flag. B. overflow flag. C. interrupt flag. D. sign flag. ANSWER: C 41. When ______ is set it indicates that signed result is out of range. A. trap flag. B. overflow flag. C. interrupt flag. D. sign flag. ANSWER: B 42. How many addressing modes are available? A. 7 B. 8 C. 6 D. 10 ANSWER: A 43. Combining base address mode and index address mode we can get _______. A. indexing base address mode. B. base index addressing mode. C. based indexing address mode. D. based index addressing mode. ANSWER: B 44. The MSB of the result is copied into ______. A. sign flag. B. carry flag. C. zero flag. D. parity flag. ANSWER: A 45. The ______ is set if result of arithmetic or logic operation is zero. A. sign flag. B. zero flag C. parity flag. D. carry flag. ANSWER: B 46. BIU stands for? A. Bus Interface Units.

B. Block interfacing unit. C. Bus Interrupt unit D. Block interrupt unit. ANSWER: A 47. The________ moves from source to destination & destination to source. A. control bus. B. data bus. C. system bus. D. address bus. ANSWER: B 48. Multiprocessor communicate and operates in__________. A. binary numbers. B. real numbers. C. whole numbers. D. float numbers. ANSWER: A 49. A ________ used for compliment state of carry flag. A. CMC. B. CLC. C. CLD. D. CCF ANSWER: A 50. The ________ set interrupt unable flag=1. A. SII. B. SIU. C. STD. D. STI. ANSWER: D 51. The 8086 based micro processor system can have maximum of ___________ memory locations. A. 240. B. 230. C. 220. D. 210. ANSWER: C 52. The 8086 micro processor has _______________. A. 16 data bus & 20 address bus. B. .20 data bus & 16 address bus. C. 18 data bus & 16 address bus. D. 16 data bus & 24 address bus.

ANSWER: A 53. Signal is used to place valid data__________ A. DENIED B. HOLD&HLDA. C. RESET. D. CTRL ANSWER: A 54. The direct memory access interfaces of 8086 minimum mode system requires the Signal_________. A. DENIED. B. HOLD & HLDA. C. RESET. D. READY. ANSWER: B 55. In protected mode ________________address lines are active. A. 18. B. 30. C. 20. D. 22. ANSWER: B 56. Protected mode addresses are _____bits long. A. 20 B. 32 C. 18 D. 64 ANSWER: B 57. A/An ______________is used as a select input for high bank of memory in the 8086 memory subsystem. A. BHE B. SSO C. DEN D. M/IO ANSWER: A 58. The ____________________produces the control signals for the I/O subsystem. A. 8288 bus controller B. 8298 bus controller C. 8828 bus controller D. 8988 bus controller ANSWER: A

59. The interrupt request recognized by 8088 signals the fact to_________. A. external circuitry. B. I/O interface. C. internal circuitry. D. memory device. ANSWER: A 60. External circuitry should put an _____________type number on bus lines AD0 through AD7. A. 8 bit. B. 16 bit. C. 32 bit. D. 64 bit. ANSWER: A 61. The distance of the data path between the MPU and interrupt interface is _____ bits in length. A. 16 bit. B. 18 bit. C. 32 bit. D. 64 bit. ANSWER: A 62. A ____________is applied as an input to a bus arbiter. A. LOCK. B. INTA. C. SSO. D. DEN. ANSWER: A 63. The 8086 microprocessor are capable of implementing any combination upto 256 interrupts they are divided into_________. A. 2 groups. B. 4 groups. C. 5 groups. D. 6 groups. ANSWER: C 64. A____________identifies the lowest priority interrupt. A. type 0. B. type 225. C. type 5. D. type 100. ANSWER: B 65. A_______________identifies the starting location of service routines in program memory. A. addressing pointer.

B. stack pointer . C. Instruction pointer. D. overflow pointer. ANSWER: A 66. Which pointer is used to identify the starting location of the non-askable interrupt service routine ? A. 2 pointer . B. 1 pointer. C. 3 pointer. D. 5 pointer. ANSWER: A 67. An ________is used to link the interrupt type numbers to the locations of their service routines in the program storage memory. A. address pointer table. B. vector table. C. programmable peripheral interface. D. I/O interface. ANSWER: A 68. Each of the 256 pointers in the vctor table require _____________of memory. A. 2 bytes. B. 2.4 bytes. C. 6 bytes. D. 8 bytes. ANSWER: B 69. The 27 pointers 5 to 31 are used to ___________. A. identify starting location. B. represent reserved portions. C. user availability . D. find the interrupts. ANSWER: B 70. A _________identifies the program memory segment in which the service routines reside. A. base address . B. 8288 bus controller. C. data bus. D. address bus. ANSWER: A 71. The 8259A is a _____________. A. programmable interrupt controller . B. programmable peripheral interface. C. I/O interface.

D. program interface. ANSWER: A 72. 8259A is treated as a ____________in the micro computer. A. peripheral. B. I/O interface. C. address bus. D. data bus. ANSWER: A 73. The last signal line involved in the host processor interface is the__________. A. A0. B. AD1 C. AD0. D. A1. ANSWER: A 74. Which two signals provide the handshake mechanism in 8259A? A. INTA and INT. B. INTA and DEN. C. INTA and RD. D. INTA and WR. ANSWER: A 75. The ______________carries the physical address generated by the CPU and selects the memory location to be accessed. A. address bus. B. data bus. C. control bus. D. memory address. ANSWER: A 76. The ____________transfers data between the CPU registers and the selected memory location. A. address bus. B. data bus C. control bus D. memory address ANSWER: B 77. Reset RD=DEN='logic1'is used to_________. A. END the read-bus-cycle. B. to initiate reading data into CPU. C. to select memory interface. D. to let data pass. ANSWER: A

78. The data from the memory is read by sampling the data bus at the end of __________. A. T1. B. T2. C. T3. D. T4. ANSWER: C 79. The _____________is introduced for the support of multiprocessor environment in Maximum mode. A. bus controller. B. address bus. C. data bus. D. control bus. ANSWER: A 80. The_________ signal is used to control the access of even or odd memory banks of 8086 system. A. bank high enable. B. data enable. C. acknowledge signal. D. ready. ANSWER: A 81. Maximum mode status codes needs to be active to generate control signals from______. A. bus controller. B. address bus. C. data bus. D. control bus. ANSWER: A 82. Which of the following interrupts have the lowest priority? A. Hardware interrupt. B. Nonmaskable interrupt. C. Software interrupt. D. Internal interrupts and exceptions. ANSWER: A 83. Microprocessor is fabricated on single chip using __________. A. MOS. B. ALU. C. CPU D. None. ANSWER: A 84. The table is located by the system, at a memory location described by the______. A. Interrupt Descriptor Table Address Register.

B. data register. C. segment register. D. pointer register. ANSWER: A 85. A___________causes external interrupts to be enable A. interrupt enable flag. B. carry flag. C. parity flag. D. zero flag. ANSWER: A 86. The ___________instruction should be used after each arithmetic instruction where there is a poss ibility of an overflow. A. INTO. B. INT C. HLT. D. WAIT. ANSWER: A 87. 8259A can manage ____________ according to the instructions written to control registers. A. 4 interrupt. B. 6 interrupts. C. 8 interrupts. D. 10 interrupts. ANSWER: C 88. When the PIC is configured through software for the cascade mode, the __________ line is used as an input A. SP/EN. B. SP. C. EN. D. INT ANSWER: A 89. Which are the eight interrupt inputs of the PIC are labeled? A. IR0 through IR7. B. IR1 through IR8. C. D0 through D7. D. D1 through D8. ANSWER: A 90. The ___________is the interrupt request output of the 8259. A. INT. B. MPU. C. INT.

D. INTR. ANSWER: A 91. Bug means__________. A. a logical error in a program. B. semantic error C. a difficult syntax error in a program. D. duplicate of a program. ANSWER: A 92. The part of machine level instruction, which tells the central processor what was to be done is__________. A. operation code. B. MOV C. INX D. INS ANSWER: A 93. The 8237A carries ______ pins. A. 48. B. 28. C. 40. D. 20. ANSWER: C 94. DMA channels has______ address register. A. 12 B. 8 C. 4 D. 2 ANSWER: D 95. 8255A carries __________ pins. A. 40 B. 28 C. 20 D. 48 ANSWER: A 96. Current address register is a ______ bit register. A. 16 B. 32 C. 8 D. 4 ANSWER: A

97. Mass register is a ______bit register. A. 8. B. 4 C. 16 D. 32 ANSWER: B 98. How many modes of operation in 8254A ? A. 5 B. 6 C. 4 D. 2 ANSWER: B 99. The 8237A operates through __________. A. software. B. hardware. C. hardware and software. D. peripheral devices. ANSWER: A 100. The Status register is a _________ bit register. A. 4. B. 6 C. 8 D. 16 ANSWER: C

S-ar putea să vă placă și

- Component Description For Single Signal Acquisition and Actuation Module (SSAM) Control UnitDocument1 paginăComponent Description For Single Signal Acquisition and Actuation Module (SSAM) Control UnitrudiÎncă nu există evaluări

- HP 3PAR StoreServe ELearning 1 2Q15 Full DeckDocument323 paginiHP 3PAR StoreServe ELearning 1 2Q15 Full Deckmjsmith11100% (2)

- Microprocessor MCQ CS 2nd YearDocument80 paginiMicroprocessor MCQ CS 2nd YearMohit SinghÎncă nu există evaluări

- PLC Training ManualQ Series Basic Course (For GX Developer) EDocument374 paginiPLC Training ManualQ Series Basic Course (For GX Developer) EHamdan AbdurrahmanÎncă nu există evaluări

- Fiber OpticsDocument26 paginiFiber OpticsCherry Ebreo OlaivarÎncă nu există evaluări

- 106A - Computer Organization and ArchitectureDocument43 pagini106A - Computer Organization and ArchitectureSohail Khan100% (1)

- Art of Metering and ExposureDocument39 paginiArt of Metering and ExposureklladoÎncă nu există evaluări

- Multiple ChoiceDocument14 paginiMultiple ChoiceMohammad HamoudeÎncă nu există evaluări

- 3g4g Question BankDocument22 pagini3g4g Question BankAnonymous pJjgXuB9Încă nu există evaluări

- Wireless and Mobie Communication (Updated)Document52 paginiWireless and Mobie Communication (Updated)ramavtar anuragiÎncă nu există evaluări

- Ost ReportDocument23 paginiOst ReportPratik Chourasia100% (2)

- 8086 MicroprocessorDocument8 pagini8086 MicroprocessordiÎncă nu există evaluări

- Introducing Unisab II Version 2.05.1 and 2.05.2Document4 paginiIntroducing Unisab II Version 2.05.1 and 2.05.2Mahmoud Mohamed100% (1)

- CH 14 Wireless LANs Multiple Choice Questions and Answers MCQ PDF - Data Communication and NetworkingDocument13 paginiCH 14 Wireless LANs Multiple Choice Questions and Answers MCQ PDF - Data Communication and NetworkingAkramÎncă nu există evaluări

- Dr.G.R.Damodaran College of Science Mobile Communication QuestionsDocument43 paginiDr.G.R.Damodaran College of Science Mobile Communication Questionssumit_22in67% (3)

- Valleylab Force FX-C Service ManualDocument230 paginiValleylab Force FX-C Service Manualbiomedico123100% (5)

- MCQs Wireless and Wire Communications SystemsDocument115 paginiMCQs Wireless and Wire Communications SystemsMitzOsorioÎncă nu există evaluări

- Microprocessor & AlpDocument43 paginiMicroprocessor & AlpKunwar Gajendra Singh TanwarÎncă nu există evaluări

- Microprocessor and Assembly Language Programming 402 PDFDocument38 paginiMicroprocessor and Assembly Language Programming 402 PDFGurram Sunitha83% (6)

- Computer Architecture McqsDocument10 paginiComputer Architecture McqsSatsshhÎncă nu există evaluări

- Multiple Choice QuestionsDocument10 paginiMultiple Choice QuestionsSanjeev Chaudhary100% (1)

- 8086: Microprocessor: Multiple Choice Question & AnswersDocument34 pagini8086: Microprocessor: Multiple Choice Question & AnswersJos BatlarÎncă nu există evaluări

- Wireless Channel CharacteristicsDocument4 paginiWireless Channel Characteristicsbenny_1811Încă nu există evaluări

- Microprocessor Question BankDocument67 paginiMicroprocessor Question BankArpit SÎncă nu există evaluări

- Forouzan MCQ in CryptographyDocument12 paginiForouzan MCQ in CryptographyNeil BarteÎncă nu există evaluări

- Digital Electronics Multiple Choice QuestionsDocument22 paginiDigital Electronics Multiple Choice QuestionsSenthilkumar KrishnamoorthyÎncă nu există evaluări

- DLD MCQsDocument60 paginiDLD MCQsRAVIHIMAJAÎncă nu există evaluări

- Microprocessors and Microcontrollers Concept TestDocument2 paginiMicroprocessors and Microcontrollers Concept TestRenit AntoÎncă nu există evaluări

- All McqsDocument52 paginiAll McqsimranÎncă nu există evaluări

- Microprocessor MCQ: For 4th Sem MCQ: For 6th Sem MCQDocument24 paginiMicroprocessor MCQ: For 4th Sem MCQ: For 6th Sem MCQKiran RajputÎncă nu există evaluări

- 100 TOP COMPUTER NETWORKS Multiple Choice Questions and Answers COMPUTER NETWORKS Questions and Answers PDFDocument21 pagini100 TOP COMPUTER NETWORKS Multiple Choice Questions and Answers COMPUTER NETWORKS Questions and Answers PDFvaraprasad_ganjiÎncă nu există evaluări

- Adc Mid I MCQ and Objective Question Bank 1Document10 paginiAdc Mid I MCQ and Objective Question Bank 1G NARSIMHULUÎncă nu există evaluări

- Multiple Choice Quiz: (See Related Pages)Document2 paginiMultiple Choice Quiz: (See Related Pages)dialauchennaÎncă nu există evaluări

- Computer Organisation and Architecture MCQ Part 1Document5 paginiComputer Organisation and Architecture MCQ Part 1Vimeno DolieÎncă nu există evaluări

- Sheet #6 Ensemble + Neural Nets + Linear Regression + Backpropagation + CNNDocument4 paginiSheet #6 Ensemble + Neural Nets + Linear Regression + Backpropagation + CNNrowaida elsayedÎncă nu există evaluări

- Computer Networks - Chapter 5 - Data Link LayerDocument9 paginiComputer Networks - Chapter 5 - Data Link LayerNirzor LiveÎncă nu există evaluări

- IBPS Networking MCQsDocument14 paginiIBPS Networking MCQsTushar SharmaÎncă nu există evaluări

- Computer Networks MCQ QuestionsDocument8 paginiComputer Networks MCQ QuestionsRez HabloÎncă nu există evaluări

- MCQ NetworkDocument80 paginiMCQ NetworkNoor Thamer100% (1)

- 20 MCQs on Personal Communication SystemsDocument5 pagini20 MCQs on Personal Communication SystemsJustin Lance RamonÎncă nu există evaluări

- Digital Communication System MCQsDocument20 paginiDigital Communication System MCQsSaquibh ShaikhÎncă nu există evaluări

- Adamson University Data Communication 7 QuestionsDocument5 paginiAdamson University Data Communication 7 Questionsasdfghjkl26Încă nu există evaluări

- EC6801 Unit 1 MCQDocument17 paginiEC6801 Unit 1 MCQVanitha R100% (1)

- Network Fundamentals ExplainedDocument140 paginiNetwork Fundamentals ExplainedSubham MajumdarÎncă nu există evaluări

- Radio Wave Propagation, Diversity Techniques, Eb/No, Received Power CalculationDocument1 paginăRadio Wave Propagation, Diversity Techniques, Eb/No, Received Power CalculationKisangiri MichaelÎncă nu există evaluări

- LINK BUDGET FOR SATELLITE COMMUNICATIONDocument10 paginiLINK BUDGET FOR SATELLITE COMMUNICATIONrakasiwi2013Încă nu există evaluări

- Ies Electronics Engineering Microwave Engineering PDFDocument51 paginiIes Electronics Engineering Microwave Engineering PDFTHILAGAVATHI AÎncă nu există evaluări

- Channel Assignment Strategies, Handoff Strategies Improvement inDocument37 paginiChannel Assignment Strategies, Handoff Strategies Improvement inHarpuneet SinghÎncă nu există evaluări

- Telecommunication Mcqs (Multiple Choices Questions) : Answer - Click HereDocument11 paginiTelecommunication Mcqs (Multiple Choices Questions) : Answer - Click HereMoiz Saif FAST NU LHRÎncă nu există evaluări

- MCQ On Unit-1Document13 paginiMCQ On Unit-1chirag shindeÎncă nu există evaluări

- MCQDocument5 paginiMCQsubhasisdattaÎncă nu există evaluări

- Chapter 8 - Multiple Access TechniquesDocument30 paginiChapter 8 - Multiple Access TechniquesDr. Mudita JunejaÎncă nu există evaluări

- 100 Electronics Engineering Interview Questions and AnswersDocument15 pagini100 Electronics Engineering Interview Questions and AnswersmanishÎncă nu există evaluări

- Microprocessor Question BankDocument3 paginiMicroprocessor Question BankSudip BiswasÎncă nu există evaluări

- Wireless T NG H PDocument24 paginiWireless T NG H PPhương Linh TrầnÎncă nu există evaluări

- EC6602-Antenna and Wave Propagation Important Questions 2Document15 paginiEC6602-Antenna and Wave Propagation Important Questions 2Sornagopal VijayaraghavanÎncă nu există evaluări

- Operating Systems (MCQ)Document26 paginiOperating Systems (MCQ)Mian Hasham Azhar AZHARÎncă nu există evaluări

- Network Fundamentals Quiz with AnswersDocument9 paginiNetwork Fundamentals Quiz with AnswersShenbaga VengatÎncă nu există evaluări

- Mcqs On MicrocontrollerDocument8 paginiMcqs On Microcontrollernitesh100% (1)

- Unit4 - WCN MCQSDocument53 paginiUnit4 - WCN MCQSM.Ganesh Kumar mahendrakarÎncă nu există evaluări

- Tutorial 2 HaiboDocument5 paginiTutorial 2 Haiborere rareÎncă nu există evaluări

- Multiple Choice Questions - Wireless CommunicationDocument3 paginiMultiple Choice Questions - Wireless CommunicationSukhada Deshpande.100% (2)

- 1-Introduction To NetworkingDocument18 pagini1-Introduction To NetworkingmikeÎncă nu există evaluări

- MPMC Question BankkkDocument55 paginiMPMC Question BankkkTUFAN GAMINGÎncă nu există evaluări

- Assignment 2 (Stik)Document12 paginiAssignment 2 (Stik)Jackson YehÎncă nu există evaluări

- Mpi MCQDocument83 paginiMpi MCQAKSHAY DagareÎncă nu există evaluări

- Multiple Choice Questions For Computer OperatorDocument5 paginiMultiple Choice Questions For Computer OperatorRikesh DewanganÎncă nu există evaluări

- Lab Manual - Basic ElectronicsDocument56 paginiLab Manual - Basic Electronicsrohi89Încă nu există evaluări

- VLSI& Embedded - MCQ's - First 10docxDocument5 paginiVLSI& Embedded - MCQ's - First 10docxrohi89Încă nu există evaluări

- Waste DisposalDocument24 paginiWaste Disposalrohi89Încă nu există evaluări

- VLSI& Embedded - MCQ's - 21 - 30Document5 paginiVLSI& Embedded - MCQ's - 21 - 30rohi89Încă nu există evaluări

- Image ProcessingDocument2 paginiImage Processingrohi89Încă nu există evaluări

- VLSI& Embedded - MCQ's - 11 - 20Document5 paginiVLSI& Embedded - MCQ's - 11 - 20rohi89Încă nu există evaluări

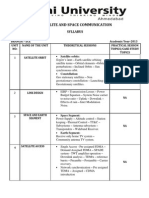

- Syllabus - Satellite and Space CommunicationDocument2 paginiSyllabus - Satellite and Space Communicationrohi89Încă nu există evaluări

- Basics of Electronics and Microprocessor-401-500-Rohit NegiDocument17 paginiBasics of Electronics and Microprocessor-401-500-Rohit Negirohi89Încă nu există evaluări

- Basics of Electronics and Microprocessor-401-500-Rohit NegiDocument17 paginiBasics of Electronics and Microprocessor-401-500-Rohit Negirohi89Încă nu există evaluări

- Behrman N 2019Document8 paginiBehrman N 2019Hasan Basri CobanÎncă nu există evaluări

- Passenger Lift: Type: Machine Room Gearless MachineDocument5 paginiPassenger Lift: Type: Machine Room Gearless Machineandri kustiawanÎncă nu există evaluări

- Sistec Major Project Report Microcontroller Enabled Speaking System For Deaf and DumbDocument32 paginiSistec Major Project Report Microcontroller Enabled Speaking System For Deaf and Dumbukpandey2580% (5)

- Medium-Voltage Circuit Breaker Maintenance: Special FeatureDocument2 paginiMedium-Voltage Circuit Breaker Maintenance: Special FeatureSing Yew LamÎncă nu există evaluări

- Fuji-Electric Fujitsu Rs9lb Rs12lbDocument16 paginiFuji-Electric Fujitsu Rs9lb Rs12lbAlain ClementeÎncă nu există evaluări

- Sailor User ManualDocument157 paginiSailor User ManualEdwin NyangeÎncă nu există evaluări

- ZVA Service ManualDocument226 paginiZVA Service Manualrf2011Încă nu există evaluări

- MOSFET-Internal Capacitances PDFDocument11 paginiMOSFET-Internal Capacitances PDFJayanth Sriranga100% (1)

- Power Factor Improvement Using Dual Boost Converter: Miss. R. S. More, Prof .D.D.AhireDocument6 paginiPower Factor Improvement Using Dual Boost Converter: Miss. R. S. More, Prof .D.D.Ahiresai charanÎncă nu există evaluări

- Circuit Note: Adrv-PackrfDocument15 paginiCircuit Note: Adrv-PackrfwesÎncă nu există evaluări

- VT-05 Operation ManualDocument12 paginiVT-05 Operation ManualKashif Ali Hasnain0% (2)

- 1 Icol Trading Product ListDocument8 pagini1 Icol Trading Product ListRichard RegidorÎncă nu există evaluări

- Electrical Load Analysis Short Circuit Current ComputationDocument5 paginiElectrical Load Analysis Short Circuit Current ComputationNoel Joseph TobsÎncă nu există evaluări

- Roland TR-505 ROM Expansion Installation Instructions: November 2016Document3 paginiRoland TR-505 ROM Expansion Installation Instructions: November 2016listentomerijnÎncă nu există evaluări

- Digital clamp multimeter safety and operation guideDocument2 paginiDigital clamp multimeter safety and operation guideAgung DuemilanoveÎncă nu există evaluări

- Remote Telemetry For Industrial Gases - DPW900 - ANOVADocument5 paginiRemote Telemetry For Industrial Gases - DPW900 - ANOVAsunshine dream50% (2)

- Electrical Machines Lab ManualDocument133 paginiElectrical Machines Lab ManualDagnachewÎncă nu există evaluări

- Troubleshoot EV100 LX SCR Control IssuesDocument33 paginiTroubleshoot EV100 LX SCR Control IssuesMigue Angel Rodríguez CastroÎncă nu există evaluări

- Electro-Pneumatic Lift and Carry Conveying SystemDocument4 paginiElectro-Pneumatic Lift and Carry Conveying SystemIJSTEÎncă nu există evaluări

- Features General Description: 3A, 12V, Synchronous-Rectified Buck ConverterDocument21 paginiFeatures General Description: 3A, 12V, Synchronous-Rectified Buck ConverterVeronica GonzalezÎncă nu există evaluări

- Hafizhul Ayyasi Khairullah English Journal on Voltage Flicker DetectionDocument4 paginiHafizhul Ayyasi Khairullah English Journal on Voltage Flicker DetectionYoshiro KitetsuÎncă nu există evaluări

- A 65nm CMOS Ultra Low Power and Low Noise 131M Front-End Transimpedance AmplifierDocument5 paginiA 65nm CMOS Ultra Low Power and Low Noise 131M Front-End Transimpedance AmplifierBerry KueteÎncă nu există evaluări

- IPC Model ListDocument27 paginiIPC Model ListHardy David Polo CastroÎncă nu există evaluări