Documente Academic

Documente Profesional

Documente Cultură

COMPUTER ARCHITECTURE OBJECTIVE TYPE QUESTIONS

Încărcat de

Ashish AgarwalDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

COMPUTER ARCHITECTURE OBJECTIVE TYPE QUESTIONS

Încărcat de

Ashish AgarwalDrepturi de autor:

Formate disponibile

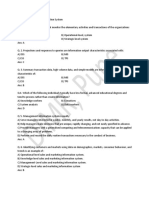

COMPUTER ARCHITURE OBJECTIVE TYPE QUESTIONS

1. How are data and instructions stored in the Von Neumann architecture? A. In separate memories C. Unified read-write memory Ans. C 2. Which of the following depicts an embedded system? A. Multi-core processor unit. B. Application specific Core C. Hardware Software Combination to perform specific application D. All of the above Ans. C 3. The performance of a processor can be measured using A. Clock period C. Throughput Ans. D 4. The Memory Address register stores the address of the word stored in which part of the architecture? A. I/O C. Memory Buffer Register Ans. C B. Program Counter D. None of the above B. Cycles per Instruction D. All of the above B. Dual ported memory D. None of the above

5. What are the parts of an instruction cycle? A. Fetch and Execute Cycle C. Decode and Store cycle Ans. A B. Fetch, decode and execute cycles D. Fetch, decode, execute and store.

6. Which of the following is not a state of the instruction cycle? A. Operand address calculation C. Instruction fetch Ans. B 7. Which of the following approach is used to handle multiple interrupts? A. Parallel interrupt processing B. Disable interrupts and priority assignment C. Interrupt wait D. None of the above. Ans. B 8. What are the interconnection wires not in the bus structure? A. Data lines C. Address lines Ans. B B. Instruction lines D. Control lines B. Data write back D. None of the above.

9. In which type of timing does the clock act as a reference? A. Interrupt timing C. Synchronous timing Ans.C 10. Which of the following is a bus arbitration scheme? A. Round-robin C. First come first serve Ans. D B. Priority D. All of the above B. Asynchronous timing D. Sequential timing

11. Performance of the memory is decided by which of the following parameters A. Transfer rate C. Cycle time Ans. D 12. When is a cache block is written into the main memory A. Valid bit is not set B. Every cycle C. Dirty bit is set D. None of the above Ans. C 13. An important attribute of RAM memories is A. Random access & non-volatile C. Sequential access Ans. B 14. How often/how is data written into the ROM? A. Anytime/when required B. Before use by microprogramming C. During manufacturing D. All of the above Ans. C 15. Redundancy is a built-in feature here A. Magnetic disks C. Serial I/O tapes Ans.B B. RAID D. Optical disks B. Volatile D. None of the above B. Latency D. All of the above

16. RAID level 0 is primarily used in applications where A. Cost is a priority B. Reliability is a priority C. Area is a priority D. All of the above Ans. A

17. Bit density is more in which device A. Compact disk C. DVD Ans. C 18. Which of the following is an example for a communication I/O? A. Monitor C. Modem Ans. C 19. This technique for data transfer does not involve the processor A. Direct Memory access C. Memory-mapped I/O Ans. A 20. What part of the OS stores utilities or frequently accessed functions? A. Memory C. Kernel Ans: C B. Registers D. None of the above B. Programmed I/O D. All the above B. Mouse D. USB B. Magnetic tape D. Magnetic disk

Q.21 In a virtual memory system, the addresses used by the programmer belongs to (A) Memory space. (C) Address space. Ans: C Q.22 The method for updating the main memory as soon as a word is removed from the Cache is called (A) Write-through (B) write-back (C) protected write Ans: B (D) cache-write (B) Physical addresses. (D) Main memory address.

Q.23 A control character is sent at the beginning as well as at the end of each block in the synchronous-transmission in order to (A) Synchronize the clock of transmitter and receiver. (B) Supply information needed to separate the incoming bits into individual character. (C) Detect the error in transmission and received system. (D) Both (A) and (C). Ans B Q.24 In a non-vectored interrupt, the address of interrupt service routine is (A) Obtained from interrupt address table. (B) Supplied by the interrupting I/O device. (C) Obtained through Vector address generator device. (D) Assigned to a fixed memory location. Ans: D Q.25 Divide overflow is generated when (A) Sign of the dividend is different from that of divisor. (B) Sign of the dividend is same as that of divisor. (C) The first part of the dividend is smaller than the divisor. (D) The first part of the dividend is greater than the divisor. Ans: B Q.26 Which method is used for resolving data dependency conflict by the compiler itself? (A) Delayed load. (B) operand forwarding. (C) Pre fetch target instruction. (D) loop buffer. Ans: A

Q.27 Stack overflow causes (A) Hardware interrupt. (B) External interrupt. (C) Internal interrupt. (D) Software interrupt. Ans: C Q.28 Arithmetic shift left operation (A) Produces the same result as obtained with logical shift left operation. (B) Causes the sign bit to remain always unchanged. (C) Needs additional hardware to preserve the sign bit. (D) Is not applicable for signed 2's complement representation. Ans: A Q.29 Zero address instruction format is used for (A) RISC architecture. (B) CISC architecture. (C) Von-Neuman architecture. (D) Stack-organized architecture. Ans: D Q.30 Address symbol table is generated by the (A) memory management software. (B) assembler. (C) match logic of associative memory. (D) generated by operating system Ans: B Q.31 How many different addresses are required by the memory that contain 16K words? (A)16,380 (B) 16,382 (C)16,384 (D) 16,386 Ans. (C) Q.32 DMA interface unit eliminates the need to use CPU registers to transfer data from (A) MAR to MBR (B) MBR to MAR (C) I/O units to memory (D) Memory to I/O units Ans. (D) Q.33 How many 128 x 8 RAM chips are needed to provide a memory capacity of 2048 bytes? (A) 8 (B) 16 (C) 24 (D) 32 Ans. (B)

Q.34 In 8085 microprocessor how many I/O devices can be interfaced in I/O mapped I/O technique? (A) Either 256 input devices or 256 output devices. (B) 256 I/O devices. (C) 256 input devices & 256 output devices. (D) 512 input-output devices. Ans. (C) Q.35 Which of the following technology can give high speed RAM? (A) TTL (B) CMOS (C) ECL (D) NMOS Ans. (C) Q.36 Which is true for a typical RISC architecture? (A) Micro programmed control unit. (B) Instruction takes multiple clock cycles. (C) Have few registers in CPU. (D) Emphasis on optimizing instruction pipelines. Ans. (A) Q.37 When an instruction is read from the memory, it is called (A) Memory Read cycle (B) Fetch cycle (C) Instruction cycle (D) Memory write cycle Ans. (B) Q.38 Which activity does not take place during execution cycle? (A) ALU performs the arithmetic & logical operation. (B) Effective address is calculated. (C) Next instruction is fetched. (D) Branch address is calculated & Branching conditions are checked. Ans. (D) Q.39 How many memory chips of (128 x 8) are needed to provide a memory capacity of 4096 x 16? (A)64 (B) 16 (C)32 (D) None Ans. (A) Q.40 Pseudo instructions are (A) Machine instructions (B) Logical instructions (C) Micro instructions (D) instructions to assembler. Ans. (A)

Q.41 An attempt to access a location not owned by a Program is called (A) Bus conflict (B) Address fault (C) Page fault (D) Operating system fault Ans. (B) Q. 42 Dynamic RAM consumes ________ Power and ________ then the Static RAM. (A) more, faster (B) more, slower (C) less, slower (D) less, faster Ans. (C) Q.43 Cache memory works on the principle of (A) Locality of data. (B) Locality of reference (C) Locality of memory (D) Locality of reference & memory Ans. (B) Q.44 An interrupt for which hardware automatically transfers the program to a specific memory location is known as (A) Software interrupt (B) Hardware interrupt (C) Maskable interrupt (D) Vector interrupt Ans. (B) Q.45 Cycle stealing technique is used in (A) Interrupt based data transfer (B) Polled mode data transfer (C) DMA based data transfer (D) None of these Ans. (C) Q.46 When CPU is not fully loaded, which of the following method of data transfer is preferred (A) DMA (B) Interrupt (C) Polling (D) None of these Ans. (D) Q.47 Associative memory is sometimes called as (A) Virtual memory (B) Cache memory (C) Main memory (D) Content addressable memory Ans. (D)

Q.48 A more efficient way to organize a Page Table is by means of an associative memory having (A) Number of words equal to number of pages (B) Number of words more than the number of pages (C) Number of words less than the number of pages (D) Any of the above Ans. (A) Q.49 CPU checks for an interrupt signal during (A) Starting of last Machine cycle (B) Last T-State of instruction cycle (C) First T-State of interrupt cycle (D) Fetch cycle Ans. (B) Q.50 Which flag of the 8085's flag register is not accessible to programmer directly? (A)Zero flag (B)Carry flag (C)Auxiliary carry flag (D)Parity flag Ans. (C)

S-ar putea să vă placă și

- Computer Organisation and Architecture MCQ Part 1Document5 paginiComputer Organisation and Architecture MCQ Part 1Vimeno DolieÎncă nu există evaluări

- STET - 2019: Important Question Based On Exam PatternDocument42 paginiSTET - 2019: Important Question Based On Exam PatternAtul Prakash DwivediÎncă nu există evaluări

- Typical Questions & AnswersDocument82 paginiTypical Questions & AnswersSudip PaulÎncă nu există evaluări

- Compiler Mcqs (Org)Document39 paginiCompiler Mcqs (Org)M ShahidÎncă nu există evaluări

- C++ Questions & Answers JECRC UniversityDocument31 paginiC++ Questions & Answers JECRC UniversityAnonymous BOreSF0% (1)

- 6102 C Language Mca MCQDocument93 pagini6102 C Language Mca MCQNISHANTÎncă nu există evaluări

- PPSC Lecturer of Computer Science Past Paper QuestionsDocument19 paginiPPSC Lecturer of Computer Science Past Paper QuestionsMian Ejaz0% (2)

- Management Information Systems QuizDocument24 paginiManagement Information Systems QuizRush RathorÎncă nu există evaluări

- PPSC Computer Lecturer MCQDocument143 paginiPPSC Computer Lecturer MCQRana afaqÎncă nu există evaluări

- Software Engineering MCQ (Multiple Choice Questions)Document26 paginiSoftware Engineering MCQ (Multiple Choice Questions)Nazir AbdulkareemÎncă nu există evaluări

- Computer Graphics MCQ'SDocument7 paginiComputer Graphics MCQ'SGuruKPOÎncă nu există evaluări

- Computer Graphics MCQDocument23 paginiComputer Graphics MCQBobby DeolÎncă nu există evaluări

- Computer Graphics MCQ 01Document10 paginiComputer Graphics MCQ 01schlemielzÎncă nu există evaluări

- Iot MCQDocument32 paginiIot MCQScary NightmareÎncă nu există evaluări

- 100 Top Data Structures and Algorithms Multiple Choice Questions and AnswersDocument22 pagini100 Top Data Structures and Algorithms Multiple Choice Questions and AnswersKiruthiga Prabakaran100% (1)

- DBMS MCQ QuesDocument29 paginiDBMS MCQ Quesأحمد العباسي100% (1)

- Coa Unit 4,5 MCQDocument26 paginiCoa Unit 4,5 MCQManish Singh RajputÎncă nu există evaluări

- Erd and Eerd: DR - ElmahdyDocument10 paginiErd and Eerd: DR - ElmahdyMahmoud Elmahdy100% (1)

- MCQ 2Document122 paginiMCQ 2laxmi bagade100% (1)

- Unit 2 MCQDocument11 paginiUnit 2 MCQShubhangi GiraseÎncă nu există evaluări

- ETI Notes For 1st Unit AI (Artificial Intelligence)Document11 paginiETI Notes For 1st Unit AI (Artificial Intelligence)Chhota PanditÎncă nu există evaluări

- Who Is The Father of Artificial Intelligence?Document74 paginiWho Is The Father of Artificial Intelligence?Deepshikha MehtaÎncă nu există evaluări

- UNIT 1 Mcqs (IPT)Document3 paginiUNIT 1 Mcqs (IPT)Ashutosh DevpuraÎncă nu există evaluări

- PPSC Lecturer Computer Science Questions & AnswersDocument14 paginiPPSC Lecturer Computer Science Questions & AnswersMuhammad Sikandar DarÎncă nu există evaluări

- MCQ Unit-3Document18 paginiMCQ Unit-3ANKUR CHOUDHARYÎncă nu există evaluări

- DIGITAL FLUENCY MCQ's-Material (Complete Syllabus)Document37 paginiDIGITAL FLUENCY MCQ's-Material (Complete Syllabus)Mohan KumarÎncă nu există evaluări

- Operating System MCQ’s Set1Document8 paginiOperating System MCQ’s Set1Yash KuncolienkerÎncă nu există evaluări

- Internet of Things (IoT) Solved MCQs (Set-3)Document5 paginiInternet of Things (IoT) Solved MCQs (Set-3)Shweta KachawarÎncă nu există evaluări

- Database Management System Multiple Choice QuestionsDocument7 paginiDatabase Management System Multiple Choice QuestionsAfshan ShaikhÎncă nu există evaluări

- 02 - Data Types - MCQDocument4 pagini02 - Data Types - MCQApurba BaruaÎncă nu există evaluări

- KVS PGT Reasoning Question Paper 2Document14 paginiKVS PGT Reasoning Question Paper 2gondaÎncă nu există evaluări

- COA Chapter 1 NotesDocument14 paginiCOA Chapter 1 NotesAmitesh ki class For engineeringÎncă nu există evaluări

- Compiler Design MCQ Question Bank Last Update 29-Dec-20202 Page 1 of 18Document18 paginiCompiler Design MCQ Question Bank Last Update 29-Dec-20202 Page 1 of 18SOMENATH ROY CHOUDHURYÎncă nu există evaluări

- MCQs of CDocument21 paginiMCQs of CFaisal M. SoomroÎncă nu există evaluări

- Operating Systems Concepts ExplainedDocument37 paginiOperating Systems Concepts ExplainedcdacssmÎncă nu există evaluări

- COA MCQ 1Document21 paginiCOA MCQ 1Nayan Ranjan Paul100% (1)

- 30 Question Network and System Exam With AnswerDocument7 pagini30 Question Network and System Exam With AnswerMichael BluntÎncă nu există evaluări

- Multiple Choice Question Bank on Power Generation Transmission and DistributionDocument21 paginiMultiple Choice Question Bank on Power Generation Transmission and DistributionsanjuÎncă nu există evaluări

- 100 TOP COMPUTER NETWORKS Multiple Choice Questions and Answers COMPUTER NETWORKS Questions and Answers PDFDocument21 pagini100 TOP COMPUTER NETWORKS Multiple Choice Questions and Answers COMPUTER NETWORKS Questions and Answers PDFvaraprasad_ganjiÎncă nu există evaluări

- Software Engineering ObjectiveDocument5 paginiSoftware Engineering Objectivebheemsinghsaini100% (1)

- Network Layer MCQs on Logical Addressing and CIDR NotationDocument15 paginiNetwork Layer MCQs on Logical Addressing and CIDR NotationGayle LokeshÎncă nu există evaluări

- CC MCQ QB 3Document5 paginiCC MCQ QB 3Ravikant AmbulgekarÎncă nu există evaluări

- System Development Life Cycle (SDLC) McqsDocument7 paginiSystem Development Life Cycle (SDLC) McqsPavan KarthikÎncă nu există evaluări

- Software Engineering Solved Mcqs PDFDocument16 paginiSoftware Engineering Solved Mcqs PDFPuskin MittalÎncă nu există evaluări

- MCQ Operating System QuestionsDocument131 paginiMCQ Operating System QuestionsRajeev BansalÎncă nu există evaluări

- MCQ NetworkDocument80 paginiMCQ NetworkNoor Thamer100% (1)

- Computer Network Technology Exam QuestionsDocument2 paginiComputer Network Technology Exam QuestionsOmar MehrajÎncă nu există evaluări

- CT RevDocument5 paginiCT RevMahmoud ElmahdyÎncă nu există evaluări

- DBMS Ctevt StudentsDocument230 paginiDBMS Ctevt StudentsDeepena PrykÎncă nu există evaluări

- COA Multiple Choice Questions and Answers PDFDocument32 paginiCOA Multiple Choice Questions and Answers PDFAnkita Jape100% (1)

- 300+ TOP Computer Organization and Architecture MCQ PDFDocument37 pagini300+ TOP Computer Organization and Architecture MCQ PDFSaikumar NemalikantiÎncă nu există evaluări

- Interview Questions: 300+ Top Computer Organization & Architecture Mcqs and AnswersDocument55 paginiInterview Questions: 300+ Top Computer Organization & Architecture Mcqs and AnswersmohammedÎncă nu există evaluări

- Computer Architecture MCQsDocument33 paginiComputer Architecture MCQsMs.Sangeetha Priya IT DepartÎncă nu există evaluări

- Multiple Choice Questions - Coa: Ans: ADocument8 paginiMultiple Choice Questions - Coa: Ans: ADeepa GoudÎncă nu există evaluări

- Computer Architecture-OBJECTIVE TYPE 75 QUESTIONS-GateDocument8 paginiComputer Architecture-OBJECTIVE TYPE 75 QUESTIONS-GatepranavbommiÎncă nu există evaluări

- CSE211 MCQ'sDocument17 paginiCSE211 MCQ'sYash Gupta MauryaÎncă nu există evaluări

- CS8491 COMPUTER ARCHITECTURE QUIZDocument8 paginiCS8491 COMPUTER ARCHITECTURE QUIZASIF MÎncă nu există evaluări

- Computer Organization and ArchitectureDocument20 paginiComputer Organization and ArchitecturePoovarasanÎncă nu există evaluări

- Computer Architecture Objective Type Questions and AnswersDocument129 paginiComputer Architecture Objective Type Questions and AnswersRajesh TiwaryÎncă nu există evaluări

- Ca Q&aDocument129 paginiCa Q&aRavi TejaÎncă nu există evaluări

- Virtual TableDocument5 paginiVirtual TableAshish AgarwalÎncă nu există evaluări

- ACM ICPC Online Contest ProblemDocument2 paginiACM ICPC Online Contest ProblemAshish AgarwalÎncă nu există evaluări

- Typical Questions & AnswersDocument187 paginiTypical Questions & AnswersRasshreeÎncă nu există evaluări

- Java Multiple Choice QuestionsDocument22 paginiJava Multiple Choice QuestionsAshish AgarwalÎncă nu există evaluări

- Switching Circuits & Logic Design: 14 Derivation of State Graphs and TablesDocument17 paginiSwitching Circuits & Logic Design: 14 Derivation of State Graphs and TablesAshish AgarwalÎncă nu există evaluări

- CompilersDocument25 paginiCompilersAshish AgarwalÎncă nu există evaluări

- LP Lab ManualDocument48 paginiLP Lab Manualcomputerstudent81% (16)

- Ec0221 Ed Lab ManualDocument72 paginiEc0221 Ed Lab ManualParvatham VijayÎncă nu există evaluări

- Intro To UMLDocument28 paginiIntro To UMLKrishna Kumaran ThampiÎncă nu există evaluări

- 1Document27 pagini1saranyakathiravanÎncă nu există evaluări

- 189 Esdras Etal AERO2015Document11 pagini189 Esdras Etal AERO2015bedawy2010Încă nu există evaluări

- Unit 16 Thermionic Emission CroDocument3 paginiUnit 16 Thermionic Emission Croyusuke123456789Încă nu există evaluări

- Butterfly Effects PDFDocument3 paginiButterfly Effects PDFpablofaure1Încă nu există evaluări

- IND780 Firmware Rev History 7-4-05Document17 paginiIND780 Firmware Rev History 7-4-05Eduardo HerreraÎncă nu există evaluări

- "Bye Bye Birdie" score/CD InfoDocument3 pagini"Bye Bye Birdie" score/CD InfoCasey on the KeysÎncă nu există evaluări

- Articulo 1. - Ibm's Deep Blue Chess Grandmaster ChipsDocument12 paginiArticulo 1. - Ibm's Deep Blue Chess Grandmaster ChipsJesús Sánchez CondadoÎncă nu există evaluări

- Dark Knight Application Using AndroidDocument15 paginiDark Knight Application Using AndroidIJRASETPublicationsÎncă nu există evaluări

- Anexo 04 - Datasheet MódulosDocument2 paginiAnexo 04 - Datasheet MódulosJoao Vitor FonsecaÎncă nu există evaluări

- Solution 3.11 Problem Statement: F I J I JDocument5 paginiSolution 3.11 Problem Statement: F I J I JPandji Arie NugrahaÎncă nu există evaluări

- 07 Chapter2 PDFDocument24 pagini07 Chapter2 PDFChhaya ThakorÎncă nu există evaluări

- Geometry m2 Topic C Lesson 12 TeacherDocument14 paginiGeometry m2 Topic C Lesson 12 TeacherMae RohÎncă nu există evaluări

- Micowave and Millimeter Wave Technologies Modern UWB Antennas and EquipmentDocument498 paginiMicowave and Millimeter Wave Technologies Modern UWB Antennas and EquipmentNguyenPhucTruong100% (1)

- Introductory Chemistry 5th Edition Tro Solutions ManualDocument6 paginiIntroductory Chemistry 5th Edition Tro Solutions Manualjonathantruongylunfl100% (16)

- Parker Drilling Rig 256 3,000 HP Land Drilling Rig: Year Modified: Rated Drilling DepthDocument2 paginiParker Drilling Rig 256 3,000 HP Land Drilling Rig: Year Modified: Rated Drilling DepthJoko SusiloÎncă nu există evaluări

- Cleanroom LED: CR434B LED48/840 PSD W60L60 AC-MLO PIDocument8 paginiCleanroom LED: CR434B LED48/840 PSD W60L60 AC-MLO PIMihaiAnastasiuÎncă nu există evaluări

- 219 Ho SBC (WJB) 9-30-02Document36 pagini219 Ho SBC (WJB) 9-30-02arkhom1Încă nu există evaluări

- Ming-Yung Hsu: Voltnar Control Istribution SubstationsDocument7 paginiMing-Yung Hsu: Voltnar Control Istribution SubstationsAsja AvdićÎncă nu există evaluări

- My Budget of Work (Mathematics)Document5 paginiMy Budget of Work (Mathematics)RomneRyanPortacion100% (1)

- A New Neotropical Genus of Meropachyni (Heteroptera: Coreidae: Meropachydinae)Document9 paginiA New Neotropical Genus of Meropachyni (Heteroptera: Coreidae: Meropachydinae)Eduardo Zavala B.Încă nu există evaluări

- CHP574 - NSD570 Teleprotection EquipmentDocument2 paginiCHP574 - NSD570 Teleprotection EquipmentMichael Parohinog GregasÎncă nu există evaluări

- Railway ProjectDocument51 paginiRailway Projectsanojjose75Încă nu există evaluări

- 8.1 Lesson: Raster To Vector Conversion: EightDocument16 pagini8.1 Lesson: Raster To Vector Conversion: Eightສີສຸວັນ ດວງມະນີÎncă nu există evaluări

- Maths 2b PapersDocument12 paginiMaths 2b Papersycharansai0Încă nu există evaluări

- PCS-9600 X Setting Guide en Overseas General X R1.00 (En ZDZD5117.0086.0001)Document60 paginiPCS-9600 X Setting Guide en Overseas General X R1.00 (En ZDZD5117.0086.0001)robert mihayoÎncă nu există evaluări

- Sri Lankan Mathematics Competition 2018 April 7, 2018 10:30 Am - 12 NoonDocument4 paginiSri Lankan Mathematics Competition 2018 April 7, 2018 10:30 Am - 12 NoonV.NawaneethakrishnanÎncă nu există evaluări

- Co2 Dragsters Research FolioDocument19 paginiCo2 Dragsters Research Folioapi-299008285Încă nu există evaluări

- Half wave rectifier experimentDocument9 paginiHalf wave rectifier experimentSidhartha Sankar RoutÎncă nu există evaluări

- Surface Vehicle Standard: Issued FEB2004Document19 paginiSurface Vehicle Standard: Issued FEB2004Jeferson CostaÎncă nu există evaluări

- MCQ Iapm Double Final 1Document48 paginiMCQ Iapm Double Final 1moamen BÎncă nu există evaluări