Documente Academic

Documente Profesional

Documente Cultură

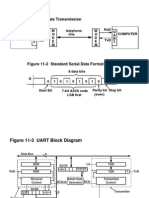

rs232 RX

Încărcat de

Harish KumarTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

rs232 RX

Încărcat de

Harish KumarDrepturi de autor:

Formate disponibile

module RS232_Receiver ( reset_neg, clock, rx_receiver, rx_dataout_ready, rx_dataout, // optional pins for identifying long break in data reception

rx_endofpacket, rx_Idle, Exe_LogicImp ); parameter HIGH = 1'b1; parameter LOW = 1'b0; //`ifdef ML401 parameter CLOCK_FREQ = 100000000; // 100MHz //`else // ifdef ML461 // parameter CLOCK_FREQ = 33000000; // 33MHz //`endif //parameter BAUD_RATE = 9600; // 115200; parameter BAUD_RATE = 115200; // 115200; // BAUD_RATE generator (Uses 8 times oversampling) parameter BAUD_RATE_8X = BAUD_RATE*8; parameter BAUD_8X_ACC_WIDTH = 16; input reset_neg; input clock; input rx_receiver; input Exe_LogicImp; output rx_dataout_ready; output [7:0] rx_dataout; // optional pins for identifying long break in data reception

// We also detect if a gap occurs in the received stream of characters // That can be useful if multiple characters are sent in burst // so that multiple characters can be treated as a "packet" output rx_endofpacket; // one clock pulse, when no more data // is received (rx_Idle is going high) output rx_Idle; // no data is being received wire [BAUD_8X_ACC_WIDTH:0] Baud_8X_Incr; reg [BAUD_8X_ACC_WIDTH:0] Baud_8X_Acc; assign Baud_8X_Incr = ((BAUD_RATE_8X << (BAUD_8X_ACC_WIDTH - 7)) + (CLOCK_FREQ >> 8)) / (CLOCK_FREQ >> 7); always @(posedge clock or negedge reset_neg) begin if (reset_neg == LOW) begin Baud_8X_Acc <= {(BAUD_8X_ACC_WIDTH + 1){LOW}}; end else if (Exe_LogicImp == 1'b1) Baud_8X_Acc <= {(BAUD_8X_ACC_WIDTH + 1){LOW}}; else begin Baud_8X_Acc <= Baud_8X_Acc[BAUD_8X_ACC_WIDTH - 1:0] + Baud_8X_Incr; end end wire Baud_Pulse_8x = Baud_8X_Acc[BAUD_8X_ACC_WIDTH]; //////////////////////////// reg [1:0] Rx_Sync; always @(posedge clock or negedge reset_neg) begin

if (reset_neg == LOW) begin Rx_Sync <= 2'b11; end else if (Exe_LogicImp == 1'b1) Rx_Sync <= 2'b11; else if (Baud_Pulse_8x) begin Rx_Sync <= {Rx_Sync[0], rx_receiver}; end end reg [1:0] Rx_Count; reg Rx_Bit; always @(posedge clock or negedge reset_neg) begin if (reset_neg == LOW) begin Rx_Count <= 2'b11; Rx_Bit <= HIGH; end else if (Exe_LogicImp == 1'b1) begin Rx_Count <= 2'b11; Rx_Bit <= HIGH; end else if(Baud_Pulse_8x) begin if( Rx_Sync[1] && Rx_Count!=2'b11) Rx_Count <= Rx_Count + 2'h1; else if(~Rx_Sync[1] && Rx_Count!=2'b00) Rx_Count <= Rx_Count - 2'h1; if(Rx_Count==2'b00) Rx_Bit <= 1'b0;

else if(Rx_Count==2'b11) Rx_Bit <= 1'b1; end end reg [3:0] State; reg [3:0] Bit_Spacing; // "next_bit" controls when the data sampling occurs // depending on how noisy the rx_receiver is, different values might work better // with a clean connection, values from 8 to 11 work wire next_bit = (Bit_Spacing==4'd10); always @(posedge clock or negedge reset_neg) begin if (reset_neg == LOW) begin Bit_Spacing <= 4'b0000; end else if (Exe_LogicImp == 1'b1) Bit_Spacing <= 4'b0000; else if(State==0) begin Bit_Spacing <= 4'b0000; end else if(Baud_Pulse_8x) begin Bit_Spacing <= {Bit_Spacing[2:0] + 4'b0001} | {Bit_Spacing[3], 3'b000}; end end always @(posedge clock or negedge reset_neg) begin if (reset_neg == LOW)

begin State <= 4'b0000; end else if (Exe_LogicImp == 1'b1) State <= 4'b0000; else if(Baud_Pulse_8x) begin case(State) 4'b0000: if(~Rx_Bit) State <= 4'b1000; // start bit found? 4'b1000: if(next_bit) State <= 4'b1001; // bit 0 4'b1001: if(next_bit) State <= 4'b1010; // bit 1 4'b1010: if(next_bit) State <= 4'b1011; // bit 2 4'b1011: if(next_bit) State <= 4'b1100; // bit 3 4'b1100: if(next_bit) State <= 4'b1101; // bit 4 4'b1101: if(next_bit) State <= 4'b1110; // bit 5 4'b1110: if(next_bit) State <= 4'b1111; // bit 6 4'b1111: if(next_bit) State <= 4'b0001; // bit 7 4'b0001: if(next_bit) State <= 4'b0000; // stop bit default: State <= 4'b0000; endcase end end reg [7:0] rx_dataout; always @(posedge clock or negedge reset_neg) begin if (reset_neg == LOW) begin rx_dataout <= 8'h00; end else if (Exe_LogicImp == 1'b1) rx_dataout <= 8'h00; else if(Baud_Pulse_8x && next_bit && State[3])

begin rx_dataout <= {Rx_Bit, rx_dataout[7:1]}; end end reg rx_dataout_ready, RxD_data_error; always @(posedge clock or negedge reset_neg) begin if (reset_neg == LOW) begin rx_dataout_ready <= LOW; RxD_data_error <= LOW; end else if (Exe_LogicImp == 1'b1) begin rx_dataout_ready <= LOW; RxD_data_error <= LOW; end else begin rx_dataout_ready <= (Baud_Pulse_8x && next_bit && State==4'b0001 && Rx_Bit); // ready only if the stop bit is received RxD_data_error <= (Baud_Pulse_8x && next_bit && State==4'b0001 && ~Rx_Bit); // error if the stop bit is not received end end // Optional functionality for detection of gap if it occurs in the // received stream of characters. reg [4:0] gap_count; always @ (posedge clock or negedge reset_neg) begin

if (reset_neg == LOW) begin gap_count<=5'h00; end else if (Exe_LogicImp == 1'b1) gap_count<=5'h00; else if (State!=0) begin gap_count<=5'h00; end else if (Baud_Pulse_8x & ~gap_count[4]) begin gap_count <= gap_count + 5'h01; end end assign rx_Idle = gap_count[4]; reg rx_endofpacket; always @(posedge clock or negedge reset_neg) begin if (reset_neg == LOW) begin rx_endofpacket <= LOW; end else if (Exe_LogicImp == 1'b1) rx_endofpacket <= LOW; else begin rx_endofpacket <= Baud_Pulse_8x & (gap_count==5'h0F); end end endmodule

S-ar putea să vă placă și

- UARTDocument22 paginiUARTanjalisweÎncă nu există evaluări

- Digital VlsiDocument18 paginiDigital Vlsiwww.chandangowda1128Încă nu există evaluări

- UARTDocument9 paginiUARTBrainz on MobÎncă nu există evaluări

- Digital ExperimentsDocument14 paginiDigital Experimentsdeekshamb01052001Încă nu există evaluări

- Verilog Receiver (Uart - RX.V)Document3 paginiVerilog Receiver (Uart - RX.V)Lucian ELÎncă nu există evaluări

- FinalDocument7 paginiFinalHoàng Long Nguyễn BùiÎncă nu există evaluări

- Universal Asynchronous Receiver Transmitter-IT CAN WORKING AS A DUPLEX AND Full Duplex. in Uart Some Parameters Are Set by Users AreDocument6 paginiUniversal Asynchronous Receiver Transmitter-IT CAN WORKING AS A DUPLEX AND Full Duplex. in Uart Some Parameters Are Set by Users AreteekamÎncă nu există evaluări

- Stop Watch DSDDocument7 paginiStop Watch DSDAwais ShamsÎncă nu există evaluări

- Project CodeDocument6 paginiProject CodeK M Kiran KumarÎncă nu există evaluări

- Uart RtransDocument6 paginiUart RtransshastryÎncă nu există evaluări

- Digital Design and Synthesis: Fall 09Document35 paginiDigital Design and Synthesis: Fall 09Lua Dinh ThiÎncă nu există evaluări

- Shri Ramdeobaba College of Engineering andDocument18 paginiShri Ramdeobaba College of Engineering andAditya BelekarÎncă nu există evaluări

- Embedded Lab Experiment ProgramDocument30 paginiEmbedded Lab Experiment ProgramYash JoshiÎncă nu există evaluări

- Lab 5 DR Muslim (Latest)Document15 paginiLab 5 DR Muslim (Latest)a ThanhÎncă nu există evaluări

- UntitledDocument6 paginiUntitledمفاتيح ابوبارق المهداويÎncă nu există evaluări

- Padhoz Rail 16F628A.hDocument6 paginiPadhoz Rail 16F628A.hPéter KovácsÎncă nu există evaluări

- Arm MicrocontrollerDocument17 paginiArm MicrocontrollerIragoudaÎncă nu există evaluări

- OrgcmdDocument13 paginiOrgcmdMuhammad Jalal AldeenÎncă nu există evaluări

- PID Control MAX6675 Thermocouple Arduino Schematic With Rotary EncoderDocument13 paginiPID Control MAX6675 Thermocouple Arduino Schematic With Rotary EncoderStewin Perez100% (1)

- Top Module / Module DPLL (SignalIn, SignalOutDocument10 paginiTop Module / Module DPLL (SignalIn, SignalOutbigjimmÎncă nu există evaluări

- Cps Signal Generator - InoDocument4 paginiCps Signal Generator - InoAlainbravopaezÎncă nu există evaluări

- PC 5Document8 paginiPC 5Miguel RodasÎncă nu există evaluări

- LED Buzzer: R6 470 LS1 R7 100Document10 paginiLED Buzzer: R6 470 LS1 R7 100pratheep01Încă nu există evaluări

- Code For Fruit Plucking Robot Using ATMEGA2560Document16 paginiCode For Fruit Plucking Robot Using ATMEGA2560Karthik K V Hathwar100% (2)

- ADC-DHT11 CDocument7 paginiADC-DHT11 CGiancarloÎncă nu există evaluări

- Name: Nguyen Nhat Duy ID: EEEEIU18025 Homework 5 Embedded Real-Time System Master CodeDocument6 paginiName: Nguyen Nhat Duy ID: EEEEIU18025 Homework 5 Embedded Real-Time System Master CodeNhất Duy NguyễnÎncă nu există evaluări

- ZadatciDocument22 paginiZadatciTakticar100% (1)

- Unsigned Divider RTL ModelDocument10 paginiUnsigned Divider RTL ModelgadhaÎncă nu există evaluări

- Ee 222 CepDocument10 paginiEe 222 CepObed AhmadÎncă nu există evaluări

- VHDL - Practical Example - Designing An UARTDocument18 paginiVHDL - Practical Example - Designing An UARTPrabakaran EllaiyappanÎncă nu există evaluări

- Listing Program Frekuensi SamplingDocument6 paginiListing Program Frekuensi SamplingNurul AzizahÎncă nu există evaluări

- Basis CodesDocument15 paginiBasis CodesJholo LopezÎncă nu există evaluări

- Portb Change InterruptDocument6 paginiPortb Change InterruptHliva ZoltanÎncă nu există evaluări

- VHDL UartDocument53 paginiVHDL UartEhsan Mahdavi100% (1)

- Chap6 PDFDocument24 paginiChap6 PDFSrinivas CherukuÎncă nu există evaluări

- Zadaci Sa Vjezbi AMIRADocument43 paginiZadaci Sa Vjezbi AMIRAsandraÎncă nu există evaluări

- CED19I032Document13 paginiCED19I032Pranavram VÎncă nu există evaluări

- 8x8x8 CodeDocument7 pagini8x8x8 CodeBalu BhoviÎncă nu există evaluări

- Proiecte ArduinoDocument46 paginiProiecte ArduinoSyad AlyÎncă nu există evaluări

- Verilog Coding ExamplesDocument11 paginiVerilog Coding ExamplesbhargavÎncă nu există evaluări

- Verilog Code For 60s TimerDocument4 paginiVerilog Code For 60s TimerChandem Bacasmas0% (3)

- LCD Interfacing With SPARTAN-3 FPGADocument12 paginiLCD Interfacing With SPARTAN-3 FPGAKaranÎncă nu există evaluări

- Application Note, Nordic nRF24L01 With Bascom-AvrDocument8 paginiApplication Note, Nordic nRF24L01 With Bascom-AvrLalinda Rathnabharatie100% (1)

- Module PISODocument3 paginiModule PISOAnbuak AnbuakÎncă nu există evaluări

- ARM Embedded Controller ManualDocument28 paginiARM Embedded Controller ManualGagan NaiduÎncă nu există evaluări

- Double - Dabble - 16 - Bit NBCD - Ones NBCD - Tens NBCD - Hundreds: Void Char Char Char CharDocument4 paginiDouble - Dabble - 16 - Bit NBCD - Ones NBCD - Tens NBCD - Hundreds: Void Char Char Char CharAlberto Alberti Nisi100% (1)

- AllinonechidoDocument6 paginiAllinonechidoCésar HernándezÎncă nu există evaluări

- Uart TestDocument5 paginiUart TestshastryÎncă nu există evaluări

- Isd Code4Document5 paginiIsd Code4Khushi AgrawalÎncă nu există evaluări

- Writing RTL Code For Virtex-4 DSP48 Blocks With XST 8.1iDocument4 paginiWriting RTL Code For Virtex-4 DSP48 Blocks With XST 8.1iAzou ThtÎncă nu există evaluări

- PidDocument5 paginiPidArif Nugroho100% (1)

- Sample Setting Up Two or More VoidDocument5 paginiSample Setting Up Two or More VoidJade Panzo SalaspeÎncă nu există evaluări

- ParcialesteDocument5 paginiParcialesteJeffersonÎncă nu există evaluări

- PIC Power SupplyDocument0 paginiPIC Power Supplyaqdus100% (1)

- Abu Minhaj Farooqi 37560 Fpga Final ExamDocument20 paginiAbu Minhaj Farooqi 37560 Fpga Final ExamMinhaj FarooqiÎncă nu există evaluări

- Electronics Design Lab Manual - VLSI Prog-V3Document14 paginiElectronics Design Lab Manual - VLSI Prog-V3shanmugasundatamÎncă nu există evaluări

- UARTDocument19 paginiUARTErick LoolÎncă nu există evaluări

- DS Zadaci PDFDocument23 paginiDS Zadaci PDFArnela Tatic100% (1)

- Projects With Microcontrollers And PICCDe la EverandProjects With Microcontrollers And PICCEvaluare: 5 din 5 stele5/5 (1)

- Pres VeriLog PDFDocument64 paginiPres VeriLog PDFpraveen_banthiÎncă nu există evaluări

- 3.4 Hazards/Glitches and How To Avoid Them: 3.4.1 The Problem With HazardsDocument8 pagini3.4 Hazards/Glitches and How To Avoid Them: 3.4.1 The Problem With HazardsHarish KumarÎncă nu există evaluări

- CAD For VLSI Design - 1: V. Kamakoti and Shankar BalachandranDocument17 paginiCAD For VLSI Design - 1: V. Kamakoti and Shankar BalachandranRajeev PandeyÎncă nu există evaluări

- NptelDocument14 paginiNptelalkjhlkjlkÎncă nu există evaluări

- Nptel Cad1 07Document10 paginiNptel Cad1 07Kapasi TejasÎncă nu există evaluări

- Pres VeriLog PDFDocument64 paginiPres VeriLog PDFpraveen_banthiÎncă nu există evaluări

- AnaloG Layout Interview QuestionsDocument2 paginiAnaloG Layout Interview QuestionsHarish Kumar100% (1)

- Lab 1Document5 paginiLab 1Uday KumarÎncă nu există evaluări

- Computer Aids For VLSI DesignDocument443 paginiComputer Aids For VLSI DesignMohammed MorsyÎncă nu există evaluări

- Dangerous Ingridents in The Most of ProductsDocument3 paginiDangerous Ingridents in The Most of ProductsHarish KumarÎncă nu există evaluări

- CAD For VLSI Design - 1: V. Kamakoti and Shankar BalachandranDocument17 paginiCAD For VLSI Design - 1: V. Kamakoti and Shankar BalachandranRajeev PandeyÎncă nu există evaluări

- Ece260b w05 Power IntroDocument73 paginiEce260b w05 Power IntroHarish KumarÎncă nu există evaluări

- CAD For VLSI Design - 1: V. Kamakoti and Shankar BalachandranDocument17 paginiCAD For VLSI Design - 1: V. Kamakoti and Shankar BalachandranRajeev PandeyÎncă nu există evaluări

- Mux and Flipflops - OptDocument16 paginiMux and Flipflops - OptHarish KumarÎncă nu există evaluări

- Logical Composition of Zero-Knowledge Proofs: Andrew Clausen, HTTP://WWW - Econ.upenn - Edu/ Clausen October 6, 2007Document4 paginiLogical Composition of Zero-Knowledge Proofs: Andrew Clausen, HTTP://WWW - Econ.upenn - Edu/ Clausen October 6, 2007Harish KumarÎncă nu există evaluări

- MMTS Train Timings - Hyderabad MMTS Train Timings - Hyderabad Metro Train Timings - MMTS Timetable - Local Train Timings - MMTS HyderabadDocument5 paginiMMTS Train Timings - Hyderabad MMTS Train Timings - Hyderabad Metro Train Timings - MMTS Timetable - Local Train Timings - MMTS HyderabadHarish KumarÎncă nu există evaluări

- Ece260b w05 Design StyleDocument57 paginiEce260b w05 Design StyleHarish KumarÎncă nu există evaluări

- 1 Quick Tour v1.0Document33 pagini1 Quick Tour v1.0Harish KumarÎncă nu există evaluări

- New Microsoft Word DocumentDocument1 paginăNew Microsoft Word DocumentHarish KumarÎncă nu există evaluări

- Ece260b w05 PlacementDocument91 paginiEce260b w05 PlacementHarish KumarÎncă nu există evaluări

- Allen P.E. Holberg D.R. CMOS Analog Circuit Design SDocument477 paginiAllen P.E. Holberg D.R. CMOS Analog Circuit Design SMallavarapu Aditi KrishnaÎncă nu există evaluări

- CryptographyDocument37 paginiCryptographyHarish Kumar0% (1)

- Diffie-Hellman and Its Application in Security Protocols: ISO 9001:2008 CertifiedDocument5 paginiDiffie-Hellman and Its Application in Security Protocols: ISO 9001:2008 CertifiedHarish KumarÎncă nu există evaluări

- Sequential CxircuitsDocument170 paginiSequential CxircuitsHarish KumarÎncă nu există evaluări

- EE/CE 4325/6325 VLSI Design: Introduction To CAD Tools by Akshay Sridharan Akshay - Sridharan@utdallas - EduDocument19 paginiEE/CE 4325/6325 VLSI Design: Introduction To CAD Tools by Akshay Sridharan Akshay - Sridharan@utdallas - EduHarish KumarÎncă nu există evaluări

- Eda ToolsDocument5 paginiEda ToolsHarish KumarÎncă nu există evaluări

- By 23456462Document7 paginiBy 23456462Harish KumarÎncă nu există evaluări

- By 23456462Document7 paginiBy 23456462Harish KumarÎncă nu există evaluări

- TXTDocument13 paginiTXTHarish KumarÎncă nu există evaluări

- Iit Karag Pur Wallace Tree MullDocument6 paginiIit Karag Pur Wallace Tree MullHarish KumarÎncă nu există evaluări

- LTE19B Reports RSLTE001 xml-2021 06 18-14 14 34 442Document283 paginiLTE19B Reports RSLTE001 xml-2021 06 18-14 14 34 442dothatua MrÎncă nu există evaluări

- Hemisphere Crescent VS110 GPS Compass: Call: EmailDocument2 paginiHemisphere Crescent VS110 GPS Compass: Call: EmailNguyen Phuoc HoÎncă nu există evaluări

- Thong-Tin-Vo-Tuyen - Bai-Tap-Matlab-Thong-Tin-Vo-Tuyen - (Cuuduongthancong - Com)Document30 paginiThong-Tin-Vo-Tuyen - Bai-Tap-Matlab-Thong-Tin-Vo-Tuyen - (Cuuduongthancong - Com)Duy Trần ĐứcÎncă nu există evaluări

- Optimized Clustering Algorithm For WBAN To WBAN CommunicationDocument13 paginiOptimized Clustering Algorithm For WBAN To WBAN CommunicationnadeemajeedchÎncă nu există evaluări

- XR 4740rdsDocument52 paginiXR 4740rdslijhubÎncă nu există evaluări

- DETEKCIJAOTONOGPOGONADocument9 paginiDETEKCIJAOTONOGPOGONAIvana SpanovicÎncă nu există evaluări

- Marine VHF Radio Telephone Operation Manual STR-6000D: Samyungenc Co.,LtdDocument64 paginiMarine VHF Radio Telephone Operation Manual STR-6000D: Samyungenc Co.,LtdMahfooz AliÎncă nu există evaluări

- Antena Biquad de La India JarchenkoDocument3 paginiAntena Biquad de La India JarchenkoKrisnoAdhiÎncă nu există evaluări

- 160-20m LOG Loop-On-Ground Page 06 RadioReference - Com ForumsDocument14 pagini160-20m LOG Loop-On-Ground Page 06 RadioReference - Com ForumstlebrykÎncă nu există evaluări

- Base Station Antennas: Antenna Type: UMW-09015-0D Antenna SpecificationsDocument3 paginiBase Station Antennas: Antenna Type: UMW-09015-0D Antenna SpecificationsAnnBlissÎncă nu există evaluări

- Sony MHC Gtr88Document77 paginiSony MHC Gtr88VIicky GalloÎncă nu există evaluări

- Analog-to-Digital and Digital-to-Analog ConversionsDocument20 paginiAnalog-to-Digital and Digital-to-Analog ConversionsArif HassanÎncă nu există evaluări

- PLL Charge PumpDocument33 paginiPLL Charge Pumprah0987Încă nu există evaluări

- BAX EQ Manual v6Document19 paginiBAX EQ Manual v6andreslazarilloÎncă nu există evaluări

- SOLiD gGENESIS DataSheet V0.6Document28 paginiSOLiD gGENESIS DataSheet V0.6Danny MunetsiÎncă nu există evaluări

- June 2021 Ericsson Mobility ReportDocument36 paginiJune 2021 Ericsson Mobility Reportmrvertigo2009Încă nu există evaluări

- Symmetry Epx2Document56 paginiSymmetry Epx2Jason BrownÎncă nu există evaluări

- Assignment 2 Questions (UGPG) PDFDocument5 paginiAssignment 2 Questions (UGPG) PDFHenryÎncă nu există evaluări

- Basic Components of RadarDocument4 paginiBasic Components of Radarmas3565560100% (1)

- Guide To LTE Neighboring Cell and X2 Interface PlanningDocument132 paginiGuide To LTE Neighboring Cell and X2 Interface PlanningMiguel Diaz100% (2)

- RF Optimization Tips - TCH Block Rate Optimization Tips in Huawei GSMDocument4 paginiRF Optimization Tips - TCH Block Rate Optimization Tips in Huawei GSMdolisieÎncă nu există evaluări

- Leach Routing Protocol Implementation in ns2Document38 paginiLeach Routing Protocol Implementation in ns2regragui50% (2)

- Design of Hamming Code Using VerilogDocument5 paginiDesign of Hamming Code Using VerilogDevanshu Anand100% (1)

- NC346 DatasheetDocument2 paginiNC346 DatasheetEl BrainÎncă nu există evaluări

- 5586 ManualDocument134 pagini5586 ManualhishamuddinohariÎncă nu există evaluări

- On DoordarshanDocument22 paginiOn DoordarshanYashank Jain100% (1)

- CQ Amateur Radio February 2021Document116 paginiCQ Amateur Radio February 2021SathawitÎncă nu există evaluări

- BC Lab Cycle Iii ExperimentsDocument15 paginiBC Lab Cycle Iii ExperimentsYaniÎncă nu există evaluări

- Doa WhitepaperDocument14 paginiDoa WhitepaperUfuk TamerÎncă nu există evaluări

- User Guide Supplement S3 (829-865 MHZ) : Ulx Wireless SystemDocument16 paginiUser Guide Supplement S3 (829-865 MHZ) : Ulx Wireless SystemJÎncă nu există evaluări