Documente Academic

Documente Profesional

Documente Cultură

P.G. Diploma Examination - 2010: (Vlsi Design)

Încărcat de

rajasekarkpr0 evaluări0% au considerat acest document util (0 voturi)

13 vizualizări2 paginiExplain the difference between LSI and MSI Elements. (b) Explain the design of Decorders and Demultiplexes. (c) Explain the usage of mixed logic as a design tool. (d) Differentiate Algorithmic State Machine and Mealy and Moore models. (e) Explain the architecture and operation of different types of ROM. (f) Give the general Architecture of FPGA. (g) Explain how a logic function can be implemented using gate array with an example. (h)

Descriere originală:

Titlu original

ASIC Design

Drepturi de autor

© Attribution Non-Commercial (BY-NC)

Formate disponibile

PDF, TXT sau citiți online pe Scribd

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentExplain the difference between LSI and MSI Elements. (b) Explain the design of Decorders and Demultiplexes. (c) Explain the usage of mixed logic as a design tool. (d) Differentiate Algorithmic State Machine and Mealy and Moore models. (e) Explain the architecture and operation of different types of ROM. (f) Give the general Architecture of FPGA. (g) Explain how a logic function can be implemented using gate array with an example. (h)

Drepturi de autor:

Attribution Non-Commercial (BY-NC)

Formate disponibile

Descărcați ca PDF, TXT sau citiți online pe Scribd

0 evaluări0% au considerat acest document util (0 voturi)

13 vizualizări2 paginiP.G. Diploma Examination - 2010: (Vlsi Design)

Încărcat de

rajasekarkprExplain the difference between LSI and MSI Elements. (b) Explain the design of Decorders and Demultiplexes. (c) Explain the usage of mixed logic as a design tool. (d) Differentiate Algorithmic State Machine and Mealy and Moore models. (e) Explain the architecture and operation of different types of ROM. (f) Give the general Architecture of FPGA. (g) Explain how a logic function can be implemented using gate array with an example. (h)

Drepturi de autor:

Attribution Non-Commercial (BY-NC)

Formate disponibile

Descărcați ca PDF, TXT sau citiți online pe Scribd

Sunteți pe pagina 1din 2

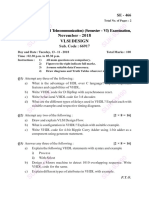

Total No.

of Pages: 2 Register Number: Name of the Candidate:

7046

P.G. DIPLOMA EXAMINATION - 2010

(VLSI DESIGN)

(PAPER II)

120. ASIC DESIGN

December) Maximum: 100 Marks Answer any FIVE questions. 1. (a) Discuss the difference between LSI and MSI Elements. (b) Explain the design of Decorders and Demultiplexes. 2. (a) Implement a Full adder using appropriate Multiplexer. (b) Explain the usage of mixed logic as a design tool. 3. (a) Design a Mod-6 counter using state table reduction method. (b) Differentiate Algorithmic State Machine and Mealy & Moore models. 4. Convert the Moore state diagram given below into an equivalent ASM chart. (Input x1x2, output z1z2) (5 20 = 100) (5) (15) (8) (12) (16) (4) (20) (Time: 3 Hours

5. Explain the architecture and operation of different types of ROM.

(20)

6. (a) Give the general Architecture of FPGA. (5) (b) Explain how a logic function can be implemented using gate array with an example. (15) 7. What is meant by Process in VHDL? Explain process. (i) using Variables; (ii) using Signals. (20)

8. (a) Design a full subtractor and write the VHDL code for a full substrater using logic equations. (14) (b) Write the VHDL description to design a D Flip Flop. (6) 9. (a) Explain the significance of timing simulation in the ASIC design flow. (b) Explain the Hazards and the method to eliminate it in the digital logic circuits. (10) (10)

10. Explain how the micro timing diagram is produced for the logic circuits with an examples. (20) %%%%%%

S-ar putea să vă placă și

- Architecture-Aware Optimization Strategies in Real-time Image ProcessingDe la EverandArchitecture-Aware Optimization Strategies in Real-time Image ProcessingÎncă nu există evaluări

- B. Tech: Microprocessor and Its ApplicationsDocument1 paginăB. Tech: Microprocessor and Its ApplicationsAnant VermaÎncă nu există evaluări

- 9A15502 Digital System DesignDocument4 pagini9A15502 Digital System Designsivabharathamurthy100% (1)

- Digital System Design Using VHDL PaperDocument2 paginiDigital System Design Using VHDL PaperlambajituÎncă nu există evaluări

- ME PAPER (SEM-1) For E.C. GTUDocument59 paginiME PAPER (SEM-1) For E.C. GTUGaurang RathodÎncă nu există evaluări

- (3965) - 636 M.E. (E & TC) : (VLSI & Embedded Systems)Document14 pagini(3965) - 636 M.E. (E & TC) : (VLSI & Embedded Systems)Manu SeaÎncă nu există evaluări

- Embedded Systems and Technologies (M. Tech. IAR)Document3 paginiEmbedded Systems and Technologies (M. Tech. IAR)Gupta RanveerÎncă nu există evaluări

- Advanced Virtual InstrumentationDocument1 paginăAdvanced Virtual InstrumentationSangeetha VeeraÎncă nu există evaluări

- Embedded Systems Model Question PaperDocument6 paginiEmbedded Systems Model Question PaperSubramanyaAIyerÎncă nu există evaluări

- AprMay 2012 (R10)Document38 paginiAprMay 2012 (R10)Rajesh ViswanadhamÎncă nu există evaluări

- Computer Architecture Question BankDocument10 paginiComputer Architecture Question BankaniprahalÎncă nu există evaluări

- Competitive Manufacturing Systems I 002Document58 paginiCompetitive Manufacturing Systems I 002Rajueswar100% (1)

- Dica Question BankDocument4 paginiDica Question BankOmprakash KuswahaÎncă nu există evaluări

- M.E. (VLSI & Embedded System) : Asic Design and Modelling (2008 Course)Document9 paginiM.E. (VLSI & Embedded System) : Asic Design and Modelling (2008 Course)Manu SeaÎncă nu există evaluări

- Iii Ece VlsiDocument2 paginiIii Ece VlsiDelphin RoseÎncă nu există evaluări

- Me 1Document436 paginiMe 1Akshay Mane0% (1)

- Question Paper Code:: Reg. No.Document2 paginiQuestion Paper Code:: Reg. No.Sharath ChandanÎncă nu există evaluări

- Vlsi DesignDocument2 paginiVlsi DesignXXXÎncă nu există evaluări

- VLSI DesignDocument1 paginăVLSI DesignSurendar AviÎncă nu există evaluări

- EC2303 Computer Architecture and Organization QUESTION PAPERDocument4 paginiEC2303 Computer Architecture and Organization QUESTION PAPERJayagopal JaiÎncă nu există evaluări

- (3hours) : CompulsoryDocument7 pagini(3hours) : CompulsorySaima ZainabÎncă nu există evaluări

- University Question Papers - VLSIDocument26 paginiUniversity Question Papers - VLSIVijayÎncă nu există evaluări

- Question BanksDocument74 paginiQuestion BanksVidhya GanesanÎncă nu există evaluări

- MCS-012 MCA (Revised) TR) Term-End Examination cNI June, 2011 0, - Mcs-012: Computer Organisation & Assembly Language ProgrammingDocument3 paginiMCS-012 MCA (Revised) TR) Term-End Examination cNI June, 2011 0, - Mcs-012: Computer Organisation & Assembly Language ProgrammingRajib SahaÎncă nu există evaluări

- Nr-Vlsi Technology and DesignDocument2 paginiNr-Vlsi Technology and DesignSudhakar SpartanÎncă nu există evaluări

- Department of Ece Model Examination Vl9261 - Asic Design: PART B - (5 × 16 80 Marks)Document2 paginiDepartment of Ece Model Examination Vl9261 - Asic Design: PART B - (5 × 16 80 Marks)Anandhi SrinivasanÎncă nu există evaluări

- MCA MGTDocument88 paginiMCA MGTAshfaq KhanÎncă nu există evaluări

- M.E. (VLSI & Embedded Systems) Analog & Digital Cmos Ic Design (2008 Course)Document4 paginiM.E. (VLSI & Embedded Systems) Analog & Digital Cmos Ic Design (2008 Course)Manu SeaÎncă nu există evaluări

- MCS 012Document4 paginiMCS 012trial versionÎncă nu există evaluări

- Sathyabama: Register NumberDocument3 paginiSathyabama: Register NumberBoopalanElumalaiÎncă nu există evaluări

- End Semester Examination, May 2 EC Microprocesso: 008 /COEIIC-311: RSDocument10 paginiEnd Semester Examination, May 2 EC Microprocesso: 008 /COEIIC-311: RSDheeraj AnandÎncă nu există evaluări

- VLSI Design NOV 18Document2 paginiVLSI Design NOV 18Saurabh BhiseÎncă nu există evaluări

- DellDocument6 paginiDellamu_manuÎncă nu există evaluări

- (Maximum Marks: 100) : TED (15) - 6042 Reg. No . (REVISION 2015) Signature .Document2 pagini(Maximum Marks: 100) : TED (15) - 6042 Reg. No . (REVISION 2015) Signature .Akhila AnilÎncă nu există evaluări

- Model PaperDocument2 paginiModel PaperSrinivasa RaoÎncă nu există evaluări

- EC2354 - Nov 2011 - AU QP Anna University Exams - VLSIDocument3 paginiEC2354 - Nov 2011 - AU QP Anna University Exams - VLSISHARANYAÎncă nu există evaluări

- WWW - Manaresults.Co - In: (Common To Ece, Eie, Etm)Document2 paginiWWW - Manaresults.Co - In: (Common To Ece, Eie, Etm)Anil Kumar BÎncă nu există evaluări

- MCS 012dec22Document4 paginiMCS 012dec22kk2760057Încă nu există evaluări

- MCS 012Document118 paginiMCS 012SongYak YamÎncă nu există evaluări

- Computer Aided Design: of Questions: 08Document2 paginiComputer Aided Design: of Questions: 08HarpreetSinghÎncă nu există evaluări

- Set No: 1: Code No: V3219/R07Document4 paginiSet No: 1: Code No: V3219/R07Gopi Pavan JonnadulaÎncă nu există evaluări

- Computer Architecture Question BankDocument10 paginiComputer Architecture Question BankMalk Malik0% (1)

- Computer Architecture and OrganizationDocument6 paginiComputer Architecture and OrganizationRahmantic SwatzÎncă nu există evaluări

- B.C.A. Introduction To Computer Organization June 2009. First YearDocument2 paginiB.C.A. Introduction To Computer Organization June 2009. First YearSudhakar RÎncă nu există evaluări

- Introduction To MicroprocessorDocument9 paginiIntroduction To MicroprocessorAman NurÎncă nu există evaluări

- Structured Digital System Design Question PaperDocument1 paginăStructured Digital System Design Question PaperSatish Bojjawar0% (1)

- PGDCMDocument18 paginiPGDCMMohit ChatapÎncă nu există evaluări

- Btech Ee 5 Sem Microprocessor and Its Applications Nee504 2019Document2 paginiBtech Ee 5 Sem Microprocessor and Its Applications Nee504 2019Dheeraj SaraswatÎncă nu există evaluări

- 5 Oct11Document12 pagini5 Oct11Manu SeaÎncă nu există evaluări

- 9A04401 Switching Theory & Logic DesignDocument4 pagini9A04401 Switching Theory & Logic DesignsivabharathamurthyÎncă nu există evaluări

- VI Sem, Jan, Feb 2005Document4 paginiVI Sem, Jan, Feb 2005Veeresh NicolyteÎncă nu există evaluări

- 6C0065Document4 pagini6C0065Joshua prabuÎncă nu există evaluări

- FPGA Based System DesignDocument2 paginiFPGA Based System Designammayi9845_930467904Încă nu există evaluări

- KVDocument2 paginiKVsrilatha sriÎncă nu există evaluări

- System Software June 2009Document1 paginăSystem Software June 2009Prasad C MÎncă nu există evaluări

- 263 - MCS-012 D18 - CompressedDocument5 pagini263 - MCS-012 D18 - CompressedAbhishek MandalÎncă nu există evaluări

- Bca CBCSDocument51 paginiBca CBCSMathan NaganÎncă nu există evaluări

- Autonomous Institution, Approved by AICTE and Permanently Affiliated To Anna University, ChennaiDocument3 paginiAutonomous Institution, Approved by AICTE and Permanently Affiliated To Anna University, ChennaiKrishna Kumar VelappanÎncă nu există evaluări

- MPI Mid-1 Exam Questions111Document8 paginiMPI Mid-1 Exam Questions111kranthi633Încă nu există evaluări

- (F3, Il#Flt - To ,,nication: Time) Examination, 2K6 701Document14 pagini(F3, Il#Flt - To ,,nication: Time) Examination, 2K6 701Tyler GatesÎncă nu există evaluări

- JNTUA - IV ECE - LPVLSI - Unit V - Leakage Power MinimizationDocument66 paginiJNTUA - IV ECE - LPVLSI - Unit V - Leakage Power Minimizationrajasekarkpr100% (2)

- Power Amplifiers - Power PointDocument33 paginiPower Amplifiers - Power PointrajasekarkprÎncă nu există evaluări

- UNIT 4 - Switched CapacitanceDocument75 paginiUNIT 4 - Switched Capacitancerajasekarkpr100% (1)

- Chapter 3Document17 paginiChapter 3rajasekarkprÎncă nu există evaluări

- 13 - Emf May 2013Document3 pagini13 - Emf May 2013rajasekarkprÎncă nu există evaluări

- Question Bank - Lowpower VLSI Circuits - JNTUADocument3 paginiQuestion Bank - Lowpower VLSI Circuits - JNTUArajasekarkpr100% (5)

- List Engg CollegesDocument7 paginiList Engg CollegespoisonedstarÎncă nu există evaluări

- Bit Serial MultiplierDocument4 paginiBit Serial MultiplierrajasekarkprÎncă nu există evaluări

- ECE 7th Sem R2008Document29 paginiECE 7th Sem R2008rajasekarkprÎncă nu există evaluări

- Implementation of Stronger Aes by Using Dynamic S-Box Dependent of Master KeyDocument9 paginiImplementation of Stronger Aes by Using Dynamic S-Box Dependent of Master KeyrajasekarkprÎncă nu există evaluări

- IntelDocument8 paginiIntelrajasekarkprÎncă nu există evaluări

- PCI6221Document7 paginiPCI6221rajasekarkprÎncă nu există evaluări

- CAD For VLSI Algorithms For VLSI Design Automation by GerezDocument330 paginiCAD For VLSI Algorithms For VLSI Design Automation by Gerezrajasekarkpr89% (9)

- Cad For Vlsi Circuits 2 PDFDocument2 paginiCad For Vlsi Circuits 2 PDFrajasekarkpr100% (1)

- Antenna MeasurementsDocument6 paginiAntenna MeasurementsrajasekarkprÎncă nu există evaluări

- Cad Question Paper PDFDocument3 paginiCad Question Paper PDFrajasekarkprÎncă nu există evaluări