Documente Academic

Documente Profesional

Documente Cultură

SR - To - JK Flip Flop Conversion VHDL Code

Încărcat de

OP2R0 evaluări0% au considerat acest document util (0 voturi)

2K vizualizări2 paginiSR_to_JK Flip Flop Conversion Vhdl Code

Titlu original

SR_to_JK Flip Flop Conversion Vhdl Code

Drepturi de autor

© © All Rights Reserved

Formate disponibile

PDF, TXT sau citiți online pe Scribd

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentSR_to_JK Flip Flop Conversion Vhdl Code

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PDF, TXT sau citiți online pe Scribd

0 evaluări0% au considerat acest document util (0 voturi)

2K vizualizări2 paginiSR - To - JK Flip Flop Conversion VHDL Code

Încărcat de

OP2RSR_to_JK Flip Flop Conversion Vhdl Code

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PDF, TXT sau citiți online pe Scribd

Sunteți pe pagina 1din 2

ONLINE PLATFORM FOR PROGRAMMING AND RESEARCH (OP2R)

S-R_TO_J-K FLIP FLOP CONVERSION VHDL CODE

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

--------------------------------------------------------entity SR_to_JK is

Port ( J,K,clock,reset : in STD_LOGIC;

Q,Q1 : inout STD_LOGIC);

end SR_to_JK;

Library ieee declaration.

In ieee library std_logic_1164 package is

declared for std_logic data types (predefined data

types).

Entity describes circuit external ports.

J, K, clock, reset: - input port to J-K flipflop.

Q, Q1: - output port to J-K flip-flop.

q:- present state, qbar: - next state.

--------------------------------------------------------architecture structural_con of SR_to_JK is

--------------------------------------------------------signal s1,s2:std_logic;

----------------------------------- Signal s1, s2 are declared to hold a

component s_rff

particular value. These are acting as inout

port (s,r,clk,rst:in std_logic;

ports.

x,y:inout std_logic);

Components (s_rff and and1) declaration.

Declarative part of D flip-flops

end component;

architecture.

----------------------------------- Components represent the structure of

component and1 is

converted flip-flop circuit.

port (a,b:in std_logic;

And1 component represents AND

c:out std_logic);

operation in digital circuit.

end component;

-----------------------------------begin

------------------------------------------------------------------------ Statements part of the

a1:and1 port map (J,Q1,s1);

architecture.

a2:and1 port map (Q,K,s2);

Components are port mapped to

ff:s_rff port map (s1,s2,clock,reset,Q,Q1);

perform J-K flip flop operation.

-------------------------------------------------------------------------end structural_con;

INFOOP2R.WIX.COM/OP2R

ONLINE PLATFORM FOR PROGRAMMING AND RESEARCH (OP2R)

RTL VIEW:-

OUTPUT WAVEFORM:-

INFOOP2R.WIX.COM/OP2R

S-ar putea să vă placă și

- SR - To - T Flip Flop Conversion VHDL CodeDocument2 paginiSR - To - T Flip Flop Conversion VHDL CodeOP2RÎncă nu există evaluări

- VHDL Code For Digital Clock On FPGADocument6 paginiVHDL Code For Digital Clock On FPGASidney O. EbotÎncă nu există evaluări

- VHDL Code For 4 Bit Multiplayer and DivisionDocument5 paginiVHDL Code For 4 Bit Multiplayer and Divisionsan521050% (2)

- SR - To - T Flip Flop Conversion VHDL CodeDocument2 paginiSR - To - T Flip Flop Conversion VHDL CodeOP2RÎncă nu există evaluări

- J-K - To - D Flip-Flop Conversion VHDL CodeDocument2 paginiJ-K - To - D Flip-Flop Conversion VHDL CodeOP2RÎncă nu există evaluări

- Full Subtractor VHDL Code Using Structural ModelingDocument2 paginiFull Subtractor VHDL Code Using Structural ModelingOP2RÎncă nu există evaluări

- VHDL ExperimentsDocument55 paginiVHDL Experimentssandeepsingh93Încă nu există evaluări

- Pedroni MITPress 1stedition SolutionSamplesDocument14 paginiPedroni MITPress 1stedition SolutionSamplesTrần Anh DũngÎncă nu există evaluări

- VHDL Code For 4 Bit ComparatorDocument2 paginiVHDL Code For 4 Bit Comparatornady220944% (9)

- VHDL Code For Half Adder by Data Flow ModellingDocument14 paginiVHDL Code For Half Adder by Data Flow ModellingPrateekKumar96% (24)

- Verilog Code For 4 Bit Ring Counter With TestbenchDocument3 paginiVerilog Code For 4 Bit Ring Counter With Testbenchsoumya100% (1)

- Full Subtractor VHDL Code Using Structural ModelingDocument2 paginiFull Subtractor VHDL Code Using Structural ModelingOP2RÎncă nu există evaluări

- Binary To Gray Converter VHDL Code Using Structural ModelingDocument1 paginăBinary To Gray Converter VHDL Code Using Structural ModelingOP2R100% (2)

- S-R Flip Flop Using Behavioural ModelingDocument2 paginiS-R Flip Flop Using Behavioural ModelingOP2RÎncă nu există evaluări

- T Flip-Flop VHDL Code Using Behavioural ModelingDocument2 paginiT Flip-Flop VHDL Code Using Behavioural ModelingOP2R100% (1)

- D Flip Flop - Structural ModelingDocument2 paginiD Flip Flop - Structural ModelingOP2RÎncă nu există evaluări

- D - To - S-R Flip-Flop Conversion VHDL CodeDocument1 paginăD - To - S-R Flip-Flop Conversion VHDL CodeOP2RÎncă nu există evaluări

- Half Adder VHDL Code Using Dataflow ModelingDocument1 paginăHalf Adder VHDL Code Using Dataflow ModelingOP2RÎncă nu există evaluări

- D - To - J-K Flip Flop Conversion VHDL CodeDocument2 paginiD - To - J-K Flip Flop Conversion VHDL CodeOP2RÎncă nu există evaluări

- Half Adder VHDL Code Using Behavioural ModelingDocument1 paginăHalf Adder VHDL Code Using Behavioural ModelingOP2R100% (5)

- Full Subtractor VHDL Code Using Data Flow ModelingDocument1 paginăFull Subtractor VHDL Code Using Data Flow ModelingOP2R100% (1)

- Half Subtractor VHDL Code Using Structrucral ModelingDocument2 paginiHalf Subtractor VHDL Code Using Structrucral ModelingOP2R0% (3)

- Full Adder VHDL Code Using Data Flow ModelingDocument1 paginăFull Adder VHDL Code Using Data Flow ModelingOP2RÎncă nu există evaluări

- Ripple Carry Adder VHDL Code Using Structural ModellingDocument1 paginăRipple Carry Adder VHDL Code Using Structural ModellingOP2R0% (1)

- 2's Complement VHDL Code Using Structrucral ModelingDocument2 pagini2's Complement VHDL Code Using Structrucral ModelingOP2RÎncă nu există evaluări

- Half Subtractor VHDL Code Using Dataflow ModelingDocument1 paginăHalf Subtractor VHDL Code Using Dataflow ModelingOP2RÎncă nu există evaluări

- 1's Complement VHDL Code Using Dataflow ModelingDocument1 pagină1's Complement VHDL Code Using Dataflow ModelingOP2RÎncă nu există evaluări

- Half Adder VHDL Code Using Structrucral ModelingDocument1 paginăHalf Adder VHDL Code Using Structrucral ModelingOP2R100% (2)

- Half Subtractor VHDL Code Using Behavioural ModelingDocument1 paginăHalf Subtractor VHDL Code Using Behavioural ModelingOP2RÎncă nu există evaluări

- Demux VHDL Code Using Behavioural ModelingDocument1 paginăDemux VHDL Code Using Behavioural ModelingOP2RÎncă nu există evaluări

- Full Adder VHDL Code Using Structural ModelingDocument2 paginiFull Adder VHDL Code Using Structural ModelingOP2R91% (11)

- Binary To Excess 3 VHDL Code Using Structural ModelingDocument1 paginăBinary To Excess 3 VHDL Code Using Structural ModelingOP2RÎncă nu există evaluări

- The VHDL Code For 4 Bit Johnson Counter IsDocument3 paginiThe VHDL Code For 4 Bit Johnson Counter Isnishant02111989Încă nu există evaluări

- DC Lab Manual Cycle3Document11 paginiDC Lab Manual Cycle3Kavya M NayakÎncă nu există evaluări

- VHDL Code For CounterDocument1 paginăVHDL Code For Countermnpaliwal020Încă nu există evaluări

- VHDL Code For Updown CNTDocument3 paginiVHDL Code For Updown CNTmeaow88100% (2)

- Design of A 8-Bit ALUDocument13 paginiDesign of A 8-Bit ALUIndranil ChakrabortyÎncă nu există evaluări

- VHDL Code For Flipflop D, JK, SR, TDocument7 paginiVHDL Code For Flipflop D, JK, SR, TPeter HerreraÎncă nu există evaluări

- Half and Full Adder Using VHDLDocument16 paginiHalf and Full Adder Using VHDLnady2209100% (3)

- L9 Understanding Atmega328P 2Document15 paginiL9 Understanding Atmega328P 2VIGHNESH AIYAÎncă nu există evaluări

- 4bit Array MultiplierDocument4 pagini4bit Array MultiplierRahul TiwariÎncă nu există evaluări

- Xlinx - VLSI Practical Lab ManualDocument31 paginiXlinx - VLSI Practical Lab ManualSamarth J Parikh0% (1)

- VHDL Digital NAND Gate Program.Document14 paginiVHDL Digital NAND Gate Program.Muchamad Aldi AnantaÎncă nu există evaluări

- VHDL ProgramDocument5 paginiVHDL ProgramJaswanth TejaÎncă nu există evaluări

- Test Bench For JK FlipDocument2 paginiTest Bench For JK Flipmnpaliwal020100% (2)

- VHDL TD - CorrigéDocument6 paginiVHDL TD - CorrigéSahsah AbdeslamÎncă nu există evaluări

- 02-3-Sequential Logic Synthesis With VHDLDocument18 pagini02-3-Sequential Logic Synthesis With VHDLEdward ConalÎncă nu există evaluări

- 8 Bit ALU by XilinxDocument16 pagini8 Bit ALU by XilinxDIPTANU MAJUMDERÎncă nu există evaluări

- Eee ADocument6 paginiEee ASundaravadivel ArumugamÎncă nu există evaluări

- VHDL Code For A Simple ALUDocument4 paginiVHDL Code For A Simple ALUparammohali100% (1)

- VHDLDocument11 paginiVHDLlizhi0007Încă nu există evaluări

- Flip Flops Verilog CodesDocument3 paginiFlip Flops Verilog Codesavireddy1Încă nu există evaluări

- Single Precision Floating Point UnitDocument46 paginiSingle Precision Floating Point UnitSumeet SauravÎncă nu există evaluări

- Void PPC UpdateDocument41 paginiVoid PPC UpdatePian RispianÎncă nu există evaluări

- HDL Manual 2020 5th Sem E&CE 18ECL58Document74 paginiHDL Manual 2020 5th Sem E&CE 18ECL58vishvakiranaÎncă nu există evaluări

- Design of Binary Multiplier Using Adders-3017 PDFDocument5 paginiDesign of Binary Multiplier Using Adders-3017 PDFAdrian Walter JavierÎncă nu există evaluări

- Digital Logic Design: VHDL Coding For Fpgas Unit 5Document34 paginiDigital Logic Design: VHDL Coding For Fpgas Unit 5Srinivas CherukuÎncă nu există evaluări

- Digital Lab Manual For CSE & IT - Anna Univeristy Chennai Syllabus - 2012Document86 paginiDigital Lab Manual For CSE & IT - Anna Univeristy Chennai Syllabus - 2012sundarkmp532588% (8)

- VHDL Very High Speed Integrated Language: Unit VDocument41 paginiVHDL Very High Speed Integrated Language: Unit VB. MeenakshiÎncă nu există evaluări

- Array MultiplierDocument2 paginiArray MultiplierNitesh Chilakala50% (2)

- Up Down CounterDocument20 paginiUp Down Countersumi36117Încă nu există evaluări

- VHDL ExamplesDocument28 paginiVHDL Examplesapi-3731978Încă nu există evaluări

- J-K Flip Flop Usig Behavioural ModelingDocument2 paginiJ-K Flip Flop Usig Behavioural ModelingOP2RÎncă nu există evaluări

- Ripple Carry Adder VHDL Code Using Structural ModellingDocument1 paginăRipple Carry Adder VHDL Code Using Structural ModellingOP2R0% (1)

- Half Adder VHDL Code Using Behavioural ModelingDocument1 paginăHalf Adder VHDL Code Using Behavioural ModelingOP2R100% (5)

- Half Subtractor VHDL Code Using Dataflow ModelingDocument1 paginăHalf Subtractor VHDL Code Using Dataflow ModelingOP2RÎncă nu există evaluări

- Half Subtractor VHDL Code Using Structrucral ModelingDocument2 paginiHalf Subtractor VHDL Code Using Structrucral ModelingOP2R0% (3)

- Mux VHDL Code Using Behavioural ModelingDocument1 paginăMux VHDL Code Using Behavioural ModelingOP2R100% (1)

- Half Subtractor VHDL Code Using Behavioural ModelingDocument1 paginăHalf Subtractor VHDL Code Using Behavioural ModelingOP2RÎncă nu există evaluări

- Half Adder VHDL Code Using Dataflow ModelingDocument1 paginăHalf Adder VHDL Code Using Dataflow ModelingOP2RÎncă nu există evaluări

- Half Adder VHDL Code Using Structrucral ModelingDocument1 paginăHalf Adder VHDL Code Using Structrucral ModelingOP2R100% (2)

- Full Adder VHDL Code Using Structural ModelingDocument2 paginiFull Adder VHDL Code Using Structural ModelingOP2R91% (11)

- Encoder VHDL Code Using Behavioural ModelingDocument1 paginăEncoder VHDL Code Using Behavioural ModelingOP2RÎncă nu există evaluări

- 2's Complement VHDL Code Using Data Flow ModelingDocument1 pagină2's Complement VHDL Code Using Data Flow ModelingOP2R67% (3)

- Full Adder VHDL Code Using Data Flow ModelingDocument1 paginăFull Adder VHDL Code Using Data Flow ModelingOP2RÎncă nu există evaluări

- Decoder VHDL Code Using Behavioural Flow ModelingDocument1 paginăDecoder VHDL Code Using Behavioural Flow ModelingOP2RÎncă nu există evaluări

- Full Subtractor VHDL Code Using Data Flow ModelingDocument1 paginăFull Subtractor VHDL Code Using Data Flow ModelingOP2R100% (1)

- Demux VHDL Code Using Behavioural ModelingDocument1 paginăDemux VHDL Code Using Behavioural ModelingOP2RÎncă nu există evaluări

- 2's Complement VHDL Code Using Structrucral ModelingDocument2 pagini2's Complement VHDL Code Using Structrucral ModelingOP2RÎncă nu există evaluări

- Binary To Excess 3 VHDL Code Using Structural ModelingDocument1 paginăBinary To Excess 3 VHDL Code Using Structural ModelingOP2RÎncă nu există evaluări

- Xor Gate Beha - ModelingDocument1 paginăXor Gate Beha - ModelingOP2RÎncă nu există evaluări

- 1's Complement VHDL Code Using Dataflow ModelingDocument1 pagină1's Complement VHDL Code Using Dataflow ModelingOP2RÎncă nu există evaluări

- 1's Complement VHDL Code Using Structrucral ModelingDocument1 pagină1's Complement VHDL Code Using Structrucral ModelingOP2RÎncă nu există evaluări

- OR Gate Beha - ModelingDocument1 paginăOR Gate Beha - ModelingOP2RÎncă nu există evaluări

- Xnor Gate Beha - ModelingDocument1 paginăXnor Gate Beha - ModelingOP2RÎncă nu există evaluări

- NAND Gate Beh - ModelingDocument1 paginăNAND Gate Beh - ModelingOP2RÎncă nu există evaluări

- NOR Gate Beha - ModelingDocument1 paginăNOR Gate Beha - ModelingOP2RÎncă nu există evaluări

- And Gate Beh - ModelingDocument1 paginăAnd Gate Beh - ModelingOP2RÎncă nu există evaluări

- P 0456 Automatic Solar Rad TrackerDocument95 paginiP 0456 Automatic Solar Rad TrackerSam Mathew100% (1)

- 174872-Report On Voice Enabled Enterprise ChatbotDocument61 pagini174872-Report On Voice Enabled Enterprise ChatbotBalaji GrandhiÎncă nu există evaluări

- 6.6 MAC Address Table AttackDocument4 pagini6.6 MAC Address Table AttackThoriq ThoriqÎncă nu există evaluări

- Red Hat Enterprise Linux-6-6.8 Release Notes-En-UsDocument65 paginiRed Hat Enterprise Linux-6-6.8 Release Notes-En-Uskamel najjarÎncă nu există evaluări

- Cgaxis Models Volume 118Document26 paginiCgaxis Models Volume 118AntezanaFernandoÎncă nu există evaluări

- ADAMS Summary User GuideDocument58 paginiADAMS Summary User GuideGalliano CantarelliÎncă nu există evaluări

- MP Unit-3Document24 paginiMP Unit-3SARTHAK PANWARÎncă nu există evaluări

- Notes: Nama: Indah Ayuning Tyas Nim:170100926Document4 paginiNotes: Nama: Indah Ayuning Tyas Nim:170100926indahÎncă nu există evaluări

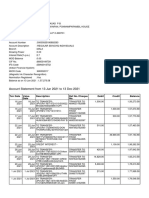

- Account Statement From 13 Jun 2021 To 13 Dec 2021Document10 paginiAccount Statement From 13 Jun 2021 To 13 Dec 2021Syamprasad P BÎncă nu există evaluări

- Question Bank - Module 1 and Module 2Document3 paginiQuestion Bank - Module 1 and Module 2Manasha DeviÎncă nu există evaluări

- Class 8 Art BookDocument17 paginiClass 8 Art BookSrijanÎncă nu există evaluări

- Hamidavi Et Al 2020 - Towards Intelligent Structural Design of Buildings ADocument15 paginiHamidavi Et Al 2020 - Towards Intelligent Structural Design of Buildings ARober Waldir Quispe UlloaÎncă nu există evaluări

- Proposal 2014 BatchDocument5 paginiProposal 2014 BatchimnithinÎncă nu există evaluări

- Security Alarm SystemDocument32 paginiSecurity Alarm SystemAnamika Yadav100% (2)

- Recommender System With Sentiment Analysis: Summer Internship ReportDocument58 paginiRecommender System With Sentiment Analysis: Summer Internship ReportbhargavÎncă nu există evaluări

- Basic Nonlinear Analysis User's Guide: Siemens Siemens SiemensDocument144 paginiBasic Nonlinear Analysis User's Guide: Siemens Siemens Siemensபென்ஸிஹர்Încă nu există evaluări

- A New Method For Encryption Using Fuzzy Set TheoryDocument7 paginiA New Method For Encryption Using Fuzzy Set TheoryAgus S'toÎncă nu există evaluări

- Unit 5 - Cyber SecurityDocument9 paginiUnit 5 - Cyber SecurityDraxÎncă nu există evaluări

- Part III WirelessDocument130 paginiPart III WirelessRalph Laurence G VisayaÎncă nu există evaluări

- Design of Innovative Ship Concepts UsingDocument22 paginiDesign of Innovative Ship Concepts UsingN KoteeswarÎncă nu există evaluări

- AI-powered Technology To Health-Check Soil and Water: Contact: Mathias SteinerDocument22 paginiAI-powered Technology To Health-Check Soil and Water: Contact: Mathias SteinerLucasÎncă nu există evaluări

- SAC Training 01Document11 paginiSAC Training 01Harshal RathodÎncă nu există evaluări

- ACESYS V8.0 - User Manual - AlternateDocument12 paginiACESYS V8.0 - User Manual - AlternateMohamed AdelÎncă nu există evaluări

- IGV AssamblyDocument31 paginiIGV AssamblyPhong le100% (1)

- Chap 5 SerializationDocument7 paginiChap 5 Serializationelwa3erÎncă nu există evaluări

- CRT Learning Module: Course Code Course Title No. of Hours Module TitleDocument16 paginiCRT Learning Module: Course Code Course Title No. of Hours Module TitleEiszel CadacioÎncă nu există evaluări

- LAW Pre Discovery User GuideDocument375 paginiLAW Pre Discovery User GuideShanequa QueenofQueens Stevenson100% (1)

- Stanley Omnilock 2013 Price BookDocument24 paginiStanley Omnilock 2013 Price BookSecurity Lock DistributorsÎncă nu există evaluări

- Payment Notification FNBDocument1 paginăPayment Notification FNBChequeÎncă nu există evaluări

- Binomial DistributionDocument3 paginiBinomial DistributionelminvaldezÎncă nu există evaluări