Documente Academic

Documente Profesional

Documente Cultură

Algorithms For Vlsi Design Automation

Încărcat de

IbmWasuserTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Algorithms For Vlsi Design Automation

Încărcat de

IbmWasuserDrepturi de autor:

Formate disponibile

J

N

T

U

W

O

R

L

D

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

Q6

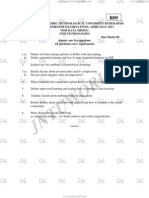

Code No: C5704, C6804, C7704

JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD

M.Tech I SEMESTER EXAMINATIONS, APRIL/MAY-2013

ALGORITHMS FOR VLSI DESIGN AUTOMATION

(COMMON TO VLSI SYSTEM DESIGN, VLSI AND EMBEDDED SYSTEMS,

EMBEDDED SYSTEMS AND VLSI DESIGN)

Time: 3hours Max.Marks:60

Answer any five questions

All questions carry equal marks

- - -

1.a) Explain bottom to top design methodology.

b) How sales man algorithm is related in VLSI design?

2.a) Explain different automation tools preferred in VLSI design flow.

b) Explain dynamic programming with example.

3. Explain ROBBOD manipulation and its principles.

4.a) Explain in detail about Tabu search with pseudo code.

b) Explain in detail about gate level modeling and simulation with examples.

5.a) Explain binary decision diagrams of logic synthesis.

b) Explain the Liao wong algorithm.

6. Explain about packing LUTs to CLBs in FPGAs.

7. Explain FPGA Routing with path finder algorithm.

8.a) Explain MCM physical design cycle.

b) Differentiate chip array based with other methods.

* * * * * * * * * *

R09

www.jntuworld.com

www.jntuworld.com

www.jwjobs.net www.android.jntuworld.com

S-ar putea să vă placă și

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- Hi This Are Sample Shortcut Commands For Msoffice CTRL+B - Bold Ctrl+i - Italic Ctrl+u - Underline CTRL+P - PrintDocument1 paginăHi This Are Sample Shortcut Commands For Msoffice CTRL+B - Bold Ctrl+i - Italic Ctrl+u - Underline CTRL+P - PrintIbmWasuserÎncă nu există evaluări

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- DS Part1Document68 paginiDS Part1IbmWasuserÎncă nu există evaluări

- Python R20 - Unit-4Document30 paginiPython R20 - Unit-4IbmWasuserÎncă nu există evaluări

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- Python R20 - Unit-5Document36 paginiPython R20 - Unit-5IbmWasuserÎncă nu există evaluări

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (895)

- Websphere MQ V6 Setup GuideDocument13 paginiWebsphere MQ V6 Setup GuideIbmWasuserÎncă nu există evaluări

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (344)

- Python R20 - Unit-2Document21 paginiPython R20 - Unit-2IbmWasuserÎncă nu există evaluări

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (399)

- Voltage StabilityDocument1 paginăVoltage StabilityIbmWasuserÎncă nu există evaluări

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (588)

- Advanced Optimization TechniquesDocument2 paginiAdvanced Optimization TechniquesIbmWasuserÎncă nu există evaluări

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- Hi This Are Sample Shortcut Commands For Msoffice CTRL+B - Bold Ctrl+i - Italic Ctrl+u - Underline CTRL+P - PrintDocument1 paginăHi This Are Sample Shortcut Commands For Msoffice CTRL+B - Bold Ctrl+i - Italic Ctrl+u - Underline CTRL+P - PrintIbmWasuserÎncă nu există evaluări

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (266)

- Advanced Compiler DesignDocument2 paginiAdvanced Compiler DesignIbmWasuserÎncă nu există evaluări

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- Advanced MechanicsDocument1 paginăAdvanced MechanicsIbmWasuserÎncă nu există evaluări

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- Advanced Computer Aided DesignDocument1 paginăAdvanced Computer Aided DesignIbmWasuserÎncă nu există evaluări

- Advanced Power System ProtectionDocument1 paginăAdvanced Power System ProtectionIbmWasuser100% (2)

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (73)

- Advanced Digital Signal ProcessingDocument1 paginăAdvanced Digital Signal ProcessingIbmWasuserÎncă nu există evaluări

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- Web ServicesDocument1 paginăWeb ServicesIbmWasuserÎncă nu există evaluări

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- Wireless SecurityDocument1 paginăWireless SecurityIbmWasuserÎncă nu există evaluări

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2259)

- Design Analysis of Experiments Objective ExamDocument8 paginiDesign Analysis of Experiments Objective Examush_ush_ush2005Încă nu există evaluări

- Wireless NetworksDocument1 paginăWireless NetworksIbmWasuserÎncă nu există evaluări

- Wireless Lans and PansDocument1 paginăWireless Lans and PansIbmWasuserÎncă nu există evaluări

- Wireless Networks and Mobile ComputingDocument1 paginăWireless Networks and Mobile ComputingIbmWasuserÎncă nu există evaluări

- Web SecurityDocument1 paginăWeb SecurityIbmWasuserÎncă nu există evaluări

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- Advanced Computer ArchitectureDocument1 paginăAdvanced Computer ArchitectureIbmWasuserÎncă nu există evaluări

- Advanced Compiler DesignDocument2 paginiAdvanced Compiler DesignIbmWasuserÎncă nu există evaluări

- Wireless Communications and NetworksDocument1 paginăWireless Communications and NetworksIbmWasuserÎncă nu există evaluări

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- Web Data MiningDocument1 paginăWeb Data MiningIbmWasuserÎncă nu există evaluări

- Advanced CadDocument1 paginăAdvanced CadIbmWasuserÎncă nu există evaluări

- Advanced CadDocument1 paginăAdvanced CadIbmWasuserÎncă nu există evaluări

- Advanced Digital Signal ProcessingDocument1 paginăAdvanced Digital Signal ProcessingIbmWasuserÎncă nu există evaluări

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (120)

- Advanced Chemical Engineering Plant DesignDocument1 paginăAdvanced Chemical Engineering Plant DesignIbmWasuserÎncă nu există evaluări

- Advanced Casting and Welding TechnologyDocument1 paginăAdvanced Casting and Welding TechnologyIbmWasuserÎncă nu există evaluări

- Software ProblemsDocument22 paginiSoftware ProblemsClaireÎncă nu există evaluări

- Aix Vio Quick ReferenceDocument28 paginiAix Vio Quick ReferenceEaster PanielÎncă nu există evaluări

- D78F9232 NecDocument383 paginiD78F9232 NecM Amjad ZaidÎncă nu există evaluări

- Fault-Tolerant DesignDocument11 paginiFault-Tolerant DesignbenÎncă nu există evaluări

- FreePBX Distro - Graphics Card Problem - FreePBX - Installation - FreePBX Community Forums PDFDocument3 paginiFreePBX Distro - Graphics Card Problem - FreePBX - Installation - FreePBX Community Forums PDFtoppexspÎncă nu există evaluări

- Delta C V200 User Interface GuideDocument16 paginiDelta C V200 User Interface GuideDIEGO GIOVANNY MURILLO RODRIGUEZÎncă nu există evaluări

- How To Extend A Fiori Application - Purchase Order ApprovalDocument40 paginiHow To Extend A Fiori Application - Purchase Order ApprovalNadiaMotylevychÎncă nu există evaluări

- Assessment: Educate, Empower, ExcelDocument3 paginiAssessment: Educate, Empower, Excelkelliy annieÎncă nu există evaluări

- Otosuite BrochureDocument2 paginiOtosuite BrochureTaha ObaidÎncă nu există evaluări

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- SQL Plus: PL/SQL Blocks On The Results of A Query in The Form of ReportsDocument57 paginiSQL Plus: PL/SQL Blocks On The Results of A Query in The Form of Reportshiwot kebedeÎncă nu există evaluări

- XC 131Document186 paginiXC 131Luis Albarracin100% (1)

- Resolving Common Citrix IssuesDocument4 paginiResolving Common Citrix IssuesHaraprasad MahapatroÎncă nu există evaluări

- Managing Sophos Firewall in Sophos CentralDocument32 paginiManaging Sophos Firewall in Sophos CentralOlatunji KehindeÎncă nu există evaluări

- Bios and UefiDocument6 paginiBios and UefiarunÎncă nu există evaluări

- Metashape-Pro 1 7 enDocument187 paginiMetashape-Pro 1 7 enArseni MaximÎncă nu există evaluări

- Quick Start Guide: Step 1: Download From DropboxDocument6 paginiQuick Start Guide: Step 1: Download From DropboxAgoun zakiaÎncă nu există evaluări

- Homework 3Document1 paginăHomework 3Dzaky Zakiyal FawwazÎncă nu există evaluări

- SdailibDocument200 paginiSdailibNourEssÎncă nu există evaluări

- Distributed Data Processing: Business Data Communications, 5eDocument14 paginiDistributed Data Processing: Business Data Communications, 5eanawarangeÎncă nu există evaluări

- Lecture-45 CPU Initiated Conditional Data Transfer: Port 1 Tristate Buffer 8-It LatchDocument9 paginiLecture-45 CPU Initiated Conditional Data Transfer: Port 1 Tristate Buffer 8-It LatchWilliamÎncă nu există evaluări

- Advance Computer Architecture: Dr. Indrajeet KumarDocument21 paginiAdvance Computer Architecture: Dr. Indrajeet KumarindrajeetkumarÎncă nu există evaluări

- Storage Technology FoundationsDocument4 paginiStorage Technology FoundationsAlisa StebukluÎncă nu există evaluări

- Course Outline For WSO2 API Manager 3.1.0: Developer AdvancedDocument9 paginiCourse Outline For WSO2 API Manager 3.1.0: Developer AdvancedCarlos Henrique LemosÎncă nu există evaluări

- Python Regex Cheatsheet With Examples: Re Module FunctionsDocument1 paginăPython Regex Cheatsheet With Examples: Re Module FunctionsAnonymous jyMAzN8EQÎncă nu există evaluări

- JMS Oracle AQDocument4 paginiJMS Oracle AQchelladuraikÎncă nu există evaluări

- Windows XP Hacks, 2nd Edition at - by Preston GrallaDocument2.574 paginiWindows XP Hacks, 2nd Edition at - by Preston GrallaZoroark MichiuÎncă nu există evaluări

- ReluxDocument140 paginiReluxridwanÎncă nu există evaluări

- Current LogDocument69 paginiCurrent LogValdemar Souza WeckÎncă nu există evaluări

- Experion Pks & Masterlogic: Fundamentals - Configuration and Implementation - Student ProgramDocument3 paginiExperion Pks & Masterlogic: Fundamentals - Configuration and Implementation - Student ProgramMohammad SafdarÎncă nu există evaluări