Documente Academic

Documente Profesional

Documente Cultură

Helio Board SCH v1.22

Încărcat de

nanostallmannDescriere originală:

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Helio Board SCH v1.22

Încărcat de

nanostallmannDrepturi de autor:

Formate disponibile

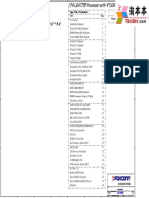

5

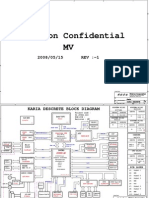

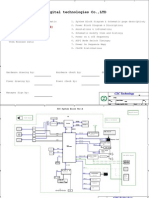

Helio Board

PAGE

C

DESCRIPTION

C

Block Diagram

FPGA Package Top

Cyclone V SoC Bank 3 & 4

Cyclone V SoC Bank 5 & 6

Cyclone V SoC Bank 7

Cyclone V SoC Transceivers & Clocks

PLL

Cyclone V SoC Configuration

JTAG

10

DDR3

11

HSMC

12

Ethernet PHY & RJ45

13

QSPI Flash & Reset Circuit

14

USB 2.0 OTG & Micro SD Card

15

User I/O ,RTC

16

UART

17

On-Board USB Blaster II

18

Power Monitor

19

Power1 - DC Input, 1.1V

20

Power2 - 3.3V

21

Power3 - 1.5V, DDR

22

Power4 - 2.5V, 5V, 1.8V

23

Power5 - 3.3V_EXT

24

Cyclone V SoC Power

25

Cyclone V SoC Capacitor

26

History

Designed

A

NOV. 20, 2013

Drawn

ALTIMA Corporation

NOV. 20, 2013

Checked

1-5-5, Shin-Yokohama, Kouhoku-ku, Yokohama, 222-8563 JAPAN

Title

NOV. 20, 2013

Approval

Helio Board

Size Document Number

A3

NOV. 20, 2013

5

ALTHEL10SOC-R1.2

Date: Wednesday, November 20, 2013

Sheet

1

of

Rev

STEP

1.22

26

FPGA Package Top View

D

Designed

A

NOV. 20, 2013

Drawn

ALTIMA Corporation

NOV. 20, 2013

Checked

1-5-5, Shin-Yokohama, Kouhoku-ku, Yokohama, 222-8563 JAPAN

Title

NOV. 20, 2013

Approval

Helio Board

Size Document Number

A3

NOV. 20, 2013

5

ALTHEL10SOC-R1.2

Date: Wednesday, November 20, 2013

Sheet

1

of

Rev

STEP

1.22

26

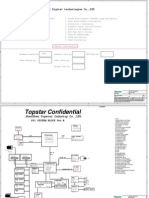

Cyclone V SoC Bank 3 & 4

4

K

N

A

B

C

o

S

X

G

V

E

N

O

L

C

Y

C

U1B

U1A

D

CYCLONE V GX SoC BANK

BA NK 3

HSMA_PRSNTn

HSMA_TX_D_P13

HSMA_TX_D_N13

HSMA_RX_D_P13

HSMA_RX_D_N13

HSMA_RX_D_P8

HSMA_RX_D_N8

HSMA_TX_D_P15

HSMA_TX_D_N15

HSMA_TX_D_P12

HSMA_TX_D_N12

HSMA_RX_D_P11

HSMA_RX_D_N11

AD5

AE4

AF4

AD10

AE9

T11

U11

AE7

AF8

AE8

AF9

AD11

AE11

Bank 3A

DIFFO_TX_B8p,DQ1B

Bank 3B

DIFFIO_TX_B25p,DQ2B,B_WE#

DIFFIO_TX_B32p,DQ2B,B_CAS#

DIFFIO_TX_B25n,GND

DIFFIO_TX_B32n,DQ2B,B_RAS#

DIFFIO_RX_B26p,DQ2B,B_A_14

DIFFIO_TX_B33p,DQ3B,B_BA_0

DIFFIO_RX_B26n,DQ2B,B_A_15

DIFFIO_TX_B33n,GND

DIFFIO_RX_B27p,DQS2B,B_CS#_0

DIFFIO_RX_B34p,DQ3B,B_BA_1

DIFFIO_RX_B27n,DQSn2B,B_CS#_1

DIFFIO_RX_B34n,DQ3B,B_BA_2

DIFFIO_TX_B28p,B_A_12

DIFFIO_RX_B35p,DQS3B,B_CK

DIFFIO_TX_B28n,DQ2B,B_A_13

DIFFIO_RX_B35n,DQSn3B,B_CK#

DIFFIO_TX_B29p,DQ2B,B_A_10

DIFFIO_TX_B36p,B_A_6

DIFFIO_TX_B29n,DQ2B,B_A_11

DIFFIO_TX_B36n,DQ3B,B_A_7

DIFFIO_RX_B30p,DQ2B,B_A_8

DIFFIO_RX_B38p,DQ3B,B_A_4

DIFFIO_RX_B30n,DQ2B,B_A_9

DIFFIO_RX_B38n,DQ3B,B_A_5

DIFFIO_TX_B40p,DQ3B,B_A_0

DIFFIO_TX_B40n,DQ3B,B_A_1

AF5

AF6

AF7

AG6

AF11

AF10

T13

T12

AH3

AH2

AE12

AD12

AH6

AH5

HSMA_TX_D_P14

HSMA_TX_D_N14

HSMA_TX_D_P16

HSMA_TX_D_N16

HSMA_RX_D_P12

HSMA_RX_D_N12

HSMA_RX_D_P16

HSMA_RX_D_N16

HSMA_TX_D_P11

HSMA_TX_D_N11

HSMA_RX_D_P9

HSMA_RX_D_N9

HSMA_TX_D_P10

HSMA_TX_D_N10

5CSXFC6C6U23

2.5V

1.5V

C426 0.1uF

C427 0.1uF

R1

2K

R2

2K

AG8

AG13

AF13

U14

U13

AG9

AH8

AG10

AH9

AF15

AE15

AG11

AH11

AH12

DIFFIO_TX_B41p,DQ4B,B_DQ_2

DIFFIO_RX_B42p,DQ4B,B_DQ_1

DIFFIO_RX_B42n,DQ4B,B_DQ_0

DIFFIO_RX_B43p,DQS4B,B_DQS_0

DIFFIO_RX_B43n,DQSn4B,B_DQS#_0

DIFFIO_TX_B44p,B_ODT_0

DIFFIO_TX_B44n,DQ4B,B_DQ_3

DIFFIO_TX_B45p,DQ4B,B_DQ_6

DIFFIO_TX_B45n,DQ4B,B_ODT_1

DIFFIO_RX_B46p,DQ4B,B_DQ_5

DIFFIO_RX_B46n,DQ4B,B_DQ_4

DIFFIO_TX_B48p,DQ4B,B_DM_0

DIFFIO_TX_B48n,DQ4B,B_DQ_7

DIFFIO_TX_B49p,DQ5B,B_DQ_10

HSMA_RX_D_P5

HSMA_RX_D_N5

HSMA_RX_D_P15

HSMA_RX_D_N15

HSMA_TX_D_P6

HSMA_TX_D_N6

HSMA_TX_D_P5

HSMA_TX_D_N5

HSMA_RX_D_P4

HSMA_RX_D_N4

HSMA_TX_D_P4

HSMA_TX_D_N4

HSMA_D2

AF17

AG16

W14

V13

AG14

AH13

AG15

AH14

AD17

AE17

AH17

AH16

AF18

DIFFIO_RX_B50p,DQ5B,B_DQ_9

DIFFIO_RX_B50n,DQ5B,B_DQ_8

DIFFIO_RX_B51p,DQS5B,B_DQS_1

DIFFIO_RX_B51n,DQSn5B,B_DQS#_1

DIFFIO_TX_B52p,B_CKE_1

DIFFIO_TX_B52n,DQ5B,B_DQ_11

DIFFIO_TX_B53p,DQ5B,B_DQ_14

DIFFIO_TX_B53n,DQ5B,B_CKE_0

DIFFIO_RX_B54p,DQ5B,B_DQ_13

DIFFIO_RX_B54n,DQ5B,B_DQ_12

DIFFIO_TX_B56p,DQ5B,B_DM_1

DIFFIO_TX_B56n,DQ5B,B_DQ_15

DIFFIO_TX_B57p,DQ6B,B_DQ_18

HSMA_RX_D_P3

HSMA_RX_D_N3

HSMA_RX_D_P7

HSMA_RX_D_N7

HSMA_TX_D_P3

HSMA_TX_D_N3

AE19

AD19

AA19

AA18

AG18

AH18

DIFFIO_RX_B58p,DQ6B,B_DQ_17

DIFFIO_RX_B58n,DQ6B,B_DQ_16

DIFFIO_RX_B59p,DQS6B,B_DQS_2

DIFFIO_RX_B59n,DQSn6B,B_DQS#_2

DIFFIO_TX_B60p,B_RESET#

DIFFIO_TX_B60n,DQ6B,B_DQ_19

AH7

HSMA_D3

DIFFIO_TX_B61p,DQ6B,B_DQ_22

DIFFIO_TX_B61n,DQ6B,GND

DIFFIO_RX_B62p,DQ6B,B_DQ_21

DIFFIO_RX_B62n,DQ6B,B_DQ_20

DIFFIO_TX_B64p,DQ6B,B_DM_2

DIFFIO_TX_B64n,DQ6B,B_DQ_23

DIFFIO_TX_B65p,DQ7B,B_DQ_26

AG19

AH19

AE20

AD20

AF20

AG20

AG21

HSMA_TX_D_P2

HSMA_TX_D_N2

HSMA_RX_D_P2

HSMA_RX_D_N2

HSMA_TX_D_P0

HSMA_TX_D_N0

HV_USB_B2_SCL

DIFFIO_RX_B66p,DQ7B,B_DQ_25

DIFFIO_RX_B66n,DQ7B,B_DQ_24

DIFFIO_RX_B67p,DQS7B,B_DQS_3

DIFFIO_RX_B67n,DQSn7B,B_DQS#_3

AF22

AF21

AD23

AE22

HSMA_RX_D_P1

HSMA_RX_D_N1

HSMA_RX_D_P0

HSMA_RX_D_N0

DIFFIO_TX_B68n,DQ7B,B_DQ_27

DIFFIO_TX_B69p,DQ7B,B_DQ_30

DIFFIO_TX_B69n,DQ7B,GND

DIFFIO_RX_B70p,DQ7B,B_DQ_29

DIFFIO_RX_B70n,DQ7B,B_DQ_28

DIFFIO_TX_B72p,DQ7B,B_DM_3

DIFFIO_TX_B72n,DQ7B,B_DQ_31

DIFFIO_TX_B73p,DQ8B,B_DQ_34

AH21

AH23

AH22

AG23

AF23

AG24

AH24

AG26

HV_USB_B2_SDA

HSMA_TX_D_P1

HSMA_TX_D_N1

HV_USB_B2_DATA4

HV_USB_B2_DATA5

HV_USB_B2_DATA3

HV_USB_B2_DATA0

HV_USB_B2_DATA1

DIFFIO_RX_B74p,DQ8B,B_DQ_33

DIFFIO_RX_B74n,DQ8B,B_DQ_32

DIFFIO_RX_B75p,DQS8B,B_DQS_4

DIFFIO_RX_B75n,DQSn8B,B_DQS#_4

AE24

AE23

AC22

AC23

HV_USB_B2_DATA6

HV_USB_B2_DATA7

HV_USB_B2_RESETn

DIFFIO_TX_B76n,DQ8B,B_DQ_35

DIFFIO_TX_B77p,DQ8B,B_DQ_38

DIFFIO_TX_B77n,DQ8B,GND

DIFFIO_RX_B78p,DQ8B,B_DQ_37

DIFFIO_RX_B78n,DQ8B,B_DQ_36

DIFFIO_TX_B80p,DQ8B,B_DM_4

DIFFIO_TX_B80n,DQ8B,B_DQ_39

AH26

AG28

AH27

AF25

AG25

AF27

AF28

HV_USB_B2_OEn

Bank 4A

RZQ_0,DIFFIO_TX_B41n

VCC

8

1

2

VCC_IO1

VCC_IO2

GND

VL

TRI_STATE

HV_USB_B2_RDn

HV_USB_B2_WRn

HV_USB_B2_DATA2

HV_USB_B2_EMPTY

HV_USB_B2_FULL

VL_IO1

VL_IO2

5

4

USB_SCL 17

USB_SDA 17

HSMA_PRSNTn

HSMA_PRSNTn 11

HSMA_D[3..0]

HSMA_D[3..0] 11

HSMA_TX_D_P[16..0]

HSMA_TX_D_P[16..0] 11

HSMA_TX_D_N[16..0]

2.5V

1.5V

0.1uF

USB_B2_CLK 7,17

3

6

MAX3373EEKA+T

C1

OVERTEMP 18

5CSXFC6C6U23

U2

HV_USB_B2_SCL

HV_USB_B2_SDA

HSMA_D0

HSMA_RX_D_P10

HSMA_RX_D_N10

HSMA_RX_D_P14

HSMA_RX_D_N14

HSMA_TX_D_P9

HSMA_TX_D_N9

HSMA_TX_D_P8

HSMA_TX_D_N8

HSMA_RX_D_P6

HSMA_RX_D_N6

HSMA_TX_D_P7

HSMA_TX_D_N7

HSMA_D1

U3

C2

16

VCC

20

19

18

17

14

13

12

11

IO_VCC1

IO_VCC2

IO_VCC3

IO_VCC4

IO_VCC5

IO_VCC6

IO_VCC7

IO_VCC8

15

GND

VL

HSMA_TX_D_N[16..0] 11

HSMA_RX_D_P[16..0]

0.1uF

FPGA USB INTERFACE

HSMA_RX_D_P[16..0] 11

HSMA_RX_D_N[16..0]

HSMA_RX_D_N[16..0] 11

HV_USB_B2_RESETn

HV_USB_B2_EMPTY

HV_USB_B2_RDn

HV_USB_B2_WRn

HV_USB_B2_OEn

HV_USB_B2_FULL

IO_VL1

IO_VL2

IO_VL3

IO_VL4

IO_VL5

IO_VL6

IO_VL7

IO_VL8

1

2

3

4

7

8

9

10

USB_RESETn 17

USB_EMPTY 17

USB_RDn 17

USB_WRn 17

USB_OEn 17

USB_FULL 17

1.5V

EN

R3

1K

MAX3013EUP

2.5V

C3

0.1uF

HV_USB_B2_DATA5

HV_USB_B2_DATA6

HV_USB_B2_DATA2

HV_USB_B2_DATA1

HV_USB_B2_DATA4

HV_USB_B2_DATA0

HV_USB_B2_DATA3

HV_USB_B2_DATA7

1.5V

U4

C4

16

VCC

20

19

18

17

14

13

12

11

IO_VCC1

IO_VCC2

IO_VCC3

IO_VCC4

IO_VCC5

IO_VCC6

IO_VCC7

IO_VCC8

15

GND

VL

IO_VL1

IO_VL2

IO_VL3

IO_VL4

IO_VL5

IO_VL6

IO_VL7

IO_VL8

0.1uF

5

1

2

3

4

7

8

9

10

USB_B2_DATA5

USB_B2_DATA6

USB_B2_DATA2

USB_B2_DATA1

USB_B2_DATA4

USB_B2_DATA0

USB_B2_DATA3

USB_B2_DATA7

R4

USB_B2_DATA[7..0] 17

Designed

A

NOV. 20, 2013

Drawn

ALTIMA Corporation

1.5V

EN

1K

NOV. 20, 2013

Checked

MAX3013EUP

1-5-5, Shin-Yokohama, Kouhoku-ku, Yokohama, 222-8563 JAPAN

Title

NOV. 20, 2013

Approval

Helio Board

Size Document Number

A3

NOV. 20, 2013

5

ALTHEL10SOC-R1.2

Date: Wednesday, November 20, 2013

Sheet

1

of

Rev

STEP

1.22

26

Cyclone V SoC Bank 5, 6

USER_PB_HPS[3..0]

USER_PB_HPS[3..0] 15

USER_DIPSW_HPS[3..0]

USER_DIPSW_HPS[3..0] 15

U1D

CYCLONE V GX SoC BANK

B ANK 6

U1C

CYCLONE V GX SoC BANK

BA NK 5

Y17

Y18

Y16

18 I2C_SCL_FPGA

18 I2C_SDA_FPGA

DIFFIO_RX_R4p,DQ1R

DIFFIO_RX_R4n,DQ1R

DIFFIO_RX_R6p,DQS1R

AA24

AA23

V16

V15

DIFFIO_TX_R7p,DQ1R

DIFFIO_TX_R7n

DIFFIO_RX_R8p,DQ1R

DIFFIO_RX_R8n,DQ1R

AB25

RZQ_2,DIFFIO_TX_R24n

Bank 5A

RZQ_1,DIFFIO_TX_R1p,DQ1R

R5

AF26

Bank 5B

100_1%

DDR3_HPS_A0

DDR3_HPS_A1

DDR3_HPS_A2

DDR3_HPS_A3

DDR3_HPS_A4

DDR3_HPS_A5

DDR3_HPS_A6

DDR3_HPS_A7

DDR3_HPS_A8

DDR3_HPS_A9

DDR3_HPS_A10

DDR3_HPS_A11

DDR3_HPS_A12

DDR3_HPS_A13

DDR3_HPS_A14

5CSXFC6C6U23

10 DDR3_HPS_CK_P

10 DDR3_HPS_CK_N

10 DDR3_HPS_CKE

DDR3_HPS_BA0

DDR3_HPS_BA1

DDR3_HPS_BA2

10 DDR3_HPS_RASn

10 DDR3_HPS_CASn

10 DDR3_HPS_WEn

10 DDR3_HPS_CSn

10 DDR3_HPS_ODT

DDR3_HPS_DM2

DDR3_HPS_DQS_P2

DDR3_HPS_DQS_N2

DDR3_HPS_DQ16

DDR3_HPS_DQ17

DDR3_HPS_DQ18

DDR3_HPS_DQ19

DDR3_HPS_DQ20

DDR3_HPS_DQ21

DDR3_HPS_DQ22

DDR3_HPS_DQ23

HPS_RZQ_0

HPS_DDR,HPS_A_0

HPS_DDR,HPS_A_1

HPS_DDR,HPS_A_2

HPS_DDR,HPS_A_3

HPS_DDR,HPS_A_4

HPS_DDR,HPS_A_5

HPS_DDR,HPS_A_6

HPS_DDR,HPS_A_7

HPS_DDR,HPS_A_8

HPS_DDR,HPS_A_9

HPS_DDR,HPS_A_10

HPS_DDR,HPS_A_11

HPS_DDR,HPS_A_12

HPS_DDR,HPS_A_13

HPS_DDR,HPS_A_14

HPS_DDR,HPS_A_15

N21

N20

L28

K28

A27

H25

G25

A25

A26

E25

L21

L20

D28

G26

HPS_DDR,HPS_CK

HPS_DDR,HPS_CK#

HPS_DDR,HPS_CKE_0

HPS_DDR,HPS_CKE_1

HPS_DDR,HPS_BA_0

HPS_DDR,HPS_BA_1

HPS_DDR,HPS_BA_2

HPS_DDR,HPS_RAS#

HPS_DDR,HPS_CAS#

HPS_DDR,HPS_WE#

HPS_DDR,HPS_CS#_0

HPS_DDR,HPS_CS#_1

HPS_DDR,HPS_ODT_0

HPS_DDR,HPS_ODT_1

W28

T19

T18

N24

N25

T28

U28

N26

N27

R27

V27

Bank 6B

HPS_DDR,HPS_DM_2

HPS_DDR,HPS_DQS_2

HPS_DDR,HPS_DQS#_2

HPS_DDR,HPS_DQ_16

HPS_DDR,HPS_DQ_17

HPS_DDR,HPS_DQ_18

HPS_DDR,HPS_DQ_19

HPS_DDR,HPS_DQ_20

HPS_DDR,HPS_DQ_21

HPS_DDR,HPS_DQ_22

HPS_DDR,HPS_DQ_23

DDR3_HPS_DM3

AB28

DDR3_HPS_DQS_P3 U19

DDR3_HPS_DQS_N3 T20

DDR3_HPS_DQ24

R26

DDR3_HPS_DQ25

R25

DDR3_HPS_DQ26 AA28

DDR3_HPS_DQ27

W26

DDR3_HPS_DQ28

R24

DDR3_HPS_DQ29

T24

DDR3_HPS_DQ30

Y27

DDR3_HPS_DQ31 AA27

Bank 6A

D25

C28

B28

E26

D26

J21

J20

C26

B26

F26

F25

A24

B24

D24

C24

G23

F24

HPS_DDR,HPS_DM_0

HPS_DDR,HPS_DQS_0

HPS_DDR,HPS_DQS#_0

HPS_DDR,HPS_DQ_0

HPS_DDR,HPS_DQ_1

HPS_DDR,HPS_DQ_2

HPS_DDR,HPS_DQ_3

HPS_DDR,HPS_DQ_4

HPS_DDR,HPS_DQ_5

HPS_DDR,HPS_DQ_6

HPS_DDR,HPS_DQ_7

G28

R17

R16

J25

J24

E28

D27

J26

K26

G27

F28

DDR3_HPS_DM0

DDR3_HPS_DQS_P0

DDR3_HPS_DQS_N0

DDR3_HPS_DQ0

DDR3_HPS_DQ1

DDR3_HPS_DQ2

DDR3_HPS_DQ3

DDR3_HPS_DQ4

DDR3_HPS_DQ5

DDR3_HPS_DQ6

DDR3_HPS_DQ7

HPS_DDR,HPS_DM_1

HPS_DDR,HPS_DQS_1

HPS_DDR,HPS_DQS#_1

HPS_DDR,HPS_DQ_8

HPS_DDR,HPS_DQ_9

HPS_DDR,HPS_DQ_10

HPS_DDR,HPS_DQ_11

HPS_DDR,HPS_DQ_12

HPS_DDR,HPS_DQ_13

HPS_DDR,HPS_DQ_14

HPS_DDR,HPS_DQ_15

P28

R19

R18

K25

L25

J27

J28

M27

M26

M28

N28

DDR3_HPS_DM1

DDR3_HPS_DQS_P1

DDR3_HPS_DQS_N1

DDR3_HPS_DQ8

DDR3_HPS_DQ9

DDR3_HPS_DQ10

DDR3_HPS_DQ11

DDR3_HPS_DQ12

DDR3_HPS_DQ13

DDR3_HPS_DQ14

DDR3_HPS_DQ15

HPS_GPI3

HPS_GPI2

HPS_GPI1

HPS_GPI0

R21

R20

K27

M25

HPS_DDR,HPS_DM_4

HPS_DDR,HPS_DQS_4

HPS_DDR,HPS_DQS#_4

HPS_DDR,HPS_DQ_32

HPS_DDR,HPS_DQ_33

HPS_DDR,HPS_DQ_34

HPS_DDR,HPS_DQ_35

HPS_DDR,HPS_DQ_36

HPS_DDR,HPS_DQ_37

HPS_DDR,HPS_DQ_38

HPS_DDR,HPS_DQ_39

AE28

V18

V17

T26

U25

AC28

V25

V19

V20

AE27

AD28

HPS_GPI13

HPS_GPI12

HPS_GPI11

HPS_GPI10

HPS_GPI9

HPS_GPI8

HPS_GPI7

HPS_GPI6

HPS_GPI5

HPS_GPI4

V24

AC27

U16

U15

Y26

Y28

T16

T17

P26

R28

USER_DIPSW_HPS0

USER_DIPSW_HPS1

USER_DIPSW_HPS2

USER_DIPSW_HPS3

USER_PB_HPS0

USER_PB_HPS1

USER_PB_HPS2

USER_PB_HPS3

V28

R429

HPS_DDR,HPS_DM_3

HPS_DDR,HPS_DQS_3

HPS_DDR,HPS_DQS#_3

HPS_DDR,HPS_DQ_24

HPS_DDR,HPS_DQ_25

HPS_DDR,HPS_DQ_26

HPS_DDR,HPS_DQ_27

HPS_DDR,HPS_DQ_28

HPS_DDR,HPS_DQ_29

HPS_DDR,HPS_DQ_30

HPS_DDR,HPS_DQ_31

HPS_DDR,HPS_RESET#

22

DDR3_HPS_RESETn 10

5CSXFC6C6U23

DDR3_HPS_A[14..0]

DDR3_HPS_A[14..0] 10

DDR3_HPS_BA[2..0]

DDR3_HPS_BA[2..0] 10

DDR3_HPS_DQS_P[3..0]

DDR3_HPS_DQS_P[3..0] 10

DDR3_HPS_DQS_N[3..0]

DDR3_HPS_DQS_N[3..0] 10

DDR_HPS_DQ[31..0]

DDR3_HPS_DQ[31..0] 10

DDR3_HPS_DM[3..0]

DDR3_HPS_DM[3..0] 10

Designed

A

NOV. 20, 2013

Drawn

ALTIMA Corporation

NOV. 20, 2013

Checked

1-5-5, Shin-Yokohama, Kouhoku-ku, Yokohama, 222-8563 JAPAN

Title

NOV. 20, 2013

Approval

Helio Board

Size Document Number

A3

NOV. 20, 2013

5

ALTHEL10SOC-R1.2

Date: Wednesday, November 20, 2013

Sheet

1

of

Rev

STEP

1.22

26

ETHERNET INTERFACE

Cyclone V SoC Bank 7

ENET_HPS_TXD[3..0]

ENET_HPS_TXD[3..0] 12

ENET_HPS_GTX_CLK

ENET_HPS_TX_EN

ENET_HPS_MDC

ENET_HPS_GTX_CLK 12

ENET_HPS_TX_EN 12

ENET_HPS_MDC 12

3.3V

R6

4.7K_1%

ENET_HPS_RXD[3..0]

JTAG_HPS_TRST

CYCLONE V GX SoC BANK

BA NK 7

3.3V

13 HPS_RESETn

9 JTAG_HPS_TDO

R7

4.7K_1%

9 JTAG_HPS_TMS

9 JTAG_HPS_TCK

9 JTAG_HPS_TRST

9 JTAG_HPS_TDI

MICTOR_RSTn

HPS_RESETn

JTAG_HPS_TRST

7 CLK_OSC1

7 CLK_OSC2

TRACE_CLK_MIC

TRACE_DATA0

TRACE_DATA1

TRACE_DATA2

CLKSEL0

XJ4

J17

1

2

3

XJ8A-0211

3.3V

10K

UART_TX

R25

10K

ENET_HPS_RXD1

ENET_HPS_RX_CLK

ENET_HPS_TX_EN

ENET_HPS_RX_DV

ENET_HPS_MDC

ENET_HPS_MDIO

ENET_HPS_RXD0

ENET_HPS_TXD3

ENET_HPS_TXD2

ENET_HPS_TXD1

ENET_HPS_TXD0

R19

XG8S-0331

CLKSEL1

XJ6

XJ8A-0211

J19

3.3V

10K

1 R20

CLKSEL1

2

10K

3 R27

R9

R11

R13

R15

14 SD_CD_DAT3

14 SD_DAT2

14 SD_CLK

XG8S-0331

USB_DATA6

USB_DATA5

USB_DATA7

USB_CLK

USB_NXT

USB_DIR

USB_STP

0

22

22

22

A23

H19

B23

HPS_nRST

HPS_nPOR

HPS_TDO

C23

K19

C22

D22

E18

E20

D20

HPS_TMS

HPS_TCK

HPS_TRST

HPS_TDI

HPS_PORSEL

HPS_CLK1

HPS_CLK2

Bank 7A

CAN0_TX,CLKSEL0,UART0_TX,SPIM1_SS0,HPS_GPIO66

CAN0_RX,UART0_RX,SPIM1_MISO,HPS_GPIO65

I2C0_SCL,UART1_TX,SPIM1_MOSI,HPS_GPIO64

I2C0_SDA,UART1_RX,SPIM1_CLK,HPS_GPIO63

UART0_TX,CLKSEL1,CAN0_TX,SPIM1_SS1,HPS_GPIO62

UART0_RX,CAN0_RX,SPIM0_SS1,HPS_GPIO61

SPIM0_SS0,BOOTSEL0,CAN1_TX,UART1_RTS,HPS_GPIO60

SPIM0_MISO,CAN1_RX,UART1_CTS,HPS_GPIO59

SPIM0_MOSI,I2C1_SCL,UART0_RTS,HPS_GPIO58

SPIM0_CLK,I2C1_SDA,UART0_CTS,HPS_GPIO57

TRACE_D7,SPIS1_MISO,I2C0_SCL,HPS_GPIO56

TRACE_D6,SPIS1_SS0,I2C0_SDA,HPS_GPIO55

TRACE_D5,SPIS1_MOSI,CAN1_TX,HPS_GPIO54

TRACE_D4,SPIS1_CLK,CAN1_RX,HPS_GPIO53

TRACE_D3,SPIS0_SS0,I2C1_SCL,HPS_GPIO52

C21

A22

B21

A21

TRACE_CLK,HPS_GPIO48

TRACE_D0,SPIS0_CLK,UART0_RX,HPS_GPIO49

TRACE_D1,SPIS0_MOSI,UART0_TX,HPS_GPIO50

TRACE_D2,SPIS0_MISO,I2C1_SDA,HPS_GPIO51

A11

J12

A12

J13

A13

E16

A14

D17

A15

J14

A16

NAND_DQ6,RGMII1_RXD1,USB1_D7,HPS_GPIO25

Bank 7B

NAND_DQ5,RGMII1_RX_CLK,USB1_D6,HPS_GPIO24

NAND_DQ4,RGMII1_TX_CTL,USB1_D5,HPS_GPIO23

NAND_DQ3,RGMII1_RX_CTL,USB1_D4,HPS_GPIO22

NAND_DQ2,RGMII1_MDC,I2C3_SCL,HPS_GPIO21

NAND_DQ1,RGMII1_MDIO,I2C3_SDA,HPS_GPIO20

NAND_DQ0,RGMII1_RXD0,,HPS_GPIO19

NAND_RB,RGMII1_TXD3,USB1_D3,HPS_GPIO18

NAND_RE,RGMII1_TXD2,USB1_D2,HPS_GPIO17

NAND_CLE,RGMII1_TXD1,USB1_D1,HPS_GPIO16

NAND_CE,RGMII1_TXD0,USB1_D0,HPS_GPIO15

B9

B11

B8

B12

B4

H12

SDMMC_D3,USB0_NXT,HPS_GPIO47

SDMMC_D2,USB0_DIR,HPS_GPIO46

SDMMC_CLK,USB0_STP,HPS_GPIO45

SDMMC_CLK_IN,USB0_CLK,HPS_GPIO44

SDMMC_D7,USB0_D7,HPS_GPIO43

SDMMC_D6,USB0_D6,HPS_GPIO42

C7

D4

F4

G4

D5

E5

C5

NAND_ALE,RGMII1_TX_CLK,QSPI_SS3,HPS_GPIO14

NAND_DQ7,RGMII1_RXD2,HPS_GPIO26

NAND_WP,RGMII1_RXD3,QSPI_SS2,HPS_GPIO27

NAND_WE,BOOTSEL2,QSPI_SS1,,HPS_GPIO28

QSPI_IO0,USB1_CLK,HPS_GPIO29

QSPI_IO1,USB1_STP,HPS_GPIO30

QSPI_IO2,USB1_DIR,HPS_GPIO31

QSPI_IO3,USB1_NXT,HPS_GPIO32

QSPI_SS0,BOOTSEL1,HPS_GPIO33

QSPI_CLK,HPS_GPIO34

QSPI_SS1,HPS_GPIO35

Bank 7C

RGMII0_MDC ,USB1_D6,I2C2_SCL,HPS_GPIO7

RGMII0_MDIO,USB1_D5,I2C2_SDA,HPS_GPIO6

RGMII0_RX_CTL,USB1_D7,HPS_GPIO8

RGMII0_RX_CLK,USB1_CLK,HPS_GPIO10

RGMII0_RXD3,USB1_NXT,HPS_GPIO13

RGMII0_RXD2,USB1_DIR,HPS_GPIO12

RGMII0_RXD1,USB1_STP,HPS_GPIO11

CLKSEL1

SPI_CSn

R8

R10

R12

R14

R16

22

22

22

22

22

D14

A5

C13

B6

H13

A4

RGMII0_RXD0,USB1_D4,HPS_GPIO5

RGMII0_TXD3,USB1_D3,HPS_GPIO4

RGMII0_TXD2,USB1_D2,HPS_GPIO3

RGMII0_TXD1,USB1_D1,HPS_GPIO2

RGMII0_TXD0,USB1_D0,HPS_GPIO1

RGMII0_TX_CLK,HPS_GPIO0

RGMII0_TX_CTL,HPS_GPIO9

C8

C4

C9

F5

C10

E4

C6

TRACE_DATA7

TRACE_DATA6

TRACE_DATA5

TRACE_DATA4

TRACE_DATA3

USER_HPS_GPIO61 15

SPI_CSn 15

SPI_MISO 15

SPI_MOSI 15

SPI_CLK 15

BOOTSEL0

3.3V

J16

R23

10K

SPI_CSn

R30

10K

XJ3

1

2

3

XJ8A-0211

XG8S-0331

BOOTSEL1

3.3V

QSPI_IO0

QSPI_IO1

QSPI_IO2

QSPI_IO3

QSPI_SS0

QSPI_CLK

J18

R24

10K

QSPI_SS0

R32

10K

13

13

13

13

13

13

XJ5

1

2

3

XJ8A-0211

XG8S-0331

C

BOOTSEL2

SD_CMD 14

3.3V

SD_DAT0 14

SD_DAT1 14

J20

R26

10K

BOOTSEL2

R34

10K

XJ7

1

2

3

XJ8A-0211

XG8S-0331

USB_DATA4

USB_DATA3

USB_DATA2

USB_DATA1

USB_DATA0

USB_RESET

CONV_HPS_USB_N 16

USB INTERFACE

USB_RESET

USB_CLK

USB_NXT

USB_DIR

USB_STP

USB_DATA[7..0]

3.3V

4.7K_1%

4.7K_1%

ENET_HPS_RX_CLK 12

ENET_HPS_RX_DV 12

ENET_HPS_MDIO 12

ENET_HPS_INTn 12

UART_TX 16

UART_RX 16

I2C_SCL_HPS 12,15,18

I2C_SDA_HPS 12,15,18

J15 ENET_HPS_GTX_CLK

ENET_HPS_RXD2

C15

ENET_HPS_RXD3

A9

BOOTSEL2

D15

A8

H16

A7

J16

QSPI_SS0

A6

C14

ENET_HPS_INTn

B14

SDMMC_CMD,USB0_D0,HPS_GPIO36

SDMMC_PWREN,USB0_D1,HPS_GPIO37

SDMMC_D0,USB0_D2,HPS_GPIO38

SDMMC_D1,USB0_D3,HPS_GPIO39

SDMMC_D4,USB0_D4,HPS_GPIO40

SDMMC_D5,USB0_D5,HPS_GPIO41

Bank 7D

UART_TX

C16

B19

B16

C19

H17

A17

J17

B18

C17

A18

C18

A19

J18

A20

K18

5CSXFC6C6U23

R17

R18

ENET_HPS_RXD[3..0] 12

ENET_HPS_RX_CLK

ENET_HPS_RX_DV

ENET_HPS_MDIO

ENET_HPS_INTn

U1E

JTAG_MICTOR_TMS

JTAG_MICTOR_TDI

USB_RESET 14

USB_CLK 14

USB_NXT 14

USB_DIR 14

USB_STP 14

USB_DATA[7..0] 14

J1

9,13 MICTOR_RSTn

9 JTAG_MICTOR_TDI

9 JTAG_MICTOR_TCK

9 JTAG_MICTOR_TMS

9 JTAG_MICTOR_TDO

9 JTAG_MICTOR_TRST

R28

10K

MICTOR_RSTn

JTAG_MICTOR_TDI

JTAG_MICTOR_TCK

JTAG_MICTOR_TMS

JTAG_MICTOR_TDO

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

5VDC

GND

CLKE

D15E

D14E

D13E

D12E

D11E

D10E

D9E

D8E

D7E

D6E

D5E

D4E

D3E

D2E

D1E

D0E

SCL

SDA

CLKO

D15O

D14O

D13O

D12O

D11O

D10O

D9O

D8O

D7O

D6O

D5O

D4O

D3O

D2O

D1O

D0O

GND1

GND2

GND3

GND4

GND5

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

39

40

41

42

43

TRACE_CLK_MIC

R29

MICTOR_PWR1 R31

MICTOR_PWR2 R33

TRACE_DATA7

TRACE_DATA6

TRACE_DATA5

TRACE_DATA4

TRACE_DATA3

TRACE_DATA2

TRACE_DATA1

R35

10K

R36

10K

R37

10K

R38

10K

TRACE_DATA0

10K

3.3V

0

DNI_R1005

3.3V

Designed

3.3V

C5

C6

0.1uF

1000pF

NOV. 20, 2013

Drawn

ALTIMA Corporation

2-5767004-2

NOV. 20, 2013

Checked

Mictor38P

1-5-5, Shin-Yokohama, Kouhoku-ku, Yokohama, 222-8563 JAPAN

Title

NOV. 20, 2013

Approval

Helio Board

Size Document Number

A3

NOV. 20, 2013

5

ALTHEL10SOC-R1.2

Date: Wednesday, November 20, 2013

Sheet

1

of

Rev

STEP

1.22

26

Cyclone V SoC Transceivers & Clocks

U1F

D

CYCLONE V GX SoC Transceiver

AF2

AF1

AB2

AB1

V2

V1

7 REFCLK_QL1_P

7 REFCLK_QL1_N

GXB_RX_L0p,GXB_REFCLK_L0p

GXB_RX_L0n,GXB_REFCLK_L0n

GXB_RX_L1p,GXB_REFCLK_L1p

GXB_RX_L1n,GXB_REFCLK_L1n

GXB_RX_L2p,GXB_REFCLK_L2p

GXB_RX_L2n,GXB_REFCLK_L2n

V5

V4

REFCLK0Lp

REFCLK0Ln

P2

P1

K2

K1

F2

F1

GXB_RX_L3p,GXB_REFCLK_L3p

GXB_RX_L3n,GXB_REFCLK_L3n

GXB_RX_L4p,GXB_REFCLK_L4p

GXB_RX_L4n,GXB_REFCLK_L4n

GXB_RX_L5p,GXB_REFCLK_L5p

GXB_RX_L5n,GXB_REFCLK_L5n

P8

N8

REFCLK1Lp

REFCLK1Ln

GXB_L0

GXB_L1

GXB_TX_L0p

GXB_TX_L0n

GXB_TX_L1p

GXB_TX_L1n

GXB_TX_L2p

GXB_TX_L2n

AD2

AD1

Y2

Y1

T2

T1

GXB_TX_L3p

GXB_TX_L3n

GXB_TX_L4p

GXB_TX_L4n

GXB_TX_L5p

GXB_TX_L5n

M2

M1

H2

H1

D2

D1

RREF_TL

B1

R39

2K

5CSXFC6C6U23

CAD Note:

Place resistor near

RREF_TL pins.

Route away frm aggressor

U1M

CYCLONE V GX SoC Clocks

Cl ocks

HSMA_CLK_IN0

V11

W11

Bank 3B

CLK0p,FPLL_BL_FBp,DIFFIO_RX_B31p,

CLK0n,FPLL_BL_FBn,DIFFIO_RX_B31n

FPLL_BL_CLKOUT0,FPLL_BL_CLKOUTp,FPLL_BL_FB,DIFFIO_TX_B37p,B_A_2

FPLL_BL_CLKOUT1,FPLL_BL_CLKOUTn,DIFFIO_TX_B37n,B_A_3

7 CLK_100M_FPGA

V12

W12

CLK1p,DIFFIO_RX_B39p

CLK1n,DIFFIO_RX_B39n

7 CLK_50M_FPGA

Y13

AA13

CLK2p,DIFFIO_RX_B47p

CLK2n,DIFFIO_RX_B47n

0_1608

Y15

AA15

CLK3p,DIFFIO_RX_B55p

CLK3n,DIFFIO_RX_B55n

HSMA_CLK_IN_P1

HSMA_CLK_IN_N1

W21

W20

CLK5p,DIFFIO_RX_R21p

CLK5n,DIFFIO_RX_R21n

R440

Y24

W24

R439

AG5

AH4

HSMA_CLK_OUT_P1

HSMA_CLK_OUT_N1

FPLL_BR_CLKOUT0,FPLL_BR_CLKOUTp,FPLL_BR_FB,DIFFIO_TX_R22p

AB26

HSMA_CLK_OUT0

FPLL_BR_CLKOUT1,FPLL_BR_CLKOUTn,DIFFIO_TX_R22n

AA26

Bank 4A

Bank 5B

0_1608

HSMA_CLK_OUT0

HSMA_CLK_OUT0 11

HSMA_CLK_OUT_P[2..1]

CLK4p,FPLL_BR_FBp,DIFFIO_RX_R23p

CLK4n,FPLL_BR_FBn,DIFFIO_RX_R23n

HSMA_CLK_OUT_N[2..1]

HSMA_CLK_IN0

Bank 8A

7 CLK_125M_FPGA_P

7 CLK_125M_FPGA_N

HSMA_CLK_IN_P2

HSMA_CLK_IN_N2

CLK7p,DIFFIO_RX_T1p

CLK7n,DIFFIO_RX_T1n

FPLL_TL_CLKOUT1,FPLL_TL_CLKOUTn,DIFFIO_TX_T4n

D8

HSMA_CLK_OUT_N2

FPLL_TL_CLKOUT0,FPLL_TL_CLKOUTp,FPLL_TL_FB,DIFFIO_TX_T4p

CLK6p,FPLL_TL_FBp,DIFFIO_RX_T9p

CLK6n,FPLL_TL_FBn,DIFFIO_RX_T9n

E8

HSMA_CLK_OUT_P2

E11

D11

HSMA_CLK_OUT_N[2..1] 11

HSMA_CLK_IN0 11

HSMA_CLK_IN_P[2..1]

D12

C12

HSMA_CLK_OUT_P[2..1] 11

HSMA_CLK_IN_N[2..1]

HSMA_CLK_IN_P[2..1] 11

HSMA_CLK_IN_N[2..1] 11

5CSXFC6C6U23

Designed

A

NOV. 20, 2013

Drawn

ALTIMA Corporation

NOV. 20, 2013

Checked

1-5-5, Shin-Yokohama, Kouhoku-ku, Yokohama, 222-8563 JAPAN

Title

NOV. 20, 2013

Approval

Helio Board

Size Document Number

A3

NOV. 20, 2013

5

ALTHEL10SOC-R1.2

Date: Wednesday, November 20, 2013

Sheet

1

of

Rev

STEP

1.22

26

PLL

3.3V

3.3V

2.5V

C7

C8

0.01uF

0.1uF

3.3V

C9

C10

2.5V

3.3V

X1

R41

1K

0.01uF

EN

GND

VCC

OUT

C12

0.1uF

0.1uF

U5

X2

22

CLK_50M_FPGA 6

1K

1

2

DUT25AT5-50MHz

2.5V

50MHz

C11

0.1uF

R43

R44

R40

1K

EN

VCC

GND

OUT

1

2

3

4

DUT35AT-25MHz

CLKIN

1G

Y0

GND

Y1

NC

VDD

Y2

C14

0.01uF

0.1uF

R42

22

R45

22

R46

22

CLK_OSC1 5

CLK_OSC2 5

CDCLVC1103PWR

25MHz

C13

8

7

6

5

CLK_25M_ENET 12

2.5V

X3

R47

1K

1

2

EN

VCC

GND

OUT

R48

22

CLK_100M_FPGA 6

DUT25AT-100MHz

100MHz

2.5V

2.5V

C482

C483

2.5V

C15

C16

0.01uF

10uF_6.3V

X5

2.5V

R443

X4

R49

1K

OE

DNI_R1005

VDD

6

CLK_125M_FPGA_N 6

CLK_125M_FPGA_P 6

NC

OUT-

GND

OUT+

DNI_C1005

EN

VCC

DNI_C0603

GND

OUT

R444

DNI_R1005

USB_B2_CLK 3,17

DNI_FCXO-03L 6.000MHz

CEM25AT5-L-125MHz

125MHz

DNI_FA-238_25MHz_50ppm_CL=18pF

DNI_C1608

Y1

4

C17

U6

2

1

4

5

XTAL_IN

RESERVED

OE

9 REFCLK_FSEL0

FSEL0

9 REFCLK_FSEL1

10

FSEL1

C18

DNI_C1608

2.5V

R50

1K

REFCLK_QL1_P 6

nQ

REFCLK_QL1_N 6

VCC

VEE

XTAL_OUT

2.5V

C19

C20

0.01uF

0.1uF

CEM20AT5-100MHz

100MHz

Designed

A

NOV. 20, 2013

Drawn

ALTIMA Corporation

NOV. 20, 2013

Checked

1-5-5, Shin-Yokohama, Kouhoku-ku, Yokohama, 222-8563 JAPAN

Title

NOV. 20, 2013

Approval

Helio Board

Size Document Number

A3

NOV. 20, 2013

5

ALTHEL10SOC-R1.2

Date: Wednesday, November 20, 2013

Sheet

1

of

Rev

STEP

1.22

26

Cyclone V SoC Configuration

2.5V

R51

10K

U1G

CYCLONE V GX SoC C onfiguration

9 JTAG_FPGA_TMS

9 JTAG_FPGA_TCK

9 JTAG_FPGA_TDI

9 JTAG_FPGA_TDO

AC7

AB5

W10

Y9

TMS

TCK

TDI

TDO

U10

CLKUSR,DIFFIO_RX_B5p,DQ1B

U7

AA8

DCLK

AD7

AC6

AC5

AB6

AA6

Y4

Y8

Y5

W8

AB4

T8

AA4

U9

AD4

V10

AC4

AS_DATA0,ASDO,DATA0

AS_DATA1,DATA1

AS_DATA2,DATA2

AS_DATA3,DATA3

nCSO,DATA4

DATA5,DIFFIO_TX_B2n

DATA6,DIFFIO_RX_B1n,DQ1B

DATA7,DIFFIO_TX_B2p,DQ1B

DATA8,DIFFIO_RX_B1p,DQ1B

DATA9,DIFFIO_TX_B4n,DQ1B

DATA10,DIFFIO_RX_B3n,DQSn1B

DATA11,DIFFIO_TX_B4p

DATA12,DIFFIO_RX_B3p,DQS1B

DATA13,DIFFIO_TX_B6n,DQ1B

DATA14,DIFFIO_RX_B5n,DQ1B

DATA15,DIFFIO_TX_B6p,DQ1B

3.3V

2

C21

0.1uF

VCC

10

GND

3

4

5

6

DCLK

DATA0

DATA1

DATA2

DATA3

nCS

16

15

8

9

1

7

NC

NC

NC

NC

14

13

12

11

NC

NC

NC

NC

USER_PB_FPGA0

USER_PB_FPGA1

USER_PB_FPGA2

USER_DIPSW_FPGA0

USER_DIPSW_FPGA1

USER_DIPSW_FPGA2

USER_DIPSW_FPGA3

USER_LED_FPGA0

USER_LED_FPGA1

USER_LED_FPGA2

USER_LED_FPGA3

EPCQ256SI16N

Bank 3A

Bank 5A

TestPAD

3.3V

R52

R54

R56

TP1

TP2

AB23

AC24

DEV_CLRn,DIFFIO_TX_R5n,DQ1R

DEV_OE,DIFFIO_TX_R5p

TP3

AA20

INIT_DONE,DIFFIO_RX_R2p

10K

10K

10K

Reconfig Switch

SW3

F7

H8

J8

nCONFIG

nSTATUS

CONF_DONE

E6

nCE

PR_READY,DIFFIO_TX_B8n,DQ1B

PR_DONE,DIFFIO_RX_B7n

PR_ERROR,DIFFIO_RX_B7p

AE6

AA11

Y11

PR_REQUEST,DIFFIO_TX_R1n,DQ1R

CvP_CONFDONE,DIFFIO_TX_R3n,DQ1R

CRC_ERROR,DIFFIO_RX_R2n

AE26

AD26

Y19

nPERSTL1,DIFFIO_RX_R6n,DQSn1R

nCEO,DIFFIO_TX_R3p,DQ1R

MSEL4

MSEL3

MSEL2

MSEL1

MSEL0

Bank 9A

5CSXFC6C6U23

HSMA_SDA 11

HSMA_SCL 11

C

W15

AE25

K9

K10

G6

H9

J10

3.3V

R53

R55

R57

R58

R59

0

0

0

0

0

MSEL[4..0] : 10010

Configuratiom mode : Active Serial x4

POR Delay : Fast

SKQMBAE010

3.3V

R60

220

Green_LED

LED1

TR1

R441

100_1%

RUE002N02

USER_LED_FPGA[3..0]

15 USER_LED_FPGA[3..0]

USER_PB_FPGA[2..0]

15 USER_PB_FPGA[2..0]

USER_DIPSW_FPGA[3..0]

15 USER_DIPSW_FPGA[3..0]

Designed

A

NOV. 20, 2013

Drawn

ALTIMA Corporation

NOV. 20, 2013

Checked

1-5-5, Shin-Yokohama, Kouhoku-ku, Yokohama, 222-8563 JAPAN

Title

NOV. 20, 2013

Approval

Helio Board

Size Document Number

A3

NOV. 20, 2013

5

ALTHEL10SOC-R1.2

Date: Wednesday, November 20, 2013

Sheet

1

of

Rev

STEP

1.22

26

3.3V

R61

1K

J2

2

4

6

8

10

17 USB_DISABLEn

1

3

5

7

9

JTAG_TCK 17

JTAG_BLASTER_TDI 17

JTAG_TMS 17

JTAG_BLASTER_TDI

JTAG_BLASTER_TDO

3.3V

R62

Logic 0 = pin 10 <--> pin 9 (HPS Bypass)

Logic 1 = pin 10 <--> pin 2 (HPS Enable)

1K

R65

JTAG_BLASTER_TDO R67

JTAG_MUX_HPS_TDI R63

1K

DNI_R1005

IN1

NO1

JTAG_MUX_TMS

4

5

On = not-in-chain

Off = in-chain

SW4

1

2

3

4

HPS_JTAG_EN

FPGA_JTAG_EN

HSMA_JTAG_EN

HSMA_JTAG_OE

8

7

6

5

R70

R71

R72

R80

JTAG Select

1

2

3

4

3.3V

1K

2.5V

1K

DNI_R1005

DNI_R1005

JTAG_SEL

R73

JTAG_HPS_SEL R74

R21

R22

8

7

6

5

KHS42C

JTAG_MUX_HPS_TMS

JTAG_MUX_TMS

JTAG_MUX_TCK

I0A

I1A

JTAG_MUX_TMS

JTAG_MICTOR_TMS

I0B

JTAG_HPS_TMS

I1B

JTAG_MUX_HPS_TDI

11

I0C

JTAG_MICTOR_TDO

10

DNI_R1005

0

JTAG_MICTOR_TMS

VCC

JTAG_MICTOR_TCK

R447

R448

HV_JTAG_FPGA_TDI

JTAG_MICTOR_TDI

14

13

YA

YB

C27

0.1uF

R356

R357

JTAG_HPS_TCK

DNI_R1005

DNI_R1005

YC

FPGA_JTAG_EN

HV_JTAG_FPGA_TDO

I1C

DNI_R1005

DNI_R1005

DNI_R1005

DNI_R1005

YD

I1D

GND

JTAG_HPS_TDO

12

1

15

IN2

COM2

R445

DNI_R1005

DNI_R1005

R353

IN1

COM1

NO1

GND

NO2

IN2

Logic 0 = pin 10 <--> pin 9 (HSMA Bypass)

Logic 1 = pin 10 <--> pin 2 (HSMA Enable)

JTAG_HPS_TDI

HSMA_JTAG_EN

HV_JTAG_HSMA_TDO

JTAG_HPS_TDO

NC1

V+

NC2

COM2

R69

JTAG_HPS_TDO 5

JTAG_MUX_TCK

HV_JTAG_FPGA_TMS

HV_JTAG_FPGA_TDI

HV_JTAG_FPGA_TDO

VCCB

10

9

8

7

B1

B2

B3

B4

VCCA

A1

A2

A3

A4

2

3

4

5

JTAG_MUX_TMS

C23

IN1

COM1

NO1

GND

12

OE

DNI_R1005

DNI_R1005

DNI_R1005

DNI_R1005

R76

10

NC1

V+

NC2

COM2

3.3V

1K

HV_JTAG_FPGA_TMS

R359

R361

R362

R364

GND

NO2

IN2

1

2

5 JTAG_MICTOR_TRST

0 JTAG_MUX_TDI

HV_JTAG_HSMA_TDI

C24

HV_JTAG_HSMA_TMS

R370

R371

COM1

NO1

DNI_R1005

DNI_R1005

DNI_R1005

DNI_R1005

R78

10

NC1

V+

NC2

COM2

3.3V

1K

R77

R368

R369

IN1

0.1uF

JTAG_HPS_TRST 5

JTAG_TRST

3.3V

JTAG_FPGA_TCK 8

JTAG_FPGA_TMS 8

JTAG_FPGA_TDI 8

JTAG_FPGA_TDO 8

GND

NO2

IN2

C25

0.1uF

B

2.5V

R79

DNI_TXB0104RUTR

0.1uF

R75

U12

DNI_C1005

JTAG_MUX_TCK

HV_JTAG_FPGA_TMS

HV_JTAG_FPGA_TDI

HV_JTAG_FPGA_TDO

HV_JTAG_HSMA_TDI

HV_JTAG_FPGA_TDI

3.3V

Logic 0 = pin 6 <--> pin 7 (HSMA Bypass)

Logic 1 = pin 6 <--> pin 4 (HSMA Enable)

JTAG_HPS_SEL

11

JTAG_MUX_HPS_TMS

DNI_R1005

DNI_R1005

10

U10

Logic 0 : pin 10 <--> pin 9 (TRST from JTAG)

Logic 1 : pin 10 <--> pin 2 (TRST from MICTOR)

C29

0 JTAG_HPS_TMS

DNI_R1005

R354

R355

TS5A23157DGSR

U13

3.3V

1K

R68

TS5A23157DGSR

2.5V

DNI_C1005

0.1uF

D

NC2

NO2

C22

QS3VH257PAG

3.3V

Logic 0 : Yx <-> I0x

Logic 1 : Yx <-> I1x

C28

GND

JTAG_HPS_TMS

JTAG_HPS_SEL

0 HV_JTAG_FPGA_TDI

3.3V

JTAG_MUX_TMS

JTAG_HPS_TDI 5

HV_JTAG_FPGA_TDI R366

JTAG_MICTOR_TDI

R367

I0D

V+

R64

JTAG_HPS_TCK

JTAG_HPS_TMS 5

JTAG_HPS_TDI

U9

JTAG_HPS_TCK 5

R358

R360

JTAG_MUX_HPS_TDI R363

JTAG_MICTOR_TDO R365

3.3V

C26

2.2uF

Logic 0 = pin 10 <--> pin 9 (FPGA Bypass)

Logic 1 = pin 10 <--> pin 2 (FPGA Enable)

U11

16

NC1

DNI_R1005

Logic 0 = pin 6 <--> pin 7 (FPGA Bypass)

Logic 1 = pin 6 <--> pin 4 (FPGA Enable)

JTAG_MUX_TCK

JTAG_MICTOR_TCK

TS5A23157DGSR

REFCLK_FSEL1 7

REFCLK_FSEL0 7

KHS42C

3.3V

JTAG_MUX_TDO

10

R446

SW1

3.3V 2.5V

1K

1K

DNI_R1005

DNI_R1005

COM1

DNI_R1005

DNI_R1005

3.3V

Logic 0 = pin 6 <--> pin 7 (HPS Bypass)

Logic 1 = pin 6 <--> pin 4 (HPS Enable)

MICTOR_RSTn 5,13

JTAG Chain Control

R351

R352

JTAG_BLASTER_TDI

JTAG_TRST

U8

HPS_JTAG_EN

JTAG_BLASTER_TDO 17

XG4C-1031

R66

0

JTAG

3.3V

DNI_R1005

TS5A23157DGSR

3.3V

3.3V

16

JTAG_TCK

17 JTAG_TCK

5 JTAG_MICTOR_TCK

17 JTAG_TMS

5 JTAG_MICTOR_TDI

YA

I1A

JTAG_TMS

I0B

I1B

JTAG_BLASTER_TDI

11

I0C

JTAG_MICTOR_TDI

10

I1C

14

I0D

13

C33

0.1uF

YC

JTAG_MUX_TCK

JTAG_MUX_TMS

R376

R377

DNI_R1005

DNI_R1005

JTAG_MUX_TDI

JTAG_BLASTER_TDO R378

JTAG_MICTOR_TDO R379

DNI_R1005

DNI_R1005

JTAG_MUX_TDO

11

JTAG_MUX_TCK

10

HV_JTAG_HSMA_TMS 9

HV_JTAG_HSMA_TDI

8

HV_JTAG_HSMA_TDO 7

JTAG_MUX_TMS

JTAG_MUX_TDI

JTAG_SEL

15

C31

VCCA

B1

B2

B3

B4

A1

A2

A3

A4

2

3

4

5

GND

OE

12

VCCB

XJ1

DNI_XJ8A-0211

DNI_XG8S-0331

DNI_C1005

JTAG_HSMA_TCK 11

JTAG_HSMA_TMS 11

JTAG_HSMA_TDI 11

JTAG_HSMA_TDO 11

HSMA_JTAG_OE

DNI_TXB0104RUTR

3.3V

Designed

3.3V

R342

10K

NOV. 20, 2013

Drawn

R343

10K

ALTIMA Corporation

JTAG_TRST

NOV. 20, 2013

Checked

QS3VH257PAG

Logic 0 : Yx <-> I0x

Logic 1 : Yx <-> I1x

17 JTAG_BLASTER_TRST

R344

TR3

RUE002N02

1-5-5, Shin-Yokohama, Kouhoku-ku, Yokohama, 222-8563 JAPAN

Title

TR4

DTC114EUA

NOV. 20, 2013

Approval

Helio Board

Size Document Number

A3

NOV. 20, 2013

5

J3

1

2

3

C30

3.3V

DNI_C1005

DNI_R1005

DNI_R1005

12

I1D

DNI_R1005

DNI_R1005

U15

R374

R375

JTAG_MUX_TDO

YD

GND

R372

R373

JTAG_MUX_TCK

JTAG_BLASTER_TDI

JTAG_MICTOR_TDI

3.3V

C32

2.2uF

JTAG_TMS

JTAG_MICTOR_TMS

YB

JTAG_MICTOR_TDO

5 JTAG_MICTOR_TDO

I0A

JTAG_BLASTER_TDO

JTAG_TCK

JTAG_MICTOR_TCK

VCC

JTAG_MICTOR_TCK

JTAG_MICTOR_TMS

5 JTAG_MICTOR_TMS

2.5V

U14

ALTHEL10SOC-R1.2

Date: Wednesday, November 20, 2013

Sheet

1

of

Rev

STEP

1.22

26

DDR3_HPS_CK_P R81

DDR3

DDR3_HPS_CK_N

100_1%

VTT_HPS_DDR3

VTT_HPS_DDR3

DDR3_HPS_BA[2..0]

4 DDR3_HPS_BA[2..0]

DDR3_HPS_DM[3..0]

4 DDR3_HPS_DM[3..0]

VTT_HPS_DDR3

VTT_HPS_DDR3

C34

47nF

C35

47nF

C36

47nF

C37

47nF

C38

47nF

C39

47nF

C40

47nF

C41

47nF

C42

47nF

C43

47nF

C44

47nF

C45

47nF

DDR3_HPS_A0

DDR3_HPS_A1

DDR3_HPS_A2

DDR3_HPS_A3

DDR3_HPS_A4

DDR3_HPS_A5

DDR3_HPS_A6

DDR3_HPS_A7

R82

R85

R88

R91

R93

R96

R98

R100

DDR3_HPS_A8

DDR3_HPS_A9

DDR3_HPS_A10

DDR3_HPS_A11

DDR3_HPS_A12

DDR3_HPS_A13

DDR3_HPS_A14

62

62

62

62

62

62

62

62

R83

R86

R89

R92

R94

R423

R424

R102

DDR3_HPS_CKE R103

DDR3_HPS_DQS_N[3..0]

4 DDR3_HPS_DQS_N[3..0]

62

62

62

62

62

62

62

DDR3_HPS_BA0 R84

DDR3_HPS_BA1 R87

DDR3_HPS_BA2 R90

62

62

62

DDR3_HPS_CSn R95

DDR3_HPS_WEn R97

DDR3_HPS_RASn R99

DDR3_HPS_CASn R101

62

62

62

62

DDR3_HPS_ODT R430

62

DDR3_HPS_CKE R428

62

1.5V

DDR3_HPS_DQS_P[3..0]

4 DDR3_HPS_DQS_P[3..0]

VTT_HPS_DDR3

VTT_HPS_DDR3

4.7K_1%

DDR3_HPS_RESETn

2K

DDR3_HPS_DQ[31..0]

4 DDR3_HPS_DQ[31..0]

DDR3_HPS_A[14..0]

4 DDR3_HPS_A[14..0]

U16

4 DDR3_HPS_CKE

4 DDR3_HPS_CK_P

4 DDR3_HPS_CK_N

4 DDR3_HPS_CSn

4 DDR3_HPS_WEn

4 DDR3_HPS_RASn

4 DDR3_HPS_CASn

4 DDR3_HPS_RESETn

4 DDR3_HPS_ODT

N3

P7

P3

N2

P8

P2

R8

R2

T8

R3

L7

R7

N7

T3

T7

DDR3_HPS_CKE

DDR3_HPS_CK_P

DDR3_HPS_CK_N

K9

J7

K7

DDR3_HPS_DM2

DDR3_HPS_DM3

E7

D3

DDR3 Device

A0

DQ0

A1

DQ1

A2

DQ2

A3

DQ3

A4

DQ4

A5

DQ5

A6

DQ6

A7

DQ7

A8

DQ8

A9

A10/AP

DQ9

DQ10

A11

A12/BC#

DQ11

NC

DQ12

NC

DQ13

DQ14

CKE

DQ15

CK

LDQS

CK#

LDQS#

LDM

UDQS

UDM

UDQS#

DDR3_HPS_CSn

DDR3_HPS_WEn

DDR3_HPS_RASn

DDR3_HPS_CASn

L2

L3

J3

K3

CS#

WE#

RAS#

CAS#

DDR3_HPS_BA0

DDR3_HPS_BA1

DDR3_HPS_BA2

DDR3_HPS_RESETn

DDR3_HPS_ODT

M2

N8

M3

T2

K1

L8

BA0

BA1

BA2

RESET#

ODT

ZQ

H1

M8

VREFDQ

VREFCA

B2

D9

G7

K2

K8

N1

N9

R1

R9

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

A1

A8

C1

C9

D2

E9

F1

H2

H9

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VREF_HPS_DDR3

R104

240

U17

DDR3_HPS_A0

DDR3_HPS_A1

DDR3_HPS_A2

DDR3_HPS_A3

DDR3_HPS_A4

DDR3_HPS_A5

DDR3_HPS_A6

DDR3_HPS_A7

DDR3_HPS_A8

DDR3_HPS_A9

DDR3_HPS_A10

DDR3_HPS_A11

DDR3_HPS_A12

DDR3_HPS_A13

DDR3_HPS_A14

C46

C484

0.1uF 0.01uF

1.5V

E3

F7

F2

F8

H3

H8

G2

H7

D7

C3

C8

C2

A7

A2

B8

A3

DDR3_HPS_DQ17

DDR3_HPS_DQ23

DDR3_HPS_DQ21

DDR3_HPS_DQ19

DDR3_HPS_DQ20

DDR3_HPS_DQ22

DDR3_HPS_DQ16

DDR3_HPS_DQ18

DDR3_HPS_DQ29

DDR3_HPS_DQ30

DDR3_HPS_DQ28

DDR3_HPS_DQ27

DDR3_HPS_DQ24

DDR3_HPS_DQ31

DDR3_HPS_DQ25

DDR3_HPS_DQ26

F3

G3

C7

B7

DDR3_HPS_DQS_P2

DDR3_HPS_DQS_N2

DDR3_HPS_DQS_P3

DDR3_HPS_DQS_N3

NC

NC

NC

NC

NC

J1

J9

L1

L9

M7

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

B1

B9

D1

D8

E2

E8

F9

G1

G9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

J2

J8

A9

M1

M9

B3

P1

P9

E1

T1

T9

G8

DDR3_HPS_A0

DDR3_HPS_A1

DDR3_HPS_A2

DDR3_HPS_A3

DDR3_HPS_A4

DDR3_HPS_A5

DDR3_HPS_A6

DDR3_HPS_A7

DDR3_HPS_A8

DDR3_HPS_A9

DDR3_HPS_A10

DDR3_HPS_A11

DDR3_HPS_A12

DDR3_HPS_A13

DDR3_HPS_A14

N3

P7

P3

N2

P8

P2

R8

R2

T8

R3

L7

R7

N7

T3

T7

DDR3_HPS_CKE

DDR3_HPS_CK_P

DDR3_HPS_CK_N

K9

J7

K7

DDR3_HPS_DM0

DDR3_HPS_DM1

E7

D3

DDR3 Device

A0

DQ0

A1

DQ1

A2

DQ2

A3

DQ3

A4

DQ4

A5

DQ5

A6

DQ6

A7

DQ7

A8

DQ8

A9

A10/AP

DQ9

DQ10

A11

A12/BC#

DQ11

NC

DQ12

NC

DQ13

DQ14

CKE

DQ15

CK

LDQS

CK#

LDQS#

LDM

UDQS

UDM

UDQS#

DDR3_HPS_CSn

DDR3_HPS_WEn

DDR3_HPS_RASn

DDR3_HPS_CASn

L2

L3

J3

K3

CS#

WE#

RAS#

CAS#

DDR3_HPS_BA0

DDR3_HPS_BA1

DDR3_HPS_BA2

DDR3_HPS_RESETn

DDR3_HPS_ODT

M2

N8

M3

T2

K1

L8

BA0

BA1

BA2

RESET#

ODT

ZQ

H1

M8

VREFDQ

VREFCA

B2

D9

G7

K2

K8

N1

N9

R1

R9

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

A1

A8

C1

C9

D2

E9

F1

H2

H9

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VREF_HPS_DDR3

R105

240

C47

C485

0.1uF 0.01uF

1.5V

MT41J64M16JT-125

E3

F7

F2

F8

H3

H8

G2

H7

D7

C3

C8

C2

A7

A2

B8

A3

DDR3_HPS_DQ0

DDR3_HPS_DQ6

DDR3_HPS_DQ4

DDR3_HPS_DQ7

DDR3_HPS_DQ1

DDR3_HPS_DQ3

DDR3_HPS_DQ5

DDR3_HPS_DQ2

DDR3_HPS_DQ8

DDR3_HPS_DQ14

DDR3_HPS_DQ9

DDR3_HPS_DQ12

DDR3_HPS_DQ11

DDR3_HPS_DQ15

DDR3_HPS_DQ10

DDR3_HPS_DQ13

F3

G3

C7

B7

DDR3_HPS_DQS_P0

DDR3_HPS_DQS_N0

DDR3_HPS_DQS_P1

DDR3_HPS_DQS_N1

NC

NC

NC

NC

NC

J1

J9

L1

L9

M7

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

B1

B9

D1

D8

E2

E8

F9

G1

G9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

J2

J8

A9

M1

M9

B3

P1

P9

E1

T1

T9

G8

MT41J64M16JT-125

1.5V

C48

C49

C50

C51

C52

C53

C54

C55

C56

C57

2.2nF

2.2nF

2.2nF

2.2nF

2.2nF

2.2nF

4.7nF

4.7nF

4.7nF

4.7nF

1Gbit : MT41J64M16JT-125

2Gbit : MT41J128M16JT-125

4Gbit : MT41J256M16RE-125

Designed

1.5V

A

C481

0.01uF

C59

0.01uF

C60

0.01uF

C61

0.01uF

C486

0.01uF

C487

0.01uF

C62

0.1uF

C63

0.1uF

C64

0.1uF

C65

0.1uF

C66

0.47uF

C67

0.47uF

C68

0.47uF

C69

NOV. 20, 2013

Drawn

0.47uF

ALTIMA Corporation

NOV. 20, 2013

Checked

1-5-5, Shin-Yokohama, Kouhoku-ku, Yokohama, 222-8563 JAPAN

Title

NOV. 20, 2013

Approval

Helio Board

Size Document Number

A3

NOV. 20, 2013

5

ALTHEL10SOC-R1.2

Date: Wednesday, November 20, 2013

Sheet

1

10

of

Rev

STEP

1.22

26

HSMC

J4

8 HSMA_SDA

9 JTAG_HSMA_TCK

9 JTAG_HSMA_TDO

6 HSMA_CLK_OUT0

HSMA_D0

HSMA_D2

HSMA_TX_D_P0

HSMA_TX_D_N0

HSMA_TX_D_P1

HSMA_TX_D_N1

C

HSMA_TX_D_P2

HSMA_TX_D_N2

HSMA_TX_D_P3

HSMA_TX_D_N3

HSMA_TX_D_P4

HSMA_TX_D_N4

HSMA_TX_D_P5

HSMA_TX_D_N5

HSMA_TX_D_P6

HSMA_TX_D_N6

HSMA_TX_D_P7

HSMA_TX_D_N7

HSMA_CLK_OUT_P1

HSMA_CLK_OUT_N1

HSMA_TX_D_P8

HSMA_TX_D_N8

HSMA_TX_D_P9

HSMA_TX_D_N9

B

HSMA_TX_D_P10

HSMA_TX_D_N10

HSMA_TX_D_P11

HSMA_TX_D_N11

HSMA_TX_D_P12

HSMA_TX_D_N12

HSMA_TX_D_P13

HSMA_TX_D_N13

3.3V

L1

3.3V_HSMA

HSMA_TX_D_P14

HSMA_TX_D_N14

DNI_L1608

3.3V_EXT

HSMA_TX_D_P15

HSMA_TX_D_N15

L2

3A_30 Ohm FB

HSMA_TX_D_P16

HSMA_TX_D_N16

HSMA_CLK_OUT_P2

HSMA_CLK_OUT_N2

12V

3.3V_HSMA

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

73

75

77

79

81

83

85

87

89

91

93

95

97

99

41

43

3.3V

47

49

3.3V

53

55

3.3V

59

61

3.3V

65

67

3.3V

71

73

3.3V

77

79

3.3V

83

85

3.3V

89

91

3.3V

95

97

3.3V

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

139

141

143

145

147

149

151

153

155

157

159

101

103

3.3V

107

109

3.3V

113

115

3.3V

119

121

3.3V

125

127

3.3V

131

133

3.3V

137

139

3.3V

143

145

3.3V

149

151

3.3V

155

157

3.3V

BANK1

3.3V_HSMA

HSMA_D[3..0]

HSMA_D[3..0] 3

HSMA_TX_D_P[16..0]

HSMA_TX_D_N[16..0]

HSMA_RX_D_P[16..0]

HSMA_RX_D_N[16..0]

HSMA_SCL 8

JTAG_HSMA_TMS 9

JTAG_HSMA_TDI 9

HSMA_CLK_IN0 6

42

44

12V

48

50

12V

54

56

12V

60

62

12V

66

68

12V

72

74

12V

78

80

12V

84

86

12V

90

92

12V

96

98

12V

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

HSMA_D1

HSMA_D3

102

104

12V

108

110

12V

114

116

12V

120

122

12V

126

128

12V

132

134

12V

138

140

12V

144

146

12V

150

152

12V

156

158

PSNTn

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

HSMA_RX_D_P8

HSMA_RX_D_N8

BANK2

BANK3

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

GND1_1

GND1_2

GND1_3

GND1_4

GND2_1

GND2_2

GND2_3

GND2_4

GND3_1

GND3_2

GND3_3

GND3_4

HSMA_CLK_OUT_P[2..1]

HSMA_CLK_OUT_N[2..1]

HSMA_CLK_IN_P[2..1]

HSMA_CLK_IN_N[2..1]

HSMA_RX_D_P0

HSMA_RX_D_N0

HSMA_TX_D_P[16..0] 3

HSMA_TX_D_N[16..0] 3

HSMA_RX_D_P[16..0] 3

HSMA_RX_D_N[16..0] 3

HSMA_CLK_OUT_P[2..1] 6

HSMA_CLK_OUT_N[2..1] 6

HSMA_CLK_IN_P[2..1] 6

HSMA_CLK_IN_N[2..1] 6

HSMA_RX_D_P1

HSMA_RX_D_N1

C

HSMA_RX_D_P2

HSMA_RX_D_N2

HSMA_RX_D_P3

HSMA_RX_D_N3

HSMA_RX_D_P4

HSMA_RX_D_N4

HSMA_RX_D_P5

HSMA_RX_D_N5

HSMA_RX_D_P6

HSMA_RX_D_N6

HSMA_RX_D_P7

HSMA_RX_D_N7

HSMA_CLK_IN_P1

HSMA_CLK_IN_N1

HSMA_RX_D_P9

HSMA_RX_D_N9

B

HSMA_RX_D_P10

HSMA_RX_D_N10

HSMA_RX_D_P11

HSMA_RX_D_N11

HSMA_RX_D_P12

HSMA_RX_D_N12

HSMA_RX_D_P13

HSMA_RX_D_N13

HSMA_RX_D_P14

HSMA_RX_D_N14

HSMA_RX_D_P15

HSMA_RX_D_N15

HSMA_RX_D_P16

HSMA_RX_D_N16

HSMA_CLK_IN_P2

HSMA_CLK_IN_N2

HSMA_PRSNTn 3

12V

C71

22uF_25V

22uF_6.3V

161

162

163

164

165

166

167

168

169

170

171

172

ASP-122953-01

C70

Designed

A

NOV. 20, 2013

Drawn

ALTIMA Corporation

NOV. 20, 2013

Checked

1-5-5, Shin-Yokohama, Kouhoku-ku, Yokohama, 222-8563 JAPAN

Title

NOV. 20, 2013

Approval

Helio Board

Size Document Number

A3

NOV. 20, 2013

5

ALTHEL10SOC-R1.2

Date: Wednesday, November 20, 2013

Sheet

1

11

of

Rev

STEP

1.22

26

10/100/1000 Ethernet - HPS

ETHERNET INTERFACE

ENET_HPS_TXD[3..0]

LED14

DNI_Yellow_LED

ENET_HPS_MDC

ENET_HPS_MDIO

36

37

MDC

MDIO

ENET_HPS_RESETn

42

RESET_N

3.3V

ENET_HPS_LED2_LINK

R106

220

11

ENET_HPS_INTn

J5

YA

YK

12

VCC

Yellow

17

GP1

GA

13

Green

14

GK

GP2

1

2

TD1_P

TD1_N

3

6

TD2_P

TD2_N

4

5

TD3_P

TD3_N

7

8

MDI_HPS_P0

MDI_HPS_N0

MDI_HPS_P1

MDI_HPS_N1

MDI_HPS_P2

MDI_HPS_N2

MDI_HPS_P3

MDI_HPS_N3

10

15

16

R108

10

2

3

5

6

7

8

10

11

4.99K

R109

C73

48

TXRXP_A

TXRXM_A

TXRXP_B

TXRXM_B

TXRXP_C

TXRXM_C

TXRXP_D

TXRXM_D

R110

17

15

LED1_PHYAD0

LED2_PHYAD1

46

45

XI

XO

ENET_HPS_RXD[3..0]

ENET_HPS_RX_CLK

ENET_HPS_RX_DV

ENET_HPS_MDIO

ENET_HPS_INTn

ENET_HPS_GTX_CLK

TX_EN

25

ENET_HPS_TX_EN

RX_DV_CLK125_EN

33

ENET_HPS_RX_DV

TXD3

TXD2

TXD1

TXD0

22

21

20

19

ENET_HPS_TXD3

ENET_HPS_TXD2

ENET_HPS_TXD1

ENET_HPS_TXD0

RXD0_MODE0

RXD1_MODE1

RXD2_MODE2

RXD3_MODE3

32

31

28

27

ENET_HPS_RXD0

ENET_HPS_RXD1

ENET_HPS_RXD2

ENET_HPS_RXD3

7 CLK_25M_ENET

LED15

DNI_Green_LED

R348

SHELL_GND1

0.01uF

0.01uF

C79

0.01uF

A0

A1

A2

GND

VCC

WP

SCL

SDA

C72

8

7

6

5

0.1uF

I2C_SCL_HPS 5,15,18

I2C_SDA_HPS 5,15,18

I2C Address = 0x51

C74

DNI_R1005

DNI_R1005

DNI_R1005

DNI_R1005

DNI_R1005

DNI_R1005

DNI_R1005

DNI_R1005

C75

10uF_6.3V 10uF_6.3V

Place near KSZ9021RN PHY

3.3V

L3

3.3V_AVDDH

MDI_HPS_P0

MDI_HPS_N0

MDI_HPS_P1

MDI_HPS_N1

MDI_HPS_P2

MDI_HPS_N2

MDI_HPS_P3

MDI_HPS_N3

3.3V_AVDDH

3A_30 Ohm FB

C80

U18B

4.7uF_16V

3.3V_DVDDH

C78

4.7K_1% 1

2

3

4

3.3V

1.2V_AVDDL_PLL

C77

3.3V

24LC32Ax-I/SN

1M

C430

R111

R112

R113

R114

R115

R116

R117

R118

ENET_HPS_RX_CLK 5

ENET_HPS_RX_DV 5

ENET_HPS_MDIO 5

ENET_HPS_INTn 5

U19

CLK125_NDO_LED_MODE

KSZ9021RN

0.01uF

ENET_HPS_RXD[3..0] 5

220

C76

3.3V

R107

41

ENET_HPS_GTX_CLK 5

ENET_HPS_TX_EN 5

ENET_HPS_MDC 5

ENET_HPS_RESETn 13

ENET_HPS_RX_CLK

24

CLK125_NDO_LED_MODE

ENET_HPS_LED1_LINK

ENET_HPS_LED2_LINK

35

GTX_CLK

ISET

0.01uF

7499111121A SHELL_GND1

3.3V

ENET_HPS_LED1_LINK

INT_N

DNI_R1005

9 R442

TD0_P

TD0_N

GND

GND_TAB

GND_TAB

38

RX_CLK_PHYAD2

MDI INTERFACE

18

3.3V

ENET_HPS_TXD[3..0] 5

ENET_HPS_GTX_CLK

ENET_HPS_TX_EN

ENET_HPS_MDC

ENET_HPS_RESETn

U18A

47

12

1

AVDDH

AVDDH

AVDDH

40

16

34

DVDDH

DVDDH

DVDDH

49

13

29

P_GND

VSS_PS

VSS

AVDDL_PLL

LDO_O

9

4

DVDDL

DVDDL

DVDDL

DVDDL

DVDDL

DVDDL

18

14

39

30

26

23

C82

0.1uF

C83

22uF_25V

44

43

AVDDL

AVDDL

C81

2.2uF

1.2V_AVDDL_PLL

C84

2.2uF

C85

0.1uF

22uF_25V

1.2V_AVDDL

L4

3.3V_DVDDH

L5

1.2V_AVDDL

1.2V_DVDDL

C86

3A_30 Ohm FB

C87

2.2uF

C88

0.1uF

C89

3A_30 Ohm FB

22uF_25V

C90

2.2uF

C91

0.1uF

22uF_25V

L6

1.2V_DVDDL

KSZ9021RN

3A_30 Ohm FB

C92

C93

2.2uF

C94

0.1uF

22uF_25V

3.3V

3.3V

R119

R120

R121

R122

4.7K_1%

4.7K_1%

4.7K_1%

4.7K_1%

R123

R125

R127

R129

R131

R133

R135

R137

R139

ENET_HPS_MDIO

ENET_HPS_MDC

ENET_HPS_INTn

ENET_HPS_RESETn

DanP:no dedicated reset Consider to connect expander and pull down

DNI_R1005 ENET_HPS_LED2_LINK R124

DNI_R1005 ENET_HPS_LED1_LINK R126

4.7K_1% ENET_HPS_RXD3

R128

4.7K_1% ENET_HPS_RXD2

R130

ENET_HPS_RXD1

4.7K_1%

R132

4.7K_1% ENET_HPS_RXD0

R134

DNI_R1005 ENET_HPS_RX_DV

R136

4.7K_1% ENET_HPS_RX_CLK

R138

CLK125_NDO_LED_MODE

4.7K_1%

R140

1K

1K

DNI_R1005

DNI_R1005

DNI_R1005

DNI_R1005

4.7K_1%

DNI_R1005

DNI_R1005

BOOT-STRAPS

5.0V

C95

1.2V_AVDDL_PLL

U20

2.2uF

2.5V

C98

2.2uF

BST

OUT

OUT

9

10

1

2

IN

IN

ADJ

PG

8

7

R141

SW

SHDN

GND

EP_GND

4

3

11

R142

10K

20K

C96

22uF_6.3V

C97

2.2uF

Designed

A

LTC3026EDD#PBF

NOV. 20, 2013

Drawn

ALTIMA Corporation

NOV. 20, 2013

Checked

1-5-5, Shin-Yokohama, Kouhoku-ku, Yokohama, 222-8563 JAPAN

Title

NOV. 20, 2013

Approval

Helio Board

Size Document Number

A3

NOV. 20, 2013

5

ALTHEL10SOC-R1.2

Date: Wednesday, November 20, 2013

Sheet

1

12

of

Rev

STEP

1.22

26

QSPI Flash & Reset Circuit

D

Not Mount

3.3V

U21

QSPI_IO0

QSPI_IO1

QSPI_IO2

QSPI_IO3

15

8

9

1

DQ0

DQ1

DQ2/VPP/W#

DQ3/HOLD#

5 QSPI_CLK

16

5 QSPI_SS0

S#

5

5

5

5

3.3V

VCC

DNU

DNU

DNU

DNU

DNU

DNU

DNU

DNU

3

4

5

6

11

12

13

14

VSS

10

3.3V

LED2

3.3V

3.3V

C99

R143

220

0.1uF

Red_LED

R144

20K

U22

4

VCC

MR

GND

RESET

R145

10K

SW5

MAX6315US29D3+T

SKQMBAE010

COLD_RESETn

R146

100_1%

R147

DNI_N25Q512A13GSF40G

ENET_HPS_RESETn 12

HPS_RESETn 5

TG1

3.3V

3.3V

3.3V

PLACE NEAR QSPI FLASH

C101

C102

4.7uF_16V

0.1uF

C100

R148

20K

0.1uF

3.3V

U23

4

VCC

GND

RESET

R149

10K

SW6

3

SKQMBAE010

MR

MAX6315US29D3+T

WARM_RESETn

R150

100_1%

MICTOR_RSTn 5,9

Designed

A

NOV. 20, 2013

Drawn

ALTIMA Corporation

NOV. 20, 2013

Checked

1-5-5, Shin-Yokohama, Kouhoku-ku, Yokohama, 222-8563 JAPAN

Title

NOV. 20, 2013

Approval

Helio Board

Size Document Number

A3

NOV. 20, 2013

5

ALTHEL10SOC-R1.2

Date: Wednesday, November 20, 2013

Sheet

1

13

of

Rev

STEP

1.22

26

USB 2.0 OTG, Micro SD Card

5.0V

USB_5.0V

C103 C104 C105

U24

1

3

9

2.2uF 2.2uF 2.2uF

USB 2.0 OTG

USB_EXTVBUS

USB_5.0V

USB_VDD

R151

DNI_R1005

3.3V

DNI_R1005

14

11

12

13

CLKOUT

NXT

DIR

STP

USB_RESET_PHY

R165

12.0K

32

RBIAS

RESET

29

15

26

C109

0.1uF

0.1uF

3.3V

R153

100K

REG_EN

31

CPEN

EXTVBUS

3

10

USB_CPEN

USB_EXTVBUS

4

8

7

5

USB_VBUS

USB_DM

USB_DP

USB_ID

VBUS

DM

DP

ID

XO

XI

GND

GND

GND_FLAG

C110

4.7uF_16V

J6

R160

820_1%

56579-0519

1

2

3

4

5

C111 24pF

27

28

Y2

4

1

2

33

USB3300-EZK

USB_5.0V

USBmini-AB

6

7

USB_CLK

USB_NXT

USB_DIR

USB_STP

R163

C108

0.1uF

DATA0

DATA1

DATA2

DATA3

DATA4

DATA5

DATA6

DATA7

ON

C107

0.1uF

3.3V

VDD1.8

24

23

22

21

20

19

18

17

GND

FAULT

C106

R164

1M

SHELL_GND2

3.3V

10K

10K

10K

10K

10K

10K

10K

10K

VDD3.3

VDD3.3

VDD3.3

VDD3.3

R154

R155

R156

R157

R158

R159

R161

R162

VDD1.8

VDD1.8

30

25

16

6

R152

DNI_R1005

U25

OUT1

OUT2

OUT3

OUT4

MAX1693HEUB+x

USB_VDDA

USB_DATA0

USB_DATA1

USB_DATA2

USB_DATA3

USB_DATA4

USB_DATA5

USB_DATA6

USB_DATA7

IN1

IN2

IN3

2

4

8

10

C112 24pF

R349

SEG35-24MHz

1M

R166

10K

USB_RESET R167

USB_RESET_PHY

C431

SHELL_GND2

4.7uF_16V

USB INTERFACE

USB_RESET

USB_CLK

USB_NXT

USB_DIR

USB_STP

USB_DATA[7..0]

5 USB_RESET

5 USB_CLK

5 USB_NXT

5 USB_DIR

5 USB_STP

5 USB_DATA[7..0]

3.3V

Micro SD Card

J7

CLK

SD_CMD

CMD

SD_DAT0

SD_DAT1

SD_DAT2

SD_CD_DAT3

7

8

1

2

DAT0

DAT1

DAT2

CD/DAT3

K1

K2

ESD5V3U2U

3

ESD5V3U2U D3

3

K2

1

K1

2

K2

ESD5V3U2U D2

3

D1

K1

SD_CLK

VDD

CAGE

CAGE

CAGE

CAGE

VSS

C113

C114

C115

2.2uF

0.1uF

0.1uF

4

9

10

11

12

6

TG2

B

693071010811

Micro SD INTERFACE

SD_DAT0

SD_DAT1

SD_DAT2

SD_CD_DATA3

SD_CMD

SD_CLK

SD_DAT0 5

SD_DAT1 5

SD_DAT2 5

SD_CD_DAT3 5

SD_CMD 5

SD_CLK 5

PLACE NEAR USB3300

3.3V

USB_VDD

USB_VDDA

C116

C117

C118

C119

C120

C121

C122

C123

C124

C125

4.7uF_16V

0.1uF

0.1uF

0.1uF

0.1uF 4.7uF_16V

0.1uF

0.1uF 4.7uF_16V

0.1uF

Designed

A

NOV. 20, 2013

Drawn

ALTIMA Corporation

NOV. 20, 2013

Checked

1-5-5, Shin-Yokohama, Kouhoku-ku, Yokohama, 222-8563 JAPAN

Title

NOV. 20, 2013

Approval

Helio Board

Size Document Number

A3

NOV. 20, 2013

5

ALTHEL10SOC-R1.2

Date: Wednesday, November 20, 2013

Sheet

1

14

of

Rev

STEP

1.22

26

User I/O, RTC

5.0V

R169

DNI_R1005

R168

DNI_R1005

DISP_SPI_CLK

DISP_SPI_MOSI

5.0V

LED INTERFACE

2.5V

8 USER_LED_FPGA[3..0]

USER_LED_FPGA0

LED3

Green_LED R170

49.9

USER_LED_FPGA1

LED4

Green_LED R171

49.9

USER_LED_FPGA2

LED5

Green_LED R172

49.9

USER_LED_FPGA3

LED6

Green_LED R173

49.9

J8

5.0V

3.3V

1

2

3

4

5

6

7

8

9

10

DISP_SPI_CSn

DISP_SPI_MISO

DISP_SPI_CLK

DISP_SPI_MOSI

C428 0.1uF

U26

DISP_SPI_CSn

DISP_SPI_MISO

DISP_SPI_MOSI

DISP_SPI_CLK

VCCB

10

9

8

7

6

SSW-110-01-G-S

C429 0.1uF

11

VCCA

B1

B2

B3

B4

A1

A2

A3

A4

2

3

4

5

GND

OE

12

R451

R452

R453

R454

0

0

0

0

SPI_CSn

SPI_MISO

SPI_MOSI

SPI_CLK

SPI_CSn 5

SPI_MISO 5

SPI_MOSI 5

SPI_CLK 5

TXB0104RUTR

LCD Socket

1.5V

SW7

3.3V

USER_PB_HPS0

SKQMBAE010

R174

USER_PB_HPS1

SKQMBAE010

R175

4.7K_1%

USER_PB_HPS2

SKQMBAE010

R179

4.7K_1%

USER_PB_HPS3

SKQMBAE010

R180

4.7K_1%

4.7K_1%

U27

C126

0.1uF

VCC

VBACKUP

14

16

1

SDA

SCL

SQW/INT

15

13

12

11

10

GND

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

4

5

6

7

8

9

SW8

5,12,18 I2C_SDA_HPS

5,12,18 I2C_SCL_HPS

SW9

R176

R178

0

0

SW10

R177

4.7K_1%

3.3V

BT1

SMTU1225

DS1339C-33#

B4

I2C Address = 0x68

2.5V

SW11

USER_PB_FPGA0

SKQMBAE010

R181

4.7K_1%

USER_PB_FPGA1

SKQMBAE010

R182

4.7K_1%

USER_PB_FPGA2

SKQMBAE010

R183

4.7K_1%

CR1225

SW12

B

SW13

1.5V

SW INTERFACE

SW14

1

2

3

4

8

7

6

5

USER_DIPSW_HPS0

USER_DIPSW_HPS1

USER_DIPSW_HPS2

USER_DIPSW_HPS3

R184

R185

R186

R187

4.7K_1%

4.7K_1%

4.7K_1%

4.7K_1%

8

7

6

5

USER_DIPSW_FPGA0

USER_DIPSW_FPGA1

USER_DIPSW_FPGA2

USER_DIPSW_FPGA3

R188

R189

R190

R191

4.7K_1%

4.7K_1%

4.7K_1%

4.7K_1%

USER_PB_HPS[3..0]

USER_DIPSW_HPS[3..0]

USER_PB_HPS[3..0] 4

USER_DIPSW_HPS[3..0] 4

KHS42C

2.5V

SW15

1

2

3

4

USER_PB_FPGA[2..0]

USER_DIPSW_FPGA[3..0]

USER_PB_FPGA[2..0] 8

USER_DIPSW_FPGA[3..0] 8

KHS42C

Designed

A

GPIO

SPI_MISO

SPI_MOSI

SPI_CLK

GPIO59

GPIO58

GPIO57

GPIO1

GPIO2

GPIO3

GPIO4

R192

R193

R194

R195

100_1%

100_1%

100_1%

100_1%

SPI_MISO

SPI_MOSI

SPI_CLK

USER_HPS_GPIO61 5

NOV. 20, 2013

Drawn

ALTIMA Corporation

NOV. 20, 2013

Checked

1-5-5, Shin-Yokohama, Kouhoku-ku, Yokohama, 222-8563 JAPAN

Title

NOV. 20, 2013

Approval

Helio Board

Size Document Number

A3

NOV. 20, 2013

5

ALTHEL10SOC-R1.2

Date: Wednesday, November 20, 2013

Sheet

1

15

of

Rev

STEP

1.22

26

UART

3.3V_USB is CP2103

supply voltage.

D

3.3V_USB

3.3V_USB

C128

2.2uF

C130

4.7uF_16V

VDD

C127

0.1uF

REGIN

C129

2.2uF

VBUS

DD+

8

4

3

NC

NC

NC

NC

NC

NC

GND

SGND

21

20

15

14

13

10

2

29

U28

DNI_Green_LED

LED7 R196

220

DNI_Green_LED

LED8 R197

220

R198

5 CONV_HPS_USB_N

DNI_R1005

R199

R200

5 UART_RX

5 UART_TX

0

0

19

18

17

16

12

11

25

24

GPIO0

GPIO1

GPIO2

GPIO3

SUSPEND

SUSPEND

TXD

RXD

VIO

J9

R201

DNI_R1005

J10

R202

4.7K_1%

1

2

XJ8A-0211

XG8S-0231

DCD

DTR

DSR

RTS

CTS

RI

RST

VBUS

ID

D+

DGND

NC

CP2103-GM

C131

0.1uF

USB mini-B

SHELL_GND3

6

3

1

2

5

XJ2

28

27

26

23

22

1

6

7

3.3V_USB

54819-0519

1

2

3

4

5

R350

1M

TG3

C

C432

SHELL_GND3

4.7uF_16V

TPD4S012DRYR

U29

Designed

A

NOV. 20, 2013

Drawn

ALTIMA Corporation

NOV. 20, 2013

Checked

1-5-5, Shin-Yokohama, Kouhoku-ku, Yokohama, 222-8563 JAPAN

Title