Documente Academic

Documente Profesional

Documente Cultură

ANX9021

Încărcat de

Floricica Victor VasileDescriere originală:

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

ANX9021

Încărcat de

Floricica Victor VasileDrepturi de autor:

Formate disponibile

ANX9021FirmwareGuideRev.1.

ANX9021HDMIReceiverFirmwareGuide

BasicSystemConnections........................................................................................................................ 2

InitializationandReset.............................................................................................................................. 2

SystemInitialization.......................................................................................................................... 2

HardwareReset ................................................................................................................................. 2

LocatingtheANX9021...................................................................................................................... 3

InitializetheANX9021...................................................................................................................... 4

FirmwareOverview.................................................................................................................................. 5

MainLoop........................................................................................................................................... 6

InterruptControl ............................................................................................................................... 7

VideoServices........................................................................................................................................... 12

AutoVideoConfiguration............................................................................................................. 12

HandlingAVIInfoFrame............................................................................................................... 13

CheckingVideoFormats................................................................................................................ 15

AudioServices.......................................................................................................................................... 16

AutomaticAudioControl.............................................................................................................. 18

AudioOutputConfiguation ......................................................................................................... 19

ANX9021FirmwareGuideRev.1.2

ANALOGIX SEMICONDUCTOR PROPRIETARY AND CONFIDENTIAL Page 2of23

ANX9021HDMIReceiverFirmwareGuide

BasicSystemConnections

ThisdocumentdescribestheapplicationoftheANX9021inadigitaldisplaysystem,suchas

adigitaltelevision.Figureillustratesarepresentativesystemconfigurationinwhichthe

ANX9021isconnectedtoahostmicrocontrollerviaitsI

2

Cinterface,interruptoutput(INTR)

andrestinput(RESETN).

ANX9021

Digital Audio/Video

System

Video

processor

Audio

DAC

microcontroller

I2C

Interrupt

pin

Digital

video

output

Digital

audio

output

TMDS

and

DDC

HDMI

transmitter

Display

2~8

channel

audio

FigureConnectionstotheHDMIreceiverisadigitalmultimediasystem

InitializationandReset

SystemInitialization

InitializationandconfigurationoftheANX9021mustfollowtheinitializationofthedisplay

systemfirmware.Therecommendedstructureofthesystemfirmwareasrelatedtothe

HDMIinterfaceiscoveredinalatersectionofthisdocument.

HardwareReset

TheRESETNinputtotheANX9021iscommonlyconnectedtoageneralpurpose

input/output(GPIO)pinofthehostmicrocontroller.Firmwareisresponsibleforgenerating

thehardwareresetsignaloftheANX9021bypulingdownRESETNforaminimumof100

ms.ThelogicstateofDEVAD_CLK48BduringtherisingedgeofRESETNalsodetermines

ANX9021FirmwareGuideRev.1.2

ANALOGIX SEMICONDUCTOR PROPRIETARY AND CONFIDENTIAL Page 3of23

theI

2

CbaseaddresstowhichtheANX9021willrespond.Forsimplicitytheremainderof

thisdocumentassumesthebaseaddresses0x60and0x68arechosen.

FigureInitializationprocessfortheANX9021

LocatingtheANX9021

Figuresummarizestheinitializationprocess.AfterassertingRESETN,firmwareshould

assureithasestablishedcommunicationswiththeANX9021byconfirmingthatitcanread

itsvendoranddeviceIDregisters(seeFigure).

ANX9021FirmwareGuideRev.1.2

ANALOGIX SEMICONDUCTOR PROPRIETARY AND CONFIDENTIAL Page 4of23

FigureSamplecodeconfirmingcommunicationswiththeANX9021

InitializetheANX9021

Afterpoweronreset,mostoftheANX9021devicefunctionsarepowereddownexceptfor

pixelclockdetection(CKDT),andHDMIporttermination.Firmwareneedstoconfigurethe

otherregistersappropriatelyforthesystemdesign.Table1liststheANX9021register

functionsinvolvedininitialization.

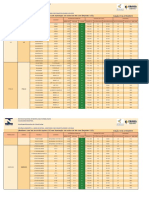

Register: Offset Register Name Initialized Vale Purpose

0x68:0x37 HDMIMute 0x03 MuteaudioandvideountildecodedHDMI

datastreamisstabletoavoidoutputnoises.

0x68:0xB3 ChipControl 0xE5 UsedigitalmethodtogenerateCKDT(HDMI

linkclockdetection).

0x60:0x79 Interrupt

Control

0x02,System

dependent

Initializedvalueissystemdependent.Forthe

EvaluationBoard,interruptsignalissetto

pushpulloutputandhighpolarity.

0x60:0x75 INTRMask1 0xFC DisableHCDPinterruptstoconformto

multimediasourcesthatdonotuseHDCP.

0x60:0x76 INTRMask2 0xBF Enablevideodetectionrelatedinterrupts.

0x60:0x77 INTRMask3 0x3F EnableAVI,SPD,audioandMPEGpacket

interrupts

0x60:0x78 INTRMask4 0xEF EnableHDCPfailureandaudioerror

interrupts

0x60:0x7D INTRMask5 0xEF Enableformatchangerelatedinterrupts

0x60:0x7E INTRMask6 0xFF EnablenewACPandcableunpluginterrupts

0x68:0x16 ACRControl3 0x07 ChangeCTSchangethresholdto0x07.

0x60:0x5F AutoVideo 0x00,System Settheautomaticvideooutputformatbased

ontherequirementofthesystem.TheEval

c1 = 0;

whi l e ( 1)

{

HDMI RX_r eset _pi n = 0;

del ay_ms( 10) ;

HDMI RX_r eset _pi n = 1;

del ay_ms_( 10) ;

c = i 2c_r ead_P0_r eg( 0x02, &c1) ;

i f ( ( c == 0) && ( c1 == 0x21) ) {

c = i 2c_r ead_P0_r eg( 0x03, &c1) ;

i f ( c == 0) && ( c1 == 0x90) )

br eak;

}

}

ANX9021FirmwareGuideRev.1.2

ANALOGIX SEMICONDUCTOR PROPRIETARY AND CONFIDENTIAL Page 5of23

Format dependent Boarduses0x00(componentvideo).

0x68:0x27 I2SControl2 0xF9,System

dependent

ConfigureI

2

Soutputs.TheEvalBoard

supportsupto8channelsandusesPCMdata

only.

0x68;0x29 AudioControl 0x05,System

dependent

EnablesI

2

SandSPDIFoutputs.

0x60:0x05 SoftwareReset 0x09then

0x80

Bywriting0x09followedby0x80tothe

softwarerestregister,thefirmwareperforms

asoftreset,HDCPreset,andenables

automaticHDCPreset.

0x60:0xB5 AECControl 0x05 Enableautoaudioandvideocontrol

0x60:0x09 PortSelect 0x11 EnablesHDMIPort0asthedefaultinput

Table1RegistersettingsforANX9021initialization

FirmwareOverview

AftertheANX9021hasbeenproperlyinitializedandwhenanHDMIsourceplugsintothe

activeinputport,thereceiverwilldetecttheTMDSclockovertheHDMIcable.Aclock

detectinterruptwilloccur,softwareacknowledgestheinterrupt,powersupallreceiver

functionsandcometonormaloperationmode.

Innormaloperationmode,allinterrupteventsareavailable.IftheHDMItransmittersendsa

validvideostream,theSYNCsignal(HSYNCandVSYNC)willbevalid,thusallowingthe

firmwaretomeasurethevideoformatandtimingthroughthecorrespondingregisters.Ifthe

videostreamisstableandtheformatissupported,firmwaremayenablethedigitalvideo

outputs.

SimilarlyfirmwareshouldwaituntilwaittheaudiostreamisstabletoenabletheI

2

Sand/or

SPDIFinterfaces.Figureshowsthehighlevelstatetransitionsofthefirmware.

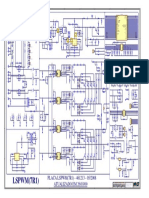

MonitorCKDTisapowereddownstate.WhentheHDMIreceiverwasfirstinitialized,or

whentheHDMIcableisunplugged,firmwarepowersdownmostofthechipfunctionsand

checksforTMDSclockdetection.

WaitSCDTfollowsTMDSclockdetection.FirmwareiswaitingfortheTMDSlinkto

becomestablyestablishedbywaitingforSCDTtobecomeactive.

WaitVideofollowssyncdetection.Firmwareiswaitingforastablevideostreamand

confirmingthatitisinaformatthatissupportedbythesystembeforeenablingvideooutput.

WaitAudioisperformedafterfirmwarehasestablishedthatvideostreamisstableandthe

inputincludesaudiodatastream.Firmwareiswaitingforastableandsupportedaudio

streampriortoenablingaudiooutput.

Playbackisthenormalaudioandvideooutputstate.

ANX9021FirmwareGuideRev.1.2

ANALOGIX SEMICONDUCTOR PROPRIETARY AND CONFIDENTIAL Page 6of23

FormatErroristhestateinwhichfirmwarehasconcludedthatthesystemdoesnotsupport

theincomingformatandwaitsforanewvideostream.

FigureFirmwarestatetransitiondiagram

MainLoop

Themainfunctionisasfollowing:

voidmain(void){

init_mcu();

init_9021_system();

while(1){

...

int_process();

timer_process();

//misc_process();

}

}

ANX9021FirmwareGuideRev.1.2

ANALOGIX SEMICONDUCTOR PROPRIETARY AND CONFIDENTIAL Page 7of23

Onaboveprogram,init_mcu()istoinitialthemicrocontrollerrelatethings,suchastimer;

init_9021_system()istoresettheANX9021chipandinitializetheANX9021registers,

int_process()istheinterrupteventhandler,timer_process()istoprocessthetimerevent.

InterruptControl

Thebasicstructureofthefirmwareisaloop,whichmonitorsallANX9021interruptevents

andcallsthecorrespondingserviceroutinesforprocessing.Theinterruptprocessingflow

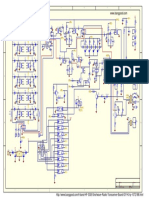

chartisshownas

FigureandFigure.

WhentheANX9021isinpowereddownmode,theonlyavailableinterrupteventisTMDS

clockdetect(CKDT);sothefirmwaresimplypowersupthedevice(0x60:0x08,setbit0to1).

Whenthedeviceispoweredup,firmwareneedstoquerytheinterruptstatusregisters(0x60,

offsets0x710x74and0x7B,0x7C)todeterminetheappropriateserviceroutine.

Someprocesses,suchaswaitingforincomingvideostreamtobestable,takesalongtimeand

sowaitingforaprocesstocompletebeforeservicinganotherwouldintroduceunacceptable

latenciesintothesystem.Thereforethefirmwaretimemultiplexesitsactivitiesintodefined

timeslots.

Thefirmwareincludesaschedulerthatdividespendingtasksintofourtimeslots(Slot0,

Slot1,Slot2,Slot3),eachslotlastsabout8ms.Slot0isreservedforvideorelatedprocesses,

Slot1isreservedforaudiorelatedprocesses,andSlot2isusedforerrorhandling.Slot3is

reserved.

ANX9021FirmwareGuideRev.1.2

ANALOGIX SEMICONDUCTOR PROPRIETARY AND CONFIDENTIAL Page 8of23

FigureInterruptprocessingflowchart

ANX9021FirmwareGuideRev.1.2

ANALOGIX SEMICONDUCTOR PROPRIETARY AND CONFIDENTIAL Page 9of23

voi d ANX9021_I nt _Pr ocess( voi d)

{

BYTE r c, c, c1, c2, s1, s2, s3, s4, s5, s6, s7, t mp;

ANX9021_ReadI 2C_RX0( STATE_REG, &s7) ;

i f ( s7 & 0x01)

{

ANX9021_Sync_Det _I nt ( ) ;

}

ANX9021_ReadI 2C_RX0( STATE_REG, &c) ;

i f ( c&0x02 )

{

i f ( sysSt at e == MONI TOR_CKDT)

{

gm_Pr i nt f ( "ANX9021_I nt _Pr ocess") ;

gm_Del ay10ms( 1) ;

ANX9021_Wr i t eI 2C_RX0( TMDS_PLL_RNG_CTRL_REG, 0x00) ;

/ / TMDS r eset r egi st er ( hi dden r egi st er )

ANX9021_Wr i t eI 2C_RX0( 0x95, 0x08) ;

gm_Del ay100ms( 4) ;

ANX9021_ReadI 2C_RX0( TMDS_PLL_RNG_STATUS_REG, &c) ;

c1 = c & 0x61;

i f ( c&0x02) c1 = c1 | 0x04;

i f ( c&0x04) c1 = c1 | 0x10;

i f ( c&0x08) c1 = c1 | 0x02;

i f ( c&0x10) c1 = c1 | 0x08;

c1 = c1 | 0x80;

ANX9021_Wr i t eI 2C_RX0( TMDS_PLL_RNG_CTRL_REG, c1) ;

/ / TMDS r eset r egi st er ( hi dden r egi st er )

ANX9021_Wr i t eI 2C_RX0( 0x95, 0x08) ;

ANX9021_ReadI 2C_RX0( SYS_CTRL1_REG, &c) ;

ANX9021_Wr i t eI 2C_RX0( SYS_CTRL1_REG, c & 0xf e) ;

gm_Del ay1ms( 5) ;

ANX9021_Wr i t eI 2C_RX0( SYS_CTRL1_REG, c | 0x01) ;

gm_Del ay10ms( 5) ;

ANX9021_Set _Sys_St at e( WAI T_SCDT) ;

ANX9021_ReadI 2C_RX0( SYS_CTRL1_REG, &c) ;

ANX9021_Wr i t eI 2C_RX0 ( SYS_CTRL1_REG, c | 0x01) ;

/ / power up al l

}

el se

ANX9021FirmwareGuideRev.1.2

ANALOGIX SEMICONDUCTOR PROPRIETARY AND CONFIDENTIAL Page 10of23

{

ANX9021_ReadI 2C_RX0( I NTR1_REG, &s1) ;

ANX9021_Wr i t eI 2C_RX0( I NTR1_REG, s1) ;

ANX9021_ReadI 2C_RX0( I NTR1_MASK_REG, &c1) ;

ANX9021_ReadI 2C_RX0( I NTR2_REG, &s2) ;

ANX9021_Wr i t eI 2C_RX0( I NTR2_REG, s2) ;

ANX9021_ReadI 2C_RX0( I NTR2_MASK_REG, &c1) ;

ANX9021_ReadI 2C_RX0( I NTR3_REG, &s3) ;

ANX9021_Wr i t eI 2C_RX0( I NTR3_REG, s3) ;

ANX9021_ReadI 2C_RX0( I NTR3_MASK_REG, &c1) ;

ANX9021_ReadI 2C_RX0( I NTR4_REG, &s4) ;

ANX9021_Wr i t eI 2C_RX0( I NTR4_REG, s4) ;

ANX9021_ReadI 2C_RX0( I NTR4_MASK_REG, &c1) ;

ANX9021_ReadI 2C_RX0( I NTR5_REG, &s5) ;

ANX9021_Wr i t eI 2C_RX0( I NTR5_REG, s5) ;

ANX9021_ReadI 2C_RX0( I NTR5_MASK_REG, &c1) ;

ANX9021_ReadI 2C_RX0( I NTR6_REG, &s6) ;

ANX9021_Wr i t eI 2C_RX0( I NTR6_REG, s6) ;

ANX9021_ReadI 2C_RX0( I NTR6_MASK_REG, &c1) ;

i f ( s2 & ANX9021_SCDT_CHANGE)

{

/ / SYNC det ect i nt er r upt

gm_Pr i nt f ( "SYNC det ect i nt er r upt . ") ;

ANX9021_Sync_Det _I nt ( ) ;

}

i f ( s2 & ANX9021_HDMI _DVI _MODE_CHANGE)

{

/ / HDMI _DVI det ect i nt er r upt

gm_Pr i nt f ( "HDMI - DVI mode change i nt er r upt . ") ;

ANX9021_HDMI _DVI _I nt ( ) ;

}

i f ( s3 & ANX9021_NEW_AVI _DECT)

{

/ / New AVI i nt er r upt

gm_Pr i nt f ( "New avi i nt er r upt . ") ;

avi _avai l abl e =1;

ANX9021_ReadI 2C_RX0( I P_CTRL_REG, &c) ;

ANX9021_Wr i t eI 2C_RX0( I P_CTRL_REG, c & 0xf e) ;

}

i f ( s1 & ANX9021_CTS_ACR_CHANGE)

/ / some audi o exept i on

{

gm_Pr i nt f ( "Rest ar t _audi o_chk. ") ;

ANX9021FirmwareGuideRev.1.2

ANALOGIX SEMICONDUCTOR PROPRIETARY AND CONFIDENTIAL Page 11of23

ANX9021_Rest ar t _Audi o_Chk( ) ;

}

i f ( s2 & ANX9021_CTS_RECV) / / det ect ct s

{

gm_Pr i nt f ( "CTS_r cv_i nt ") ;

ANX9021_Ct s_Rcv_I nt ( ) ;

}

i f ( s2 & ANX9021_AUDI O_RECV) / / det ect audi o

{

gm_Pr i nt f ( "Audi o packet r ecei ved. ") ;

ANX9021_Audi o_Rcv_I nt ( ) ;

}

i f ( s4 & ANX9021_HDCP_ERROR) / / HDCP er r or

{

gm_Pr i nt f ( "HDCP er r or i nt . ") ;

ANX9021_HDCP_Er r or _I nt ( ) ;

}

i f ( ( s4 & 0x01) && ( sysSt at e == PLAYBACK) )

{

anx9021_f i f o_e_cnt 1 ++;

}

el se{

anx9021_f i f o_e_cnt 1 = 0;

}

i f ( ( s4 & 0x02) && ( sysSt at e == PLAYBACK) )

{

anx9021_f i f o_e_cnt 2 ++;

}

el se{

anx9021_f i f o_e_cnt 2 = 0;

}

i f ( s5 & ANX9021_AAC_MUTE) / / AAC done

{

gm_Pr i nt f ( "Audi o Aut o Conf i gur e done i nt . ") ;

ANX9021_Aac_Done_I nt ( ) ;

}

}

}

}

FigureInterruptprocessingloop

ANX9021FirmwareGuideRev.1.2

ANALOGIX SEMICONDUCTOR PROPRIETARY AND CONFIDENTIAL Page 12of23

VideoServices

MONI TOR_CKDT

Vi deo Ti mer

sl ot

CLK Det ect ed

Ent er power on mode,

Set up TMDS

and ent er WAI T_SCDT

st at e

Sync Val i d?

SCDT count

expi r ed?

I ncr ement

SCDT count er

and wai t

l onger

Ent er Power

Down mode

Ent er

MONI TOR_CKDT

st at e

Syst em i n Wai t

vi deo or

pl ayback st at e

AVMUTE set ?

( MUSTATUS=1)

Cl ear Vi deo

St abl e

count er

Ent er Wai t

Vi deo St at e

Mut e Audi o

Mut e Vi deo

Vi deo f or mat

changed?

Vi deo st abl e

l ong enough?

HDMI mode?

Vi deo mode

suppor t ed?

Vi deo mode

suppor t ed?

Unmut e Vi deo

Ent er Wai t

Audi o st at e

Mut e Vi deo

Ent er For mat

Er r or st at e

Unmut e Vi deo

Ent er

Pl ayback

st at e

Check AVI

Yes

Yes

Yes

Yes

Yes

Yes

Yes Yes

Yes

Yes

r et ur n

Yes

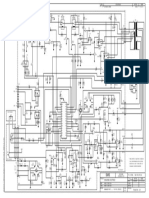

Figure7Videotimeslotservices

TheANX9021supportsconfigurablevideooutputformatscontrolledbytheVideoOutput

Formatregister(0x60,offset0x5F).Theappropriateoutputformatdependsontheformats

supportbythedownstreamvideoprocessorandisthereforespecifictoasystemdesign.

HDMIsupportsalargevarietyofinputvideoformats.Videoformatinformationisprovided

inanAVIInfoFrametoallowthefirmwaretoquicklydeterminetheinputformat.The

ANX9021supportsautomaticvideoconfigurationwhichisenabledbysettingbit5ofthe

AUTOregister(0x60,offset0xB5).Itisrecommendedforthefirmwaretotakeadvantageof

thisfeature.

WhenthesystemisintheWaitVideostate,itmustdeterminethatdecodedvideoinstable

beforeunmutingthevideooutput.Ifthereportedvideotimingischanging,thedecoded

videostreamisunstable.

Afterthevideoisstable,thesystementerstheWaitAudiostateiftheinputisHDMIorenters

thePlaybackstateiftheinputisDVI.

AutoVideoConfiguration

ByanalysisthearrivingAVIInfoFramesandmeasuringthevideostreams,theANX9021can

getmostinformationofcomingvideo,suchasvideoformat(RGB4:4:4,YCbCr4:4:4,YCbCr

4:2:2),Hresolution,Vresolution,etc.InAVCmode,oncethemicrocontrollerassignsthe

ANX9021FirmwareGuideRev.1.2

ANALOGIX SEMICONDUCTOR PROPRIETARY AND CONFIDENTIAL Page 13of23

desiredvideooutputformat,ANX9021willadaptitsvideodatapathtoconverttheincoming

formattotheoutputformatautomatically.

BysettingtheAutoControlRegister(0x60:0xB5),bit2to1,theANX9021willworkin

AVCmode.ThenusershouldsettheAutoVideoOutputFormatControlRegister

(0x60:0x5F)tothecorrectvalue.

Forexample,settheAutoVideoOutputFormatControlRegisterto0xC0,theoutputformat

willbeYCbCr4:2:2(16Bit),with16bitdatawidth,separatesyncbutwithoutCLK4B,

MUX_SYNC,andanalogoutput.IftheinputvideoformatisRGB4:4:4,theregistersshowed

intable2willbesetbytheAVClogicautomatically.

RegisterControlledByAVC

RegisterName Address

(0x60)

FieldName Bit Value Comment

INS_SYNC 7 0

MUX_YC 6 0

DITHER 5 1

RANGE_R2Y 4 1

CSPACE_R2Y 3 1

UP_SAMPLE 2 0

DOWN_SAMPLE 1 0

VideoMode

Register1

0x4A

INS_CSYNC 0 0

RANGE_Y2R 3 0 VideoMode

Register2

0x49

CSPACE_Y2R 2 0

INV_VSYNC 7 0

INV_HSYNC 6 0

CSYNC_VSYNC 5 0

CSYNC_HSYNC 4 0

CSPACE_Y2R 2 0

VideoControlRegister 0x48

CSPACE_R2Y 0 1

Table2RegisterscontrolledbyAVCLogicinAVCmode

Aboutthedetaileddescriptionofthesethreevideocontrolregisters,pleaserefertothe

ANX9021DS_r05.pdf,table41~43,page36~37.

HandlingAVIInfoFrame

ThedetailedAVIInfoFrameisdescribedintheHDMI1.1Specification(Section8.2.1)and

EIA/CEA861BSpecification(Section6.1).ThecontentoftheAVIInfoFrameisasTable3.

Packet

Byte#

EIA/CEA

861BByte

#

7 6 5 4 3 2 1 0

ANX9021FirmwareGuideRev.1.2

ANALOGIX SEMICONDUCTOR PROPRIETARY AND CONFIDENTIAL Page 14of23

PB0 N.A. Checksum

PB1

DataByte

1

Rsvd

(0)

Y1 Y0 A0 B1 B0 S1 S0

PB2

DataByte

2

C1 C0 M1 M0 R3 R2 R1 R0

PB3

DataByte

3

Reserved(0) SC1 SC0

PB4

DataByte

4

Rsvd

(0)

VIC6 VIC5 VIC4 VIC3 VIC2 VIC1 VIC0

PB5

DataByte

5

Reserved(0) PR3 PR2 PR1 PR0

PB6

DataByte

6

LineNumberofEndofTopBar(lower8bits)

PB7

DataByte

7

LineNumberofEndofTopBar(upper8bits)

PB8

DataByte

8

LineNumberofstartofBottomBar(lower8bits)

PB9

DataByte

9

LineNumberofstartofBottomBar(upper8bits)

PB10

DataByte

10

PixelNumberofEndofLeftBar(lower8bits)

PB11

DataByte

11

PixelNumberofEndofLeftBar(upper8bits)

PB12

DataByte

12

PixelNumberofEndofRightBar(lower8bits)

PB13

DataByte

13

PixelNumberofEndofRightBar(upper8bits)

PB14

PB27

n.a. Reserved(0)

Table3AVIInfoFramePacketContents

TheAVIInfoFramewillbecarriedinthecontrolpacketandbetransmittedfromthesource

tothesink.TheANX9021willcaptureandstoretheAVIInfoFrameintheregistersgroup

whichdescribedinTable4.Theseregistersarereadonly.Thefirmwarewillgetsome

informationfromtheseregistersifnecessary.

Register

Address

RegisterName R/W Default

Value

Description

0x68:0x40 AVI_TYPE_CODE RO 0x82 DefinedbyHDMI

Spec1.1.

0x68:0x41 AVI_VERSION_NUMBER RO 0x02 DefinedbyHDMI

Spec1.1.

ANX9021FirmwareGuideRev.1.2

ANALOGIX SEMICONDUCTOR PROPRIETARY AND CONFIDENTIAL Page 15of23

0x68:0x42 AVI_INFOFRAME_LENG

TH

RO 0x0D LengthofAVI

InfoFrame(13)

0x68:0x43 AVI_PB0 RO 0 Checksum

0x68:0x44 AVI_PB1 RO

0x68:0x45 AVI_PB2 RO

0x68:0x46 AVI_PB3 RO

0x68:0x47 AVI_PB4 RO

0x68:0x48 AVI_PB5 RO

0x68:0x49 AVI_PB6 RO

0x68:0x4A AVI_PB7 RO

0x68:0x4B AVI_PB8 RO

0x68:0x4C AVI_PB9 RO

0x68:0x4D AVI_PB10 RO

0x68:0x4E AVI_PB11 RO

0x68:0x4F AVI_PB12 RO

0x68:0x50 AVI_PB13 RO

0 AVIInfoFrame

DataBytes

Table4AVIInfoFrameRegisters

CheckingVideoFormats

Incomingvideoformatmaychangeduringplayback.Firmwareisrequiredtodetectthe

changeandmutethevideooutputuntilthenewvideostreamisstabletoavoidanyviewable

artifacts.Todetectvideoformatchanges,firmwareshouldmonitorthefollowingregisters

Videohorizontalresolution,lowbyte(register0x60,offset0x3A)

Videohorizontalresolution,highbyte(register0x60,offset0x3B)

Videoverticalresolution,lowbyte(register0x60,offset0x3C)

Videoverticalresolution,highbyte(register0x60,offset0x3D)

Videopixelclockcounter(register0x60,offset0x6F)

Thevideoformatmaybechangedduringtheplayingbackstate,andthenthefirmware

shouldcatchthechangeanddosomecorrespondingprocessjustlikemutingvideoand

videobeforethenewformatvideoisstable.Thefirmwarecancatchtheformatchangefrom

thechangeoffiveregisters.Theseregistersarelistedintable5.

RegisterName Address Description

VideoHorizontalResolutionLowByte

Register

0x60:0x3A

VideoHorizontalResolutionHighByte

Register

0x60:0x3B

VideoVerticalResolutionLowByteRegister 0x60:0x3C

VideoVerticalResolutionHighByteRegister 0x60:0x3D

VideoPixelClockCounterRegister 0x60:0x6F

ANX9021FirmwareGuideRev.1.2

ANALOGIX SEMICONDUCTOR PROPRIETARY AND CONFIDENTIAL Page 16of23

Table5VideoFormatChangeCheckingRelatedRegisters

Aboutthedetaileddescriptionofthesethreevideocontrolregisters,pleaserefertothe

ANX9021DS_r05.pdf,table39~40,page35~36,andtable57,page

42.

Figure8showstheflowchartofthefirmwareusedtodeterminevideoformatchange.In

everyvideotimeslot,firmwarewillfetchthevaluesofthesefiveregistersandcomparethem

againstthevaluesrecordedfromtheprevioustimeslot.Iftheresultsdifferbymorethan3,

videoformathaschanged.

ANX9021FirmwareGuideRev.1.2

ANALOGIX SEMICONDUCTOR PROPRIETARY AND CONFIDENTIAL Page 17of23

Figure8Videoformatchangedeterminationflowchart

AudioServices

InHDMImode,aftervideoisstable,thefirmwarewillbeginaudioprocessing.Basically,

videoprocessingrelatedregistersaredescribedinTable6.

RegisterName Address Bit Value Comment

HDCPreceiverstatus

shadow

0x60:0x30 4 1 Bit4showswhether

theworkmodeisDVI

orHDMI.

HDMImutecontrolregister 0x68:0x37 4 0 Bit4showswhether

theaudioismuteor

not.

AutoControlRegister 0x60:0xB5 0 1 Setbit0=1toenable

autoaudioconfig.

AutoControlRegister 0x60:0xB5 5 1 AACwillcontrolI2S

andSPDIFoutput.

Table6BasicAudioProcessingRelatedRegisters

IftheANX9021isusedtoreceiveanHDMIdatastream,itwillhavetoprocessbothvideo

andaudioinformation.IftheincomingdataisinDVImode,onlyvideodataisinvolved.

ANX9021FirmwareGuideRev.1.2

ANALOGIX SEMICONDUCTOR PROPRIETARY AND CONFIDENTIAL Page 18of23

Therefore,whentheincomingformatisDVI,thesystementersthePlaybackstateassoonas

videobecomesstable.WhentheincomingformatisHDMI,thesystementerstheWait

Audiostate.OnlyafteraudioalsobecomesstabledoesthesystementersPlayback.

Audio Time

Slot

Waiting on

CKDT?

HDMI

input?

HDCP

error?

PLAYBACK

state?

WAIT

AUDIO?

Get N/CTS?

Audio Stable

long enough?

Audio

Muted?

Clear Audio

stable counter

Enter Wait

Audio State

Increment

Audio stable

counter

Unmute Audio

Enter

Playback

State

Yes

Yes

Yes

Yes

Yes Yes Yes

Yes

return

Figure9Audiotimeslotservices

Figure9showstheaudiotimeslotflowchart.Theregistersinvolvedinaudioprocessing

follows:

HDCPreceiverstatusshadow(register0x60,offset0x30)

HDMImute(register0x68,offset0x17)

Autocontrol(register0x60,offset0xB5)

AutomaticAudioControl

TheANX9021supportsautomaticaudiocontrol,whichisenabledbysettingAAC_OEand

AAC_ENintheAutoControlregister.Whenanaudioexceptionoccurs,ANX9021hardware

automaticallymutestheaudiooutput.Unmuteiscontrolledbythefirmware.

Therelatedcodecanbefoundintheroutineinitial.

i2c_write_p0_reg(AEC_EN0_REG,0xe7);

i2c_write_p0_reg(AEC_EN1_REG,0xd9);

ANX9021FirmwareGuideRev.1.2

ANALOGIX SEMICONDUCTOR PROPRIETARY AND CONFIDENTIAL Page 19of23

i2c_write_p0_reg(AEC_EN2_REG,0x06);

i2c_write_p0_reg(AEC_CTRL_REG,0x05);

AutoaudiocontrolisenablebysettingAAC_ENdescribedinTable7.AAC_OEcontrols

whetherI2SandSPDIFoutputisinfluencedbyAAC_EN.

RegisterName Address Bit Default

Value

Description

AAC_OE 0x60:0xB5 5 0x0

AAC control of I2S and SPDIF output. 1 =

enable AAC to control I2S and SPDIF

output; 0 = AAC has no control of I2S and

SPDIF.

AAC_EN 0x60:0xB5 0 0x0

AAC enable control. 1 = enabled; 0 =

disabled.

Table7AutoaudiocontrolRelatedRegisters

WhenAAC_ENisset,eachbitofthefollowingthreeregistersenablesaconditionwhich

triggershardwaresoftmute.Besides,mostoftheseconditions(except2)alsoset

correspondinginterruptbit.ThedetailsarelistedinTable8.

RegisterName Address Bit Default

Value

Description

AEC_EN00 0x60:0xB6 0 0x0

Cable unplug exception enable control.

AEC_EN01 0x60:0xB6 1 0x0

PLL unlocked exception enable control.

AEC_EN02 0x60:0xB6 2 0x0

ACR N changed exception enable control.

AEC_EN03 0x60:0xB6 3 0x0

ACR CTS changed exception enable

control.

AEC_EN04 0x60:0xB6 4 0x0

Video clock changed exception enable

control.

AEC_EN05 0x60:0xB6 5 0x0

InforFrame CP mute set exception enable

control.

AEC_EN06 0x60:0xB6 6 0x0

Sync detect exception enable control.

AEC_EN07 0x60:0xB6 7 0x0

Clock switch detect exception enable

control.

AEC_EN08 0x60:0xB7 0 0x0

HDMI mode change exception enable

control.

AEC_EN09 0x60:0xB7 1 0x0

Audio FIFO underrun exception enable

control.

AEC_EN10 0x60:0xB7 2 0x0

Audio FIFO overrun exception enable

control.

AEC_EN11 0x60:0xB7 3 0x0

CTS reused exception enable control.

AEC_EN12 0x60:0xB7 4 0x0

Fs changed exception enable control.

AEC_EN13 0x60:0xB7 5 0x0

Interlace changed exception enable control.

AEC_EN14 0x60:0xB7 6 0x0

Sync Polarity changed exception enable

control.

AEC_EN15 0x60:0xB7 7 0x0

H resolution changed exception enable

control.

AEC_EN16 0x60:0xB8 0 0x0

V resolution changed exception enable

control.

ANX9021FirmwareGuideRev.1.2

ANALOGIX SEMICONDUCTOR PROPRIETARY AND CONFIDENTIAL Page 20of23

AEC_EN17 0x60:0xB8 1 0x0

Link error exception enable control.

AEC_EN18 0x60:0xB8 2 0x0

Fn clock changed exception enable control.

Table8AutoExceptionEnableRegisters

EachaudioexceptionenablebitlistedinTable8enableoneconditiontotriggerthehardware

softmute.Unmuteistriggeredbyfirmware.

AudioOutputConfiguation

AudiooutgeneralcontrolisimplementedbysettingtheregisterslistinTable9.

Name Address Bit Default

Value

Description

PASS_SPDIF_ERR 0x68:0x29 4 0x1 Pass SPDIF error control. 0 = do not pass

SPDIF type of errors, conceal errors by

repeating last good sample; 1 = pas all

audiodata,regardlessoferrors.

PASS_AUDIO_ERR 0x68:0x29 3 0x1 Pass audio error control. 0 = do not pass

errors, conceal errors by repeating last

sample;1=passallaudiodata,regardless

oferrors.

SOFT_MUTE_EN 0x68:0x29 5 0x0 Softmuteenable.1=enable;0=disable.

CH3_MU 0x68:0x32 3 0x0 Channel3mute.

CH2_MU 0x68:0x32 2 0x0 Channel2mute.

CH1_MU 0x68:0x32 1 0x0 Channel1mute.

CH0_MU 0x68:0x32 0 0x0 Channel0mute.

Table9AudiooutgeneralcontrolRegisters

AudiooutI2ScontrolisimplementedbysettingtheregisterslistinTable10.

Name Address Bit Default

Value

Description

I2S_MODE 0x68:0x29 2 0x0 I2S output mode control. 0 = All I2S

outputsaregrounded(SD,SCK,WS);1=

SCK and WS toggle, SD is on or off

dependingonthevalueinI2S_CTRL2.

SCK_EDGE 0x68:0x26 6 0x1 Sampleclockedgeselect.0=sampleedge

isrising;1=sampleedgeisfalling.

SIZE_SEL 0x68:0x26 5 0x0 Wordsizeselect.1=16bits;0=32bits.

MSB_SIGN_EXT 0x68:0x26 4 0x0 MSB sign extension enable control. 0 =

enabled;1=disabled.

WS_POL 0x68:0x26 3 0x0 Word select left/right polarity select. 0 =

leftpolaritywhenworksselectislow;1=

leftpolaritywhenwordselectishigh.

JUST_CTRL 0x68:0x26 2 0x0 SD Justification control. 1 = data is right

ANX9021FirmwareGuideRev.1.2

ANALOGIX SEMICONDUCTOR PROPRIETARY AND CONFIDENTIAL Page 21of23

justified;0=dataisleftjustified.

DIR_CTRL 0x68:0x26 1 0x0 SDdataIndian(MSBorLSBfirst)control.

0=MSBfirst;1=LSBfirst.

SHIFT1 0x68:0x26 0 0x0 WS to SD shift first bit. 0 = fist bit shift

(PhilipsSpec);1=noshift.

SD3_EN 0x68:0x27 7 0x0 I2SChannel3outputcontrol.0=disabled

(alwaysoutputlow);1=channelenabled.

SD2_EN 0x68:0x27 6 0x0 I2SChannel2outputcontrol.0=disabled

(alwaysoutputlow);1=channelenabled.

SD1_EN 0x68:0x27 5 0x0 I2SChannel1outputcontrol.0=disabled

(alwaysoutputlow);1=channelenabled.

SD0_EN 0x68:0x27 4 0x0 I2SChannel0outputcontrol.0=disabled

(alwaysoutputlow);1=channelenabled.

MCLK_EN 0x68:0x27 3 0x0 MCLKenable.0=tristateMCLKOUT;1=

enableMCLKOUT.

VUCP_EN 0x68:0x27 1 0x0 VUCP bits enable. 0 = send only 24 real

data bits via I2S; 1 = send 28 bits of data

withVUCPbist.

PCM_DET 0x68:0x27 0 0x1 I2S data pass select. 0 = pass whatever

dataisintheS/PDIFpackets;1=passonly

data from S/PDIF packets which are

recognizedasPCMdata.WhennonPCM

dataisdetected,send0.

SD3_MAP 0x68:0x28 7:6 0x3 I2S Channel 3 data stream select. 0 =

stream 0; 1 = stream 1; 2 = stream 2; 3 =

stream3;

SD2_MAP 0x68:0x28 5:4 0x2 I2S Channel 2 data stream select. 0 =

stream 0; 1 = stream 1; 2 = stream 2; 3 =

stream3;

SD1_MAP 0x68:0x28 3:2 0x1 I2S Channel 1 data stream select. 0 =

stream 0; 1 = stream 1; 2 = stream 2; 3 =

stream3;

SD0_MAP 0x68:0x28 1:0 0x0 I2S Channel 0 data stream select. 0 =

stream 0; 1 = stream 1; 2 = stream 2; 3 =

stream3;

SW3 0x68:0x2E 7 0x0 Swapleft/rightchannelonI2Schannel3.1

=swap;0=noswap.

SW2 0x68:0x2E 6 0x0 Swapleft/rightchannelonI2Schannel2.1

=swap;0=noswap.

SW1 0x68:0x2E 5 0x0 Swapleft/rightchannelonI2Schannel1.1

=swap;0=noswap.

SW0 0x68:0x2E 4 0x0 Swapleft/rightchannelonI2Schannel0.1

=swap;0=noswap.

ANX9021FirmwareGuideRev.1.2

ANALOGIX SEMICONDUCTOR PROPRIETARY AND CONFIDENTIAL Page 22of23

LENOV 0x68:0x29 7 0x0 Enable overwrite of the audio sample

length for the I2S data. 0 = take from the

HDMI packet; 1 = take form

AUDO_MUTEbit[7:4].

LEN_OVERRIDE 0x68:0x32 7:4 0x0 Audiowordlengthoverridevalue.When

LENOV = 1, this value is used to set the

word length for I2S output instead of the

lengthextractedfromchannelstatusbits.

Table10AudiooutI2ScontrolRegisters

AudiooutS/PDIFcontrolisimplementedbysettingtheregisterslistinTable11.

Name Address Bit Default

Value

Description

SP_MODE 0x68:0x29 1 0x0 SPDIFflatlineenable.0=SPDIFoutput

alwaysproducesvalidbiphasemark

encodeddata,evenduringflatline;1=

SPDIFoutputiszero(grounded)ifflat

lineisdetected.

SP_EN 0x68:0x29 0 0x0 SPDIFoutputenable.1=enabled;0=

disabled(outputflatlineorzero

accordingtoSP_MODE)

Table11AudiooutS/PDIFcontrolRegisters

AudioinS/PDIFchannelstatuscanbereadoutthroughtheregisterslistedinTable12

Name Address Bit Default

Value

Description

MODE 0x68:0x2A 7:6 0x0 00=PCMAudio

PRE_EMPHASIS 0x68:0x2A 5:3 0x0 000 = 2 audio channels without pre

emphasis;

001 = 2 audio channels with 50/15 usec

preemphasis???

SW_CPRGT 0x68:0x2A 2 0x0 0 = software for which copyright is

asserted;

1 = software for which no copyright is

asserted

NON_PCM 0x68:0x2A 1 0x0 0 = audio sample word represents linear

PCMsamples;

1 = audio sample word used for other

purposes.

PROF_APP 0x68:0x2A 0 0x0 0 = consumer applications; 1 =

professionalapplications.

CAT_CODE 0x68:0x2B 7:0 0x0 Category code (corresponding to channel

statusbits[15:8])

ANX9021FirmwareGuideRev.1.2

ANALOGIX SEMICONDUCTOR PROPRIETARY AND CONFIDENTIAL Page 23of23

CH_NUM 0x68:0x2C 7:4 0x0 Channel number (corresponding to

channelstatusbits[23:20])

SOURCE_NUM 0x68:0x2C 3:0 0x0 Sourcenumber(correspondingtochannel

statusbits[19:16])

FS_FREQ 0x68:0x30 3:0 0x0 Samplingclockfrequency(corresponding

to channel status bits [27:24]). 0000 = 44.1

KHz;0010=48KHz;0011=32KHz;1000

= 88.2 KHz; 1010 = 96 KHz; 176.4 KHz;

1110=192KHz;others=reserved.

CLK_ACCUR 0x68:0x30 5:4 0x0 Clock accuracy (corresponding to

channels status bits [29:28]). These two

bits define the sampling frequency

tolerance. The bits are set in the

transmitter.

AUD_LENGTH 0x68:0x31 7:4 0x0 Audio word length (corresponding to

channel status bits [35:33]). When

AUD_MX=0,000=16bits;010=18bits;

100 = 19 bits; 101 = 20 bits; 110 = 17 bits;

whenAUD_MX=1,001=20bits;010=22

bits; 100 = 23 bits; 101 = 24 bits; 110 = 21

bits.

AUD_MX 0x68:0x31 3:1 0x0 Audio word length Max (corresponding

to channel status bits 32). 0 = maximal

wordlengthis20bits;1=maximalword

lengthis24bits.

Table12AudioinS/PDIFchannelstatusRegisters

Audiostatusoverwriteregistersarelistedintable13.

Name Address Bit Default

Value

Description

OW_CHEN 0x68:2E 0 0x0 Channel status overwrite enable. 0 = no

overwrite to channel status bits; 1 =

channel status bits 2 and 815 are

overwritten with the values in OW_B2

andOW_CHST5

OW_B2 0x68:2E 2 0x0 Channel status Bit 2 overwrite data. This

bit value is used for CHST1 Bit 2 when

OW_CHEN=1.

OW_CHST5 0x68:2F 7:0 0x0 Channelstatusbyte5overwritedata.This

fieldvalueisusedforoverwritingchannel

statusBits[15:8]whenOW_CHENis1.

Table13Audiostatusoverwriteregisters

S-ar putea să vă placă și

- Caixa Acustica PCX6500 Biv. V.ADocument7 paginiCaixa Acustica PCX6500 Biv. V.Aservitec informaticaÎncă nu există evaluări

- Training LG 50pa4500 DM 50pa4510 DJ Chpb23aDocument52 paginiTraining LG 50pa4500 DM 50pa4510 DJ Chpb23aFrancisco AntonioÎncă nu există evaluări

- LG 50pa4500-Sf - Ch. Pb21a PDFDocument48 paginiLG 50pa4500-Sf - Ch. Pb21a PDFJuliano ZanchiÎncă nu există evaluări

- LG 50PB560B Chassis PU41A PDFDocument47 paginiLG 50PB560B Chassis PU41A PDFCesar Guzman100% (1)

- Equivalencia CIs Fontes ChaveadasDocument14 paginiEquivalencia CIs Fontes ChaveadasRobmixÎncă nu există evaluări

- Esquema Elétrico Receptor Orbisat S-2200 Plus IIDocument6 paginiEsquema Elétrico Receptor Orbisat S-2200 Plus IIeletronicagauchoÎncă nu există evaluări

- Philips Chassis Q552.2lla 40pfl7606d 312278519115Document203 paginiPhilips Chassis Q552.2lla 40pfl7606d 312278519115Gaston TolozaÎncă nu există evaluări

- SSC9527SDocument1 paginăSSC9527SJhon Arenas100% (1)

- The Specifications of SW5084B: Details PDFDocument1 paginăThe Specifications of SW5084B: Details PDFArgoÎncă nu există evaluări

- HCD DX9Document70 paginiHCD DX9PALAGUERRA LENIS EVERÎncă nu există evaluări

- Nobreak NhsDocument1 paginăNobreak Nhsatomo33100% (2)

- Monitoare FinalDocument88 paginiMonitoare FinalCiprianIfrimÎncă nu există evaluări

- HV320WHB N10 BoeDocument25 paginiHV320WHB N10 Boechanchaldatta67% (3)

- Lgit LGP55-13PL2 PDFDocument73 paginiLgit LGP55-13PL2 PDFboroda241086% (22)

- Datasheet CM6802Document18 paginiDatasheet CM6802Gilson3DÎncă nu există evaluări

- Service Manual: Mini Component Sound SystemDocument44 paginiService Manual: Mini Component Sound SystemAndres Florentin Pizarro Lazarte100% (1)

- BOE HV280WX2-270 Product Specification Rev. O 20141111Document24 paginiBOE HV280WX2-270 Product Specification Rev. O 20141111abir ahmedÎncă nu există evaluări

- Semp Toshiba Manual de Servico PDFDocument49 paginiSemp Toshiba Manual de Servico PDFAnildo Eldivar De Oliveira SarmentoÎncă nu există evaluări

- TV Led PDFDocument37 paginiTV Led PDFMa RodriguesÎncă nu există evaluări

- Ap 3502 em Regulador DCDC s1005Document11 paginiAp 3502 em Regulador DCDC s1005gerson evandro hanauerÎncă nu există evaluări

- The Transistor Tester User Manual (Newly)Document7 paginiThe Transistor Tester User Manual (Newly)Tanel Laanemägi100% (1)

- 9619 Sony KDL-32BX355 40BX455 46BX45 Chassis AZ3TK Level III Televisor LCD Manual de ServicioDocument32 pagini9619 Sony KDL-32BX355 40BX455 46BX45 Chassis AZ3TK Level III Televisor LCD Manual de ServicioJorge Eliecer Mendoza DucaraÎncă nu există evaluări

- LG 47lm6400Document156 paginiLG 47lm6400Boniface AsuvaÎncă nu există evaluări

- Iw7019 PDFDocument1 paginăIw7019 PDFhectorsevillaÎncă nu există evaluări

- Eax65284601 - Eay628103015Document1 paginăEax65284601 - Eay628103015ies837Încă nu există evaluări

- LSPWM (7R1) 26 03 09Document1 paginăLSPWM (7R1) 26 03 09Ricardo EmilioÎncă nu există evaluări

- Datasheet LD7523 PDFDocument18 paginiDatasheet LD7523 PDFIvica ConićÎncă nu există evaluări

- Sony Bravia KDL LCD TV Error Codes PDFDocument16 paginiSony Bravia KDL LCD TV Error Codes PDFMilton MedinaÎncă nu există evaluări

- Esq Nobreak T0319500 Net SensationDocument1 paginăEsq Nobreak T0319500 Net SensationrenanÎncă nu există evaluări

- Circuito de Controle Do Display TV Samsung Ln-26A330J: (PLACA T-CON V260-B1-C04)Document2 paginiCircuito de Controle Do Display TV Samsung Ln-26A330J: (PLACA T-CON V260-B1-C04)ELECTRONICA J Y CENTRO ELECTRONICO100% (2)

- SSB6 1-SchematicDocument1 paginăSSB6 1-Schematicfox787867% (3)

- PS4 NOR Chip Dumping ProcessDocument8 paginiPS4 NOR Chip Dumping ProcessGabriel Angel Quiroz GonzalezÎncă nu există evaluări

- Guia de FlybackDocument84 paginiGuia de FlybackEulides RomeroÎncă nu există evaluări

- KL5TW1111 American Electrical Inc Product DetailsDocument3 paginiKL5TW1111 American Electrical Inc Product DetailsJeinis Morales0% (1)

- 21FA18-T Service ManualDocument30 pagini21FA18-T Service ManualAnura Maddumage100% (2)

- 42LF20FRDocument28 pagini42LF20FRkanakÎncă nu există evaluări

- D 450Document6 paginiD 450Jose Benavides100% (1)

- Manager Net++Document1 paginăManager Net++Luis SantosÎncă nu există evaluări

- Samsung Bn94-00629q (SCH)Document10 paginiSamsung Bn94-00629q (SCH)gouroukiÎncă nu există evaluări

- Tsum1pfr LFDocument1 paginăTsum1pfr LFanh_sao_dem_92Încă nu există evaluări

- Mini Hi-Fi System: Service ManualDocument85 paginiMini Hi-Fi System: Service Manualthe profeÎncă nu există evaluări

- 9619 Philips Chassis TPM14.1L-LA Televisor LED Manual de Servicio PDFDocument109 pagini9619 Philips Chassis TPM14.1L-LA Televisor LED Manual de Servicio PDFMario Gabriel MoralliÎncă nu există evaluări

- Bit3251 Led 931Document1 paginăBit3251 Led 9319183290782100% (4)

- T ConDocument2 paginiT ConAssis Carneiro100% (1)

- Fuente 32ld874ht PDFDocument13 paginiFuente 32ld874ht PDFies837Încă nu există evaluări

- LSPWM (7R1) 27 11 09Document1 paginăLSPWM (7R1) 27 11 09ShermanFreitasdeLima50% (2)

- Samsung BN44 - 00134ADocument3 paginiSamsung BN44 - 00134APablo Acapulco GuerreroÎncă nu există evaluări

- FUJITSU AMILO 1420 M Service Manual PDFDocument178 paginiFUJITSU AMILO 1420 M Service Manual PDFelprimÎncă nu există evaluări

- Service Manual ForDocument180 paginiService Manual ForAdam TsiolakakisÎncă nu există evaluări

- PCM-9580 Manual Ed.5-469721Document115 paginiPCM-9580 Manual Ed.5-469721Asep SaepudinÎncă nu există evaluări

- Pca-6751man CPUDocument111 paginiPca-6751man CPUquintanacalzadillasjaimeÎncă nu există evaluări

- FC100 200 InstallDocument100 paginiFC100 200 InstallGiurgi CostinÎncă nu există evaluări

- 8050QRDocument121 pagini8050QRcjarekÎncă nu există evaluări

- PCA6751 Manual Ed.4Document111 paginiPCA6751 Manual Ed.4remstan7Încă nu există evaluări

- Nfpik8aa V1.0Document110 paginiNfpik8aa V1.0Ivan MartinezÎncă nu există evaluări

- 8011 Service ManualDocument135 pagini8011 Service Manualserb_71Încă nu există evaluări

- ' LCD TVDocument62 pagini' LCD TVSantiago CandoÎncă nu există evaluări

- PCM 5862EDocument118 paginiPCM 5862EPaulo Henrique ValérioÎncă nu există evaluări

- Cordex CXCIDocument2 paginiCordex CXCIibs434Încă nu există evaluări

- Sony Ge4a Cxa3809am Fa7700n Ba2901sf SCH PDFDocument2 paginiSony Ge4a Cxa3809am Fa7700n Ba2901sf SCH PDFFloricica Victor VasileÎncă nu există evaluări

- Data SheetDocument62 paginiData SheetToni Martin SebéÎncă nu există evaluări

- Tea 6420Document8 paginiTea 6420Floricica Victor VasileÎncă nu există evaluări

- BC 635Document4 paginiBC 635Floricica Victor VasileÎncă nu există evaluări

- Philips Dps-182bp Chassis Lc7.1ala 32pfl5332Document2 paginiPhilips Dps-182bp Chassis Lc7.1ala 32pfl5332takatalvi100% (1)

- ServiceManuals LG TV PLASMA 42PT250 42PT250 Service ManualDocument36 paginiServiceManuals LG TV PLASMA 42PT250 42PT250 Service ManualFloricica Victor Vasile67% (6)

- Audio IC Power Amp AN7112 Typical ApplicationDocument1 paginăAudio IC Power Amp AN7112 Typical ApplicationFloricica Victor VasileÎncă nu există evaluări

- LG 42pj150-Ze Chassis Pd01aDocument35 paginiLG 42pj150-Ze Chassis Pd01aFloricica Victor VasileÎncă nu există evaluări

- LCD TV LG 32lc41-4r 32lc42 32lc43 32lc44 Chassis Lp78aDocument30 paginiLCD TV LG 32lc41-4r 32lc42 32lc43 32lc44 Chassis Lp78aFloricica Victor VasileÎncă nu există evaluări

- Uba 2071Document35 paginiUba 2071Floricica Victor VasileÎncă nu există evaluări

- Beko BKL15LWL03M TFTDocument31 paginiBeko BKL15LWL03M TFTFloricica Victor VasileÎncă nu există evaluări

- PANASONIC TH-46PY85P Chassis GPF11DEDocument154 paginiPANASONIC TH-46PY85P Chassis GPF11DEFloricica Victor VasileÎncă nu există evaluări

- CW29Z68PSG - Chassis K55ADocument84 paginiCW29Z68PSG - Chassis K55AFloricica Victor VasileÎncă nu există evaluări

- Digital Logic Design: Lecture 2 - Number SystemsDocument50 paginiDigital Logic Design: Lecture 2 - Number SystemsMD Sadique AnsariÎncă nu există evaluări

- Intermec 5250 TE2000 Programmers GuideDocument278 paginiIntermec 5250 TE2000 Programmers GuidedjkibÎncă nu există evaluări

- Assembly Language Programming: HandoutsDocument44 paginiAssembly Language Programming: HandoutsAbdullah MuzammilÎncă nu există evaluări

- Supported Visual FoxPro Commands and FunctionsDocument3 paginiSupported Visual FoxPro Commands and FunctionsRafael Nery BritoÎncă nu există evaluări

- IBM System Storage DS8870 Performance With High Performance Flash EnclosureDocument32 paginiIBM System Storage DS8870 Performance With High Performance Flash Enclosureliew99Încă nu există evaluări

- C ProgramsDocument5 paginiC ProgramsLiladhar RewatkarÎncă nu există evaluări

- Chapter 7: How To Install MELSOFT SoftwareDocument17 paginiChapter 7: How To Install MELSOFT SoftwareThương Nguyễn ThanhÎncă nu există evaluări

- Shaheer Pervaiz Masters of Networking and Telecommunication EngineeringDocument34 paginiShaheer Pervaiz Masters of Networking and Telecommunication EngineeringThasleem ReyasÎncă nu există evaluări

- 9608 s17 Ms 12Document7 pagini9608 s17 Ms 12CrustÎncă nu există evaluări

- Ownership Based Cache CoherenceDocument10 paginiOwnership Based Cache CoherenceArunava BiswasÎncă nu există evaluări

- OpenScape Business V2, OpenScape Business S, Installation Guide, Issue 3Document84 paginiOpenScape Business V2, OpenScape Business S, Installation Guide, Issue 3Mostafa SalehiÎncă nu există evaluări

- Unit IDocument7 paginiUnit IHarinath Ramamoorthy100% (1)

- Delta V Course 7009-11Document42 paginiDelta V Course 7009-11Freddy TorresÎncă nu există evaluări

- Computer-Aided Part ProgrammingDocument10 paginiComputer-Aided Part ProgrammingPradip PatelÎncă nu există evaluări

- Indian Legal Advise and Guidelines SystemDocument4 paginiIndian Legal Advise and Guidelines System1000 ProjectsÎncă nu există evaluări

- Lab 2: Installing Prodiscover Basic Edition: What You Need For This ProjectDocument6 paginiLab 2: Installing Prodiscover Basic Edition: What You Need For This ProjectNguyễn Ngọc Bảo LongÎncă nu există evaluări

- Sample EletterDocument2 paginiSample EletterdivakarÎncă nu există evaluări

- NVR 3 Standard Release Notes V3.0.12.42 20160922Document12 paginiNVR 3 Standard Release Notes V3.0.12.42 20160922Diego EndaraÎncă nu există evaluări

- Bob Teal Magnipulsion User ManualDocument90 paginiBob Teal Magnipulsion User Manualmartdot73490Încă nu există evaluări

- Z HMC Operations Guide SC28-6905-01a PDFDocument286 paginiZ HMC Operations Guide SC28-6905-01a PDFShonie MaxwellÎncă nu există evaluări

- Depot 6.99945858Document24 paginiDepot 6.99945858John paul JadaoneÎncă nu există evaluări

- Tivoli and WebSphere Application Server On Z-OS Sg247062Document384 paginiTivoli and WebSphere Application Server On Z-OS Sg247062bupbechanhÎncă nu există evaluări

- Computer Organization and Architecture by William StallingsDocument101 paginiComputer Organization and Architecture by William Stallingsmotumbo motúmbezÎncă nu există evaluări

- Windows 10 and Windows Server 2016 Security Auditing and Monitoring ReferenceDocument757 paginiWindows 10 and Windows Server 2016 Security Auditing and Monitoring Referencejinish.K.GÎncă nu există evaluări

- DMX 6fire Usb Manual enDocument42 paginiDMX 6fire Usb Manual endavitunesÎncă nu există evaluări

- Introduction To ZTE ZXUR9000 v4RNC and DimensioningDocument20 paginiIntroduction To ZTE ZXUR9000 v4RNC and Dimensioningbob_mirkÎncă nu există evaluări

- Livelink WCM 9.5 SystemIntegration - enDocument213 paginiLivelink WCM 9.5 SystemIntegration - enRaghu ReddyÎncă nu există evaluări

- Wireless N300 Multi-WAN Router: Product HighlightsDocument3 paginiWireless N300 Multi-WAN Router: Product HighlightsL. VÎncă nu există evaluări

- Arduino-TempHumidity-with-LCD-And-Web-Interface ALLSTEPSDocument12 paginiArduino-TempHumidity-with-LCD-And-Web-Interface ALLSTEPSKurniawan SusiloÎncă nu există evaluări

- FactoryTalk Optix OnCourseDocument180 paginiFactoryTalk Optix OnCourseAbid Hossain RupamÎncă nu există evaluări