Documente Academic

Documente Profesional

Documente Cultură

8.1 Mux 1

Încărcat de

Maddy TrichyTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

8.1 Mux 1

Încărcat de

Maddy TrichyDrepturi de autor:

Formate disponibile

11/14/2014

Design of 8 : 1 Multiplexer Using When-Else Statement (VHDL Code). ~ VHDL Programming

Search

VHDL Programming

Learn All about VHDL Programming with Naresh Singh Dobal.

HOME

VHDL PROGRAMS

PROJECTS

TUTORIALS

ASSIGNMENTS

ABOUT US

CONTACT US

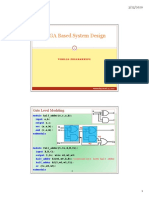

Design of 8 : 1 Multiplexer Using When-Else

Statement (VHDL Code).

Verilog HDL

Find US on FaceBook

Like

VHDL DESIGN

11:30

naresh.dobal

Search Here

Search

2 comments

Recommend this on Google

Share 28,303 people like this.

Design of 8 : 1

Multiplexer Using When-Else Concurrent Statement (Data

Flow Modeling Style)-

TESTIMONIAL

Current Time

07:01:40 am

Total Pageviews

Share

284,426

View stats

Email Subscribe

Email address...

Followers

Submit

Join this site

w ith Google Friend Connect

Members (27) More

Naresh Singh Dobal.

Powered by Blogger.

About Me

Output Waveform : 8 : 1 Multiplexer

NARES H. DOBAL

VHDL Code-

NOI DA, UT T AR

P RADES H, I NDI A

V IE W M Y COM P LE TE

P ROF ILE

Live Traffic Feeds...

Already a member? Sign in

Archives

--------------------------------------------------------------------------------- Title

: multiplexer8_1

-- Design

: vhdl_test

-- Author

: Naresh Singh Dobal

-- Company : nsd

---------------------------------------------------------------------------------- File

: 8 : 1 multiplexer using when else.vhd

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity multiplexer8_1 is

port(

din : in STD_LOGIC_VECTOR(7 downto 0);

sel : in STD_LOGIC_VECTOR(2 downto 0);

dout : out STD_LOGIC

);

end multiplexer8_1;

architecture multiplexer8_1_arc of multiplexer8_1 is

http://vhdlbynaresh.blogspot.in/2013/07/design-of-8-1-multiplexer-using-when.html

2014 ( 3 )

2013 ( 133 )

November ( 12 )

October ( 5 )

July ( 116 )

The Three Basic

Element inside a

Computer Chip

Let's start with making

a Semiconductor

Chip

Let's know about our

Semiconductor

Industry

Computer Chips are

EveryWhere

(Application of Elec...

Very Important

ACRONYMS &

TERMS of

Semicondutor In...

Electronics - Trends

Setting Points

World of Integrated

1/6

11/14/2014

Design of 8 : 1 Multiplexer Using When-Else Statement (VHDL Code). ~ VHDL Programming

Live Traffic Feed

Chips AND

Electronic Design.

begin

Design of 8 : 3 Priority

Encoder using

std_matc...

dout <= din(7) when (sel="000") else

din(6) when (sel="001") else

A visitor from Trichy, Tamil Nadu

din(5) when (sel="010") else

viewed "Design of 8 : 1

din(4) when (sel="011") else

Multiplexer Using When-Else

din(3) when (sel="100") else

Statement (VHDL Code). ~

A

visitorProgramming"

from Ghaziabad,

Uttarago

din(2) when (sel="101") else

VHDL

33 secs

Pradesh viewed "Design of SR

din(1) when (sel="110") else

Flip Flop using Behavior Modeling

din(0);

Style (VHDL Code). ~ VHDL

A

visitor from Delhi

Programming"

7 minsviewed

ago

end multiplexer8_1_arc;

"Design of 4 to 2 Encoder using

CASE Statements (VHDL Code).

~ VHDL

Programming"

15 mins

A

visitor from

Milwaukee,

New er Post

Home

ago

Wisconsin

left "Design of 8 : 3

Priority Encoder using if - else 2 comments :

statements - Method 1 (VHDL

Code).

VHDL

Programming

A visitor~from

Milwaukee,

Anonymous said...

via

1.bp.blogspot.com

15 mins

Wisconsin viewed "Design

of 8 : 3

Can you provide a structural domain programming of this 8x1 Mux

ago

Priority Encoder using if - else

mail to saurabh_pati@yahoo.com if possible

statements - Method 1 (VHDL

Code).

VHDL

Programming

A visitor~from

Tlalnepantla,

6 March 2014 19:29

15 mins viewed

ago

Mexico

"Design of 4 Bit

Adder cum Subtractor using

Anonymous said...

Structural Modeling Style (VHDL

Code).

VHDL

Programming

A

visitor~from

Bangalore,

thank you... :)

25 mins agoleft "VHDL Lab

Karnataka

8 October 2014 16:21

Exercise ::: Exercise 4 ~ VHDL

Programming" via

A visitor from Bangalore,

3.bp.blogspot.com 35 mins ago Post a Comment

Karnataka viewed "VHDL Lab

Exercise ::: Exercise 4 ~ VHDL

Programming" 36 mins ago

A visitor from Manipal, Karnataka

Enter your comment...

viewed "Design of 8 : 3 Priority

Encoder using if - else statements Method 1 (VHDL Code). ~

VHDL

40 mins

A

visitorProgramming"

from Ghaziabad,

Uttarago

Comment as: Google Account

Pradesh viewed "Design of SR

Flip Flop using Behavior Modeling

Style (VHDL Code). ~ VHDL

Publish

Preview

Real-time view Menu

Design of 8 : 3 Priority

Encoder using if else ...

Design of 8 : 3 Priority

Encoder using

std_match ...

Design of 8 to 3 Priority

Encoder using When

Else ...

Older Post

Design of 8 nibble

Queue using

Behavior Modeling

S...

Design of Parallel In Serial OUT Shift

Register ...

System Design using

Loop Statements

(Behavior Mode...

Sample Programs for

Basic Systems using

VHDL

Design of 4 Bit Adder

cum Subtractor using

Loops (...

Design of 4 Bit

Subtractor using

Loops (Behavior M...

Design of 4 Bit Adder

using Loops

(Behavior Modeli...

Design of Stepper Motor

Driver (Half Step)

using B...

Design of Stepper Motor

Driver (Full Step)

using B...

Design of ODD number

Frequency Divider

using Behav...

Design of 8 - nibble

stack using Behavior

Modeling...

YouTube Projects

Design of First IN - Last

OUT (FILO) Register

usin...

Popular Posts

Design of First IN - First

OUT (FIFO) Register

usi...

Design of 3 :

8 Decoder

Using WhenElse

Statement

(VHDL Code).

Design of 3 : 8 Decoder

Using When - Else

Statement (Data Flow

Modeling Style)- Output

Waveform : 3 : 8 Decoder

VHDL Code- --...

Design of JK

Flip Flop

using

Behavior

http://vhdlbynaresh.blogspot.in/2013/07/design-of-8-1-multiplexer-using-when.html

Design of 8 nibble RAM

(Memory) using

Behavior Mod...

Design of 8 Nibble ROM

(Memory) using

Behavior Mod...

Sensor Based Traffic

Light Controller using

FSM Te...

Timer Based Single

Way Traffic Light

Controller us...

Design of ODD Counter

using FSM

2/6

11/14/2014

Design of 8 : 1 Multiplexer Using When-Else Statement (VHDL Code). ~ VHDL Programming

Modeling

Style (VHDL Code).

Design of JK Flip Flop using

Behavior Modeling Style Output Waveform : JK Flip

Flop VHDL Code - -----------------...

Design of 4

to 1

Multiplexer

using if-else

statement

(VHDL Code).

Design of 4 to 1 Multiplexer

using if - else statement

(Behavior Modeling Style)Output Waveform : 4 to 1

Multiplexer VHDL...

Design of 4

Bit Adder

using 4 Full

Adder (Structural

Modeling Style) (VHDL

Code).

Design of 4 Bit Adder using

4 Full Adder (Structural

Modeling Style)- Output

Waveform : 4 Bit Adder

using 4 Full Adder V...

Design of 8 :

1 Multiplexer

Using WhenElse

Statement

(VHDL Code).

Design of 8 : 1 Multiplexer

Using When-Else Concurrent

Statement (Data Flow

Modeling Style)- Output

Waveform : 8 : 1 Multiplexer

V...

Design of 1

to 4

Demultiplexer using CASE

Statements (VHDL Code).

Design of 1 to 4

Demultiplexer using CASE

Statements (Behavior

Modeling Style). Output

Waveform : 1 to 4

Demultiplexer VHD...

Full

Subtractor

Design using

Logical

Gates (VHDL

Code).

Full Subtractor Design using

Logical Gates (VHDL Code) Output Waveform : Full

Subtractor Program- ---------------------------...

Small Description about

Data Flow Modelling Style

in VHDL.

Data flow modeling style

Data flow modeling style

shows how the data flow

from input to output threw

the registers / components...

Technique. (VHDL

C...

Design of Frequency

Dividers in VHDL.

Design of Frequency

Divider (Divide by 10)

using B...

Design of Frequency

Divider (Divide by 8)

using Be...

Design of Frequency

Divider (Divide by 4)

using Be...

Design of Frequency

Divider Module

(Divide by 2) u...

Design of MOD-6

Counter using

Behavior Modeling

St...

Design of BCD Counter

using Behavior

Modeling Styl...

Design of Integer

counter using

Behavior Modeling ...

Design of 4 Bit Binary

Counter using

Behavior Mode...

Counters Design in

VHDL.

Design of 2 Bit Binary

Counter using

Behavior Mode...

How to use CASE

Statements in

Behavior Modeling ...

How to use IF-ELSE

Statements in

Behvaior Modeling...

Design of a Simple

numbers based

Grading System us...

Design of SR - Latch

using Behavior

Modeling Style...

Design of D-Latch using

Behavior Modeling

Style (V...

Design of Toggle Flip

Flop using Behavior

Modeling...

Design of JK Flip Flop

using Behavior

Modeling Sty...

Design of SR Flip Flop

using Behavior

Modeling St...

Design of D Flip Flop

Using Behavior

Modeling Styl...

Design of 4 Bit Parallel

IN - Parallel OUT

Shift...

Design of 4 Bit Serial IN

- Parallel OUT Shift

Reg...

Design of 4 Bit

http://vhdlbynaresh.blogspot.in/2013/07/design-of-8-1-multiplexer-using-when.html

3/6

11/14/2014

Design of 8 : 1 Multiplexer Using When-Else Statement (VHDL Code). ~ VHDL Programming

Comparator

using IFELSE

Statements

(VHDL Code).

Design of 4 Bit Comparator

using IF-ELSE Statements

(Behavior Modeling Style) Output Waveform : 4 Bit

Comparator VHDL ...

Design of 1 :

8

Demultiplexer Using

When-Else (VHDL Code).

Design of 1 : 8 Demultiplexer

Using When - Else

Concurrent Statement (Data

Flow Modeling Style)- Output

Waveform : 1 : 8

Demultiplexer ...

Design of 4 bit Serial IN

- Serial OUT Shift

Regis...

Design of BCD to 7

Segment Driver for

Common Catho...

Design of BCD to 7

Segment Driver for

Common Anode...

Design of GRAY to

Binary Code

Converter using

CASE...

Design of BINARY to

GRAY Code

Converter using

CASE...

Design of GRAY to

BINARY Code

Converter using IFE...

Design of Binary To

GRAY Code

Converter using IFE...

Design of 4 Bit

Comparator using IFELSE Statement...

Design of 2 to 4

Decoder using CASE

Statements (VH...

Design of 4 to 2

Encoder using CASE

Statements (V...

Design of 1 to 4

Demultiplexer using

CASE Statemen...

Design of 4 to 1

Multiplexer using

CASE Statement ...

Design of 2 to 4

Decoder using IFELSE Statement (...

Design of 4 to 2

Encoder using IFELSE Statement...

Design of 1 to 4

Demultiplexer using

IF-ELSE State...

Design of 4 to 1

Multiplexer using ifelse stateme...

Small Description about

Behavior Modeling

Style

FPGA / CPLD Based

Project.

Simulation Based

Projects (VHDL)

Project List (VHDL &

FPGA Projects)

Modeling Styles in

VHDL

Design of Parallel IN Parallel OUT Shift

Regist...

Design of Serial In Parallel Out Shift

http://vhdlbynaresh.blogspot.in/2013/07/design-of-8-1-multiplexer-using-when.html

4/6

11/14/2014

Design of 8 : 1 Multiplexer Using When-Else Statement (VHDL Code). ~ VHDL Programming

Register ...

Design of Serial IN Serial Out Shift

Register u...

Design of Toggle Flip

Flop using J-K Flip

Flop (VH...

Design of Master Slave Flip Flop using

D- Flip F...

Design of Toggle Flip

Flop using D-Flip

Flop (VHDL...

Design of 4 Bit Adder /

Subtractor using XOR

Gate ...

Design of 4 Bit Adder

cum Subtractor using

Structu...

Design of 4 Bit

Subtractor using

Structural Modeli...

Design of 4 Bit Adder

using 4 Full Adder (Struct...

Design of 2 to 1

Multiplexer using

Structural Mode...

How to write Codes in

Structural Modeling

Style in...

Small Description about

Structural Modeling

Style ...

Design of BCD to 7Segment Driver For

Common Anode...

Design of 2 Bit

Comparator Using

When-Else

Stateme...

Design of 3 : 8 Decoder

Using When-Else

Statement ...

Design of 8 : 3 Encoder

using When - Else

Statemen...

Design of 1 : 8

Demultiplexer Using

When-Else (VHD...

Design of 8 : 1

Multiplexer Using

When-Else Statem...

Design of BCD to 7

Segment Driver for

Common Anode...

WHEN - ELSE

Concurrent

Statement (Data

Flow ...

with-select concurrent

statement (Data Flow

Modeli...

Design of BCD to 7

Segment Driver for

Common Katho...

Design of Binary to

Excess3 Code

http://vhdlbynaresh.blogspot.in/2013/07/design-of-8-1-multiplexer-using-when.html

5/6

11/14/2014

Design of 8 : 1 Multiplexer Using When-Else Statement (VHDL Code). ~ VHDL Programming

Converter using w...

Design of 2 : 4 Decoder

using With-Select

Concurre...

Design of 4 : 2 Encoder

using with-select

Concurre...

Design of 1 : 4

Demultiplexer using

with-select Co...

Design of 4 : 1

Multiplexer using

With-Select Conc...

Design of Gray to

Binary Code

Converter using

Logi...

Binary To Gray Code

Converter using

Logical Expres...

Design of 1 Bit

Comparator using

Logical Gates (VH...

Full Subtractor Design

using Logical Gates

(VHDL C...

Half Subtractor Design

using Logical

Expression (V...

4 : 2 Encoder using

Logical Gates (VHDL

Code).

Digital System Design

using Logical

Expression (VH...

Digital System Design

using with-select

Concurrent...

2 : 4 Decoder using

Logical GATES

(VHDL Code).

1:4 Demultiplexer

Design using Gates

(VHDL Code).

4 to 1 Multiplexer

Design using Logical

Expression...

Small Description about

Data Flow Modelling

Style ...

Full Adder Design using

Logical Expression

(VHDL C...

Half Adder Design using

Logical Expressions

(VHDL ...

Logical Operators test

in VHDL Design

Simple AND Gate

design using VHDL

Copyright 2011 VHDL Programming | Powered by Blogger

Design by Wordpress Theme | Bloggerized by Free Blogger Templates | coupon codes

http://vhdlbynaresh.blogspot.in/2013/07/design-of-8-1-multiplexer-using-when.html

6/6

S-ar putea să vă placă și

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (895)

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (345)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (121)

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (74)

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- VHDL - 1100 Sequence Detector - Electrical Engineering Stack ExchangeDocument3 paginiVHDL - 1100 Sequence Detector - Electrical Engineering Stack ExchangeMaddy TrichyÎncă nu există evaluări

- ALU 4 Bit VerilogDocument11 paginiALU 4 Bit Verilognhungdieubatchot100% (1)

- Question Papper Code: 11332: B.E./B.Tech. Degree Examination, May/June 2012 Fifth SemesterDocument3 paginiQuestion Papper Code: 11332: B.E./B.Tech. Degree Examination, May/June 2012 Fifth SemesterMaddy TrichyÎncă nu există evaluări

- FIR Filters and Convolution ExampleDocument2 paginiFIR Filters and Convolution ExampleMaddy TrichyÎncă nu există evaluări

- 8051 Programs With OpcodeDocument80 pagini8051 Programs With OpcodeMaddy Trichy100% (4)

- 8.1 Mux 2Document4 pagini8.1 Mux 2Maddy TrichyÎncă nu există evaluări

- Design of Adders, Subtractors, BCD Adders Week6 and 7 - Lecture 2Document60 paginiDesign of Adders, Subtractors, BCD Adders Week6 and 7 - Lecture 2Gursheel SinghÎncă nu există evaluări

- Delay, Power Performance of 8-Bit ALU Using Carry Look-Ahead Adder With High VT CellDocument9 paginiDelay, Power Performance of 8-Bit ALU Using Carry Look-Ahead Adder With High VT CellIJRASETPublicationsÎncă nu există evaluări

- ECE 2003 ManualDocument79 paginiECE 2003 Manualannambaka satishÎncă nu există evaluări

- Cse1003 DLD LabDocument14 paginiCse1003 DLD LabPranav Chaurasia 18BCE0216Încă nu există evaluări

- Adc Lab Manual PDFDocument74 paginiAdc Lab Manual PDFJega Deesan75% (4)

- FPGA Based System Design: Gate Level ModelingDocument11 paginiFPGA Based System Design: Gate Level Modelingwaleed umerÎncă nu există evaluări

- Digital Questions ObjectiveDocument22 paginiDigital Questions ObjectiveSathiya GunasekaranÎncă nu există evaluări

- Lab Manual EC1010 Digital Systems LabDocument51 paginiLab Manual EC1010 Digital Systems Labsudipta2580Încă nu există evaluări

- DLC LAB - 08 - Student - ManualDocument10 paginiDLC LAB - 08 - Student - ManualImtiaj SajinÎncă nu există evaluări

- Register Transfer LanguageDocument11 paginiRegister Transfer LanguageShiva IdokÎncă nu există evaluări

- 08 CA (Constructing+an+ALU)Document17 pagini08 CA (Constructing+an+ALU)Royal StarsÎncă nu există evaluări

- EC6601-VLSI Design QBDocument11 paginiEC6601-VLSI Design QBThahsin ThahirÎncă nu există evaluări

- Altes00365 1Document57 paginiAltes00365 1abhiÎncă nu există evaluări

- IC 74 FamilyDocument12 paginiIC 74 FamilyFlavio Cabrera-MoraÎncă nu există evaluări

- CS8351-Digital Principles and System Design PDFDocument16 paginiCS8351-Digital Principles and System Design PDFJabeen BanuÎncă nu există evaluări

- Objective Questions. Topic: Number System and CodesDocument56 paginiObjective Questions. Topic: Number System and Codesthejareddy14Încă nu există evaluări

- Digital Electronics Lab EE-224-FDocument48 paginiDigital Electronics Lab EE-224-FIshwar Singh ChandraÎncă nu există evaluări

- CS302 Mcqs MidTerm by Vu Topper RMDocument47 paginiCS302 Mcqs MidTerm by Vu Topper RMBukhari SyedÎncă nu există evaluări

- Digital Systems Lab ManualDocument63 paginiDigital Systems Lab Manualinfant199218Încă nu există evaluări

- Digital Electronics Lab ManualDocument111 paginiDigital Electronics Lab ManualmuraliÎncă nu există evaluări

- Lab 3 Manual (At Zachry)Document6 paginiLab 3 Manual (At Zachry)jamesÎncă nu există evaluări

- Experiment - 3 Design and Simulation of Four-Bit Ripple Carry AdderDocument18 paginiExperiment - 3 Design and Simulation of Four-Bit Ripple Carry AdderUnlimited XfinityÎncă nu există evaluări

- Combinational Logic CircuitsDocument17 paginiCombinational Logic CircuitsAdarsha Bhattarai100% (1)

- Computer Organisation and ArchitectureDocument2 paginiComputer Organisation and ArchitectureRavi VenkatesanÎncă nu există evaluări

- Simplification of Boolean Functions: 1-Two - Variable K-MapDocument22 paginiSimplification of Boolean Functions: 1-Two - Variable K-MapWikiÎncă nu există evaluări

- DLD Lab 4Document12 paginiDLD Lab 4گيدوڙو ماڇيÎncă nu există evaluări

- VHDL Implementation of Arithmetic Logic Unit: April 2014Document9 paginiVHDL Implementation of Arithmetic Logic Unit: April 2014ammarÎncă nu există evaluări

- CH4 Combinational LogicDocument69 paginiCH4 Combinational LogicmahmudulÎncă nu există evaluări

- Digital. PPT - Chapter 4Document40 paginiDigital. PPT - Chapter 4JenberÎncă nu există evaluări