Documente Academic

Documente Profesional

Documente Cultură

Bulban Lucrarev

Încărcat de

Valik1708Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Bulban Lucrarev

Încărcat de

Valik1708Drepturi de autor:

Formate disponibile

UTM 525.

1 101 16

Mod Coala

Nr. docum.

Elaborat

Bulan Dan

Verificat

Nastas V.

Contr. t.

Semnat.

Data

Litera

Proiectarea unui sistem pe baza

microprocesorului Intel 8086

STAS

Coala

Coli

27

UTM FIMET TLC-122

Aprobat

CUPRINS

Introducere..................................................................................................................................2

Proiectarea procesorului..............................................................................................................5

Generatorul de sistem.................................................................................................................9

Circuitul de formare a semnalului.........................................................................................10

Proiectarea magistralei..........................................................................................................11

Controlerele cu magistralele i controlere de system............................................................11

Proiectarea dispozitivelor de memorie ale sistemelor de baz de microprocessor...................14

Memoria dinamic K565P5...............................................................................................17

Microcircuitul K573P4......................................................................................................19

Proiectarea unitii de intrare/iesire......................................................................................21

Proiectarea tastaturii..............................................................................................................24

CONCLUZII.............................................................................................................................25

UTM 525.1 101 16 ME

Mod Coala

Nr. docum.

Semnat.

Data

Introducere

Conducerea numeric a proceselor industriale a cptat astzi valene noi, atat ca

urmare a evoluiei conceptului de conducere, cat mai ales ca urmare a evoluiei tehnologiei

circuitelor integrate pe scar larg (LSI) i pe scar foarte larg (VLSI), a microprocesoarelor,

microcalculatoarelor i a minicalculatoarelor. Astfel, conceptele moderne privind conducerea

proceselor, concretizate n clase largi de algoritmi de reglare i conducere, devin operaionale i

eficiente ca urmare a dezvoltrii instruciunilor hardware cat i microprocesoarelor pe care sunt

implementate cu performane deosebite.

Progresele obinute in domeniul sistemelor de interfa cu procesele industriale, al

sistemelor de achiziie de date, de conversie i prelucrare primar, precum i al sistemelor de

acionare au permis extinderea domeniilor de utilizare a tehnicii de calcul numeric in

conducerea proceselor industriale.

inand seama de diversitatea proceselor, de gradul de complexitate al acestora, de cerinele

de performan impuse sistemelor de conducere, de gradul de cunoatere al acestora, au fost

dezvoltate i implementate structuri de sisteme de conducere cu grade diferite de complexitate

compatibile atat cu probleme relativ simple privind reglarea numeric a proceselor, cat i cu

probleme complexe ale conducerii proceselor dup criterii globale de performan.

Dezvoltrile in tehnologia calculatoarelor in ultimii ani cu consecine deosebite in

creterea performanelor (viteza de prelucrare, capacitatea de memorare, fiabilitate), reducerea

spectaculoas a costului precum i elaborarea de programe orientate au contribuit la

realizarea unor sisteme de microcalculatoare i minicalculatoare destinate rezolvrii

problemelor de conducere in timp real a proceselor industriale.

Structurile hardware organizate in jurul microprocesoarelor de 8 bii, 16 bii i 32 bii au

deschis noi direcii pentru realizarea unor structuri moderne de sisteme de conducere. Astfel, s-au

impus structurile de sisteme de conducere distribuit inclusiv achiziie distribuit a datelor

din proces, precum i structurile ierarhizate de conducere, in cadrul crora fiecrui

echipament ii revin sarcini in concordan cu poziia ocupat in ierarhie.

Asemenea arhitecturi de sisteme distribuite i ierarhizate sunt caracterizate printr-o limit a

flexibilitii i fiabilitii, prin performane superioare, determinate de puterea de calcul,

Coala

UTM 525.1 101 16 ME

Mod Coala

Nr. docum.

Semnat.

Data

viteza de prelucrare i de clasele de algoritmi evoluai ce pot fi implementai, in comparaie cu

structurile de conducere centralizat cu calculator de proces.

Structurile moderne de conducere distribuit i ierarhizat, reprezentand gradul de

inteligen la diferite echipamente de prelucrare numeric, asigur prin resursele hardware i

software o conducere eficient a proceselor i o integrare puternic a operatorului in sistem

prin interaciunea om-main indus ca funcie a sistemului integrat de conducere. In funcie de

complexitatea procesului, de complexitatea funciilor de conducere concrete, a performanelor,

echipamentelor hardware pot fi organizate in structuri de conducere ierarhizate multistrat

(multilayer control hierarchy), structuri de conducere multinivel (multilevel control hierarchy)

structuri de conducere multistrat temporale (temporal multilayer control hierarchy). Conducerea

ierarhizat multistrat caracterizeaz o ierarhizare funcional pe diverse straturi, pe. cand

conducerea ierarhizat multinivel presupune o ierarhizare structural cu implementarea

diverselor funcii pe diferite echipamente organizate pe mai multe nivele ierarhice.

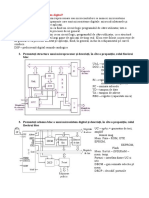

Mai jos este prezentat o structur a unui sistem cu microprocesor.

Fig.1 Structura unui sistem cu microprocesor

Unitatea central de prelucrare implementat sub forma unui chip microprocesor, este piesa

central a oricrui sistem de calcul. CPU realezeaz prelucrri numerice.

Registrele reprezint locaii de memorie temporare aflate n interiorul CPU. Registrele snt fie

dedicate (program counter, status register), fie generale.

Unitatea logico-aritmetic este unitatea care realizeaz prelucrarea efectiv a datelor. Operaiile

Coala

UTM 525.1 101 16 ME

Mod Coala

Nr. docum.

Semnat.

Data

realizate de ALU snt fie logice (operanzi interpretai ca o mulime de bii), fie aritmetice (operanzi

interpretai ca numere exprimate n baza doi).

Calea de control coordoneaz activitatea microprocesorului i realezeaz secvenialitatea execuiei

programelor. Circuitele din calea de control decodific instruciunea i lanseaz comenzi pentru

unitile interne i externe n scopul executrii acesteia.

Memoria nmagazineaz programele i datele. Programul de iniializare i gestionare a resurselor

sistemului (monitor, sistem de operare) este meninut ntr-o memorie ROM. Restul spaiului de

memorie este ocupat de memorie RAM.

Dispozitivele de intrare/ieire denumite i periferice, reprezint mijloacele de comunicare ale

microprocesorului cu lumea exterioar. Tastatura, monitorul sau imprimanta snt controlate de ctre

CPU prin intermediul porturilor de intrare/ieire.

Magistralele de adrese, date i control interconecteaz unitatea central cu memoria i

dispozitivele I/O. Pe bus-ul de date se transfer bidirecional informaii codificate binar, interpretate

ca date sau ca instruciuni. Bus-ul de adrese unidirecional este folosit de CPU pentru a transmite

adrese ctre memorie i dispozitive I/O. Pe bus-ul de control se transmit comenzi de la CPU spre

memorie si spre dispozitivele I/O.

ntreruperile snt situaii n care microprocesorul i suspend execuia secvenial a programului

pentru a deservi apelul venit de la un periferic. De obicei, ntr-un sistem exist mai multe

dispozitive care pot lansa cereri de ntreruperi. Pentru a putea fi servite toate, ntreruperile trebuie

ierarhizate prin asocierea unor prioriti.

Accesul direct la memorie (Direct Memory Access - DMA) reprezint o soluie de transfer rapid

a datelor de la un periferic n memorie fr ca acestea s mai treac prin microprocesor.

Prin utilizarea DMA, CPU pred controlul magistralelor ctre un dispozitiv periferic care

controleaz transferarea datelor direct n memoria sistemului.

Modurile de adresare reprezint totalitatea modalitilor de determinare a adreselor pentru

accesarea memoriei externe

Coala

UTM 525.1 101 16 ME

Mod Coala

Nr. docum.

Semnat.

Data

Proiectarea procesorului

Spaiul de adresare a MP K1810 const din spaiul memoriei, porturilor i memoria

superoperativ. Spaiul de adresare a memoriei volumul total 1 MB este segmentat i are

organizarea logic 1 M*8. Fiecare segment are volumul pn la 64 KB i se adreseaz cu adresa de

16 bii care indic poziia celulei adresate fa de nceputul segmentului. Poziia segmentului n

memorie este indicat cu adresa de 20 bii, 16 dintre care sunt adresa segmentului i 4 poziii

inferioare nule. Segmentele sunt amplasate cu pasul 24=16B n oricare loc a memoriei n vecintate

la distan, intercalndu-se total sau parial. Adresa cu 20 de poziii se formeaz prin nsumarea a

adresei segmentului de 20 bii cu cei 16 bii a adresei n segment. n fiecare moment curent de timp

procesorul pstreaz adresa a 4 segmentecomenzi, stivei i a 2 segmente de date. Pentru accesul

la alte segmente este necesar schimbarea adresei prin intermediului programului. Dou regiuni ale

spaiului de memorie situate n cei mai inferiori 1 KB (00000...003FF) i cei mai superiori 16B

(FFFF0...FFFFF) se utilizeaz pentru tratarea ntrerupelor i a iniializrii sistemului corespunztor.

Cuvintele n memorie se aranjeaz n ordinea creterii biilor: baitul inferior la adresa inferioar,

baitul superiorla adresa superioar.

Organizarea fizic a spaiului de memorie i dispozitivelor externe este analogic

organizrii logice.

Memoria superoperativ a procesorului K1810 formeaz un masiv de registre

cu volumul 14*16bii. toate registrele sunt adresate cu un cod de 3 bii. registrele date ndeplinesc

funcii speciale i sunt adresate involuntar.

Adresarea memoriei de ctre microprocesoarelor K1810 se realizeaz cu dou adrese

logice de 16 bii: adresa n segment i adresa segmentului. Metoda de determinare a adresei depinde

de tipul segmentului i tipul datelor adresate (figura 1). Instruciunile se aleg din segmentul

instruciunilor i adresa se determin de coninutul registrului CS. nceputul adresei (adresa iniial)

este adresa din registru indicator IP care se determin din simpla adresare.

Datele pot fi amplasate n orice segment. De obicei ele sunt situate n segmentul datelor

adresat de ctre registrul DS. Tabelele i constantele este comod de a stoca n segmentul

instruciunilor. Parametrii subprogramului i alte date incluse n stiv se amplaseaz n segmentul

stivei. Dac la determinarea adresei se folosete registrul BP, datele se pstreaz n segmentul curent

al stivei, adresat de registru SS. Pentru adresarea dispozitivelor periferice, situate n regiunea

adreselor dispozitivelor periferice se folosete adresarea de registre direct i indirect. La

adresarea direct, adresa dispozitivului periferic este 8 bii ce permite adresarea a 256 dispozitive.

Mai jos este prezentat destinaia pinilor a MP K1810BM88.

Coala

UTM 525.1 101 16 ME

Mod Coala

Nr. docum.

Semnat.

Data

Fig.1. Destinaia terminalelor MP K1810BM86 n regim minimal

La adresarea indirect adresa dispozitivului extern este amplasat n registrul DX ce permite

adresarea a 65536 dispozitive. Adresarea dispozitivelor periferice situate n spaiul dispozitivelor de

memorie se realizeaz cu utilizarea metodelor de adresare n memorie. Structura microprocesorului

K1810BM86 conine dou dispozitive funcionale independente: dispozitivul de prelucrare i

dispozitivul de joncionare. Dispozitivul de prelucrare (ALU, RDG, RAM, superoperativ, registrul

fanioanelor) ndeplinete operaii asupra datelor i determin adresele funcionale din memorie.

Dispozitivul primete datele sau adresele de la magistral intern, le prelucreaz, iar rezultatul l

pstreaz n RAM superoperativ sau pe magistrala intern. Dispozitivul de joncionare (sumatorul

de adrese SMA, registrele segmentelor) determin adresele fizice a memoriei, alege i aeaz n

irul instruciunile, realizeaz schimbul de date ntre magistral intern i cea extern, formeaz

Coala

UTM 525.1 101 16 ME

Mod Coala

Nr. docum.

Semnat.

Data

semnalele la ieirile magistralei externe. Destinaia pinilor a MP K1810BM86 este prezentat mai

jos:

Fig.2. Destinaia pinilor MP K1810BM86

Coala

UTM 525.1 101 16 ME

Mod Coala

Nr. docum.

Semnat.

Data

Fig.3. Arhitectura MP K1810BM86

Ambele dispozitive lucreaz paralel, datorit acestui fapt alegerea i realizarea instruciunilor este

corelat n timp. Corelarea nu se realizeaz dac irul este ncrcat (la 3/4), se realizeaz

instruciunile sau este cererea pentru schimb de date de la magistrala extern. Lungimea irului

instruciunilor pentru I8086 este de 4B.

Destinaia terminalelor microprocesorului K1810BM86 n dependen de regimul de funcionare (n

cazul dat minim) este reprezentat n figura 1:

Linia tristabil de alegere a bancului superior a memoriei/dispozitivului periferic;

Magistrala tristabil de 4 bii de adrese/stri A19...A16/ST6...ST3;

Magistrala de 16 bii de adrese/date AD15...ADO;

Linii de comand cu interfa de sistemstrobul de adrese STB utilizat pentru nscrierea

adreselor n registrul de adrese extern;

Coala

UTM 525.1 101 16 ME

Mod Coala

Nr. docum.

Semnat.

Data

Linia tristabil de permitere DE i direcia de transmitere OPIP a formatoarelor de

magistral de date;

Linia de comand tristabil IO/Malegerea IO sau M;

Citire RD;

nscriere WR;

Linie de comand tristabil cu controlerele externe de deservire a ntreruperilor INTA;

Codul format de combinaia semnalelor SSTO, IO/M, OP/IP indic 8 stri de funcionare a

magistralei de sistem. Acest cod poate fi utilizat de circuitele externe pentru formarea semnalelor

de comand. Microprocesorul are ieiri aparte a magistralei de adrese de 8 bii A15...A8 i

magistral multiplexat tristabil de adrese/date AO7...ADO. Ieirea de adrese ale registrelor de

segment la terminalele ST3, ST4 permite de a lrgi spaiul de adresare a memorie pn la 4 MB,

utiliznd pentru fiecare segment memorie aparte cu volum 1MB.

Regimul de oprire are loc la terminarea executrii programului, dup instruciunea HLT

procesorul nceteaz citirea instruciunilor i executarea lor. n acest caz n regim minimal apare un

semnal la ieirea STB la ieirile ST2...ST0. n acest regim procesorul nu genereaz nici un semnal

de comand. Din regimul de oprire microprocesorul poate fi scos cu semnalul RESET sau semnalul

de ntrerupere la intrare INT.

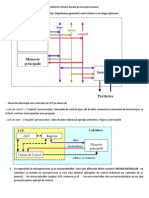

n figura urmtoare este prezentat harta memoriei principale la microprocesorul Intel 8086.

Coala

UTM 525.1 101 16 ME

Mod Coala

Nr. docum.

Semnat.

Data

Fig.4 Harta memoriei principale ale microprocesorului Intel 8086

Generatorul de sistem

Generatorul de sistem KP181084 este destinat dirijrii microproce-soarelor

KP1810BM86/88 i dispozitivelor periferice, de asemenea pentru sincronizarea semnalelor READY

cu semnalele de tact ale microprocesorului i semnalelor magistralei interfeei MULTIBUS.

Generatorul de sistem include circuite de formare a impulsurilor de tact (OSC, CLK, PCLK),

semnalului RESET i semnalului READY (figura 6).

Circuitul de formare a impulsurilor de tact genereaz semnalele:

CLKfrecvena de tact pentru microprocesor;

PCLKfrecvena de tact pentru dirijarea circuitelor periferice;

OSCfrecvena de tact a generatorului etalon, necesar pentru dirijarea dispozitivelor

sistemului i pentru sincronizare. Semnalele sunt sincrone, frecvenele lor sunt legate de relaia:

FOSC=3FCLK=6FPCLK n regim de generator intern i:

FEFI=3FCLK=6FPCLK n regim de generator extern.

Alegerea regimului de funcionare se determin de potenialul la intrare F/C. Dac intrarea

este conectat la mas, atunci GS lucreaz n regim de formare a semnalelor de la generatorul

intern, iar dac la F/C se aplic un potenial nalt atunci n regim de formare a semnalului de la

generatorul extern.

Circuitul de formare a semnalului RESET are la intrare un trigher Shmidt, iar la ieire

trigher formator al frontului semnalului RESET. De obicei la intrare RES se conecteaz un circuit

RC care asigur formarea automat a semnalului la conectarea sursei de alimentare.

Circuitul de formare a impulsurilor de tact are o intrare de sincronizare special (CSYNC), cu

ajutorul creia se poate sincroniza funcionarea a ctorva generatoare de sistem. Aa sincronizare se

realizeaz cu ajutorul a dou a dou trighere D la intrrile CSYNC i EFI.

Reprezentarea grafic a acestuia este n figura urmtoare:

Coala

10

UTM 525.1 101 16 ME

Mod Coala

Nr. docum.

Semnat.

Data

Fig.6. Reprezentarea grafic a generatorului impulsurilor de tact 181084

Circuitul de formare a semnalului

Semnalul de intrare READY se utilizeaz n calitate de afirmare a posibilitii de schimb

(transfer). Circuitul de formare a acestui semnal n GS este construit astfel, pentru a simplifica

conectarea sistemului n magistrala interfeei MULTIBUS i are dou perechi de semnale identice

RDY1, AEN1 i RDY2, AEN2 conectate cu un circuit SAU. Semnalele RDY sunt formate de

elemente ce intr n sistem i indic posibilitatea lor de schimb.

Semnalele AEN permit formarea semnalului READY n semnalele RDY, afirmnd adresarea

elementului adresat.

Elementul de ieire al schemei (F) formeaz frontul semnalului READY.

Proiectarea magistralei

Controlerele cu magistralele prezint amplificatoare care realizeaz acordarea ieirilor

procesorului central cu magistralele de transmitere a informaiei. n sistemul de microprocesor

liniile de adresare sunt conectate cu un ir de intrri ale diferitor module conectate n paralel.

Coala

11

UTM 525.1 101 16 ME

Mod Coala

Nr. docum.

Semnat.

Data

Unitatea de memorie de obicei consum un curent mic (0,02-0,4 mA), ns n componena

sistemului intr dispozitive logice care au un consum de 1,6 mA n starea zero logic i 0,04 mA n

starea unu logic.

Pentru a micora consumul de curent n liniile semnalelor logice cu scopul de a evita

necesitatea introducerii controalelor cu magistralele, transformri logice se pot realiza pe baza CI

din familia K 555, care au un consum de curent redus: 0,36 mA n starea zero i 0,02 mA n starea

unu. n aa mod microprocesorul poate rezista sarcina a 5 CI din familia K 555.

ns n caz general sarcina dup curent pe liniile de adrese poate ntrece posibilitile CI i

atunci apare necesitatea utilizrii controlerelor de sistem.

Microcircuitele KP580BA86 i KP580BA87 sunt cele mai convenabile pentru utilizarea

practic. n comparaie cu formatoarelor de magistrale din familia K589 acestea au incorporate 8

controlere de magistrale care satisfac acordarea ntregii MD i strii acesteia.

La proiectarea sistemului de microprocesor este necesar de a determina sarcina dup curent

asupra fiecrei linii magistralelor MA i MD. Dac sarcina sumar a uneia din linii va fi mai mare

de ct valorile admisibile, n aa caz se utilizeaz controlerelor de sistem.

Controlerele cu magistralele i controlere de system

Controlerul cu magistralele KP580P82 este utilizat i n calitate de organizator cu

tampoanele de memorie, porturi I/O, multiplexatori, etc. El conine opt trighere informaionale (T)

cu circuite de ieire (SW) cu trei stri, semnale comune de nscriere a informaiei STB i dirijarea

cu circuitele de ieire OE. n aa registru la circuitele de ieire se conecteaz ieirele neinversate a

trigherilor informaionali.

Destinaia pinilor:

DI7-DI0liniile datelor de intrare;

D07-D00liniile datelor de ieire;

STBsemnal de strobare;

OEpermiterea transferului de date;

Coala

12

UTM 525.1 101 16 ME

Mod Coala

Nr. docum.

Semnat.

Data

La prezena semnalului de nivel nalt la intrarea STB starea liniilor de intrare DI7-DI0 se

transmite la liniile de ieire D07-D00. Homorarea n trigherile informaionale se realizeaz la

trecerea semnalului STB de la nivel nalt la cel jos (la cderea semnalului STB). Semnalul OE

dirijeaz cu tampoanele de ieire: la OE=0 tamponul se deschide, la OE=1el trece n starea cu

impedan nalt. Semnalul OE nu influeneaz nici asupra strilor trigherilor informaionali, nici

asupra funciei de nscriere.

Curentul de intrare mic i de ieire mare permit dea utiliza aceste elemente n calitate de

tampoane de memorare sau formatoare de magistrale, conectnd n acest caz STB printr-un rezistor

1 k la +5V, iar intrarea OEla masa ceea ce-l face transparent.

Controlerul de sistem KP580BA86 se utilizeaz n calitate de formator al magistralei de date.

Puterea mare de ieire i simplitatea de dirijare permite de a le utiliza n proiectarea tampoanelor

bidirecionale intermodul sau ca etaje simple de amplificare.

Formatorul const din opt module funcionale similare cu semnale comune de dirijare T i

OE.

Destinaia pinilor:

A7-A0intrarea/ieirea liniilor de date. n dependen de starea intrrii T ele pot fi de intrare,

dac la T este aplicat semnal de nivel mic;

B7-B0intrarea/ieirea liniilor de date. Ele sunt de ieire dac T are semnal de nivel mic i

de ieire dac la T se aplic semnalul de nivel mare;

Tsemnal de dirijare de intrare. Dac T=0 are loc transferul de la B la A (regim BA), la

T=1de la A la B. Semnalul Talege formatorul-amplificator de sus sau de jos, permind transferul

corespunztor;

OEsemnal de intrare de permitere a transferului. Cnd OE=0 starea cu impedana nalt de

la ieirea amplificatorului-formator ales dup intrare. Avantajele formatorului: curent de ieire

major la un curent de intrare mic, lipsa zgomotului la ieire la comutri.

Fig.7. Reprezentarea grafic a

Fig.8. Reprezentarea grafic a

registrului formator a magistralei

formatorului magistralei de date 580BA82

de adrese 58082

Coala

13

UTM 525.1 101 16 ME

Mod Coala

Nr. docum.

Semnat.

Data

Pentru dirijarea cu memoria de destinaie general i interfeele familiei KP580 este necesar

de utilizat magistrala multiplexat cu conectarea tampoanelor magistralelor. Structura procesorului

cu aa tip de magistral este reprezentat n figura 5. n aa scheme interfaa magistralei de adrese

MA este realizat pe CI registrelor tampon KP58082, iar interfaa magistralei de date MD-pe CI

formatoarelor de magistrale KP580BA86. Multiplexorul K55511 formeaz semnalele

citire/nscriere pentru memorie i dispozitivele periferice.

Capacitatea de sarcin a magistra-lei 32 mA. MA-20bii A19mAO, MD-8 bii D7...D0

2

5

11

14

3

6

10

13

8

16

A

1x1

MUX

S

2x1

1x2

2x2

1x3

2x3

1x4

2x4

G

UCC

K55511

15

MRD

MWR

IORD

IOWR

4

7

9

12

Coala

14

UTM 525.1 101 16 ME

Mod Coala

Nr. docum.

Semnat.

Data

Fig.9. Reprezentarea grafic a multiplexorului 55511

Proiectarea dispozitivelor de memorie ale

sistemelor de baz de microprocessor

Unitile de memorie ale sistemelor de microprocesor sunt destinate pentru pstrarea datelor

i programelor. Caracteristicile de baz a unitii de memorie sunt volumul, viteza de lucru, puterea

consumat, rezistena la apariia erorilor.

La proiectarea memoriei se rezolv problemele de divizare a volumului necesar de memorie

ntre memoria operativ RAM i fizic ROM; proiectarea volumului i capacitii RAM i ROM;

realizarea dispozitivelor de joncionare a RAM i ROM cu magistrala de sistem.

Unitile de memorie se construiesc pe baz de circuite integrate de memorie care se

caracterizeaz cu capacitatea ni i volumul Ni. Capacitatea necesar se proiecteaz prin adugare a

K=n/ni circuite integrate (CI) conectate n paralel, iar volumul necesar - prin conectarea a L=N/Ni

BI conectate serie, fiecare bloc constituind din K CI de memorie.

Sistemele de funcionare a memoriei cu magistrala de sistem asigur acordarea diagramelor

de timp de funcionare a memorie i operaiile de citire/nscriere, acordarea dup nivele de sarcin a

semnalelor.

RAM sunt realizate pe baz de CI statice cu volumul Ni i capacitatea ni are intrri de adrese

cu capacitatea m=log2Ni, intrrile Ei ieirile de date cu capacitatea ni, intrrile de citire/nscriere.

Pentru a realiza capacitatea necesar n a memoriei, K=n/ni elemente de memorie se

conecteaz n module, aa cum e reprezentat n figura 10. Toate CI a modulului au intrri de adres

comune, selectare a cristalului i citire/nscriere. ntrrile i ieirile de date formeaz ntrrile i

ieirile modulului dat cu capacitatea n bii. n acest caz CI RAM static O pstreaz biii inferiori ni,

iar CI RAM statice (k-1) - biii superiori. Pentru a primi volumul necesar N a memoriei se unesc

L=N/Ni blocuri de memorie aa cum e reprezentat n figura 11. Pentru divizarea adreselor de obicei

se folosete un multiplicator de adrese, numrul de ieiri ai cruia L este egal cu numrul de module

de memorie, iar numrul intrrilor l=log2L. Toate intrrile i ieirile modulelor de memorie, n afar

de intrrile de selectare, se unesc ntre ele, iar intrrile de selectare se unesc n corespundere cu

ieirele multiplexorului de adrese. Modul RAM static cu organizarea N*n are intrrile de adrese cu

capacitatea (l+m)=log2N, intrrile, ieirele de date cu capacitatea n i 0 intrare comun de

Coala

15

Coala

UTM 525.1 101 16 ME

Mod Coala

Nr. docum.

Semnat.

16

Data

nscriere/citire. Intrarea de selectare CS se folosete pentru a plasa n locul necesar al spaiului de

adres al memoriei.

CS

A(m)

m

m

CS

A(m)

CEO

CI RAM statica

DO(ni)

ni

CEO

CS

.

A(m)

CEO

CI RAM statica

DO(ni)

DO(n)

ni

n=kni

Fig.10. Schema de sporire a capacitii memoriei pe CI RAM static

RA

M dinamic este realizat pe baz de elemente capacitive de memorie i necesit regenerare

periodic a informaiei. Timpul de regenerare se calculeaz n uniti de milisecunde. La volume

mari de memorie pentru regenerarea fiecrei celule sunt necesare intervale de timp egale cu

fraciuni de microsecunde. Memoria RAM dinamic cu volumul Ni i capacitatea ni are

m/2=(log2N)/2 linii de adrese, intrri CAS i RAS, intrri i ieiri de date i intrare de permitere a

citirii. Pentru regenerarea memoriei dinamice se folosete controlerul memoriei dinamice (figura

12).

Coala

UTM 525.1 101 16 ME

Mod Coala

Nr. docum.

Semnat.

17

Data

CAS RAS A(m/2) CEO

m/2

CAS RAS A(m/2) CEO

CI RAM dinamica

k-1

DI(ni)

ni

DO(ni)

CAS

.

RAS A(m/2) CEO

CI RAM dinamica

0

DI(ni)

ni

DO(ni)

ni

DI(n)

ni

DO(n)

Fig.11. Schema de sporire a capacitii memoriei pe CI RAM dinamic

Unitatea de memorie a SMP este format din memorie fix (ROM) i operativ (RAM).

Pentru a obine un volum de memorie RAM de 48 kB vom utiliza 6 microcircuite de memorie

operativ dinamic K565P5, care necesit a fi conectate mpreun cu controlerul memoriei

dinamice. n calitate de controler al memoriei dinamice (CMD) vom utiliza microcircuitul

K1810BT03. Memoria fix este efectuat pe baza microcircuitului K573P4.

UTM 525.1 101 16 ME

Mod Coala

Nr. docum.

Semnat.

Data

Fig.12 Harta memoriei RAM i ROM

Memoria dinamic K565P5

Circuitul K565P5 este un microcircuit de memorie dinamic, organizat n 65536 rnduri

cte un bit. Analogul internaional este MCM6664, de la firma Motorola. Forma fizic a acestuia

este prezentat mai jos:

Fig.13 Microcircuitul K565P5

Diagrama bloc a acestuia, de unde poate fi dedus i principiul de lucru este prezentat mai jos:

Coala

18

UTM 525.1 101 16 ME

Mod Coala

Nr. docum.

Semnat.

Data

Fig.14 Diagrama bloc a microcircuitului K565P5

Diagrama n timp a procesului de citire i nscriere este prezentat mai jos:

Coala

19

UTM 525.1 101 16 ME

Mod Coala

Nr. docum.

Semnat.

Data

Fig.15 Diagrama n timp a procesului de citire

Fig.14 Diagrama n timp a procesului de nscriere

Coala

20

UTM 525.1 101 16 ME

Mod Coala

Nr. docum.

Semnat.

Data

Harta memoriei cu cele 6 microcircuite implementate este prezentat mai jos;

Fig. 15 Harta memoriei cu microcircuitele K565P5 implementate

n urmtorul paragraf se va vorbi despre memoria ROM (Read Only Memory) i

microcircuitul folosit.

Microcircuitul K573P4

Microcircuitul K573P4 este un microcircuit de memorie programabil cu ajutorul UV. Este

organizat n 8192 rnduri cte 8 bii. De obicei este folosit n carcas cte 28 pini, avnd o

ferestruic pentru reprogramare cu ajutorul razelor ultraviolet. n proiectarea dat vom folosi 2

microcircuite de acest tip, pentru a avea 16 kB de memorie.

Forma fizic a acestuia este prezentat mai jos:

Coala

21

UTM 525.1 101 16 ME

Mod Coala

Nr. docum.

Semnat.

Data

Fig.16 Microcircuitul K573P4

Harta memoriei mpreun cu memoria RAM este prezentat mai jos:

Coala

22

UTM 525.1 101 16 ME

Mod Coala

Nr. docum.

Semnat.

Data

Fig.17 Harta memoriei RAM i ROM

Proiectarea unitii de intrare/iesire.

Pentru realizarea schimbului de informaie dintre SMP i dispozitivele externe este nevoie de

porturi de intrare/ieire (IOP). Porturile sunt de cteva tipuri: serie, paralel, analogic. La elaborarea

acestui proiect vom utiliza portul de tip serie. n calitate de IOP serie sau utilizat MC

KP580BB51A.

MC KP580BB51A prezint port serie de ntrare/ieire, se utilizeaz n calitate de dispozitiv de

ntrare/ieire de destinaie general ce realizeaz joncionarea diferitor dispozitive periferice cu

magistrala de date a sistemului.

Microschema data MC KP580BB51A, se alimenteaza la tensiunea de +5V si consuma

curentul de 100mA.Microschema este in sine universala, sincron si asincron dispozitiv de primire si

transmitere a datelor.Microschema poate fi programata pentru lucru in cinci regimuri:

-transmitere asincrona

Coala

23

UTM 525.1 101 16 ME

Mod Coala

Nr. docum.

Semnat.

Data

-primire asincrona

-transmitere sincrona

-primire sincrona

-primirea sincrona cu sincronizare externa

Fig.18 Pinout a micrcircuitului de intrare ieire

D0D7-intrari de date

R D-intrarea receptorului

R C-sincronizarea receptorului

R RDY-receptorul in modul de asteptarea comenzii

SYND-iesirea de initializare a sincronizatiei interne

DSR-pregatirea transmitatorului terminalului

DTR-adresarea transmitatorului terminalului

CTS-pregatirea receptorului terminalului

RTS-adresarea receptorului terminalului

Coala

24

UTM 525.1 101 16 ME

Mod Coala

Nr. docum.

Semnat.

Data

T E-registrul transmitatorului gol

T RDY-transmitatorul in modul de asteptarea comenzii

T C-sincronizarea transmitatorului

T D-iesirea transmitatorului

CS-alegerea BIS

C/D-conducerea cu datele(1-conducerea, 0-datele)

RD-citirea

WR-inscrierea

CLK-sincronizarea

RES-resetul

Destinati pinilor microcircuitului KP580BB55

Coala

25

UTM 525.1 101 16 ME

Mod Coala

Nr. docum.

Semnat.

Data

Fig.19 Pinout a micrcircuitului de intrare ieire

PA7PA0-iesirile portului A

BA7BA0- iesirile portului B

CA7CA4,CA3CA0- iesirile porrtului C.

CS- semnal de selectie

A1,A0-Adresarea porturilor

D7D0- datele de intrare.

RD- semnal de citire.

WR- semnal de inscriere.

RES- semnal de initializare.

Pentru relizarea portului paralel vom folosi doua micrcrocircuiteKP580BB55.

Proiectarea tastaturii

Pentru a avea posibilitatea de a dirija cu SMP din exterior vom utiliza i tastatura. Tastatura se

conecteaz la SMP cu ajutorul unuia din porturile paralele KP580BB55A studiate mai sus. Schema

bloc de conexiune a tastaturii este prezentat mai jos

n cazul proiectrii tastaturii pentru a avea 64 de taste vom folosi port A i B cu toate 8 linii a

intrrilor/ieirilor. Tastatura nu are nici o schem electric n plus i prezint nite comutatoare

aranjate n form de matrice. La apsarea tastei corespunztoare liniei li coloanei se scurcircuiteaz,

formnd o conectare. Detectnd poziia liniei i coloanei n care s-a produs scurtcircuitul contactelor

se determin codul cuvntului corespunztoare tastei apsate. Portul de ieire trimite semnal 0 n

linia 0 i n restul liniilor , apoi se numr i se verific liniile coloanelor. Dac n linia 0 nu este

semnal 0 procesul se repet pentru linia 1 apoi pentru linia 2 ... Cnd se detecteaz 0 se determin

tasta apsat , poziia liniei este cunoscut dup combinaia introdus , iar poziia coloanei dup

rezultatul introducerii.

Coala

26

UTM 525.1 101 16 ME

Mod Coala

Nr. docum.

Semnat.

Data

mpreunnd codul poziiei liniei i coloanei n care s-a detectat 0 se poate de format un

cuvnt dintr-un simbol artnd poziia tastei apsate. Tastatura are dou neajunsuri : apsarea

concomitent a dou taste i apariia unui proces tranzitoriu la conectarea ntreruptorului.

Fig.20 Modul de conectare a tastaturii

CONCLUZII

n urma efecturii lucrrii date, am proiectat un sistem pe baza microprocesorului Intel 8086,

mai bine zis a analogului acestuia. n prima etap s-a proiectat schema general de structur, dup

cure s-a proiectat fiecare element din cadrul acestei structuri. Cel mai mult am atras atenia la

proiectarea memoriei RAM i ROM. n proiectul dat am folosit memorie operativ dinamic, de

tipul K565P5, 8194 rnduri * 1 bit. Am folosit 6 microcircuite de acest tip, pentru obinerea a 48

kB. Memoria ROM, a fost aleas pe baza microcircuitului K573P4, n proiect fiind folosite 2

microcircuite cte 8 kB fiecare. Memoria RAM dinaimc este condus de ctre controlorul de

memorie dinamic K1810BT03. Totodat au fost proiectate i unitile de intrare i ieire i

tastatura cu 64 de taste.

ntr-un final a fost realizat sistemul cu urmtoarele caracteristici:

Coala

27

UTM 525.1 101 16 ME

Mod Coala

Nr. docum.

Semnat.

Data

Microprocesor: Intel 8086

Memorie RAM 48 kB

Memorie ROM 16 kB

Tastatur 64 de taste

Bibliografie

1. ..

. . 1988

2. . . . . 1988

3. . . . .

1990

Coala

28

UTM 525.1 101 16 ME

Mod Coala

Nr. docum.

Semnat.

Data

4. . . 1810. .

1989

5. , -. . - .: , 1986.

6. -

: . - .: , 1987.

7. . 6, 1988.

Coala

29

S-ar putea să vă placă și

- Arhitectura Sistemelor de CalculDocument41 paginiArhitectura Sistemelor de CalculVlad MuresanÎncă nu există evaluări

- Microprocesoare 13Document17 paginiMicroprocesoare 13neacsu92Încă nu există evaluări

- Arhitectura Sistemelor de CalculDocument13 paginiArhitectura Sistemelor de CalculLeraCecan100% (1)

- Componentele Si Function Area MicroprocesoruluiDocument29 paginiComponentele Si Function Area MicroprocesoruluiAlina MihaelaÎncă nu există evaluări

- Tema 5 ACRDocument37 paginiTema 5 ACRAlex RacuÎncă nu există evaluări

- Echipamente de BiroticaDocument53 paginiEchipamente de BiroticaNiculaie Alina100% (1)

- Arhitectura Sistemelor de CalculDocument61 paginiArhitectura Sistemelor de CalculAnonymous BCWEBkPTÎncă nu există evaluări

- MicroprocesorDocument7 paginiMicroprocesorTudor MunteanuÎncă nu există evaluări

- Informatica 1Document9 paginiInformatica 1Ionut GheorghitaÎncă nu există evaluări

- Cursul Meu 10 6. Structura Hardware A Unui Sistem MecatronicDocument26 paginiCursul Meu 10 6. Structura Hardware A Unui Sistem MecatronicVadim EriomencoÎncă nu există evaluări

- Atestat MicroprocesorDocument5 paginiAtestat MicroprocesorBogdanGiuÎncă nu există evaluări

- Proiect de Certificare A Competențelor Profesionale: Colegiul Tehnic 'Ion Mincu'' FocșaniDocument19 paginiProiect de Certificare A Competențelor Profesionale: Colegiul Tehnic 'Ion Mincu'' FocșaniIulian SavaÎncă nu există evaluări

- Curs PMP1 PDFDocument205 paginiCurs PMP1 PDFDan Patrick-ErnestÎncă nu există evaluări

- Componentele CalculatoruluiDocument34 paginiComponentele Calculatoruluilic_86Încă nu există evaluări

- Cap 12Document80 paginiCap 12Catalin Ionut GhitaÎncă nu există evaluări

- Microprocesoare Si MicrocontrolereDocument265 paginiMicroprocesoare Si MicrocontrolereDragos SimonaÎncă nu există evaluări

- Arhitectura Sistemelor de CalculDocument8 paginiArhitectura Sistemelor de CalculDru BarrettÎncă nu există evaluări

- Structuri MecatroniceDocument20 paginiStructuri MecatroniceAnton Valentin100% (2)

- Sisteme de Calcul Si Retele de Calculatoare-Curs 1Document16 paginiSisteme de Calcul Si Retele de Calculatoare-Curs 1eoliannÎncă nu există evaluări

- Curs Calculator (ECDL)Document33 paginiCurs Calculator (ECDL)Mihai StoicaÎncă nu există evaluări

- Arhitectura Sistemelor de Calcul (ASC)Document13 paginiArhitectura Sistemelor de Calcul (ASC)Eduard StanescuÎncă nu există evaluări

- M&M CursDocument73 paginiM&M CursalbudfÎncă nu există evaluări

- Proiectarea Microsistemelor DigitaleDocument34 paginiProiectarea Microsistemelor DigitaleIulia Casapu100% (1)

- Tipuri de Microprocesoare - Docx BardanDocument5 paginiTipuri de Microprocesoare - Docx BardanBardan MariusÎncă nu există evaluări

- Subiecte Sisteme Bazate Pe MicroprocesoareSubiecte Sisteme Bazate Pe MicroprocesoareSubiecte Sisteme Bazate Pe MicroprocesoareDocument36 paginiSubiecte Sisteme Bazate Pe MicroprocesoareSubiecte Sisteme Bazate Pe MicroprocesoareSubiecte Sisteme Bazate Pe MicroprocesoaredetonatorulÎncă nu există evaluări

- ASC 3 Structura Unui Calculator (II)Document35 paginiASC 3 Structura Unui Calculator (II)Alis Madalina EneÎncă nu există evaluări

- Componentele Unui Calculator Partea IIDocument22 paginiComponentele Unui Calculator Partea IImihaitapadurariu9Încă nu există evaluări

- TIC - Sisteme de CalculDocument44 paginiTIC - Sisteme de CalculAndreea DumitraÎncă nu există evaluări

- Initiere ITDocument119 paginiInitiere ITjulia007100% (1)

- carteMicrocontrolereMH FINAL PDFDocument210 paginicarteMicrocontrolereMH FINAL PDFPitzy Locca100% (1)

- Descrierea Calculatorului - Partea HardwareDocument14 paginiDescrierea Calculatorului - Partea HardwareNimrod FoldvariÎncă nu există evaluări

- Curs OCER- bunDocument131 paginiCurs OCER- bunRadu CatalinÎncă nu există evaluări

- Lab 1 MDocument24 paginiLab 1 Mviorica88Încă nu există evaluări

- Examen PMP2Document23 paginiExamen PMP2Tatar DanielÎncă nu există evaluări

- SOLTR AllDocument217 paginiSOLTR AllClaudiu Gabriel PopescuÎncă nu există evaluări

- Microprocesoare, Curs 1Document15 paginiMicroprocesoare, Curs 1Petrovai AlexandruÎncă nu există evaluări

- Tema ASC 1Document10 paginiTema ASC 1Andrei CristianÎncă nu există evaluări

- Structura Şi Funcţionarea UnuiDocument28 paginiStructura Şi Funcţionarea UnuiNume PredefinitÎncă nu există evaluări

- Suport Curs Oivpd 568183b5a0fa0Document75 paginiSuport Curs Oivpd 568183b5a0fa0RADU CÎMPEANÎncă nu există evaluări

- Structura Hardware A CalculatoruluiDocument8 paginiStructura Hardware A CalculatoruluiDeya RoxanaÎncă nu există evaluări

- Ac ExamDocument92 paginiAc ExamNegru TatianaÎncă nu există evaluări

- TIC9 Clasa A IX-a 2015-2016Document205 paginiTIC9 Clasa A IX-a 2015-2016Mihi pihiÎncă nu există evaluări

- Micro ControllerDocument13 paginiMicro ControllerCatalin LazarÎncă nu există evaluări

- Schema Bloc A Unui Sistem Cu MicroprocesorDocument2 paginiSchema Bloc A Unui Sistem Cu MicroprocesorGirbea PetrisorÎncă nu există evaluări

- Suport Curs Operator Introducere, Prelucrare, Validare DateDocument34 paginiSuport Curs Operator Introducere, Prelucrare, Validare DateJeana LunguÎncă nu există evaluări

- Cap 10Document139 paginiCap 10micumarianÎncă nu există evaluări

- MicroprocesorDocument17 paginiMicroprocesorterry bogardÎncă nu există evaluări

- Proiectarea Unui Microsistem Electronic de ComandăDocument34 paginiProiectarea Unui Microsistem Electronic de ComandăAdrian Capatina100% (1)

- Proiect Procesor Pentru PCDocument2 paginiProiect Procesor Pentru PCPetrut SarbuÎncă nu există evaluări

- Curs SAIPDocument114 paginiCurs SAIPLaura ElenaÎncă nu există evaluări

- MicroprocesorulDocument33 paginiMicroprocesorulRaul LazarÎncă nu există evaluări

- Carte Var FinalDocument87 paginiCarte Var FinalCoz AnimationÎncă nu există evaluări

- Lectia 3 CSSDocument10 paginiLectia 3 CSSValik1708Încă nu există evaluări

- Atestarea 2 FinalDocument5 paginiAtestarea 2 FinalGuzganShobolanÎncă nu există evaluări

- Lab #2Document1 paginăLab #2Valik1708Încă nu există evaluări

- Statistica Pe UniversitatiDocument1 paginăStatistica Pe UniversitatiValik1708Încă nu există evaluări

- TC Lab 2Document20 paginiTC Lab 2Valik1708Încă nu există evaluări

- IoT CheckListDocument1 paginăIoT CheckListValik1708Încă nu există evaluări

- Pointeri PDFDocument22 paginiPointeri PDFMarian Soryn100% (1)

- Sirbu FinalDocument386 paginiSirbu FinalValik1708Încă nu există evaluări

- Laborator 2Document8 paginiLaborator 2Valik1708Încă nu există evaluări

- EncoderDocument1 paginăEncoderValik1708Încă nu există evaluări

- CuratDocument45 paginiCuratValik1708Încă nu există evaluări

- MSW A4 FormatDocument3 paginiMSW A4 FormatValik1708Încă nu există evaluări

- My CareerDocument3 paginiMy CareerValik1708Încă nu există evaluări

- Sirbu FinalDocument386 paginiSirbu FinalValik1708Încă nu există evaluări

- Referat Inteligenţa EmoţionalăDocument3 paginiReferat Inteligenţa EmoţionalăCirstoiu IoanaÎncă nu există evaluări

- AVVIDDocument3 paginiAVVIDValik1708Încă nu există evaluări

- WWW - Referat.ro-Cariera Profesionala Pe Plan EuropeanDocument4 paginiWWW - Referat.ro-Cariera Profesionala Pe Plan EuropeanigormocanÎncă nu există evaluări

- I8086 DasdasDocument27 paginiI8086 DasdasValik1708Încă nu există evaluări

- Curs 4 Desene Pasteurizare SterilizareDocument7 paginiCurs 4 Desene Pasteurizare SterilizareValik1708Încă nu există evaluări

- Lab2 Com MsasobileDocument11 paginiLab2 Com MsasobileValik1708Încă nu există evaluări

- Intel8086 32kBDocument35 paginiIntel8086 32kBValik1708Încă nu există evaluări

- UML-Diagrame de StareDocument17 paginiUML-Diagrame de StareValik1708Încă nu există evaluări

- Curs de FizicaDocument2 paginiCurs de FizicaValik1708Încă nu există evaluări

- Defiopniti Notiunea de RADIOCANALDocument9 paginiDefiopniti Notiunea de RADIOCANALValik1708Încă nu există evaluări

- Raspunsuri La PMSDDocument27 paginiRaspunsuri La PMSDValik1708Încă nu există evaluări

- Surse de AlimentareDocument22 paginiSurse de AlimentareValik1708Încă nu există evaluări

- C4 Extrudarea+si+calandrareaDocument40 paginiC4 Extrudarea+si+calandrareaValik1708Încă nu există evaluări

- Serviciul WWWDocument7 paginiServiciul WWWValik1708Încă nu există evaluări

- Dare de SeamaDocument1 paginăDare de SeamaValik1708Încă nu există evaluări