Documente Academic

Documente Profesional

Documente Cultură

Toshiba C660D-145 - LA-6849P

Încărcat de

Valerică HizanuTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Toshiba C660D-145 - LA-6849P

Încărcat de

Valerică HizanuDrepturi de autor:

Formate disponibile

A

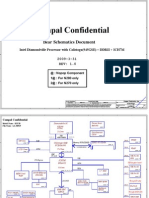

Compal confidential

Brazos-Delhi 10AB

PWWBE LA-6849P Schematics Document

Mobile AMD APU ZACATE-FT1 + FCH Hudson-M1

3

2010-11-22 Rev. 1.0

Compal Secret Data

Security Classification

2010-09-09

Issued Date

2010-09-09

Deciphered Date

Title

Compal Electronics, Inc.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS Custom

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

SCHEMATICS, MB A6849

Rev

B

4019BA

Sheet

Monday, December 06, 2010

E

of

38

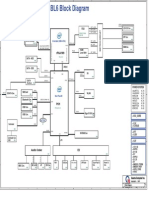

Compal Confidential

Model Name : PWWBE

File Name : LA-6849P

Memory BUS(DDRIII)

Single Channel

AMD Zacate APU

LVDS

Fan Control

page 5

CRT

page 9,10

BANK 0, 1, 2, 3

1.5V DDRIII 1066/1333MHZ

FT1

BGA 413-Ball

19mm x 19mm

page 17

200pin DDRIII-SO-DIMM X2

1

RTL8105E 10/100M

PCIe 1x

RJ45

PCIe port 2

page 19

LAN

page 19

page 5,6,7,8

page 16

PCIe 1x

WLAN

PCIe port3

page 18

x4 UMI Gen. 1

2.5GT/s per lane

Hudson M1

BT Combo

IO/B-- USB Right

USB port 6

page 18

USB port 0,1

BGA 605-Ball

23mm x 23mm

page 18

USB

Card Reader

USB port7

page 20

Int. Camera

5V 480MHz

SATA port 0

USB port 5

5V 1.5GHz(150MB/s)

page 17

SATA port 1

5V 1.5GHz(150MB/s)

SATA HDD

page 18

SATA ODD

page 18

page 11,12,13,14,15

3

RTC CKT.

SPI ROM

page 24

Power On/Off CKT.

page 30

Power/B

LPC BUS

page 26

3.3V 33 MHz

page 25

DC/DC Interface CKT.

HD Audio

3.3V/1.5V 24MHz

HDA Codec

ALC259

Power Circuit DC/DC

page 21

page 27,28,29,30,31

32,33,34,35

Debug Port

ENE KB926 E0

page 23

page 24

Int.

MIC CONN

page 17

Touch Pad

Int.KBD

page 25

page 24

2010-09-09

2010-09-09

Deciphered Date

Title

Date:

SPK CONN

page 22

Compal Electronics, Inc.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

Custom

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

HP CONN

page 22

page 24

Compal Secret Data

Security Classification

Issued Date

MIC CONN

page 22

EC ROM

SCHEMATICS, MB A6849

Rev

B

4019BA

Monday, December 06, 2010

Sheet

E

of

38

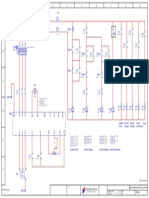

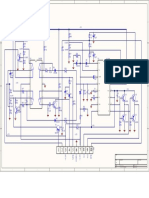

DESIGN CURRENT 0.1A

+3VL

DESIGN CURRENT 0.1A

+5VL

DESIGN CURRENT 1A

+3VALW

DESIGN CURRENT 3.5A

+5VALW

B+

RT8205EGQW

SUSP

N-CHANNEL

SI4800

DESIGN CURRENT 2A

+5VS

DESIGN CURRENT 330mA

+3V_LAN

DESIGN CURRENT 1.5A

+3VS

DESIGN CURRENT 1A

+LCD_VDD

DESIGN CURRENT 300mA

+2.5VS

DESIGN CURRENT 2.5A

+1.8VS

DESIGN CURRENT 0.3A

+1.1VALW

DESIGN CURRENT 3.5A

+1.1VS

DESIGN CURRENT 6A

+NB_CORE

DESIGN CURRENT 18A

+CPU_CORE0

DESIGN CURRENT 18A

+CPU_CORE1

DESIGN CURRENT 4A

+VDDNB

DESIGN CURRENT 5A

+1.5V

DESIGN CURRENT 1A

+1.5VS

DESIGN CURRENT 1A

+0.75VS

DESIGN CURRENT 1.5A

+1.05VS

WOL_EN#

P-CHANNEL

AO-3413

SUSP

N-CHANNEL

SI4800

ENVDD

P-CHANNEL

AO-3413

APL5508

PWWAE LC-Marseille AMD

SUSP#

MP2121DQ

POK

RT8209BGQW

VLDT_EN#

N-CHANNEL

IRF8113

VLDT_EN#

N-CHANNEL

IRF8113

VR_ON

B

ISL6265A

SYSON

RT8209BGQW

SUSP

N-CHANNEL

IRF8113

SUSP

APL5331KAC

VR_ON#

APL5331KAC

Compal Secret Data

Security Classification

2010-09-09

Issued Date

2010-09-09

Deciphered Date

Title

Compal Electronics, Inc.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS Custom

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

SCHEMATICS, MB A6849

Rev

B

4019BA

Sheet

Monday, December 06, 2010

1

of

38

Voltage Rails

O : ON

X : OFF

+5VS

power

plane

+3VS

+1.8VS

+1.5VS

State

+B

+5VALW

+3VL

+3VALW

+5VL

+1.1VALW

+1.1VS

+1.5V

Platform

+1.05VS

CPU

APU FT1

Brazos

+0.75VS

SB

FCH M1

VGA

NA

EC

Comment

KB926

+AGP_CORE

+RTCVCC

+APU_VDDNB

S0

S1

S3

S5 S4/AC

S5 S4/ Battery only

S5 S4/AC & Battery

don't exist

@ : just reserve , no build

CONN@ : just reserve for Connector only

8105E_VC@: just reserve for 10/100 LAN VC version only

8105E_VB@: just reserve for 10/100 LAN VBversion only

HDT@:just reserve for JHDT connector

E240@ : AMD E240 1.5Ghz CPU only

E350@ : AMD E350 1.6Ghz CPU only

SMBUS Control Table

3

SOURCE

FCH SM Bus0 address

FCH SM Bus1 address

Power

Power

HEX

Device

Address

+3VS

DDR SO-DIMM 0 A0 H

1010 0000 b

+3VS

DDR SO-DIMM 1 A4 H

1010 0100 b

Device

HEX

Address

EC_SMB_CK1

KB926

EC_SMB_DA1

LCD_EDID_DATA

D_DDCCLK

Power

Device

Power

+3VL

Smart Battery 16H

HEX

Address

Device

HEX

0001 011X b

Address

D_DDCDATA

FCH_SMCLK0

FCH_SMDAT0

FCH_SMCLK1

FCH_SMDAT1

CRT

DDC

ROM

WLAN

LCD

DDC

ROM

APU

KB926

EC_SMB_DA2

LCD_EDID_CLK

EC SM Bus2 address

SODIMM

I / II

EC_SMB_CK2

EC SM Bus1 address

BATT

APU FT1

APU FT1

FCH M1

FCH M1

Compal Secret Data

Security Classification

2010-09-09

Issued Date

2010-09-09

Deciphered Date

Title

Compal Electronics, Inc.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS Custom

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

SCHEMATICS, MB A6849

Rev

B

4019BA

Sheet

Monday, December 06, 2010

E

of

38

P_GPP_RXP0

P_GPP_RXN0

AB4

AC4

P_GPP_RXP1

P_GPP_RXN1

19 PCIE_PTX_C_IRX_P2

19 PCIE_PTX_C_IRX_N2

AA1

AA2

P_GPP_RXP2

P_GPP_RXN2

18 PCIE_PTX_C_IRX_P3

18 PCIE_PTX_C_IRX_N3

Y4

Y3

P_GPP_RXP3

P_GPP_RXN3

AA12

Y12

11 UMI_RX0P

11 UMI_RX0N

Y14

P_ZVDD_10

AA10

Y10

P_UMI_RXP1

P_UMI_RXN1

11 UMI_RX2P

11 UMI_RX2N

AB10

AC10

P_UMI_RXP2

P_UMI_RXN2

11 UMI_RX3P

11 UMI_RX3N

AC7

AB7

P_UMI_RXP3

P_UMI_RXN3

AB6

AC6

P_GPP_TXP1

P_GPP_TXN1

AB3

AC3

P_GPP_TXP2

P_GPP_TXN2

Y1

Y2

P_ZVSS

P_UMI_RXP0

P_UMI_RXN0

11 UMI_RX1P

11 UMI_RX1N

P_GPP_TXP0

P_GPP_TXN0

P_GPP_TXP3

P_GPP_TXN3

LAN

PCIE_ITX_PRX_P2 0.1U_0402_25V6

PCIE_ITX_PRX_N2 0.1U_0402_25V6

2

2

1 C1264

1 C1265

PCIE_ITX_C_PRX_P2 19

PCIE_ITX_C_PRX_N2 19

PCIE_ITX_PRX_P3 0.1U_0402_25V6

PCIE_ITX_PRX_N3 0.1U_0402_25V6

R994

AA14

1

2

1.27K_0402_1%

2

2

1 C1268

1 C1269

PCIE_ITX_C_PRX_P3 18

PCIE_ITX_C_PRX_N3 18

V3

V4

AB12

AC12

UMI_TX0P_C

UMI_TX0N_C

C1270 1

C1271 1

2 0.1U_0402_25V6

2 0.1U_0402_25V6

UMI_TX0P 11

UMI_TX0N 11

P_UMI_TXP1

P_UMI_TXN1

AC11

AB11

UMI_TX1P_C

UMI_TX1N_C

C1272 1

C1273 1

2 0.1U_0402_25V6

2 0.1U_0402_25V6

UMI_TX1P 11

UMI_TX1N 11

P_UMI_TXP2

P_UMI_TXN2

AA8

Y8

UMI_TX2P_C

UMI_TX2N_C

C1274 1

C1275 1

2 0.1U_0402_25V6

2 0.1U_0402_25V6

UMI_TX2P 11

UMI_TX2N 11

P_UMI_TXP3

P_UMI_TXN3

AB8

AC8

UMI_TX3P_C

UMI_TX3N_C

C1276 1

C1277 1

2 0.1U_0402_25V6

2 0.1U_0402_25V6

UMI_TX3P 11

UMI_TX3N 11

P_UMI_TXP0

P_UMI_TXN0

UMI I/F

+1.05VS

1

2 R993

2K_0402_1%

PCIE I/F

U1A

AA6

Y6

WLAN

Zacate-FT1_BGA_413P-T

@

U1

U1

E240

E350

E240@

E350@

+5VS

1A

1

1

2

3

4

23 EN_DFAN1

EN

VIN

VOUT

VSET

GND

GND

GND

GND

8

7

6

5

C1121

1000P_0402_25V8J

1

2

3

1

2

3

4

5

GND

GND

+FAN1

1

@

U31

+3VS

JFAN

R795

10K_0402_5%

2

C1119

10U_0805_6.3V6M

2

C1120

10U_0805_6.3V6M

+FAN1

ACES_85204-0300N

CONN@

FAN_SPEED1 23

APL5607KI-TRG_SO8

2

@

1

C1122

0.01U_0402_25V7K

Compal Secret Data

Security Classification

2010-09-09

Issued Date

2010-09-09

Deciphered Date

Title

Compal Electronics, Inc.

SCHEMATICS, MB A6849

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS Custom

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

Rev

B

4019BA

Sheet

Monday, December 06, 2010

E

of

38

U1E

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

9,10 DDR_A_DQS0

9,10 DDR_A_DQS#0

9,10 DDR_A_DQS1

9,10 DDR_A_DQS#1

9,10 DDR_A_DQS2

9,10 DDR_A_DQS#2

9,10 DDR_A_DQS3

9,10 DDR_A_DQS#3

9,10 DDR_A_DQS4

9,10 DDR_A_DQS#4

9,10 DDR_A_DQS5

9,10 DDR_A_DQS#5

9,10 DDR_A_DQS6

9,10 DDR_A_DQS#6

9,10 DDR_A_DQS7

9,10 DDR_A_DQS#7

9

9

9

9

10

10

10

10

+1.5V

R9981

2 1K_0402_5%

DDR_A_CLK0

DDR_A_CLK#0

DDR_A_CLK1

DDR_A_CLK#1

DDR_B_CLK2

DDR_B_CLK#2

DDR_B_CLK3

DDR_B_CLK#3

9,10 DDR_RST#

9,10 MA_EVENT_L

MA_EVENT_L

9,10 DDR_CKE0

9,10 DDR_CKE1

M_ADD0

M_ADD1

M_ADD2

M_ADD3

M_ADD4

M_ADD5

M_ADD6

M_ADD7

M_ADD8

M_ADD9

M_ADD10

M_ADD11

M_ADD12

M_ADD13

M_ADD14

M_ADD15

DDR_A_BS#0

DDR_A_BS#1

DDR_A_BS#2

R18

T18

F16

M_BANK0

M_BANK1

M_BANK2

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

D15

B19

D21

H22

P23

V23

AB20

AA16

M_DM0

M_DM1

M_DM2

M_DM3

M_DM4

M_DM5

M_DM6

M_DM7

DDR_A_DQS0

DDR_A_DQS#0

DDR_A_DQS1

DDR_A_DQS#1

DDR_A_DQS2

DDR_A_DQS#2

DDR_A_DQS3

DDR_A_DQS#3

DDR_A_DQS4

DDR_A_DQS#4

DDR_A_DQS5

DDR_A_DQS#5

DDR_A_DQS6

DDR_A_DQS#6

DDR_A_DQS7

DDR_A_DQS#7

A16

B16

B20

A20

E23

E22

J22

J23

R22

P22

W22

V22

AC20

AC21

AB16

AC16

M_DQS_H0

M_DQS_L0

M_DQS_H1

M_DQS_L1

M_DQS_H2

M_DQS_L2

M_DQS_H3

M_DQS_L3

M_DQS_H4

M_DQS_L4

M_DQS_H5

M_DQS_L5

M_DQS_H6

M_DQS_L6

M_DQS_H7

M_DQS_L7

DDR_A_CLK0

DDR_A_CLK#0

DDR_A_CLK1

DDR_A_CLK#1

DDR_B_CLK2

DDR_B_CLK#2

DDR_B_CLK3

DDR_B_CLK#3

M17

M16

M19

M18

N18

N19

L18

L17

M_CLK_H0

M_CLK_L0

M_CLK_H1

M_CLK_L1

M_CLK_H2

M_CLK_L2

M_CLK_H3

M_CLK_L3

DDR_RST#

MA_EVENT_L

L23

N17

M_RESET_L

M_EVENT_L

DDR_CKE0

DDR_CKE1

F15

E15

M_CKE0

M_CKE1

9

9

10

10

DDR_A_ODT0

DDR_A_ODT1

DDR_B_ODT0

DDR_B_ODT1

DDR_CS0_DIMMA#

DDR_CS1_DIMMA#

DDR_CS0_DIMMB#

DDR_CS1_DIMMB#

9,10 DDR_A_RAS#

9,10 DDR_A_CAS#

9,10 DDR_A_WE#

DDR_A_ODT0

DDR_A_ODT1

DDR_B_ODT0

DDR_B_ODT1

W19

V15

U19

W15

M0_ODT0

M0_ODT1

M1_ODT0

M1_ODT1

DDR_CS0_DIMMA#

DDR_CS1_DIMMA#

DDR_CS0_DIMMB#

DDR_CS1_DIMMB#

T17

W16

U17

V16

M0_CS_L0

M0_CS_L1

M1_CS_L0

M1_CS_L1

DDR_A_RAS#

DDR_A_CAS#

DDR_A_WE#

U18

V19

V17

M_RAS_L

M_CAS_L

M_WE_L

B14

A15

A17

D18

A14

C14

C16

D16

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

M_DATA8

M_DATA9

M_DATA10

M_DATA11

M_DATA12

M_DATA13

M_DATA14

M_DATA15

C18

A19

B21

D20

A18

B18

A21

C20

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

M_DATA16

M_DATA17

M_DATA18

M_DATA19

M_DATA20

M_DATA21

M_DATA22

M_DATA23

C23

D23

F23

F22

C22

D22

F20

F21

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

M_DATA24

M_DATA25

M_DATA26

M_DATA27

M_DATA28

M_DATA29

M_DATA30

M_DATA31

H21

H23

K22

K21

G23

H20

K20

K23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

M_DATA32

M_DATA33

M_DATA34

M_DATA35

M_DATA36

M_DATA37

M_DATA38

M_DATA39

N23

P21

T20

T23

M20

P20

R23

T22

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

M_DATA40

M_DATA41

M_DATA42

M_DATA43

M_DATA44

M_DATA45

M_DATA46

M_DATA47

V20

V21

Y23

Y22

T21

U23

W23

Y21

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

M_DATA48

M_DATA49

M_DATA50

M_DATA51

M_DATA52

M_DATA53

M_DATA54

M_DATA55

Y20

AB22

AC19

AA18

AA23

AA20

AB19

Y18

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

M_DATA56

M_DATA57

M_DATA58

M_DATA59

M_DATA60

M_DATA61

M_DATA62

M_DATA63

AC17

Y16

AB14

AC14

AC18

AB18

AB15

AC15

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

M_VREF

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

9,10

9,10

9,10

9,10

9,10

9,10

9,10

9,10

DDR_A_D8 9,10

DDR_A_D9 9,10

DDR_A_D10 9,10

DDR_A_D11 9,10

DDR_A_D12 9,10

DDR_A_D13 9,10

DDR_A_D14 9,10

DDR_A_D15 9,10

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

9,10

9,10

9,10

9,10

9,10

9,10

9,10

9,10

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

9,10

9,10

9,10

9,10

9,10

9,10

9,10

9,10

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

9,10

9,10

9,10

9,10

9,10

9,10

9,10

9,10

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

9,10

9,10

9,10

9,10

9,10

9,10

9,10

9,10

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

9,10

9,10

9,10

9,10

9,10

9,10

9,10

9,10

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

9,10

9,10

9,10

9,10

9,10

9,10

9,10

9,10

+1.5V

R999

1K_0402_1%

+MEM_VREF

M23

9

9

10

10

M_DATA0

M_DATA1

M_DATA2

M_DATA3

M_DATA4

M_DATA5

M_DATA6

M_DATA7

9,10

9,10

9,10

9,10

9,10

9,10

9,10

9,10

R17

H19

J17

H18

H17

G17

H15

G18

F19

E19

T19

F17

E18

W17

E16

G15

9,10 DDR_A_BS#0

9,10 DDR_A_BS#1

9,10 DDR_A_BS#2

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

R1000

M_ZVDDIO_MEM_S

M22

2 39.2_0402_1%

C1280

+1.5V

1000P_0402_50V7K

Zacate-FT1_BGA_413P-T

R1001

1K_0402_1%

C1281

0.1U_0402_16V4Z

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

DDR SYSTEM MEMORY

9,10

9,10

9,10

9,10

9,10

9,10

9,10

9,10

9,10

9,10

9,10

9,10

9,10

9,10

9,10

9,10

Close to CPU within

1"

Compal Secret Data

Security Classification

Issued Date

2010-09-09

Deciphered Date

2010-09-09

Compal Electronics, Inc.

SCHEMATICS,

MB A6849

Size Document Number

Custom

4019BASheet 6 of 38

Monday, December 06, 2010

Date:

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

1

Rev

B

U1B

TDP1_TXP2

TDP1_TXN2

A10

B10

TDP1_TXP3

TDP1_TXN3

17 LCD_TXOUT2+

17 LCD_TXOUT2-

B5

A5

LTDP0_TXP0

LTDP0_TXN0

17 LCD_TXOUT1+

17 LCD_TXOUT1-

D6

C6

17 LCD_TXOUT0+

17 LCD_TXOUT0-

A6

B6

LTDP0_TXP2

LTDP0_TXN2

17 LCD_TXCLK+

17 LCD_TXCLK-

D8

C8

LTDP0_TXP3

LTDP0_TXN3

+3VS

R1016 1

2 1K_0402_5%

APU_ALERT#_R

11

11

APU_CLK

APU_CLK#

V2

V1

11

11

DISP_CLK

DISP_CLK#

D2

D1

R1017 1

2 1K_0402_5%

APU_PROCHOT#

R1018 1 @

2 1K_0402_5%

APU_SIC

R1020 1 @

2 1K_0402_5%

APU_SID

34

34

R1149 1

R1150 1

APU_PROCHOT#

R1151 1

13 APU_ALERT#

T26PAD

2

2

1

B

1K_0402_5%

10K_0402_5%

T25PAD

R1033

P3

P4

SIC

SID

T3

T4

RESET_L

PWROK

2

2

2

2

2

2

2

0_0402_5%

0_0402_5%

0_0402_5%

0_0402_5%

0_0402_5%

0_0402_5%

0_0402_5%

T13PAD

R1031 1

34 APU_VDD0_RUN_FB_L

R1032 1

34 APU_VDDNB_RUN_FB_L

1 H_THERMTRIP#

2 0_0402_5%

2 0_0402_5%

H_THERMTRIP# 12

SVC

SVD

APU_SIC

APU_SID

2 0_0402_5%

2 0_0402_5%

R1152 1

R1153 1

R1154 1

R1155 1

R1156 1

R1157 1

R1158 1

DISP_CLKIN_H

DISP_CLKIN_L

J1

J2

34 APU_VDDNB_RUN_FB_H

34 APU_VDD0_RUN_FB_H

Q165

APU_THERMTRIP#

R1025 1

CLKIN_H

CLKIN_L

APU_SVC

APU_SVD

2 0_0402_5%

APU_THERMTRIP#

2 0_0402_5% APU_ALERT#_R

APU_TDI

APU_TDO

APU_TCK

APU_TMS

APU_TRST#

APU_DBRDY

APU_DBREQ#

+3VS

R1064

APU_SVC

APU_SVD

LDT_RST#

H_PWRGD

11 LDT_RST#

11,34 H_PWRGD

LTDP0_TXP1

LTDP0_TXN1

U1

U2

T2

PROCHOT_L

THERMTRIP_L

ALERT_L

N2

N1

P1

P2

M4

M3

M1

TDI

TDO

TCK

TMS

TRST_L

DBRDY

DBREQ_L

F4

G1

F3

VDDCR_NB_SENSE

VDDCR_CPU_SENSE

VDDIO_MEM_S_SENSE

F1

VSS_SENSE

B4

W11

V5

TEST

2 0_0402_5% APU_PROCHOT#

DP MISC

D10

C10

VGA DAC

TDP1_TXP1

TDP1_TXN1

DISPLAYPORT 0

R1021 1

11 H_PROCHOT#

B9

A9

APU_DBREQ#

APU_SVC

APU_SVD

LDT_RST#

H_PWRGD

TEST_25_L

TEST36

CLK

300_0402_5%

1K_0402_5%

1K_0402_5%

300_0402_5%

300_0402_5%

510_0402_1%

1K_0402_5%

SER

1

2

2

1

1

2

2

CTRL

R1005 2

R1007 1

R1008 1

R1009 2

R1011 2

R1012 1

R1013 1

TDP1_TXP0

TDP1_TXN0

JTAG

A8

B8

DISPLAYPORT 1

R1003

+1.8VS

H3

DP_BLON

DP_DIGON

DP_VARY_BL

G2

H2

H1

TDP1_AUXP

TDP1_AUXN

B2

C2

RSVD_1

RSVD_2

RSVD_3

2 150_0402_1%

1

DP_BLON

UMA_ENVDD 17

TDP1_HPD

C1

R1065 1

LTDP0_AUXP

LTDP0_AUXN

A3

B3

LCD_EDID_CLK

LCD_EDID_DATA

LTDP0_HPD

D3

R1015 1

R1002 1

2 100K_0402_5%

R1014 1

2 0_0402_5% @ GMCH_INVT_PWM

GMCH_INVT_PWM 17

R1004 1

2 0_0402_5%

UMA_ENBKL 23

R1006 1

2 0_0402_5% @

R1010 1

2 0_0402_5%

GMCH_INVT_PWM

2 100K_0402_5%

LCD_EDID_CLK 17

LCD_EDID_DATA 17

2 10K_0402_5%

All LCD panel control by APU

+3VS

C12

D13

A12

B12

A13

B13

UMA_CRT_R

UMA_CRT_R 16

R987

2 150_0402_1% UMA_CRT_R

UMA_CRT_G

UMA_CRT_G 16

R988

2 150_0402_1% UMA_CRT_G

UMA_CRT_B

UMA_CRT_B 16

R989

2 150_0402_1% UMA_CRT_B

DAC_HSYNC

DAC_VSYNC

E1

E2

UMA_CRT_HSYNC

UMA_CRT_VSYNC

UMA_CRT_HSYNC 16

UMA_CRT_VSYNC 16

DAC_SCL

DAC_SDA

F2

D4

UMA_CRT_CLK

UMA_CRT_DATA

UMA_CRT_CLK 16

UMA_CRT_DATA 16

DAC_ZVSS

D12

TEST4

TEST5

TEST6

TEST14

TEST15

TEST16

TEST17

TEST18

TEST19

TEST25_H

TEST25_L

TEST28_H

TEST28_L

TEST31

TEST33_H

TEST33_L

TEST34_H

TEST34_L

TEST35

TEST36

TEST37

R1

R2

R6

T5

E4

K4

L1

L2

M2

K1

K2

L5

M5

M21

J18

J19

U15

T15

H4

N5

R5

DAC_RED

DAC_REDB

DAC_GREEN

DAC_GREENB

DAC_BLUE

DAC_BLUEB

TEST38

DMAACTIVE_L

R1019 1

2 499_0402_1%

PAD T3

PAD T4

PAD T5

TEST15

TEST_18

TEST_19

TEST25_H

TEST_25_L

TEST28_H

TEST28_L

TEST31

TEST33_H

TEST33_L

TEST34_H

TEST34_L

TEST35

TEST36

TEST37

PAD T6

PAD T7

@

R1022 1

2 1K_0402_5%

R1023 1

R1024 1

R1026 1

2 1K_0402_5%

2 1K_0402_5%

2 510_0402_1%

PAD T9

PAD T8

PAD T10

C1282

C1283

PAD T11

PAD T12

2 0.1U_0402_16V4Z

2 0.1U_0402_16V4Z

1

1

R1029 1

PAD T14

R1030 1

K3

T1

R1027 1

R1028 1

2 51_0402_1%

2 51_0402_1%

2 1K_0402_5%

@

2 1K_0402_5%

TEST35 for HDMI function

+1.8VS

TEST35

ALLOW_STOP# 11

R1034 1

2 1K_0402_5%

+1.8VS

Zacate-FT1_BGA_413P-T

MMBT3904_NL_SOT23-3

@ D94

2

DP_ZVSS

Disable

Enable

1

CH751H-40PT_SOD323-2

TR DMN66D0LDW-7 2N

R1035

10K_0402_5%

@

APU_SID

1

6

@

Q8A

DMN66D0LDW-7 2N_SOT363-6

1

R1050

EC_SMB_DA

1

R1040

1

R1044

+1.8VS

JHDT1

R1036

+1.8VS

Vgs(th): min 1.0V

Typ 1.6V

Max 2.0V

1K_0402_5%

+3VS

2

0_0402_5%

2

0_0402_5%

FCH_SID

EC_SMB_DA2

FCH_SID

12

EC_SMB_DA2 23

T0 FCH

HDT@

APU_TRST#

R1041 1

TO EC

R1042 2

R1045 2

R1047 2

2 0_0402_5% APU_TRST#_R

1 10K_0402_5%

1 10K_0402_5%

1 10K_0402_5%

2

0_0402_5%

1

3

5

7

9

11

13

15

17

19

1

3

5

7

9

11

13

15

17

19

CONN@

2

4

6

8

10

12

14

16

18

20

2

4

6

8

10

12

14

16

18

20

LDT_RST#_R

R1043 1 HDT@

APU_DBRDY_R R1046 1 HDT@

APU_DBREQ#_R R1048 1 HDT@

APU_TCK

R1037 2

1 1K_0402_5%

APU_TMS

R1038 2

1 1K_0402_5%

APU_TDI

R1039 2

1 1K_0402_5%

APU_TDO

H_PWRGD

2 0_0402_5% LDT_RST#

2 0_0402_5% APU_DBRDY

2 0_0402_5% APU_DBREQ# R1049 1

2 300_0402_5%

TEST_19

TEST_18

+1.8VS

ACES_88076-02001_20P

@

APU_SIC

A

4

@

EC_SMB_CK

Q8B

DMN66D0LDW-7 2N_SOT363-6

1

2

R1053

0_0402_5%

1

R1051

1

R1052

FCH_SIC

2

0_0402_5%

EC_SMB_CK2

2

0_0402_5%

FCH_SIC

12

EC_SMB_CK2 23

T0 FCH

A

TO EC

2010-09-09

Issued Date

Compal Electronics, Inc.

Compal Secret Data

Security Classification

2010-09-09

Deciphered Date

Title

SCHEMATICS, MB A6849

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS Custom

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

Document Number

Rev

B

4019BA

Sheet

Monday, December 06, 2010

1

of

38

U1D

C1289

2

G16

G19

E17

J16

L16

L19

N16

R16

R19

W18

U16

VDDIO_MEM_S_1

VDDIO_MEM_S_2

VDDIO_MEM_S_3

VDDIO_MEM_S_4

VDDIO_MEM_S_5

VDDIO_MEM_S_6

VDDIO_MEM_S_7

VDDIO_MEM_S_8

VDDIO_MEM_S_9

VDDIO_MEM_S_10

VDDIO_MEM_S_11

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

C1290

2

C1285

2

1U_0402_6.3V6K

+1.8VS

1

2

FBMA-L11-201209-221LMA30T_0805

1

+

C1286

2

2

10U_0805_10V6K

C1291

220U_B2_2.5VM_R25M

+1.8VS_DAC

+1.8VS

L85

1

2

1 FBMA-L11-201209-221LMA30T_0805

C1293

W9

VDD_18_DAC

POWER

10U_0805_10V6K

2

+1.05VS

+1.05VS_VDDPL

1U_0402_6.3V6K

DIS PLL

200mA

U11

VDDPL_10

1

C1294

0.1U_0402_16V4Z

L86

1

2

FBMA-L11-201209-221LMA30T_0805

C1296

C1295

2

C1297

220U_B2_2.5VM_R25M

10U_0805_10V6K

2

+1.05VS_VDD

5500mA-->20mil0.1U_0402_16V4Z

PCIE/IO/DDR3 Phy

L87

1

2

FBMA-L11-201209-221LMA30T_0805

1U_0402_6.3V6K

U13

W13

V12

T12

VDD_10_1

VDD_10_2

VDD_10_3

VDD_10_4

C1298

0.1U_0402_16V4Z

DDR3

2000mA

C1284

C1292

1U_0402_6.3V6K

GPU AND NB CORE

+1.5V

DAC

VDDCR_NB_1

VDDCR_NB_2

VDDCR_NB_3

VDDCR_NB_4

VDDCR_NB_5

VDDCR_NB_6

VDDCR_NB_7

VDDCR_NB_8

VDDCR_NB_9

VDDCR_NB_10

VDDCR_NB_11

VDDCR_NB_12

VDDCR_NB_13

VDDCR_NB_14

VDDCR_NB_15

VDDCR_NB_16

VDDCR_NB_17

VDDCR_NB_18

VDDCR_NB_19

VDDCR_NB_20

VDDCR_NB_21

VDDCR_NB_22

8000mA

U8

W8

U6

U9

W6

T7

V7

VDD_18_1

VDD_18_2

VDD_18_3

VDD_18_4

VDD_18_5

VDD_18_6

VDD_18_7

150mA

E8

E11

E13

F9

F12

G11

G13

H9

H12

K11

K13

L10

L12

L14

M11

M12

M13

N10

N12

N14

P11

P13

+APU_VDDNB

CPU CORE

VDDCR_CPU_1

VDDCR_CPU_2

VDDCR_CPU_3

VDDCR_CPU_4

VDDCR_CPU_5

VDDCR_CPU_6

VDDCR_CPU_7

VDDCR_CPU_8

VDDCR_CPU_9

VDDCR_CPU_10

VDDCR_CPU_11

VDDCR_CPU_12

VDDCR_CPU_13

VDDCR_CPU_14

VDDCR_CPU_15

C1288

0.1U_0402_16V4Z

1U_0402_6.3V6K

1

1

1

L84

C1287

68P_0402_50V8J

4500mA

2000mA

TSense/PLL/DP/PCIE/IO

E5

E6

F5

F7

G6

G8

H5

H7

J6

J8

L7

M6

M8

N7

R8

+APU_CORE

+1.8VS_VDD

1

1

1

C1302

C1300

C1301

1U_0402_6.3V6K

10U_0805_10V6K

2

2

2

C1299

2

1

C1303

2

10U_0805_10V6K

DP Phy/IO

A4

0.1U_0402_16V4Z

+APU_CORE

10U_0805_10V6K

1

C1313

2

C1315

0.1U_0402_16V4Z

0.1U_0402_16V4Z

+1.5V

C1317

10U_0805_10V6K

+APU_CORE

0.1U_0402_16V4Z

C1309

180P_0402_50V8J

+APU_VDDNB

0.1U_0402_16V4Z

C1316

10U_0805_10V6K

2

1

C1308

180P_0402_50V8J

10U_0805_10V6K

1

1

C1314

10U_0805_10V6K

2

1

C1307

C1312

10U_0805_10V6K

2

+APU_VDDNB

180P_0402_50V8J

Close to U1.A4 pin

C1306

C1311

0.1U_0402_16V4Z

1

C1318

10U_0805_10V6K

1

C1319

10U_0805_10V6K

1

C1320

10U_0805_10V6K

1

C1321

10U_0805_10V6K

C1322

2

C1323

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

C1324

3

C1326

0.1U_0402_16V4Z

C1327

C1328

+APU_VDDNB

330U_D2_2V_Y

1

1

C1331

C1332

C1333

C1334

C1335

1U_0402_6.3V6K 1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K 1U_0402_6.3V6K

2

2

2

2

2

+APU_CORE

C1336

C1338 +

C1337

2

330U_D2_2V_Y

+1.8VS_VDD

+1.8VS_DAC

1

1

C1344 +

C1345 +

@

330U_D2_2V_Y

C1342

+1.05VS_VDDPL

1U_0402_6.3V6K

330U_D2_2V_Y

C1343

0.1U_0402_16V4Z

0.1U_0402_16V4Z

+APU_CORE

+APU_VDDNB

C1330

2

2

1U_0402_6.3V6K

1

C1346

1

C1347

1U_0402_6.3V6K

+1.5V

+1.5V

C1348

2

1U_0402_6.3V6K

1

C1349

10U_0805_10V6K

1

C1350

10U_0805_10V6K

C1351

C1352

C1353

C1354

1U_0402_6.3V6K 1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

2

2

2

2

1

C1355

180P_0402_50V8J

1

C1339

180P_0402_50V8J

1

C1340

180P_0402_50V8J

+APU_VDDNB

C1357

180P_0402_50V8J

+1.05VS_VDD

+1.5V

C1363

0.1U_0402_16V4Z

2200P_0402_50V7K

C1362

68P_0402_50V8J

2200P_0402_50V7K

C1361

C1360

68P_0402_50V8J

0.1U_0402_16V4Z

1

C1364

+3VS

1

C1358

180P_0402_50V8J

C1359

0.1U_0402_16V4Z

C1365

C1366

4

0.1U_0402_16V4Z

Compal Secret Data

Security Classification

2010-09-09

Issued Date

2010-09-09

Deciphered Date

Title

Compal Electronics, Inc.

SCHEMATICS, MB A6849

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS Custom

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

C1341

180P_0402_50V8J

1

C1356

180P_0402_50V8J

1

+APU_CORE

0.1U_0402_16V4Z

C1325

3

C1329

180P_0402_50V8J

C1305

1U_0402_6.3V6K

+APU_CORE

10U_0805_10V6K

1

C1304

@

N13

N20

N22

P10

P14

R4

R7

R20

T6

T9

T11

T13

U4

U5

U7

U12

U20

U22

V8

V9

V11

V13

W1

W2

W4

W5

W7

W12

W20

Y5

Y7

Y9

Y11

Y13

Y15

Y17

Y19

AA4

AA22

AB2

AB5

AB9

AB13

AB17

AB21

AC5

AC9

AC13

A11

500mA

Zacate-FT1_BGA_413P-T

C1310

10U_0805_10V6K

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSSBG_DAC

Zacate-FT1_BGA_413P-T

+3VS

VDD_33

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

GND

A7

B7

B11

B17

B22

C4

D5

D7

D9

D11

D14

B15

D17

D19

E7

E9

E12

E20

F8

F11

F13

G4

G5

G7

G9

G12

G20

G22

H6

H11

H13

J4

J5

J7

J20

K10

K14

L4

L6

L8

L11

L13

L20

L22

M7

N4

N6

N8

N11

+1.8VS_VDD

U1C

Rev

B

4019BA

Sheet

Monday, December 06, 2010

E

of

38

+1.5V

+1.5V

JDDRL

DDR_A_D2

DDR_A_D3

DDR_A_D8

DDR_A_D9

6,10 DDR_A_DQS#1

6,10 DDR_A_DQS1

DDR_A_D10

DDR_A_D11

DDR_A_D16

DDR_A_D17

6,10 DDR_A_DQS#2

6,10 DDR_A_DQS2

DDR_A_D18

DDR_A_D19

DDR_A_D24

DDR_A_D25

DDR_A_DM3

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

139

141

143

145

147

149

151

153

155

157

159

161

163

165

167

169

171

173

175

177

179

181

183

185

187

189

191

193

195

197

199

201

203

CKE0

VDD1

NC1

BA2

VDD3

A12/BC#

A9

VDD5

A8

A5

VDD7

A3

A1

VDD9

CK0

CK0#

VDD11

A10/AP

BA0

VDD13

WE#

CAS#

VDD15

A13

S1#

VDD17

NCTEST

VSS27

DQ32

DQ33

VSS29

DQS#4

DQS4

VSS32

DQ34

DQ35

VSS34

DQ40

DQ41

VSS36

DM5

VSS37

DQ42

DQ43

VSS39

DQ48

DQ49

VSS41

DQS#6

DQS6

VSS44

DQ50

DQ51

VSS46

DQ56

DQ57

VSS48

DM7

VSS49

DQ58

DQ59

VSS51

SA0

VDDSPD

SA1

VTT1

205

G1

VSS1

DQ4

DQ5

VSS3

DQS#0

DQS0

VSS6

DQ6

DQ7

VSS8

DQ12

DQ13

VSS10

DM1

RESET#

VSS12

DQ14

DQ15

VSS14

DQ20

DQ21

VSS16

DM2

VSS17

DQ22

DQ23

VSS19

DQ28

DQ29

VSS21

DQS#3

DQS3

VSS24

DQ30

DQ31

VSS26

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

DDR_A_D4

DDR_A_D5

DDR_A_DQS#0 6,10

DDR_A_DQS0 6,10

DDR_A_D[0..63]

DDR_A_D6

DDR_A_D7

DDR_A_DM[0..7]

DDR_A_D[0..63]

6,10

DDR_A_DM[0..7]

6,10

1

DDR_A_D12

DDR_A_D13

DDR_A_MA[0..15]

DDR_A_DM1

DDR_A_MA[0..15] 6,10

DDR_RST# 6,10

DDR_A_D14

DDR_A_D15

DDR_A_D20

DDR_A_D21

DDR_A_DM2

DDR_A_D22

DDR_A_D23

DDR_A_D28

DDR_A_D29

+1.5V

+1.5V

DDR_A_DQS#3 6,10

DDR_A_DQS3 6,10

DDR_A_D30

DDR_A_D31

R310

1K_0402_1%

R48

1K_0402_1%

1

DDR_A_D26

DDR_A_D27

VREF_DQ

VSS2

DQ0

DQ1

VSS4

DM0

VSS5

DQ2

DQ3

VSS7

DQ8

DQ9

VSS9

DQS#1

DQS1

VSS11

DQ10

DQ11

VSS13

DQ16

DQ17

VSS15

DQS#2

DQS2

VSS18

DQ18

DQ19

VSS20

DQ24

DQ25

VSS22

DM3

VSS23

DQ26

DQ27

VSS25

DDR_A_DM0

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

C627

DDR_A_D0

DDR_A_D1

1000P_0402_50V7K

C626

0.1U_0402_16V4Z

+VREF_DQ

+VREF_DQ

DDR_A_MA3

DDR_A_MA1

6

6

DDR_A_CLK0

DDR_A_CLK#0

DDR_A_MA10

6,10 DDR_A_BS#0

6,10 DDR_A_WE#

6,10 DDR_A_CAS#

DDR_A_MA13

6 DDR_CS1_DIMMA#

DDR_A_D32

DDR_A_D33

6,10 DDR_A_DQS#4

6,10 DDR_A_DQS4

DDR_A_D34

DDR_A_D35

DDR_A_D40

DDR_A_D41

DDR_A_DM5

DDR_A_D42

DDR_A_D43

DDR_A_D48

DDR_A_D49

6,10 DDR_A_DQS#6

6,10 DDR_A_DQS6

DDR_A_D50

DDR_A_D51

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

R445

10K_0402_5%

1

2

R446

10K_0402_5%

2

C651

0.1U_0402_16V4Z

C650

+3VS

2.2U_0603_6.3V6K

DDR_A_DM7

2

1

206

G2

DDR_A_MA6

DDR_A_MA4

DDR_A_MA2

DDR_A_MA0

< Close to JDDRH & JDDRL >

DDR_A_CLK1 6

DDR_A_CLK#1 6

DDR_A_BS#1 6,10

DDR_A_RAS# 6,10

DDR_CS0_DIMMA# 6

DDR_A_ODT0 6

DDR_A_ODT1 6

+VREF_CA

DDR_A_D36

DDR_A_D37

DDR_A_DM4

DDR_A_D38

DDR_A_D39

DDR_A_D44

DDR_A_D45

+1.5V

0.1U_0402_16V4Z

2

C87

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

C88

C640

C641

1

0.1U_0402_16V4Z

DDR_A_DQS#5 6,10

DDR_A_DQS5 6,10

0.1U_0402_16V4Z

2

C642

1

0.1U_0402_16V4Z

C643

1

0.1U_0402_16V4Z

2

C644

1

0.1U_0402_16V4Z

C645

1

0.1U_0402_16V4Z

2

C646

C647

1

0.1U_0402_16V4Z

DDR_A_D46

DDR_A_D47

DDR_A_D52

DDR_A_D53

DDR_A_DM6

DDR_A_D54

DDR_A_D55

DDR_A_D60

DDR_A_D61

+0.75VS

DDR_A_DQS#7 6,10

DDR_A_DQS7 6,10

DDR_A_D62

DDR_A_D63

0.1U_0402_16V4Z

2

C665

MA_EVENT_L 6,10

FCH_SMDAT0 10,12

FCH_SMCLK0 10,12

C664

1

0.1U_0402_16V4Z

C961

2

4.7U_0603_6.3V6K

+0.75VS

4

TYCO_2-2013289-1

CONN@

Compal Secret Data

Security Classification

DIMM_A STD H:5.2 mm

<Address: A0 H>

2010-09-09

Issued Date

2010-09-09

Deciphered Date

Title

Compal Electronics, Inc.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS Custom

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

R315

1K_0402_1%

R49

1K_0402_1%

DDR_A_MA11

DDR_A_MA7

1

DDR_A_MA8

DDR_A_MA5

DDR_A_MA15

DDR_A_MA14

C649

DDR_A_MA12

DDR_A_MA9

+VREF_CA

DDR_CKE1 6,10

0.1U_0402_16V4Z

6,10 DDR_A_BS#2

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

202

204

C648

CKE1

VDD2

A15

A14

VDD4

A11

A7

VDD6

A6

A4

VDD8

A2

A0

VDD10

CK1

CK1#

VDD12

BA1

RAS#

VDD14

S0#

ODT0

VDD16

ODT1

NC2

VDD18

VREF_CA

VSS28

DQ36

DQ37

VSS30

DM4

VSS31

DQ38

DQ39

VSS33

DQ44

DQ45

VSS35

DQS#5

DQS5

VSS38

DQ46

DQ47

VSS40

DQ52

DQ53

VSS42

DM6

VSS43

DQ54

DQ55

VSS45

DQ60

DQ61

VSS47

DQS#7

DQS7

VSS50

DQ62

DQ63

VSS52

EVENT#

SDA

SCL

VTT2

1000P_0402_50V7K

6,10 DDR_CKE0

SCHEMATICS, MB A6849

Rev

B

4019BA

Sheet

Monday, December 06, 2010

E

of

38

+1.5V

+1.5V

JDDRH

DDR_A_DM0

DDR_A_D2

DDR_A_D3

DDR_A_D8

DDR_A_D9

6,9 DDR_A_DQS#1

6,9 DDR_A_DQS1

DDR_A_D10

DDR_A_D11

DDR_A_D16

DDR_A_D17

6,9 DDR_A_DQS#2

6,9 DDR_A_DQS2

DDR_A_D18

DDR_A_D19

DDR_A_D24

DDR_A_D25

DDR_A_DM3

DDR_A_D26

DDR_A_D27

6,9

2

DDR_CKE0

6,9 DDR_A_BS#2

DDR_A_MA12

DDR_A_MA9

DDR_A_MA8

DDR_A_MA5

DDR_A_MA3

DDR_A_MA1

6

6

DDR_B_CLK2

DDR_B_CLK#2

DDR_A_MA10

6,9 DDR_A_BS#0

6,9 DDR_A_WE#

6,9 DDR_A_CAS#

DDR_A_MA13

6 DDR_CS1_DIMMB#

DDR_A_D32

DDR_A_D33

6,9 DDR_A_DQS#4

6,9 DDR_A_DQS4

DDR_A_D34

DDR_A_D35

DDR_A_D40

DDR_A_D41

DDR_A_DM5

DDR_A_D42

DDR_A_D43

DDR_A_D48

DDR_A_D49

6,9 DDR_A_DQS#6

6,9 DDR_A_DQS6

DDR_A_D50

DDR_A_D51

DDR_A_D56

DDR_A_D57

DDR_A_DM7

DDR_A_D58

DDR_A_D59

10K_0402_5%

R448 1

2

+3VS

C681

2.2U_0603_6.3V6K

CRB

1

C680

2

0.1U_0402_16V4Z

R449

10K_0402_5%

VREF_DQ

VSS2

DQ0

DQ1

VSS4

DM0

VSS5

DQ2

DQ3

VSS7

DQ8

DQ9

VSS9

DQS#1

DQS1

VSS11

DQ10

DQ11

VSS13

DQ16

DQ17

VSS15

DQS#2

DQS2

VSS18

DQ18

DQ19

VSS20

DQ24

DQ25

VSS22

DM3

VSS23

DQ26

DQ27

VSS25

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

139

141

143

145

147

149

151

153

155

157

159

161

163

165

167

169

171

173

175

177

179

181

183

185

187

189

191

193

195

197

199

201

203

CKE0

VDD1

NC1

BA2

VDD3

A12/BC#

A9

VDD5

A8

A5

VDD7

A3

A1

VDD9

CK0

CK0#

VDD11

A10/AP

BA0

VDD13

WE#

CAS#

VDD15

A13

S1#

VDD17

NCTEST

VSS27

DQ32

DQ33

VSS29

DQS#4

DQS4

VSS32

DQ34

DQ35

VSS34

DQ40

DQ41

VSS36

DM5

VSS37

DQ42

DQ43

VSS39

DQ48

DQ49

VSS41

DQS#6

DQS6

VSS44

DQ50

DQ51

VSS46

DQ56

DQ57

VSS48

DM7

VSS49

DQ58

DQ59

VSS51

SA0

VDDSPD

SA1

VTT1

205

G1

VSS1

DQ4

DQ5

VSS3

DQS#0

DQS0

VSS6

DQ6

DQ7

VSS8

DQ12

DQ13

VSS10

DM1

RESET#

VSS12

DQ14

DQ15

VSS14

DQ20

DQ21

VSS16

DM2

VSS17

DQ22

DQ23

VSS19

DQ28

DQ29

VSS21

DQS#3

DQS3

VSS24

DQ30

DQ31

VSS26

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

CKE1

VDD2

A15

A14

VDD4

A11

A7

VDD6

A6

A4

VDD8

A2

A0

VDD10

CK1

CK1#

VDD12

BA1

RAS#

VDD14

S0#

ODT0

VDD16

ODT1

NC2

VDD18

VREF_CA

VSS28

DQ36

DQ37

VSS30

DM4

VSS31

DQ38

DQ39

VSS33

DQ44

DQ45

VSS35

DQS#5

DQS5

VSS38

DQ46

DQ47

VSS40

DQ52

DQ53

VSS42

DM6

VSS43

DQ54

DQ55

VSS45

DQ60

DQ61

VSS47

DQS#7

DQS7

VSS50

DQ62

DQ63

VSS52

EVENT#

SDA

SCL

VTT2

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

202

204

G2

206

DDR_A_D4

DDR_A_D5

DDR_A_DQS#0 6,9

DDR_A_DQS0 6,9

DDR_A_D[0..63]

DDR_A_D6

DDR_A_D7

DDR_A_DM[0..7]

DDR_A_D[0..63]

6,9

DDR_A_DM[0..7]

6,9

1

DDR_A_D12

DDR_A_D13

DDR_A_MA[0..15]

DDR_A_MA[0..15] 6,9

DDR_A_DM1

DDR_RST# 6,9

DDR_A_D14

DDR_A_D15

DDR_A_D20

DDR_A_D21

DDR_A_DM2

DDR_A_D22

DDR_A_D23

DDR_A_D28

DDR_A_D29

DDR_A_DQS#3 6,9

DDR_A_DQS3 6,9

DDR_A_D30

DDR_A_D31

DDR_CKE1 6,9

DDR_A_MA15

DDR_A_MA14

DDR_A_MA11

DDR_A_MA7

DDR_A_MA6

DDR_A_MA4

DDR_A_MA2

DDR_A_MA0

DDR_B_CLK3 6

DDR_B_CLK#3 6

DDR_A_BS#1 6,9

DDR_A_RAS# 6,9

DDR_CS0_DIMMB# 6

DDR_B_ODT0 6

DDR_B_ODT1 6

+VREF_CA

DDR_A_D36

DDR_A_D37

DDR_A_DM4

DDR_A_D38

DDR_A_D39

DDR_A_D44

DDR_A_D45

C679

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

1000P_0402_50V7K

C652 C653

2

DDR_A_D0

DDR_A_D1

C678

0.1U_0402_16V4Z

1000P_0402_50V7K

0.1U_0402_16V4Z

+VREF_DQ

DDR_A_DQS#5 6,9

DDR_A_DQS5 6,9

DDR_A_D46

DDR_A_D47

+1.5V

DDR_A_D52

DDR_A_D53

0.1U_0402_16V4Z

2

DDR_A_DM6

C666

1

0.1U_0402_16V4Z

DDR_A_D54

DDR_A_D55

0.1U_0402_16V4Z

2

C667

1

C668

1

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

C669

C670

C671

1

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

C672

1

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

C673

C674

C677

1

0.1U_0402_16V4Z

DDR_A_D60

DDR_A_D61

C128 Co-layout with C86

DDR_A_DQS#7 6,9

DDR_A_DQS7 6,9

+0.75VS

+1.5V

DDR_A_D62

DDR_A_D63

0.1U_0402_16V4Z

2

C676

MA_EVENT_L 6,9

FCH_SMDAT0 9,12

FCH_SMCLK0 9,12

1

0.1U_0402_16V4Z

+0.75VS

C675

1

1

C925

2

4.7U_0603_6.3V6K

+1.5V

@

C86 + 330U_SX_2VY~D

C128

2

390U_2.5V_M_R10

4

Place near DIMM2

LOTES_AAA-DDR-111-K01

CONN@

only one 4.7k

Compal Secret Data

Security Classification

DIMM_B STD H:9.2 mm

<Address: A4 H>

2010-09-09

Issued Date

2010-09-09

Deciphered Date

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS Custom

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

Compal Electronics, Inc.

SCHEMATICS, MB A6849

Rev

B

4019BA

Sheet

Monday, December 06, 2010

E

10

of

38

T15

PAD

150P_0402_50V8J

C1367 1

2

U22E

APU_CLK_R

APU_CLK#_R

PCIE_RCLKP/NB_LNK_CLKP

PCIE_RCLKN/NB_LNK_CLKN

U29

U28

NB_DISP_CLKP

NB_DISP_CLKN

T26

T27

NB_HT_CLKP

NB_HT_CLKN

V21

T21

CPU_HT_CLKP

CPU_HT_CLKN

V23

T23

SLT_GFX_CLKP

SLT_GFX_CLKN

L29

L28

GPP_CLK0P

GPP_CLK0N

N29

N28

CLK_PCIE_MCARD2_R

CLK_PCIE_MCARD2#_R

M29

M28

GPP_CLK2P

GPP_CLK2N

19 CLK_PCIE_LAN

19 CLK_PCIE_LAN#

R1068 1

R1069 1

2 0_0402_5%

2 0_0402_5%

CLK_PCIE_LAN_R

CLK_PCIE_LAN#_R

T25

V25

GPP_CLK3P

GPP_CLK3N

L24

L23

GPP_CLK4P

GPP_CLK4N

LAN

+3VALW

GPP_CLK6P

GPP_CLK6N

PLT_RST#

N26

N27

GPP_CLK7P

GPP_CLK7N

T29

T28

GPP_CLK8P

GPP_CLK8N

CLK_48M_CR

2

22_0402_5%

L25

14M_25M_48M_OSC

25M_CLK_X1

L26

25M_X1

PLT_RST# 18,19,23,24

R1071

8.2K_0402_5%

NC7SZ08P5X_NL_SC70-5

R1072

20 CLK_48M_CR_R

1

RC8

0_0402_5%

25M_CLK_X2

C1380

22P_0402_50V8J

2

1

L27

25M_X2

Y7

1

PAD T18

FCH_CLKRUN

AJ6

AG6

AG4

AJ4

34

FCH_32KHI

1 22P_0402_50V8J

NC

OSC

NC

OSC

R1060

20M_0402_5%

1 22P_0402_50V8J

FCH_32KHO

@

R1063

2

10K_0402_5%

@ PJ29

PASSWD_CLEAR#

R1159 1

2 10K_0402_5%

G21

H21

K19

G22

J24

ALLOW_STOP#

H_PROCHOT#

H_PWRGD

32K_X1

C1

FCH_32KHI

32K_X2

C2

FCH_32KHO

RTCCLK

INTRUDER_ALERT_L

VDDBT_RTC_G

D2

B2

B1

+3VS

Reserve PJ29 and add R1159 pull high on 10/26

JUMP_43X79

R1070 1

LPC_CLK1 15

LPC_AD0 18,23,24

LPC_AD1 18,23,24

LPC_AD2 18,23,24

LPC_AD3 18,23,24

LPC_FRAME# 18,23,24

2 22_0402_5%

2

C1378

1

CLK_PCI_EC

15,18,23,24

22P_0402_50V8J

SERIRQ 23,24

ALLOW_STOP# 7

H_PROCHOT# 7

H_PWRGD 7,34

3

LDT_RST#

LDT_RST# 7

RTC_CLK 23

+FCH_VBAT

+3VL

+RTCVCC_R

+RTCVCC

D92

+RTCBATT_R

2

R1074

1

1 120_0402_5%

R1075

1

2

120_0402_5%

C1382

2

25M_CLK_X2

2

1U_0402_6.3V6K

22P_0402_50V8J

J1

@ JUMP_43X39

+RTCBATT

1

R1076

3

C1383

H_PWRGD_L

C1377 2

PAD T17

C1381

25MHZ_20PF_7A25000012

2

Q164

2N7002_SOT23-3

HUDSON-M1_BGA_605P-T

R1073

1M_0402_5%

32.768KHZ_12.5PF_Q13MC14610002

25M_CLK_X1

RTC

Reserve U56 and put R1072 on 9/20

H_PWRGD

Y6

CLK_PCI_EC1

LPC_CLK1

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

LPC_FRAME#

ALLOW_LDTSTP/DMA_ACTIVE_L

PROCHOT_L

LDT_PG

LDT_STP_L

LDT_RST_L

15

15

15

15

15

15

15

C1376 2

H24

H25

J27

J26

H29

H28

G28

J25

AA18

AB19

LPCCLK0

LPCCLK1

LAD0

LAD1

LAD2

LAD3

LFRAME_L

LDRQ0_L

LDRQ1_L/CLK_REQ6_L/GPIO49

SERIRQ/GPIO48

CPU

GPP_CLK5P

GPP_CLK5N

P29

P28

P25

M25

U56

A_RST#

C1379

2

1

0.1U_0402_16V4Z

2 B

INTE_L/GPIO32

INTF_L/GPIO33

INTG_L/GPIO34

INTH_L/GPIO35

LPC

18 CLK_PCIE_MCARD2

18 CLK_PCIE_MCARD2#

2 0_0402_5%

2 0_0402_5%

PCI_AD23

PCI_AD24

PCI_AD25

PCI_AD26

PCI_AD27

PCI_AD28

PCI_AD29

2

JRTC1

1K_0402_5%

CHN202UPT_SC70-3

WLAN

GPP_CLK1P

GPP_CLK1N

R1066 1

R1067 1

CLOCK GENERATOR

M23

P23

PCI_AD23

PCI_AD24

PCI_AD25

PCI_AD26

PCI_AD27

PCI_AD28

PCI_AD29

GPP_RX0P

GPP_RX0N

GPP_RX1P

GPP_RX1N

GPP_RX2P

GPP_RX2N

GPP_RX3P

GPP_RX3N

+3VS

R1057

10K_0402_5%

AA22

Y21

AA25

AA24

W23

V24

W24

W25

+1.8VS

GPP_TX0P

GPP_TX0N

GPP_TX1P

GPP_TX1N

GPP_TX2P

GPP_TX2N

GPP_TX3P

GPP_TX3N

2 0_0402_5%

2 0_0402_5%

PCIE_CALRP

PCIE_CALRN

AA28

AA29

Y29

Y28

Y26

Y27

W28

W29

PAD T16

15

15

15

15

R1061 1

R1062 1

APU_CLK

APU_CLK#

DISP_CLK_R

DISP_CLK#_R

AD29

AD28

V2

AA1

AA4

AA3

AB1

AA5

AB2

AB6

AB5

AA6

AC2

AC3

AC4

AC1

AD1

AD2

AC6

AE2

AE1

AF8

AE3

AF1

AG1

AF2

AE9

AD9

AC11

AF6

AF4

AF3

AH2

AG2

AH3

AA8

AD5

AD8

AA10

AE8

AB9

AJ3

AE7

AC5

AF5

AE6

AE4

AE11

AH5

AH4

AC12

AD12

AJ5

AH6

AB12

AB11

AD7

PCI_CLK1

PCI_CLK2

PCI_CLK3

PCI_CLK4

2 0_0402_5%

2 0_0402_5%

UMI_RX0P

UMI_RX0N

UMI_RX1P

UMI_RX1N

UMI_RX2P

UMI_RX2N

UMI_RX3P

UMI_RX3N

PCI_CLK1

PCI_CLK2

PCI_CLK3

PCI_CLK4

7

7

590_0402_1%

2K_0402_1%

AE24

AE23

AD25

AD24

AC24

AC25

AB25

AB24

PCIRST_L

AD0/GPIO0

AD1/GPIO1

AD2/GPIO2

AD3/GPIO3

AD4/GPIO4

AD5/GPIO5

AD6/GPIO6

AD7/GPIO7

AD8/GPIO8

AD9/GPIO9

AD10/GPIO10

AD11/GPIO11

AD12/GPIO12

AD13/GPIO13

AD14/GPIO14

AD15/GPIO15

AD16/GPIO16

AD17/GPIO17

AD18/GPIO18

AD19/GPIO19

AD20/GPIO20

AD21/GPIO21

AD22/GPIO22

AD23/GPIO23

AD24/GPIO24

AD25/GPIO25

AD26/GPIO26

AD27/GPIO27

AD28/GPIO28

AD29/GPIO29

AD30/GPIO30

AD31/GPIO31

CBE0_L

CBE1_L

CBE2_L

CBE3_L

FRAME_L

DEVSEL_L

IRDY_L

TRDY_L

PAR

STOP_L

PERR_L

SERR_L

REQ0_L

REQ1_L/GPIO40

REQ2_L/CLK_REQ8_L/GPIO41

REQ3_L/CLK_REQ5_L/GPIO42

GNT0_L

GNT1_L/GPO44

GNT2_L/GPO45

GNT3_L/CLK_REQ7_L/GPIO46

CLKRUN_L

LOCK_L

W2

W1

W3

W4

Y1

R1058 1

R1059 1

DISP_CLK

DISP_CLK#

1

1

UMI_TX0P

UMI_TX0N

UMI_TX1P

UMI_TX1N

UMI_TX2P

UMI_TX2N

UMI_TX3P

UMI_TX3N

PCICLK0

PCICLK1/GPO36

PCICLK2/GPO37

PCICLK3/GPO38

PCICLK4/14M_OSC/GPO39

PCI I/F

7

7

2

2

PCIE_RST_L

A_RST_L

AD26

AD27

AC28

AC29

AB29

AB28

AB26

AB27

R1055

R1056

+PCIE_VDDR

UMI_RX0P_C

UMI_RX0N_C

UMI_RX1P_C

UMI_RX1N_C

UMI_RX2P_C

UMI_RX2N_C

UMI_RX3P_C

UMI_RX3N_C

UMI_TX0P

UMI_TX0N

UMI_TX1P

UMI_TX1N

UMI_TX2P

UMI_TX2N

UMI_TX3P

UMI_TX3N

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

5

5

5

5

5

5

5

5

1

1

1

1

1

1

1

1

P1

L1

UMI_RX0P

UMI_RX0N

UMI_RX1P

UMI_RX1N

UMI_RX2P

UMI_RX2N

UMI_RX3P

UMI_RX3N

C1368 2

C1369 2

C1370 2

C1371 2

C1372 2

C1373 2

C1374 2

C1375 2

1 33_0402_5%

PCI EXPRESS I/F

5

5

5

5

5

5

5

5

R1054

PCI CLKS

A_RST#

0.1U_0402_16V4Z

SUYIN_060003HA002G202ZL

Compal Secret Data

Security Classification

Issued Date

2010-09-09

Deciphered Date

2010-09-09

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

C

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

Compal Electronics, Inc.

SCHEMATICS, MB A6849

Document Number

Rev

B

4019BA

Monday, December 06, 2010

E

Sheet

11

of

38

+3VALW

U22A

1

R1079

LAN_CLKREQ#

10K_0402_5%

@

2

R1081

1 EC_RSMRST#

100K_0402_5%

23

@

@

@

KB_RST#

KB_RST#

C1236

0.1U_0402_16V4Z

+3VALW

R1077 1

PM_SLP_S3#

PM_SLP_S5#

PBTN_OUT#

SB_PWRGD

PAD

PAD

PAD

T20

T19

T21

23

GATEA20

23

23

EC_SCI#

EC_SMI#

FCH_TEST0

FCH_TEST1

FCH_TEST2

GATEA20

EC_SCI#

EC_SMI#

2 10K_0402_5%

FCH_PCIE_WAKE

19 FCH_PCIE_WAKE

H_THERMTRIP#

NB_PWRGD

7 H_THERMTRIP#

EC_RSMRST#

23 EC_RSMRST#

LAN_CLKREQ#

19 LAN_CLKREQ#

+3VS

2.2K_0402_5% FCH_SMCLK0

R1083

2.2K_0402_5% FCH_SMDAT0

R1084

2.2K_0402_5%

NB_PWRGD

Change R1085 to 10 ohm and R1088 to 10pF on 11/22 for EMC request

USB_OC#0

18,23 USB_OC#0

1

10_0402_5%

R1086

21 AZ_SDOUT_HD

15 AZ_SDOUT_HD_R

21 AZ_SDIN0_HD

33_0402_5%

21 AZ_BITCLK_HD

1

10P_0402_50V8J

R1088

2

R1090

R1091

21 AZ_SYNC_HD

21 AZ_RST_HD#

1

1

2

2

33_0402_5%

33_0402_5%

G19

USB_FSD1P/GPIO186

USB_FSD1N

J10

H11

USB_FSD0P/GPIO185

USB_FSD0N

H9

J8

CLK_REQ4_L/SATA_IS0_L/GPIO64

CLK_REQ3_L/SATA_IS1_L/GPIO63

SMARTVOLT1/SATA_IS2_L/GPIO50

CLK_REQ0_L/SATA_IS3_L/GPIO60

SATA_IS4_L/FANOUT3/GPIO55

SATA_IS5_L/FANIN3/GPIO59

SPKR_GPIO66

SCL0_GPIO43

SDA0_GPIO47

SCL1_GPIO227

SDA1_GPIO228

CLK_REQ2_L/FANIN4_GPIO62

CLK_REQ1_L/FANOUT4_GPIO61

IR_LED_L/LLB_L/GPIO184

SMARTVOLT2/SHUTDOWN_L/GPIO51

DDR3_RST_L/GEVENT7_L

GBE_LED0/GPIO183

GBE_LED1/GEVENT9_L

GBE_LED2/GEVENT10_L

GBE_STAT0/GEVENT11_L

CLK_REQG_L/GPIO65_OSCIN

H3

D1

E4

D4

E8

F7

E7

F8

BLINK/USB_OC7_L/GEVENT18_L

USB_OC6_L/IR_TX1/GEVENT6_L

USB_OC5_L/IR_TX0/GEVENT17_L

USB_OC4_L/IR_RX0/GEVENT16_L

USB_OC3_L/AC_PRES/TDO/GEVENT15_L

USB_OC2_L/TCK/GEVENT14_L

USB_OC1_L/TDI/GEVENT13_L

USB_OC0_L/TRST_L/GEVENT12_L

M3

N1

L2

M2

M1

M4

N2

P2

AZ_BITCLK

AZ_SDOUT

AZ_SDIN0/GPIO167

AZ_SDIN1/GPIO168

AZ_SDIN2/GPIO169

AZ_SDIN3/GPIO170

AZ_SYNC

AZ_RST_L

F11

E11

USB_HSD11P

USB_HSD11N

E14

E12

USB_HSD10P

USB_HSD10N

J12

J14

USB_HSD9P

USB_HSD9N

A13

B13

USB_HSD8P

USB_HSD8N

D13

C13

USB_HSD7P

USB_HSD7N

G12

G14

USB20_P7

USB20_N7

USB_HSD6P

USB_HSD6N

G16

G18

USB20_P6

USB20_N6

USB_HSD5P

USB_HSD5N

D16

C16

USB20_P5

USB20_N5

USB_HSD4P

USB_HSD4N

B14

A14

USB_HSD3P

USB_HSD3N

E18

E16

USB_HSD2P

USB_HSD2N

J16

J18

USB_HSD1P

USB_HSD1N

B17

A17

USB20_P1

USB20_N1

USB_HSD0P

USB_HSD0N

A16

B16

USB20_P0

USB20_N0

SCL2/GPIO193

SDA2/GPIO194

SCL3_LV/GPIO195

SDA3_LV/GPIO196

EC_PWM0/EC_TIMER0/GPIO197

EC_PWM1/EC_TIMER1/GPIO198

EC_PWM2/EC_TIMER2/GPIO199

EC_PWM3/EC_TIMER3/GPIO200

D25

F23

B26

E26

F25

E22

F22

E21

GPIO193

GPIO194

FCH_SIC

FCH_SID

KSI_0/GPIO201

KSI_1/GPIO202

KSI_2/GPIO203

KSI_3/GPIO204

KSI_4/GPIO205

KSI_5/GPIO206

KSI_6/GPIO207

KSI_7/GPIO208

G24

G25

E28

E29

D29

D28

C29

C28

GPIO201

2

2

1

10K_0402_5%

1

10K_0402_5%

1

10K_0402_5%

GBE_COL

GBE_MDIO

R1095

10K_0402_5%

@

GBE_CRS

GBE_RXERR

GBE_RXERR

KSO_0/GPIO209

KSO_1/GPIO210

KSO_2/GPIO211

KSO_3/GPIO212

KSO_4/GPIO213

KSO_5/GPIO214

KSO_6/GPIO215

KSO_7/GPIO216

KSO_8/GPIO217

KSO_9/GPIO218

KSO_10/GPIO219

KSO_11/GPIO220

KSO_12/GPIO221

KSO_13/GPIO222

KSO_14/GPIO223

KSO_15/GPIO224

KSO_16/GPIO225

KSO_17/GPIO226

B28

A27

B27

D26

A26

C26

A24

B25

A25

D24

B24

C24

B23

A23

D22

C22

A22

B22

+3VALW

R1099

1 CIR_EN#

10K_0402_5%

GBE_PHY_INTR

@

+3VALW

CIR_EN#

1

R1101

1

R1102

1

R1103

2 @

100K_0402_5%

2

2.2K_0402_5%

2

2.2K_0402_5%

EC_LID_OUT#

FCH_SIC

FCH_SID

E23

E24

F21

G29

PS2_DAT/SDA4/GPIO187

PS2_CLK/SCL4/GPIO188

SPI_CS2_L/GBE_STAT2/GPIO166

FC_RST_L/GPO160

D27

F28

F29

E27

PS2KB_DAT/GPIO189

PS2KB_CLK/GPIO190

PS2M_DAT/GPIO191

PS2M_CLK/GPIO192

EHCI13 / OHCI3

EHCI2 / OHCI2

USB20_P7 20

USB20_N7 20

USB-7 Card reader

USB20_P6 18

USB20_N6 18

USB-6 WLAN

USB20_P5 17

USB20_N5 17

USB-5 Int Camera

2

EHCI1 / OHCI1

<Wake Up support>

USB20_P1 18

USB20_N1 18

USB-1 Right side

USB20_P0 18

USB20_N0 18

USB-0 Right side

R1087 1

R1089 1

FCH_SIC

FCH_SID

FCH_EC_PWM2 15

FCH_EC_PWM3 15

GPIO201 for UMA and DIS option

+3VALW

GPIO201

R1100

10K_0402_5%

DIS

Pull up

UMA

DEFAULT

GPIO201

HUDSON-M1_BGA_605P-T

FCH_SMCLK1

2

2.2K_0402_5%

2

2.2K_0402_5%

Pull down

Toshiba AMD platform version

R1104

10K_0402_5%

2

1

R1105

1

R1106

SPI and LPC STRAP PIN

2 10K_0402_5%

2 10K_0402_5%

7

7

R1098

R1094

10K_0402_5%

35ohm

R1097

GBE_PHY_INTR

R1096

GBE_MDIO

1

10K_0402_5%

1

10K_0402_5%

GBE LAN

R1093

GBE_COL

GBE_CRS

GBE_MDCK

GBE_MDIO

GBE_RXCLK

GBE_RXD3

GBE_RXD2

GBE_RXD1

GBE_RXD0

GBE_RXCTL/RXDV

GBE_RXERR

GBE_TXCLK

GBE_TXD3

GBE_TXD2

GBE_TXD1

GBE_TXD0

GBE_TXCTL/TXEN

GBE_PHY_PD

GBE_PHY_RST_L

GBE_PHY_INTR

Close to SB within 1"

B12

A12

EMBEDDED CTRL

R1092

3

T1

T4

L6

L5

T9

U1

U3

T2

U2

T5

V5

P5

M5

P9

T7

P7

M7

P4

M9

V7

2

R1080

OHCI4

USB_HSD12P

USB_HSD12N

+3VALW

GBE_COL

GBE_CRS

USB_RCOMP 1

11.8K_0402_1%

USB_HSD13P

USB_HSD13N

RSMRST_L

HD AUDIO

R1085

A10

USB_RCOMP

USB OC

EC_LID_OUT#

23 EC_LID_OUT#

USBCLK/14M_25M_48M_OSC

USB 2.0

G1

AD19

AA16

AB21

AC18

AF20

AE19

AF19

AD22

AE22

F5

F4

AH21

AB18

E1

AJ21

H4

D5

D7

G5

K3

AA20

PCI_PME_L/GEVENT4_L

RI_L/GEVENT22_L

SPI_CS3_L/GBE_STAT1/GEVENT21_L

SLP_S3_L

SLP_S5_L

PWR_BTN_L

PWR_GOOD

SUS_STAT_L

TEST0

TEST1/TMS

TEST2

GA20IN/GEVENT0_L

KBRST_L/GEVENT1_L

LPC_PME_L/GEVENT3_L

LPC_SMI_L/GEVENT23_L

GEVENT5_L

SYS_RESET_L/GEVENT19_L

WAKE_L/GEVENT8_L

IR_RX1/GEVENT20_L

THRMTRIP_L/SMBALERT_L/GEVENT2_L

NB_PWRGD

GPIO

R1082

PCH_SPKR

FCH_SMCLK0

FCH_SMDAT0

FCH_SMCLK1

FCH_SMDAT1

21

PCH_SPKR

9,10 FCH_SMCLK0

9,10 FCH_SMDAT0

18 FCH_SMCLK1

18 FCH_SMDAT1

18 CLKREQ_MCARD2#

J2

K1

D3

F1

H1

F2

H5

G6

B3

C4

F6

AD21

AE21

K2

J29

H2

J1

H6

F3

J6

AC19

USB 1.1

23

23

23

23

PM_SLP_S3#

PM_SLP_S5#

PBTN_OUT#

SB_PWRGD

FCH_PCIE_WAKE

10K_0402_5%

USB MISC

ACPI/WAKE UP EVENTS

1

R1078

FCH_SMDAT1

Compal Secret Data

Security Classification

2010-09-09

Issued Date

2010-09-09

Deciphered Date

Title

Compal Electronics, Inc.