Documente Academic

Documente Profesional

Documente Cultură

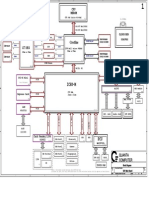

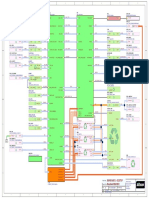

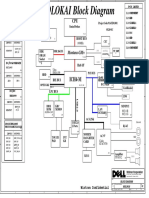

50Mhz Clock Out Generate by IP101A: Bandgap Resistor

Încărcat de

hungtranTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

50Mhz Clock Out Generate by IP101A: Bandgap Resistor

Încărcat de

hungtranDrepturi de autor:

Formate disponibile

5

DVDD33

U1

MDC

MDIO

TXD0

TXD1

50MHz CLOCK OUT

Generate by IP101A

DVDD33

25

26

6

5

4

3

TX_EN

2

REFCLK_IP101A 7

CRS_DV

22

RXD0

21

RXD1

20

19

18

16

COL/RMII

1

23

RX_ER

24

X1_INPUT

46

X2_OUTPUT

47

P3 REFCLK_IP101A

50MHz_CLKOUT

P3 50MHz_CLKOUT

R3

5.1k

Set IP101A

to RMII Mode

R4

5.1k

AVDD33

MDC

MDIO

TXD0

TXD1

TXD2

TXD3

TX_EN

REF_CLK

CRS_DV

RXD0

RXD1

RXD2

RXD3

C50M_O

COL

CRS/LEDMOD

RX_ER

X1

X2

DVDD33

5.1k INT

*

P3 PHYAD0/LED0

P3 PHYAD1/LED1

P3 PHYAD2/LED2

P3 PHYAD3/LED3

P3 PHYAD4/LED4

PHYAD0/LED0

PHYAD1/LED1

PHYAD2/LED2

PHYAD3/LED3

PHYAD4/LED4

use 25M crystal

X2_OUTPUT

14

48

DVDD33

INTR

9

10

12

13

15

PHYAD0/LED0

PHYAD1/LED1

PHYAD2/LED2

PHYAD3/LED3

PHYAD4/LED4

11

17

45

DGND

DGND

DGND

X1_INPUT

AVDD33

REGIN

REGOUT

AVDD33

REGIN

REGOUT

36

8

32

AGND

AGND

29

35

ISET

28

MDI_RP

MDI_RN

31

30

MDI_RP

MDI_RN

MDI_TN

MDI_TP

33

34

MDI_TN

MDI_TP

TEST_ON

27

AN_ENA

DPLX

SPD

RPTR

APS

ISOL

MII/SNIB

37

38

39

40

41

43

44

RESET_N

42

IP101A

DVDD33

R5

R1

5.1K

REGOUT P2

D

BANDGAP

RESISTOR

JP1

R2

6.19K/1%

1

AN_ENA

DPLX

SPD

RPTR

APS

ISOL

MII/SNIB

1

2

3

4

5

6

7

8

9

10

MDI_RP P2

MDI_RN P2

MDI_TN P2

MDI_TP P2

TP1

1

1

1

1

1

1

1

MDIO

MDC

RXD1

RXD0

CRS_DV

RX_ER

TX_EN

TXD0

TXD1

COL/RMII

HEADER 10

TP2

TP3

TP4

TP5

TP6

TP7

TP8

RMII Signals

Hardwire Configuration network:

IP101A LQFP48

Y1

R6

33R

Pin48 could be short VDD33 if

interrupt funtion is not

used.

25MHZ

C1

C2

30pF

30pF

JP2

1

2

1. This configuration shows

Enable: Auto negotiation, Full duplex, 100Mbps,

Link Down Power Saving, RMII interface

Disable: Isolate, Repeater mode

2. These senven configuration pins could be connected

to VDD or GND directly.

RESET_N

R7

0

HEADER 2/SM

RESET_N

R9

0

DVDD33

CRYSTAL

as close as to chip

R8

470K

C3

0.1U

VDD33

L1

MLB-160808-1000A-N2, 1.0ohm, 100mA

AVDD33

VDD33

P2 REGOUT

REGOUT

0R

+

C9

0.1uF

REGIN

0R

+

C5

0.1uF

C4

22uF

C6

0.1uF

C7

0.01uF

**

C10

0.1uF

As close to IP101A

Pin36 as possible

R10

**

L3

MLB-160808-0450B-N3, 0.5ohm, 100mA

L2

C8

10uF

DVDD33

As close to IP101A

Pin32 as possible

As close to IP101A

Pin14 as possible

As close to IP101A

Pin8 as possible

** Bead should be placed as close to IP101A

as possible and in the same side as IP101A.

IC Plus Semiconductor Corporation

Title

Size

B

Date:

5

* : Optional ,but recommended

www.BDTIC.com/ICplus

IP101A

Chip Circuit Diagram

Document Number

RMII UTP

Wednesday, April 30, 2008

Sheet

1

of

Rev

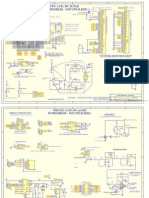

C11

.1u

C12

1n/2KV/1206

R11

49.9(1%)

R12

49.9(1%)

U2

U3

P1 MDI_RN

RD-

RX-

CT

CT

10

RD+

RX+

11

P1 MDI_RP

P1 MDI_TN

TD-

TX-

14

CT

CT

15

TD+

TX+

16

P1 MDI_TP

TS8121C

R13

R14

49.9(1%) 49.9(1%)

C13

1n/2KV/1206

TX+

TX-

RX+

N/C

N/C

RX-

N/C

N/C

GND

RJ8-45

R15

75

R16

75

R17

75

R18

75

C14

.1u

C15

R19

0

R20

0

Only 1 resister is needed

if 2 CT of transformer

have been shorted inside.

REGOUT

C16

C17

0.01U

0.1U

C18

0.01U

1n/2KV/1206

REGOUT P1

C19

0.1U

IC Plus Semiconductor Corporation

Title

IP101A Chip Circuit Diagram

www.BDTIC.com/ICplus

3

Size

A

Document Number

Date:

Wednesday, April 30, 2008

RMII UTP

2

Sheet

of

1

Rev

DC 5V INPUT ONLY

VDD5V

LED and PHY address Configuration

L4

BEAD

CN1

+5V

3

1

2

R21

POWERJACK

This schematic sets PHY address to

00001b.

330R

D1

DIODE

DVDD33

Z1

RLED

L5

BEAD

R22

P1 PHYAD0/LED0

R23

5.1K

D2

510 ohm

"Voltage 3.3V"

VDD5V

U4

3

VIN

ADJ(GND)

C20

220uF

LT1086CT

VOUT

OUT

LED

R24

VDD33

P1 PHYAD1/LED1

L6

1U, 50-100OHM@100-1000MHZ

3.3V

D3

5.1K

R25

C

C21

220uF

510 ohm

LED

C22

10nF

C23

0.1uF

R26

P1 PHYAD2/LED2

R27

D4

110R/1%

LED

R29

182R/1%

5.1K

R28

510 ohm

R30

P1 PHYAD3/LED3

D5

5.1K

LED

R31

510 ohm

R32

CLOCK generate by IP101A

P1 PHYAD4/LED4

D6

5.1K

R33

UZ1

P1 50MHz_CLKOUT

DVDD33

A

2

4

6

8

1A0

1A1

1A2

1A3

1Y0

1Y1

1Y2

1Y3

18

16

14

12

17

15

13

2A0

2A1

2A2

2Y0

2Y1

2Y2

3

5

7

1

19

1OE

2OE

20

VCC

GND

RZ1

RZ2

0

REFCLK_OUT

510 ohm

JP3

LED0

Link

1

2

LED1

Dupx

LED2

10Act

LED3

100Act

LED4

COL

HEADER 2/SM

REFCLK_OUT

There could be more than 2

output REFCLK(50MHz) when

using buffer 74LV244.

10

74LV244

LED

REFCLK_IP101A P1

IC Plus Semiconductor Corporation

Title

IP101A Chip Circuit Diagram

www.BDTIC.com/ICplus

3

Size

A

Document Number

Date:

Wednesday, April 30, 2008

RMII UTP

2

Sheet

of

1

Rev

S-ar putea să vă placă și

- Network with Practical Labs Configuration: Step by Step configuration of Router and Switch configurationDe la EverandNetwork with Practical Labs Configuration: Step by Step configuration of Router and Switch configurationÎncă nu există evaluări

- 8051 Microcontroller: An Applications Based IntroductionDe la Everand8051 Microcontroller: An Applications Based IntroductionEvaluare: 5 din 5 stele5/5 (6)

- Equipment Grounding ConductorDocument4 paginiEquipment Grounding ConductorTan AkumaÎncă nu există evaluări

- Service Manual: PPP P PDocument185 paginiService Manual: PPP P PLaurent CAUFRIEZÎncă nu există evaluări

- 2202acdc Service Manual PDFDocument91 pagini2202acdc Service Manual PDFex-215660% (5)

- Digital Signal Processing Using the ARM Cortex M4De la EverandDigital Signal Processing Using the ARM Cortex M4Evaluare: 1 din 5 stele1/5 (1)

- Lecture 6 Import Design and FloorplanDocument54 paginiLecture 6 Import Design and FloorplanVamsi KrishnaÎncă nu există evaluări

- 555 Timer (Important)Document76 pagini555 Timer (Important)money_kandan2004Încă nu există evaluări

- Virtual Private Networking: A Construction, Operation and Utilization GuideDe la EverandVirtual Private Networking: A Construction, Operation and Utilization GuideÎncă nu există evaluări

- EE61 Power System AnalysisDocument3 paginiEE61 Power System AnalysisMartin De Boras PragashÎncă nu există evaluări

- Rayto 1904 Manual InstructionsDocument39 paginiRayto 1904 Manual InstructionsHenry Kaunang60% (5)

- The Engineering of Microprocessor Systems: Guidelines on System DevelopmentDe la EverandThe Engineering of Microprocessor Systems: Guidelines on System DevelopmentÎncă nu există evaluări

- Sony-Vaio-Vgn-Cr-13 qd-gd1 SCHEMATICDocument36 paginiSony-Vaio-Vgn-Cr-13 qd-gd1 SCHEMATICvideosonÎncă nu există evaluări

- Sony Vaio VGN-FJ Series - Quanta Rd1 - Rev 1aDocument32 paginiSony Vaio VGN-FJ Series - Quanta Rd1 - Rev 1aJose A LachiondoÎncă nu există evaluări

- Sony-Vgn-Cr392 - Mbx-177a SCHEMATICDocument35 paginiSony-Vgn-Cr392 - Mbx-177a SCHEMATICvideosonÎncă nu există evaluări

- Schematic DiagramDocument6 paginiSchematic DiagramvideosonÎncă nu există evaluări

- Schematic1 - 03 - Sphe8202rDocument1 paginăSchematic1 - 03 - Sphe8202rThơm BùiÎncă nu există evaluări

- P+5V P+5V: Power On MuteDocument8 paginiP+5V P+5V: Power On MuteuyrikÎncă nu există evaluări

- DigiX PinoutDocument4 paginiDigiX PinoutKirk TaylorÎncă nu există evaluări

- PE4H VER24 SchematicDocument2 paginiPE4H VER24 SchematicB Huerta MuñozÎncă nu există evaluări

- Piq102 Piq103 Piq103 Piq102: Pir702 Pir701 Pir1002 Pir702Document7 paginiPiq102 Piq103 Piq103 Piq102: Pir702 Pir701 Pir1002 Pir702xacdinhdiÎncă nu există evaluări

- ®MCI Electronics WWW - Olimex.cl: 3V3 3V3 RssiDocument1 pagină®MCI Electronics WWW - Olimex.cl: 3V3 3V3 Rssiefx8100% (1)

- IT66121FN Datasheet v1.02Document40 paginiIT66121FN Datasheet v1.02mohamad yahyaÎncă nu există evaluări

- Hws 13642Document3 paginiHws 13642dhieward100% (2)

- Quanta ZR7U Rev1ADocument38 paginiQuanta ZR7U Rev1ACarlos GomesÎncă nu există evaluări

- MTK 6218 SchematicsDocument5 paginiMTK 6218 SchematicssajjadfattahÎncă nu există evaluări

- Sony-Pcg-5k2t SCHEMATICDocument35 paginiSony-Pcg-5k2t SCHEMATICvideosonÎncă nu există evaluări

- G5 SchematicDocument1 paginăG5 Schematicjkifnoin100% (1)

- Pololu Wixel Schematic DiagramDocument1 paginăPololu Wixel Schematic DiagramGustavo CervantesÎncă nu există evaluări

- Fujitsu Siemens Esprimo V6535 PDFDocument47 paginiFujitsu Siemens Esprimo V6535 PDFPC MediaPointÎncă nu există evaluări

- Daouw1mb8c0 Ich7 PDFDocument33 paginiDaouw1mb8c0 Ich7 PDFflavio_b_7039Încă nu există evaluări

- SRT 4155 and SRT4355 - ServicemanualDocument40 paginiSRT 4155 and SRT4355 - ServicemanualMohamed MakiÎncă nu există evaluări

- Philips Dvp-3010 SCHDocument17 paginiPhilips Dvp-3010 SCHnike03Încă nu există evaluări

- Nokia 6210n Rm-367 SchematicsDocument41 paginiNokia 6210n Rm-367 SchematicsMarian MarinÎncă nu există evaluări

- V.Govinda Rao M.tech-ICS 05024D1410Document20 paginiV.Govinda Rao M.tech-ICS 05024D1410Kiran KumarÎncă nu există evaluări

- Acer Aspire One d270 Quanta Ze7 Rev c3c SCH 1Document42 paginiAcer Aspire One d270 Quanta Ze7 Rev c3c SCH 1Don ZielantÎncă nu există evaluări

- Mach Ngly Sim300czDocument2 paginiMach Ngly Sim300czViet Bui QuocÎncă nu există evaluări

- RS232-Interface Pic 16f84Document1 paginăRS232-Interface Pic 16f84enot1100% (2)

- Diagrama Max g55Document6 paginiDiagrama Max g55Rocio NavaÎncă nu există evaluări

- 08 RC4 CircuitDiagramDocument1 pagină08 RC4 CircuitDiagrammd faisalÎncă nu există evaluări

- Manual MF FDDocument4 paginiManual MF FDPramudita Johan IswaraÎncă nu există evaluări

- 2008-05-02 ALC662 DEMO CIRCUIT REV 0.57 Included Desktop and MobileDocument2 pagini2008-05-02 ALC662 DEMO CIRCUIT REV 0.57 Included Desktop and MobileMarcela BenitezÎncă nu există evaluări

- Wistron Sjv50 TRDocument59 paginiWistron Sjv50 TRvimaro24Încă nu există evaluări

- Piq103 Piq103: Pid202 Pik101 Pik104 Piq102 Pik101 Pid202 Pik104 Piq102Document2 paginiPiq103 Piq103: Pid202 Pik101 Pik104 Piq102 Pik101 Pid202 Pik104 Piq102Syaf TanjungÎncă nu există evaluări

- Arduino Esplora SchematicDocument1 paginăArduino Esplora SchematicJoão Carlos CarvalhoÎncă nu există evaluări

- Toshiba Satellite M300 M305 Quanta TE1 Laptop SchematicsDocument40 paginiToshiba Satellite M300 M305 Quanta TE1 Laptop SchematicsErick RodriguezÎncă nu există evaluări

- MT8888Document1 paginăMT8888Dan Nguyen VanÎncă nu există evaluări

- Acer Aspire 5930GDocument50 paginiAcer Aspire 5930Gperaja12Încă nu există evaluări

- Intel CPU: Ddriii 800/1066/1333 Ddriii 800/1066/1333 Ics9Lrs3197AklftDocument50 paginiIntel CPU: Ddriii 800/1066/1333 Ddriii 800/1066/1333 Ics9Lrs3197Aklftdrop9721Încă nu există evaluări

- Smp8654 Dev Board: 922Reva3ADocument15 paginiSmp8654 Dev Board: 922Reva3AМихаил ГудковÎncă nu există evaluări

- Quanta Bd3a r3c SchematicsDocument44 paginiQuanta Bd3a r3c SchematicsKostas AthanasiadisÎncă nu există evaluări

- Connecting Ethernet Interface With LPC2000: Rev. 01 - 7 February 2007 Application NoteDocument21 paginiConnecting Ethernet Interface With LPC2000: Rev. 01 - 7 February 2007 Application NoteJorBS57Încă nu există evaluări

- Piic102 Piic102: Pir202 Pir201 Pir202Document3 paginiPiic102 Piic102: Pir202 Pir201 Pir202ChàngNgốc VôTìnhÎncă nu există evaluări

- OV7670 + AL422B (FIFO) Camera Module (V2.0) SchematicDocument1 paginăOV7670 + AL422B (FIFO) Camera Module (V2.0) SchematicMuhammad Alfiansyah100% (3)

- Acer Aspire 5235 5535 5735 - Wistron Cathedral Peak IIDocument44 paginiAcer Aspire 5235 5535 5735 - Wistron Cathedral Peak IIMatias ArÎncă nu există evaluări

- Cab LageDocument2 paginiCab LageSalah DahouathiÎncă nu există evaluări

- So Do Nb2dsk01Document72 paginiSo Do Nb2dsk01maithuong85Încă nu există evaluări

- Schematics Laptop Dell Inspiron 700m 710m Wistron MolokaiDocument39 paginiSchematics Laptop Dell Inspiron 700m 710m Wistron MolokaiFábio DominguesÎncă nu există evaluări

- FAQ - Causes of Electrical Cable Failure - Eland CablesDocument4 paginiFAQ - Causes of Electrical Cable Failure - Eland CablesPavan SharmaÎncă nu există evaluări

- Cea 311 ReportDocument2 paginiCea 311 ReportFaher Gaosel WatamamaÎncă nu există evaluări

- EMACH1 - DC GeneratorDocument60 paginiEMACH1 - DC GeneratorKiyoshi Jiro MalinaoÎncă nu există evaluări

- Surge Arresters: Varistar Storm Trapper High Energy Mov Arrester Installation InstructionsDocument2 paginiSurge Arresters: Varistar Storm Trapper High Energy Mov Arrester Installation InstructionsAgussalim AddinÎncă nu există evaluări

- EnVoice MK II Manual EnglDocument24 paginiEnVoice MK II Manual EnglEdu ReyesÎncă nu există evaluări

- SDM630MCT-ML Datasheet Dec22Document3 paginiSDM630MCT-ML Datasheet Dec22Marco Lo GueÎncă nu există evaluări

- Technical and Vocational Education Faculty: Engineering Education Department (JPK)Document27 paginiTechnical and Vocational Education Faculty: Engineering Education Department (JPK)Farahnasuhaa JamilÎncă nu există evaluări

- Tesla meter,Gauss meter、Magnetic flux densimeter、Introduction Handy typeDocument2 paginiTesla meter,Gauss meter、Magnetic flux densimeter、Introduction Handy typesomkiat kongprasiatÎncă nu există evaluări

- Modul Peka Science Year 3Document11 paginiModul Peka Science Year 3Helyza HayesÎncă nu există evaluări

- EE 310 Lab3 ReportDocument10 paginiEE 310 Lab3 Reporttol5187100% (1)

- OBSoil-01 ElecFreaksDocument5 paginiOBSoil-01 ElecFreaksARLEYITO ANDRADE ESPINOSAÎncă nu există evaluări

- EM Clamp For Immunity Tests Acc. EN 61000-4-6 Ed. 4.0: EMCL-20Document5 paginiEM Clamp For Immunity Tests Acc. EN 61000-4-6 Ed. 4.0: EMCL-20spohanÎncă nu există evaluări

- Current ElectricityDocument8 paginiCurrent Electricityhj48khy8jjÎncă nu există evaluări

- 55-2-1 PhysicsDocument11 pagini55-2-1 PhysicsSezein DuaÎncă nu există evaluări

- Design and Development of Small Active and Passive Loop Antennas For Measurement of Shielding Effectiveness Per IEEE Std.299Document5 paginiDesign and Development of Small Active and Passive Loop Antennas For Measurement of Shielding Effectiveness Per IEEE Std.299Andrea QuadriÎncă nu există evaluări

- EE360 - Electric Circuit (Basics Needs To Revise For The Course)Document66 paginiEE360 - Electric Circuit (Basics Needs To Revise For The Course)بدون اسمÎncă nu există evaluări

- 3a SCR TRIACDocument46 pagini3a SCR TRIACFAZRI RENDI KURNIAWANÎncă nu există evaluări

- Tutorial Sheet 3Document3 paginiTutorial Sheet 3KusanSanjitÎncă nu există evaluări

- D-Tect 3: Motion DetectorDocument2 paginiD-Tect 3: Motion DetectorAdrian DeoancaÎncă nu există evaluări

- Transistor DesignDocument51 paginiTransistor DesignJohn GentileÎncă nu există evaluări

- VS1-2 Manual PDFDocument284 paginiVS1-2 Manual PDFJorge InostrozaÎncă nu există evaluări

- DM OLED24 630 DatasheetDocument17 paginiDM OLED24 630 Datasheetady_gligor7987Încă nu există evaluări

- Bat 12v 18ah - Amp9039 - UkDocument2 paginiBat 12v 18ah - Amp9039 - UkAbdoullai camaraÎncă nu există evaluări