Documente Academic

Documente Profesional

Documente Cultură

DSD

Încărcat de

Anil Marturi0 evaluări0% au considerat acest document util (0 voturi)

259 vizualizări1 paginăghfh

Titlu original

Dsd

Drepturi de autor

© © All Rights Reserved

Formate disponibile

PDF, TXT sau citiți online pe Scribd

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentghfh

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PDF, TXT sau citiți online pe Scribd

0 evaluări0% au considerat acest document util (0 voturi)

259 vizualizări1 paginăDSD

Încărcat de

Anil Marturighfh

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PDF, TXT sau citiți online pe Scribd

Sunteți pe pagina 1din 1

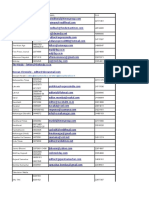

M.Tech.

(VLSI/ VLSI DESIGN/VLSI SYSTEM DESIGN)-R13 Regulations

JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD

M. Tech I Year I Sem. (VLSI/VLSI Design/VLSi System Design)

DIGITAL SYSTEM DESIGN

(ELECTIVE -I)

UNIT -I:

Minimization and Transformation of Sequential Machines:

The Finite State Model Capabilities and limitations of FSM State equivalence and machine

minimization Simplification of incompletely specified machines.

Fundamental mode model Flow table State reduction Minimal closed covers Races, Cycles

and Hazards.

UNIT -II:

Digital Design:

Digital Design Using ROMs, PALs and PLAs , BCD Adder, 32 bit adder, State graphs for control

circuits, Scoreboard and Controller, A shift and add multiplier, Array multiplier, Keypad Scanner,

Binary divider.

UNIT -III:

SM Charts:

State machine charts, Derivation of SM Charts, Realization of SM Chart, Implementation of Binary

Multiplier, dice game controller.

UNIT -IV:

Fault Modeling & Test Pattern Generation:

Logic Fault model Fault detection & Redundancy- Fault equivalence and fault location Fault

dominance Single stuck at fault model Multiple stuck at fault models Bridging fault model.

Fault diagnosis of combinational circuits by conventional methods Path sensitization techniques,

Boolean Difference method Kohavi algorithm Test algorithms D algorithm, PODEM, Random

testing, Transition count testing, Signature analysis and test bridging faults.

UNIT -V:

Fault Diagnosis in Sequential Circuits:

Circuit Test Approach, Transition Check Approach State identification and fault detection

experiment, Machine identification, Design of fault detection experiment

TEXT BOOKS:

th

1. Fundamentals of Logic Design Charles H. Roth, 5 Ed., Cengage Learning.

2. Digital Systems Testing and Testable Design Miron Abramovici, Melvin A.

Breuer and Arthur D. Friedman- John Wiley & Sons Inc.

3. Logic Design Theory N. N. Biswas, PHI

REFERENCE BOOKS:

nd

1. Switching and Finite Automata Theory Z. Kohavi , 2 Ed., 2001, TMH

th

2. Digital Design Morris Mano, M.D.Ciletti, 4 Edition, PHI.

3. Digital Circuits and Logic Design Samuel C. Lee , PHI

S-ar putea să vă placă și

- Syllabus JntuhDocument27 paginiSyllabus JntuhSai KumarÎncă nu există evaluări

- EEE Jntuk 26Document1 paginăEEE Jntuk 26jamesdd10Încă nu există evaluări

- Jawaharlal Nehru Technological University Hyderabad M.Tech. Digital Electronics & Communication Systems Course Structure and SyllabusDocument12 paginiJawaharlal Nehru Technological University Hyderabad M.Tech. Digital Electronics & Communication Systems Course Structure and Syllabustejaswi.mÎncă nu există evaluări

- MTech VLSI Design 1st Sem SyllabusDocument5 paginiMTech VLSI Design 1st Sem SyllabusPrakash Sinha100% (1)

- Digital System DesignDocument1 paginăDigital System Designvalaravi0% (1)

- Decs I SemDocument14 paginiDecs I SemRamana MurthyÎncă nu există evaluări

- Advanced Computer Architecture and AlgorithmsDocument12 paginiAdvanced Computer Architecture and Algorithmsgangadhar_aspnetÎncă nu există evaluări

- Design For Testability SyllabusDocument1 paginăDesign For Testability SyllabusAshraf AliÎncă nu există evaluări

- Jawaharlal Nehru Technological University Anantapur B. Tech III-I Sem. (EEE) L T P C 3 1 0 3 15A04510 Digital Circuits and Systems (Moocs-I) Course OutcomesDocument2 paginiJawaharlal Nehru Technological University Anantapur B. Tech III-I Sem. (EEE) L T P C 3 1 0 3 15A04510 Digital Circuits and Systems (Moocs-I) Course Outcomesjeravi84Încă nu există evaluări

- MCA IV Sem SyllabusDocument2 paginiMCA IV Sem SyllabusAnchal KesharwaniÎncă nu există evaluări

- Switching Theory and Logic DesignDocument2 paginiSwitching Theory and Logic DesignManjunath BadigerÎncă nu există evaluări

- Type of Questions For University Examination Question 1 - 8 Short Answer Questions of 5 Marks Each. 2 Questions From Each ModuleDocument8 paginiType of Questions For University Examination Question 1 - 8 Short Answer Questions of 5 Marks Each. 2 Questions From Each ModuleVishnu PrabhakarÎncă nu există evaluări

- Vlsi Mtech 1st - Year - Jntu Kakinada SyllabusDocument8 paginiVlsi Mtech 1st - Year - Jntu Kakinada Syllabustele203Încă nu există evaluări

- Vlsi Mtech Jntu Kakinada II Sem SyllabusDocument16 paginiVlsi Mtech Jntu Kakinada II Sem Syllabusrv prasad50% (2)

- Ap7102 Adsd SyllabiDocument6 paginiAp7102 Adsd SyllabishankarÎncă nu există evaluări

- I Semester PDFDocument7 paginiI Semester PDFSolaiÎncă nu există evaluări

- M Tech-DecsDocument27 paginiM Tech-Decsjagadish3794Încă nu există evaluări

- VLSI SyllabusDocument13 paginiVLSI SyllabusNagabhushanam KoduriÎncă nu există evaluări

- V Rajaraman Computer Oriented Numerical MethodsDocument38 paginiV Rajaraman Computer Oriented Numerical Methodssun_shenoy40% (5)

- Distributed Systems and Advanced Computer ArchitectureDocument4 paginiDistributed Systems and Advanced Computer ArchitectureShwetank GoelÎncă nu există evaluări

- IT Computer Organization ArchitectureDocument5 paginiIT Computer Organization ArchitectureAkash DasÎncă nu există evaluări

- 1st Sem MCADocument6 pagini1st Sem MCArohietsharmaaÎncă nu există evaluări

- Syllabus 5th SemDocument5 paginiSyllabus 5th SemDivyansh VinodÎncă nu există evaluări

- DSP and Compiler ConstructionDocument6 paginiDSP and Compiler ConstructionAmal NanduÎncă nu există evaluări

- Regulations - 2009: Affiliated Institutions Anna University, ChennaiDocument10 paginiRegulations - 2009: Affiliated Institutions Anna University, Chennaisri_vas00074013Încă nu există evaluări

- STLDDocument1 paginăSTLDAmy OliverÎncă nu există evaluări

- Vlsi System DesignDocument12 paginiVlsi System DesignMahender GoudÎncă nu există evaluări

- De SyllabusDocument2 paginiDe SyllabusKarthikeyan_Go_9525Încă nu există evaluări

- CSE 6th SyllabusDocument5 paginiCSE 6th Syllabusmanish raushanÎncă nu există evaluări

- Vlsi DesignDocument12 paginiVlsi DesignTanveer AhmedÎncă nu există evaluări

- MCA Course Structure and SyllabusDocument6 paginiMCA Course Structure and SyllabusMeitei opubunqÎncă nu există evaluări

- Es IiDocument16 paginiEs IiSivasankar YalavarthyÎncă nu există evaluări

- Swttching Theory and Logic Design PDFDocument2 paginiSwttching Theory and Logic Design PDFgoutamkrsahooÎncă nu există evaluări

- M.tech2nd Sem SyllabusDocument8 paginiM.tech2nd Sem Syllabusirfan449Încă nu există evaluări

- Jntuh Mech Engg R16 SyllabusDocument7 paginiJntuh Mech Engg R16 SyllabusAqib syedÎncă nu există evaluări

- DLD SylabusDocument1 paginăDLD SylabusSiva PratapÎncă nu există evaluări

- Vlsi Mtech Jntu Kakinada SyllabusDocument11 paginiVlsi Mtech Jntu Kakinada Syllabusaditya414Încă nu există evaluări

- Ap7102 AdsdDocument5 paginiAp7102 AdsdshankarÎncă nu există evaluări

- VLSI Syllabus M.tech BurlaDocument27 paginiVLSI Syllabus M.tech BurlaBiswajit BeheraÎncă nu există evaluări

- Principles of Management: HU-601 / CREDIT 2Document6 paginiPrinciples of Management: HU-601 / CREDIT 2extraincome108Încă nu există evaluări

- 6Xn1 Digital Integrated CircuitsDocument2 pagini6Xn1 Digital Integrated CircuitsapbhatkarÎncă nu există evaluări

- CAD CAM II SemDocument13 paginiCAD CAM II SemSayyadh Rahamath BabaÎncă nu există evaluări

- M E EmbeddedSystemTechnologiesDocument31 paginiM E EmbeddedSystemTechnologiesRohini BabuÎncă nu există evaluări

- MCA SubjectsDocument33 paginiMCA SubjectsLakshmi PujariÎncă nu există evaluări

- First Sem PDFDocument5 paginiFirst Sem PDFRajvardhan JaidevaÎncă nu există evaluări

- Tool Engineering Sem 2Document7 paginiTool Engineering Sem 2psg10474383Încă nu există evaluări

- MCA First Year Syllabus Manipur UniversityDocument6 paginiMCA First Year Syllabus Manipur UniversityMeitei opubunqÎncă nu există evaluări

- MRSPTU 8th Sem Syllabus 2020Document4 paginiMRSPTU 8th Sem Syllabus 2020PiyushÎncă nu există evaluări

- P: 0 Sessional: 75marksDocument15 paginiP: 0 Sessional: 75marksNilimoy BuragohainÎncă nu există evaluări

- UEC2302 Digital System Design Course OverviewDocument10 paginiUEC2302 Digital System Design Course OverviewAmoga LekshmiÎncă nu există evaluări

- Traffic Flow Theory: Characteristics, Experimental Methods, and Numerical TechniquesDe la EverandTraffic Flow Theory: Characteristics, Experimental Methods, and Numerical TechniquesEvaluare: 4.5 din 5 stele4.5/5 (5)

- Introduction to Digital Systems: Modeling, Synthesis, and Simulation Using VHDLDe la EverandIntroduction to Digital Systems: Modeling, Synthesis, and Simulation Using VHDLÎncă nu există evaluări

- Mobile Edge Artificial Intelligence: Opportunities and ChallengesDe la EverandMobile Edge Artificial Intelligence: Opportunities and ChallengesÎncă nu există evaluări

- Modern Data Mining Algorithms in C++ and CUDA C: Recent Developments in Feature Extraction and Selection Algorithms for Data ScienceDe la EverandModern Data Mining Algorithms in C++ and CUDA C: Recent Developments in Feature Extraction and Selection Algorithms for Data ScienceÎncă nu există evaluări

- Modeling of Transport Demand: Analyzing, Calculating, and Forecasting Transport DemandDe la EverandModeling of Transport Demand: Analyzing, Calculating, and Forecasting Transport DemandÎncă nu există evaluări

- The CNC Handbook: Digital Manufacturing and Automation from CNC to Industry 4.0De la EverandThe CNC Handbook: Digital Manufacturing and Automation from CNC to Industry 4.0Evaluare: 5 din 5 stele5/5 (1)

- Engineering Principles of Combat Modeling and Distributed SimulationDe la EverandEngineering Principles of Combat Modeling and Distributed SimulationÎncă nu există evaluări

- Smart Cities and Homes: Key Enabling TechnologiesDe la EverandSmart Cities and Homes: Key Enabling TechnologiesEvaluare: 5 din 5 stele5/5 (1)

- Intelligent Technologies for Automated Electronic SystemsDe la EverandIntelligent Technologies for Automated Electronic SystemsÎncă nu există evaluări

- What Is The Difference Between 0.2 and 0.2S Class CT - QuoraDocument3 paginiWhat Is The Difference Between 0.2 and 0.2S Class CT - QuoraAnil MarturiÎncă nu există evaluări

- What Is A High Speed Earth Switch, and How Does It Work - Quora PDFDocument2 paginiWhat Is A High Speed Earth Switch, and How Does It Work - Quora PDFAnil MarturiÎncă nu există evaluări

- What Is A High Speed Earth Switch, and How Does It Work - Quora PDFDocument2 paginiWhat Is A High Speed Earth Switch, and How Does It Work - Quora PDFAnil MarturiÎncă nu există evaluări

- Abirami AnthathiDocument24 paginiAbirami Anthathijekay2ab92% (12)

- Gmail - Your Sunday Ride To PorurDocument2 paginiGmail - Your Sunday Ride To PorurAnil MarturiÎncă nu există evaluări

- SF6 Properties and Use in MV and HV SwitchgearDocument26 paginiSF6 Properties and Use in MV and HV SwitchgearPradeep_Vashist100% (1)

- Impact of VT Burden Rating on AccuracyDocument2 paginiImpact of VT Burden Rating on AccuracyRuben Dario ToroÎncă nu există evaluări

- AathichudiDocument16 paginiAathichudiமுரளி கிருஷ்ணன் alias முகி100% (9)

- Sales Brochure Mod LIC-s JA6-080218Document2 paginiSales Brochure Mod LIC-s JA6-080218Anil MarturiÎncă nu există evaluări

- Lics Jeevan Akshay Vi Uin 512n234v06Document5 paginiLics Jeevan Akshay Vi Uin 512n234v06Rahul KolateÎncă nu există evaluări

- Road Culvert DrawingDocument1 paginăRoad Culvert DrawingAnil MarturiÎncă nu există evaluări

- 6 - Section DGset R4Document12 pagini6 - Section DGset R4Anil MarturiÎncă nu există evaluări

- CTS - 110kV Metering BayDocument1 paginăCTS - 110kV Metering BayAnil MarturiÎncă nu există evaluări

- Gajwel Retrofit Scope InputDocument14 paginiGajwel Retrofit Scope InputAnil MarturiÎncă nu există evaluări

- Bahubali 2Document1 paginăBahubali 2Anil MarturiÎncă nu există evaluări

- 09 Manual ReluxSuiteDocument105 pagini09 Manual ReluxSuiteAxel Ramses Valencia JacquesÎncă nu există evaluări

- SL No Description As Per Annexure: 12 Offered by Us Remarks Qty Units Qty UnitsDocument5 paginiSL No Description As Per Annexure: 12 Offered by Us Remarks Qty Units Qty UnitsAnil MarturiÎncă nu există evaluări

- Level Sheet For Road 2 Level B H L Actual Level Average Level Filling QTYDocument21 paginiLevel Sheet For Road 2 Level B H L Actual Level Average Level Filling QTYAnil MarturiÎncă nu există evaluări

- Principal: Vasavi College of Engineering (Autonomous)Document1 paginăPrincipal: Vasavi College of Engineering (Autonomous)Anil MarturiÎncă nu există evaluări

- Lightning Arresters Sl. No. Description Lightning Arresters: Peak Peak PeakDocument3 paginiLightning Arresters Sl. No. Description Lightning Arresters: Peak Peak PeakAnil MarturiÎncă nu există evaluări

- 125mvar, 400Kv Bus Reactor Bay Extn. at 400/220/132Kv Gajwel Substation, Medak Dist, Telangana StateDocument1 pagină125mvar, 400Kv Bus Reactor Bay Extn. at 400/220/132Kv Gajwel Substation, Medak Dist, Telangana StateAnil MarturiÎncă nu există evaluări

- AP TRANSCO site level formation cutting and filling reportDocument1 paginăAP TRANSCO site level formation cutting and filling reportAnil MarturiÎncă nu există evaluări

- 0.2S Class SpecificationDocument15 pagini0.2S Class SpecificationAnil MarturiÎncă nu există evaluări

- Recharge Invoice 766982908Document1 paginăRecharge Invoice 766982908Anil MarturiÎncă nu există evaluări

- EPC Division Stationary Inventory ListDocument1 paginăEPC Division Stationary Inventory ListAnil MarturiÎncă nu există evaluări

- SBI Clerk Vacancies 2015 16Document2 paginiSBI Clerk Vacancies 2015 16Naga RajÎncă nu există evaluări

- Sizing Battery Banks For Switchgear and Control Applications by HandDocument4 paginiSizing Battery Banks For Switchgear and Control Applications by HandAnil MarturiÎncă nu există evaluări

- Walk-In For Electrical Engineers - Leads at Cyient, Hyderabad On 10jan16 - Hyderabad - Secunderabad - Cyient Limited - 5-To-10 Years of ExperienceDocument4 paginiWalk-In For Electrical Engineers - Leads at Cyient, Hyderabad On 10jan16 - Hyderabad - Secunderabad - Cyient Limited - 5-To-10 Years of ExperienceAnil MarturiÎncă nu există evaluări

- Recharge Invoice 766982908Document1 paginăRecharge Invoice 766982908Anil MarturiÎncă nu există evaluări

- 12-II.2. Tower SpottingDocument16 pagini12-II.2. Tower Spottingashok10577Încă nu există evaluări

- Ánñr©Od Πnªnl: Mastering Arabic 1: Arabic NumbersDocument1 paginăÁnñr©Od Πnªnl: Mastering Arabic 1: Arabic Numbersporco dio caneÎncă nu există evaluări

- Rubric For ScreencastingDocument1 paginăRubric For ScreencastingLovely FloresÎncă nu există evaluări

- Culminatingactivity Lesson1 221007160252 9bb3a9b3Document23 paginiCulminatingactivity Lesson1 221007160252 9bb3a9b3jaterÎncă nu există evaluări

- Comp 122 Comp121 Cosf 122 Discrete StructuresDocument5 paginiComp 122 Comp121 Cosf 122 Discrete Structuresvictor kimutaiÎncă nu există evaluări

- OOP Course OverviewDocument11 paginiOOP Course OverviewIjaz KhanÎncă nu există evaluări

- Learning Plan For Grade 9 Music S.Y. 2019-2020: and Audience) During Classical PeriodDocument2 paginiLearning Plan For Grade 9 Music S.Y. 2019-2020: and Audience) During Classical PeriodCatalinus SecundusÎncă nu există evaluări

- Vocabulary - AdjectivesDocument2 paginiVocabulary - AdjectivesJohnÎncă nu există evaluări

- Displaying Data From Data Base: Home Oracle Application Framework Oaf TutorialsDocument5 paginiDisplaying Data From Data Base: Home Oracle Application Framework Oaf TutorialsOracle developerÎncă nu există evaluări

- Glorious Grace Day 9: Take Time To Listen - JosephPrince - Com BlogDocument3 paginiGlorious Grace Day 9: Take Time To Listen - JosephPrince - Com Blogadebee007Încă nu există evaluări

- Silas WoodsmithDocument1 paginăSilas Woodsmithapi-317585365Încă nu există evaluări

- BP A2 CB Ak Business Partners A2 CB Answer Keys Is A Book That Can Help You Solve Your LessonDocument49 paginiBP A2 CB Ak Business Partners A2 CB Answer Keys Is A Book That Can Help You Solve Your LessonĐăng Minh NguyễnÎncă nu există evaluări

- Intro To GentooDocument20 paginiIntro To GentooL4loSky100% (1)

- Endeca Assembler App Developers GuideDocument186 paginiEndeca Assembler App Developers Guidedsoares74Încă nu există evaluări

- DBMS Unit 3Document25 paginiDBMS Unit 3Yash KadamÎncă nu există evaluări

- Sri Ranganatha TempleDocument12 paginiSri Ranganatha TempleKANIKA GUPTAÎncă nu există evaluări

- 26DESDocument2 pagini26DESabhilashmaramullaÎncă nu există evaluări

- Embedded System Design Using Arduino 18ECO108J: Unit IvDocument53 paginiEmbedded System Design Using Arduino 18ECO108J: Unit IvHow MeanÎncă nu există evaluări

- 14th ROMAN 4.2Document7 pagini14th ROMAN 4.2Dhruv BajajÎncă nu există evaluări

- MoogAnimatics 2016 ProductCatalogDocument52 paginiMoogAnimatics 2016 ProductCatalogChaly KhoaÎncă nu există evaluări

- Media ContactDocument2 paginiMedia ContactsmartguyxÎncă nu există evaluări

- KKIPS SLAC Action Plan in SchoolDocument6 paginiKKIPS SLAC Action Plan in SchoolEmz Mzz33% (3)

- 2nd PERIODICAL TEST ENGLISH GRADE 3, FINALDocument5 pagini2nd PERIODICAL TEST ENGLISH GRADE 3, FINALRowena Caluya100% (4)

- The Sacred Books & Early Literature of The East VOL 10: India & Buddhism - Charles Francis Horne 1917Document430 paginiThe Sacred Books & Early Literature of The East VOL 10: India & Buddhism - Charles Francis Horne 1917Waterwind100% (3)

- Az - History Book Year 8Document60 paginiAz - History Book Year 8Nargiz AhmedovaÎncă nu există evaluări

- TSQL Lab 1 - Intro to Transact-SQL queriesDocument12 paginiTSQL Lab 1 - Intro to Transact-SQL queriesireshaÎncă nu există evaluări

- Método GET - EXTERNAL - ALV - DATADocument21 paginiMétodo GET - EXTERNAL - ALV - DATAanselmodelarcoÎncă nu există evaluări

- Bolor ShichidaDocument2 paginiBolor ShichidaЖ.Ж. БолорÎncă nu există evaluări

- Pages From A Search For Two QuartersDocument17 paginiPages From A Search For Two QuartersPageMasterPublishingÎncă nu există evaluări

- 8 Engleza ORALDocument3 pagini8 Engleza ORALDiana RaduÎncă nu există evaluări

- Language Tasks BreakdownDocument4 paginiLanguage Tasks Breakdown9036112Încă nu există evaluări