Documente Academic

Documente Profesional

Documente Cultură

MCT Laborator

Încărcat de

frankyroDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

MCT Laborator

Încărcat de

frankyroDrepturi de autor:

Formate disponibile

LABORATOR 1

1.1. Ceneralitati

Microcontrolerul AT89CSI este un microcontroler de 8 biti realizat in tehnologie CMOS, cu performante ridicate, de put ere mica si este reprezentantul familiei ATNffiL de microcontrolere. Are 0 memorie program interns de tip FLASH cu 0 capacitate de 4 Kocteti, iar setul de

.structiuni si conexiunile externe sunt compatibile cu produsele din standardul MCS-Sl. Memoria program interna FLASH se reprogrameaza in sistem cu un program conventional pentru memorii nevolatile, admite pana la 1000 de cicluri de scrierel stergere si dispune de trei nivele de blocare. Structura microcontrolerului este proiectata cu logica statica pentru a lucra de la frecventa de OHz a oscilatorului de tact pana la frecventa maxima de 24?v1Hz.

Microcontrolerul AT89CSI coniine intr-un singur circuit integrat urmatoarele resurse: microprocesorul, memoria program interna FLASH cu 0 capacitate de 4Kocteti, memoria de date interna RAM cu 0 capacitate de 128 octeti, patru porturi paralele de intrare/iesire de 8 biti fiecare, doua contoare de cate 16 biti, un canal serial programabil, un sistem de intreruperi cu cinci surse organizate pe doua nivele de prioritate, un oscilator de tact intern si doua moduri de lucru pentru consum redus.

Microeontrolerul AT89CSI este un microcomputer puternic care of era 0 flexibilitate ridicata si un cost mic pentru numeroase aplicatii.

1.2. Caracteristicile microcontrolerului A T89C51

Principalele caraeteristici ale microcontrolerului AT89CSI, reprezentantul familiei AT MEL

~ microcontrolere de 8 biti sunt:

- compatibil eu produsele standard MCS-Sl;

- realizat in tehnologie CMOS;

- frecventa oscilatorului de tact intern OHz - 24 MHz;

- tensiunea de alimentare continua de SV ± 20%;

- 4 Kocteti de memorie program interna FLASH, reprogramabila pentru 1000 cicluri de

scriere/ stergere Programarea acestei memorii se realizeaza In mod paralel cu 0 tensiune ridicata

- 1.1 -

de +12V sau cu 0 tensiune scazuta de +5V. Admite trei nivele de blocare a memoriei program; - adreseaza 64 Kocteti de memorie program externa;

- 128 octeti de memorie de date interna RAM;

- adreseaza 64 Kocteti de memorie de date externa;

- spatiul registrelor eu functii speciale (SFR) contine 21 registre;

- 32 linii de intrere/iesire programabile organizate in 4 porturi paralele de cate 8 biti;

- 2 contoare de 16 biti programabile;

- un canal serial prograrnabil;

- 5 surse de intrerupere organizate pe doua nivele de prioritati;

- 2 moduri de lucru eu eonsum redus;

- capsula PDIP (40 pini), PLCC (44 pini), PQFP/TQFP (44 pini).

1.3. Arhitectura interna a microcontrolerului A T89C51

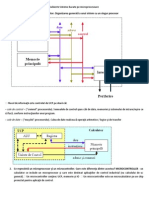

Microcontrolerul AT89C51 de 8 biti are arhitectura interna de prineipiu redata in fig. 1.1 .

.. - - - - - - -~ - - - -

MEM

~-------------------1

I

MP LB2 FLASH

MD RAM I

LBI

PP

PN

IS

CI

CB

............... - -" --Mediii'extem' _ .. _ .. , .... _ ... _.

Fig. 1. 1.

Microcontrolerul AT89C51 este organizat in jurul magistralei interne Ml si contine urmatoarele resurse interne:

- u.P - microprocesorul optirnizat pentru aplicatii de comanda ~i control este alcatuit din:

- RI - registrul de instructiuni;

- DEC - decodifieatorul de instructiuni;

- UCC - unitatea de cornanda si control; RI, DEC si VCC asigura executarea

- 1.2 -

programelor si generarea semnalelor de cornanda pentru functionarea microcontrolerului; - Osc - oscilatorul de tact;

- VAL - unitatea aritrnetica si logica executa operatii aritmetice (adunare, scadere,

incrementare, decrementare, comparare, ajustare zecimala, inmultire, impartire) si logice (SAU, S1, SAU EXCLUS1V, NU, rotiri); in registrele temporare AT si RT (nefigurate) aflate pe cele doua brate ale unitatii aritmetice ~i logice se incarca operanzii instructiunii;

- SFR - spatiul de memorie pentru registrele cu functii speciale;

- PC - numaratorul de program;

- MEM - memoria interna alcatuita din:

- MP - memoria program este 0 memorie nevolatila de tip FLASH cu 0 capacitate

de 4 kocteti, din care se efectueaza numai citiri, fiind destinata pentru memorarea programelor utilizator sau a structurilor de date (fixe). Continutul acestei memorii nu se pierde in urma intreruperii alimentarii microcontrolerului (AT89C52, AT89C55\VD, AT89C51RC au memoria program de 8Ko, 20Ko si respectiv 32 Ko);

- LB1, LB2, LB3 - biti de blocare acces la memoria program interna FLASH;

- MD - memoria de date este 0 memorie volatila de tip RAM cu 0 capacitate de

128 octeti, din care se efectueaza citiri ~i scrieri, fiind destinata pentru memorarea datelor initiale, a rezultatelor intermediare ~i a eelor finale. Continutul acestei memorii se pierde in urrna intreruperii alimentarii mierocontrolerului (AT89C52 si AT89C55WD au memoria de date de 256 o cteti , iar AT89C51RC are memoria de date de 512 octeti).

Microeontrolerele ATMEL adreseaza distinct memoria program si memoria de date. Cireuitele periferiee au rolul de a transmite semnale digitale in mediul extern sau de a receptiona semnale digitale din mediul extern. Prineipalele circuite periferiee de uz general sunt:

- PP - porturile paralele de intrarel iesire care pot fi adresate la nivel de octet sau de bit. • Iicrocontrolerul AT89C51 are patru porturi paralele de intrarel iesire (AT89C2051, AT89C4051 au 2 porturi paralele, iar AT89C51RD2 are 6 porturi paralele). Unele porturi indeplinesc ~i alte functii atunci cand se extinde memoria microcontrolerului in exterior, astfel:

- portul PO - multiplexeaza partea Iowa busului de adresa (BAo_i) cu busul de date (BDo_7);

- portul P2 - furnizeaza partea high a busului de adresa (BAs_I5);

- portul P3 - furnizeaza semnale de comanda (iesiri de comanda pentru citirea din memoria de

date externa si pentru scrierea in memoria de date externa; celelalte linii pot fi utilizate ea linii de

- 1.3 -

intrare pentru cererile de intrerupere externa, intrari pentru numaratoare, intrare ~i respectiv iesire pentru interfata de comunicatie seriala)

- IS - interfata seriala pentru transrniterea si receptia asincrona a datelor (full - duplex);

- PN - port cu doua numaratoare (contoare) de 16 biti care pot fi utilizate in modul

temporizator sau numarator (AT89C52, AT89C55WD si AT89C51RC au trei contoare);

- CI - controlerul de intreruperi ext erne si interne. Dispune de 5 surse de intreruperi programabile pe doua nivele de prioritati. Inrreruperile ext erne sunt active pe nivellogic sau pe front si se aplica la intrarile L~TO si INTI. Intreruperile interne sunt generate de cele doua contoare de 16 biti si de interfata de cornunicatie seriala

- CB - controlerul de bus asigura functionarea sincronizata a informatiilor pe busuri si permite extinderea in exterior a MP pana Ja 64 Kccteti, iar a MD cu 64 kocteti;

1.3.1. Memoria program

Adresarea memoriei program interne sau externe se face cu adrese de 16 biti; MP contine programe care sunt executate de microprocesor sau tabele de date care au 0 structura fixa. Din aceasta memorie se fac numai citiri. Structura MP a microcontrolerului este precizata in fig. 1.2.

MP externa l000-0FFFFH

SAU

11J> externa OOOO-OFF'FFH

MP interna OOOO-OFFFH

EA=O

PSEN

EA=l

Fig. 1.2.

Pentru adresarea MP interne a rnicrocontrolerului AT89C51 care este 0 memone

nevolatila FLASH cu 0 capacitate de 4 Kocteti, pinul EA al microcontrolerului este conectat la 1 logic; in acest caz, pentru zona de memorie 0000 - OFFFH este selectata MP interna, iar pentru zona de memorie 1000 - OFFFFH este selectata I\IP externa eu semnalul PSEN

Pentru adresarea MP ext erne pinul EA al microcontrolerului este conectat la 0 logic. iar selectia cipului de MP externa se realizeaza cu semnalul PSEN Memoria program externa este o memorie nevolatila de tipul PROM, EPROM, FLASH cu 0 capacitate maxima de 64 Kocteti.

- 1.4 -

f

1.3.2. Memoria de date

Adresarea memoriei de date interne se face cu adrese de 8 biti, iar a celei ext erne cu adrese de 16 biti. Memoria de date externa este selectata cu ajutorul semnalelor de comanda RD pentru citire si WR pentru scriere. MD este 0 memorie volatila care contine numai date hexazecimale ~i poate fi cit ita sau scrisa.

Structura MD interne si externe este prezentata in fig. 1.3.

MD" interns. 80-0FFH

SFR 80-0FFH

SI

MDexterna OOOO-OFFFFH

MD intema 00-7FH

+ WR

Fig. 1.3.

Memoria de date interna este alcatuita din:

- 0 zona de memorie adresabila direct sau indirect in spatiul de adresa 00- 7FH si are 0 capacitate de 128 octeti; aceasta zona de memorie interna de date exists la toate microcontrolerele din familia ATMEL;

- 0 zona de memorie adresabila indirect in spatiul de adresa 80-0FFH si are 0 capacitate de 128 octeti; aceasta zona de memorie interna de date exista numai la unele microcontrolere

(AT89C52, AT89C55WD, AT89C51RC, etc.);

- 0 zona de memorie adresabila direct in spatiul de adresa 80-0FFH care este pentru registrele cu functii speciale (SFR) si are 0 capacitate maxima de 128 octeti; in acest spatiu de memorie numai unele locatii de memorie au 0 anumita sernnificatie. Microcontrolerul AT89C51 are implementate in aceasta zona de memorie 21 de registre. Circuitele periferice interne ale microcontrolerului impreuna cu cele ext erne sunt tratate ca locatii de memorie.

o locatie de memorie de date este adresata direct atunci cand adresa este prezenta in codul instructiunii ~i este adresata indirect atunci cand adresa este precizata de un registru.

Memoria de date externa este 0 memorie volatila de tipul SRAM si are 0 capacitate maxima de 64 Kocteti. Nu se folosese memorii DRAlv1 deoarece acestea necesita 0 refreshare (reimprospatare) a continului memoriei dinamice care se realizeaza cu 0 structura hard externa (controler specializat).

- 1.5 -

1.3.2.1. Memoria interna de date

In zona de memorie de date interna adresabila direct ~i indirect a oricarui microcontroler

din spatiul de adrese 00- 7FH se afla (vezi tabelul 1. 1.):

- patru bancuri de cate opt registre generale RO, RI, ... R7 in spatiul de memorie de date 00 - IFH; din cele patru bancuri este selectat intotdeauna numai un bane de registre generale eu ajutorul a doi indicatori RSI si RSO din registrul PSW aflat in SFR; registrele generale sunt locatii de memorie de opt biti, volatile, manevrabile individual de utilizator ~i constituie spatiul de lucru pentru utilizator.

- 1 OH= 16Z locatii de memorie adresate la nivel de octet si de bit in spatiul de memorie de date 20H-2FH;

- restul zonei de memorie din spatiul 30-7FH este adresabila numai la nivel de octet si este la dispozitia utilizatorului.

Adresa Semnificatie

0O-07H Bane ° de opt registre generale RO, RI, ... R7

OS-OFH Bane 1 de opt registre generale RO, RI, ... R7

10-17H Bane 2 de opt registre generale RO, RI, '" R7

lS-lFH Bane 3 de opt registre generale RO, RI, ... R7

20-2FH Zona de memorie adresabila la nivel de oetet ~i bit

30-7FH Zona de memorie adresabila la nivel de oetet _j Tabelul 1.1.

Zona de memorie de date interna adresabila indirect din spatiu de adrese SO-OFFH este la dispozitia utilizatorului si este disponibila numai la unele rnicrocontrolere din familia ATMEL

(ATS9C52 de exemplu).

1.3.2.2. Spatiul registrelor eu functii speciale

Registrele eu functii speciale (SFR) ale rnicrocontrolerului AT89C51 din zona de memorie adresabila direct (SO-'-OFFH) sunt precizate in tabelul 1.2.

T oate aceste registre sunt de 8 biti si au semnificatia:

- registrul acumulator ACC (se utilizeaza notatia A de cele mai multe ori); este eel mai important registru pentru realizarea transferurilor de date intre diverse resurse ~i a operatiilor aritmetice si logice cu doi operanzi;

- 1.6 -

I

- registrul B; utilizat cu precadere la operatiile de inmultire ~i impartire;

- registrul indicator de conditii (flaguri) PSW; contine informatii referitoare la rezultatul

operatiilor aritmetice si logice;

- registrul indicator de stiva SP; contine in permanents adresa varfului de stiva, Stiva este o zona de memorie de tip LIFO care retine 0 succesiune de date;

- registrul pentru adresarea memoriei exteme DPTR; acest registru de 16 biti este alcatuit din doua registre de 8 biti: DPH care este partea high a registrului DPTR si DPL care este partea Iowa registrului DPTR;

- registre pentru cele patru porturi paralele de 8 biti: PO, PI, P2 ~i P3;

- registre pentru cele doua numaratoare de 16 biti (TO ~i Tl) TMOD, TCON, THO, TLO,

THI, TLI (programare, date);

- registre pentru interfata seriala asincrona SCON, SBUF (programare, date);

- registre pentru intreruperi IP, IE;

- registrul pentru modul de lucru consum redus PCON.

SFR +0 +1 +2 +3 +4 +5 +6 +7

80H PO SP DPL DPH - - - PCON

88B TCON TMOD TLO TLI THO TBI - -

90B PI - - - - - - -

98B SCON SBUF - - - - - -

AOH P2 - - - - - - -

A8B IE - - - - - - -

BOH P3 - - - - - - -

B8H IP - - - - - - -

COH - - - - - - - -

C8H - - - - - - - -

DOH PSW - - - - - - -

D8H - - - - - - - -

EOH ACC - - - - - - -

E8H - - - - - - - -

FOH B - - - - - - -

F8H - - - - - - - - Tabelul l.2.

Din registrele enumerate mai sus, registrele A, B, PSW, SP, DPTR sunt de baza. Locatiile de memorie cu adresele divizibile prin opt (80H, 88H, 90H, 98H, ... , F8H) din spatiul registrelor cu functii speciale sunt adresabile la nivel de octet si de bit.

- 1.7 -

1.3.2.3. Semnificatia principalelor registre ale microcontrolerului A T89C51

Semnificatia principalelor registre (de baza) ale microcontrolerului AT89C51 este prezentata in paragrafele urmatoare.

Registrul acumulator ACC (notat in cele mai multe cazuri cu A) este unul din cele mai importante registre. Acest registru este utilizat in cele mai muIte instructiuni de transfer a datelor si in toate instructiunile aritmetice ~i logice cu doi operanzi cand unul din operanzi este in acumulator, iar rezultatul operatiei este depus tot in acumulator; accesarea memoriei de date externe pentru citirea sau pentru scrierea unei date se poate realiza numai prin interrnediul registrului acumulator.

Registrul Beste utilizat in operatiile de inmultire si impartire. Pentru aceste instructiuni unul din operanzi si 0 parte din rezultat este in acest registru.

Registrul indicator de conditii PSW este alcatuit din asocierea mai multor circuite basculante bistabile numite indicatoare de conditii sau flaguri. Acest registru of era informatii despre rezultatele operatiilor aritmetice ~i logice.

Structura registrului PSW este redata in tabelul 1.3:

Bit7 Bit6 BitS Bit4 Bit3 Bit2 Bitt BitO

C AC FO RSI RSO OV PSW.l P Tabelul 1. 3.

Semnificatia indicatoarelor din PSW este urmatoarea:

- C - indicator de transport; unitatea aritmetica si logica (UAL) a microprocesorului din microcontroler efectueaza operatii aritmetice pe 8 biti ~i este posibil ca in urrna executarii unei instructiuni de adunare sau scadere sa apara un transport din bitul 7 catre bitul 8, respectiv un imprumut din bitul 8 catre bitul 7. Indicatorul de transport in starea setat indica un transport din bitul 7 in bitul 8 sau un imprumut din bitul 8 in bitul 7 in urrna executarii unei instructiuni de adunare, respectiv de scadere.

- AC - indicator de transport auxiliar; in starea setat indica un transport din bitul 3 in bitul 4 dupa executarea unei instructiuni de adunare sau un imprumut din bitul 4 in bitul 3 dupa executarea unei instructiuni de scadere.

- FO - indicator aflat la dispozitia utilizatorului.

- RSl, RSO sunt doi indicatori utilizati pentru select area unui bane de opt registre

generale din cele patru bancuri ale microcontrolerului, ca in tabelul 1.4.

- 1.8 -

RSI RSO Registre generale Spatiu adrese

0 0 BancO 00 - 07H

0 1 Bane 1 08 - OFH

1 0 Banc2 10 - 17H

1 1 Bane 3 18 - 1FH Tabelul 1A.

- OV - indicator de depasire; in cazul operatiilor aritmetice cu semn, cei mai putin semnificativi 7 biti sunt destinati valorii numerice, iar bitul eel mai semnificativ este destinat semnului (0 - semn pozitiv; 1 - semn negativ). in urma executarii unei instructiuni de adunare poate sa apara un transport din bitul 6 catre bitul 7 sau in urma executarii unei instructiuni de scadere poate sa apara un imprumut din bitul 7 catre bitul 6. In acest mod, este afectat bitul de semn in cazul operatiilor aritmetice cu semn. Indicatorul de depasire in starea setat indica un transport din bitul 6 In bitul 7 sau un imprumut din bitul 7 catre bitul 6 in urma executarii unei instructiuni de adunare, respectiv de scadere.

- PSW.l - indicator rezervat.

- P - indicator de paritate; in starea setat indica un numar impar de biti 1 sau 0 din

registrul acumulator.

Registrul indicator de stivi SP este de 8 biti. Stiva este 0 zona de memorie de tip LIFO (ultimul intrat - primul iesit) capabila sa retina istoria unei succesiuni de evenimente (In cazul nostru de date). Registrul indicator de stivi contine in permanents adresa varfului de stiva, deci adresa de la care se pot face operatii de scriere si de citire cu stiva. Pentru microcontrolerele din familia ATMEL stiva poate fi definita numai in memoria interna de date si este crescatoare (la fiecare salvare se incrementeaza SP, iar la fiecare restaurare se decrernenteaza SP). In urma resetarii microcontrolerului registrul SP este initializat cu 07H, dar prin soft SP poate fi initializat cu orice valoare numerica din gama de valori posibile. Stiva constituie un mod util si convenabil de lucru pentru salvarea si restaurarea datelor din registre, dar care poate fi inlocuit.

Stiva este absolut necesara atunci cand se lucreaza cu subrutine. Cand intr-un program de baza se intalneste 0 instructiune de apel subrutina CALL ADR, se abandoneaza secventa de instructiuni a programului apelant, apoi se executa instructiunile subrutinei care incep de la adresa ADR, iar la intalnirea instructiunii RET care marcheaza sfarsitul subrutinei se revine in programul intrerupt, la instructiunea imediat urmatoare dupa CALL ADR. Instructiunea de apel subrutina salveaza In varful stivei adresa urmatoarei instructiunii de dupa CALL ADR din programul apelant

- 1.9 -

~i incarca numaratorul de program cu adresa ADR, iar la executarea instructiunii RET se restaureaza in numaratorul de program adresa de revenire in programul principal (apelant) prin citirea celor doi octeti din stiva. Trebuie avuta 0 grija deosebita atunci cand se utilizeaza stiva, deoarece in stiva se pot salva date din registrele programului, dar ~i adresele de revenire din subrutine; la restaurare se pot inversa aceste date dintr-o eroare de program, caz in care se pierde controlul microprocesorului.

Registrul pentru adresarea memoriei exteme DPTR este de 16 biti; cu ajutorul acestui registru se poate citi si scrie continutul locatiilor de memorie de date extema.

Celelalte registre din SFR sunt destinate circuitelor periferice ce sunt tratate ca locatii de memorie ~i vor fi prezentate pe larg in alte capitole.

Registrul numarator de program PC este de 16 biti, nu face parte din SFR, dar este un registru important. Registrul PC contine in permanents adresa instructiunii ce urmeaza a fi executata de microprocesorul din microcontroler. Dupa ce a fost citit codul instructiunii curette din memoria program (ciclu fetch), continutul registrului PC este increment at automat cu 0 unitate pentru a se putea citi urmatorii octeti din instructiune sau codul instructiunii urmatoare. In acest mod, se asigura secventialitatea de executare a unui sir de instructiuni dintr-un program. Instructiunile se executa una dupa alta in ordinea crescatoare a adreselor din memoria care contine programul de comanda; de la aceasta regula se abat instructiunile de rarnificare care incarca numaratorul de program cu 0 anumita adresa de salt. Dupa initializarea microcontrolerului se executa instructiunile aflate In memorie de la adresa OR.

1.3.3. Executarea unei instructiuni de microcontroler

Instructiunile microcontrolerelor de opt biti din familia ATMEL sunt de lungime variabila, cuprinsa intre 1-3 octeti, iar primul octet reprezinta intotdeauna codul instructiunii.

Memoria program interna sau externa a microcontrolerului este organizata pe cuvinte cu lungimea de un octet, iar pozitia fiecarui octet din memorie este caracterizata de 0 adresa de 16 bili·

Un program de comanda ce urmeaza a fi executat de microprocesoruI din microcontroler este incarcat in memoria program interna sau externa (MP) in locatii consecutive, iar executia fiecarei instructiuni decurge conform fig. lA. si a etapelor prezentate in continuare.

-1.10-

MP

(internalexternA

r-----, BA

I PC Ml~'"

..... I

'- _____ 1 adresa

~UCC-~ PSEN CE

.:..:.i! ••• comanda citire MP

t------:-+

..... !DEC:

r-----I BD

I 1 Do-D7

I RI I'" cod instructiune

!...-----, )

Fig. 1.4.

Continutul registrului numarator de program este plasat pe busul de adresa BA (intern sau extern), indicand adresa locatiei de memorie in care se ami codul instructiunii ce urmeaza a fi executat. Dupa ce continutul registrului PC este plasat pe busul de adresa, se realizeaza incrementarea cu 0 unitate a numaratorului de program. in continuare, unitatea de comanda ~i control genereaza un semnal intern sau extern de citire a memoriei program PSEN (se aplicaun nivel 0 logic la pinul de selectie al memoriei).

Dupa trecerea timpului de acces la memorie, starea de impedanta ridicata a liniilor de date este parasita ~i codul instructiunii va fi disponibil pe busul de date BD.

in acest mod, codul de instructiune lecturat din memoria program de la adresa furnizata de PC este incarcat de pe busul de date in registrul de instructiuni, Din acest moment, semnalul de comanda PSEN devine inactiv ~i memoria program este deselectata. Continutul registrului de instructiuni este decodificat, iar UCC furnizeaza toate semnalele de comanda necesare pentru executarea instructiunii. in situatia cand instructiunea in curs de executie are doi sau trei octeti, urmeaza citirea octetilor respectivi, iar apoi executarea instructiunii respective.

Dupa ce instructiunea a fost executata, se plaseaza in continuare continutul registrului numarator de program pe busul de adresa, se genereaza semnalul de cornanda PSEN de citire a urmatorului cod de instructiune s.a.m.d.

Regula generala pentru executarea instructiunilor dintr-un program este aceea ca instructiunile se executa una dupa alta in ordinea intalnirii acestora. De la aceasta regula se abat instructiunile de ramificare (salt, apel subrutina, revenire din subrutina) care incarca numaratorul de program cu 0 anumita adresa de salt.

Dupa initializarea microcontrolerului se executa instructiunile aflate in memoria program de la adresa OOOOH.

-1.11-

1.4. Conexiunile externe ale microcontrolerului AT89C51

Conexiunile ext erne ale microcontrolerului AT89C5l pot fi grupate astfel: - 2 pentru oscilatorul de tact intern;

- 4 pentru semnalele de comanda;

- 2 pentru alimentare;

- 32 pentru liniile de intrare/ iesire ale celor patru porturi paralele (PO, PI, P2, P3) de cate

8 biti fiecare (inclusiv liniile pentru interfata seriala, numaratoare, controlerul de tratare a cererilor de intrerupere externa).

Microcontrolerul A T89C5l are conexiunile ext erne precizate in fig. 1.5.

AT89C5 I

PI P2 - As.15

Fig. l.5.

Semnificatiile conexiunilor ext erne ale microcontrolerului sunt urmatoarele:

- XTALI, XTAL2 - conexiuni ale oscilatorului de tact intern la care se conecteaza

elementele externe (cristalul de cuart si doi condensatori ceramici); - RS T - intrarea de initializare a microcontrolerului;

- EA - intrare pentru configurarea microcontrolerului cu magistrale externe;

- ALE - iesire de comanda pentru demultiplexarea partii Iowa busului de adresa de busul

de date;

- PSEN - iesire de comanda pentru selectia memoriei program externe;

- V oc- GND - conexiuni pentru alimentarea microcontrolerului de la sursa de tensiune

continua de +5V;

- POO+7 (AO_7 / Do_7) - conexiuni externe utilizate ca linii de intrare/ iesire pentru portul PO (EA = 1) sau ca magistrala bidirectionala care multiplexeaza partea Iowa busului de adresa cu

-1.12-

busul de date (EA = 0).

- P10+7 - conexiuni ext erne utilizate numai ca linii de intrarel iesire pentru portul Pl.

- P20+7 (As_Is) - conexiuni externe utilizate ca linii de intrarel iesire pentru portul P2 (EA= 1)

sau ca partea high a busului de adresa (EA=O).

- P30+7 - conexiuni ext erne utilizate ca linii de intrarel iesire pentru portul P3 (EA=1). In cazul in care microcontrolerul este configurat cu magistrale ext erne (EA=O)se modifies semnificatia urmatoarelor doua linii ale portului astfel:

- P3.7 devine RD - semnal de comanda de iesire pentru citirea din memoria de date externa a microsistemului;

- P3.6 devine WR - semnal de comanda de iesire pentru scrierea in memoria de date externa a microsistemului.

Indiferent de valoarea Iogica a intrarii EA, celelalte conexiuni ext erne ale portului P3 sunt

utilizate de circuitele periferice interne ale microcontrolerului astfel: - P3.5 devine Tl - intrare in numaratorul de 16 biti Tl;

- P3.4 devine TO - intrare in numaratorul de 16 biti TO;

- P3.3 devine INTI - intrare pentru 0 cerere de intrerupere externa (INTI) de la un

proces extern;

- P3.2 devine INTO - intrare pentru 0 cerere de intrerupere externa (INTO) de la un proces extern;

- P3.I devine TxD - iesire pentru transmiterea serie asincrona a datelor;

- P3.0 devine RxD - intrare pentru receptionarea serie asincrona a datelor.

Pentru a furniza in exteriorul microcontrolerului busurile de adresa, date $i unele semnale de comanda, se utilizeaza liniile porturilor paralele care, dupa cum am vazut mai sus, au 0 semnificatie dubla, Porturile paralele au fiecare cate un registru intern in SFR care au acelasi nume ca $i portul caruia Ii corespund. La initializarea microcontrolerului toate porturile paralele sunt de intrare, iar registrele porturilor de iesire sunt incarcate cu OFFH. Cand 0 linie din port sau intreg portul trebuie sa fie utilizat ca linie sau port de intrare, dupa ce a fost utilizat ca linie sau port iesire este absolut necesar ca bistabilul sau registrul de iesire corespunzator sa fie setat. In caz contrar, se poate distruge bufferul de iesire al portului respectiv.

Microcontrolerul A T89C51 este un circuit integrat cu 40 conexiuni externe si este realizat in capsule PDIP40 cu 40 pini, PLCC44 cu 44 pini sau PQFPITQFP cu 44 pini.

-1.13-

1.4.1. Oscilatorul de tact

Microcontrolerul AT89C51 are oscilatorul de tact intern, iar la conexiunile externe XTALI ~i XTAL2 se conecteaza un cristal de cuart cu frecventa maxima de 24 MHz ~i doi condensatori de 30 pF, ca in fig. 1.6.

AT89C51

Fig. 1.6.

Conexiunea externa XTALI este intrarea in amplificatorul inversor al oscilatorului de tact intern, iar XTAL2 este iesirea din acest oscilator (amplificator inversor).

Cele doua conexiuni externe XTALI ~i XTAL2 la care sunt conectate elementele externe (cristalul de cuart si condensatoarele) constituie impreuna cu structura interna (amplificatorul inversor) un oscilator de semnal dreptunghiular. Acest oscilator este utilizat pentru comanda circuitului de tact intern al microeontrolerului, iar frecventa semnalului de tact intern (STI) este jumatate din frecventa oscilatorului. Semnalul de tact cu perioada Tose (Tose=lIfosd permite definirea urmatoarelor notiuni: faza interna P (egala cu T oscl- stare interna S (alcatuita din doua perioade T oscl si ciclu masina CM (compus din sase stari),

Structura de principiu a oscilatorului de tact intern din microcontrolerele realizate in tehnologie CMOS este redata in fig. 1.7; GC este geratorul de clock intern care ill principiu, realizeaza divizarea eu doi a semnalului de tact fose.

AT89C51

STI

Fig. 1.7.

Microeontrolerele din familia ATMEL pot fi comandate ~i de oseilatoare de tact exteme. Microcontrolerele realizate in tehnologie CMOS conecteaza semnalul de tact extern la terrninalul XTALI prin intermediul unei porti logice CMOS, iar terminalul XTAL2 ramane neconectat ca in fig. 1.8.

- 1.14 -

CMOS

AT89C51

Osc extern

NC XTAL2

Fig. 1.8.

1.4.2. Structura ciclurilor masina

Executarea unei instructiuni de catre rnicroprocesorul din rnicrocontroler consta dintr-o secventa specifics de operatii. In primul rand se incarca codul instructiunii din memoria program in registrul de instructiuni, apoi se executa instructiunea respectiva, care consta din executarea unui transfer de date, a unei operatii aritmetice sau logice sau a unui salt la 0 alta instructiune. Toate activitatile pentru executarea unei instructiuni se realizeaza intr-un ciclu instructiune (Cl) care este alcatuit din unul, doua sau patru cicluri masina (eM). Orice instructiune incepe cu un ciclu masina care realizeaza intotdeauna citirea codului respectiv, dupa care urmeaza executarea instructiunii.

Fiecare ciclu masina este alcatuit din sase stan numerotate de la Slla S6, iar fiecare stare este alcatuita din doua faze care sunt notate cu PI si P2. 0 faza corespunde cu 0 perioada a generatorului de tact; prin urmare 0 stare are durata a doua perioade de tact, iar un ciclu masina are durata a 12 perioade de tact.

Un ciclu masina este reprezentat in fig. 1.9 cu cele sase stari alcatuite fiecare din cate doua perioade ale oscilatorului de tact Tosc. Orice ciclu rnasina are durata de 0,5 J.1s daca frecventa oscilatorului de tact este de 24 MHz. Fiecare ciclu masina incepe cu SIPI si se termina cu S6P2.

·

;..

CM

lr\!f3:1" :rlrt:n:1'\ :n:r! :n:1'\ :f3l

I .. I • I I ••• I I I •

• ••••••• I I , ••

T osc i .... -=....;::=-=·~: ~'=-..;:=--='::.....;:: =-=' ~:=-:.::.....;:: =-=' ~.;:::. ~~ t

• • • t I I •

l.s 1. :.s.;1.s3~;.S4~j4s5~': ... S6IJ

Fig. l.9.

Instructiunile de rnicrocontroler au lungimea de unul, doi sau trei octeti si se executa in unul, doua sau patru cicluri masina. Pentru instructiunile microcontrolerului AT89C51 cazurile

-l.I5 -

posibile rezultate din combinarea numarului de octeti si durata executarii sunt redate in tabelul 1.5.

I Nr. octeti I Nr. de cicluri masina I

,

1 1

1 2

1 4

2 1

2 2

3 2 Tabelul 1.5.

Ciclurile pentru instructiunile microcontrolerelor din familia ATMEL constau din secvente de 1, 2 sau 4 cicluri masina, in functie de numarul de octeti din instructiune ~i de tipul acesteia.

1.4.3. Initializarea microcontrolerului

Intrarea de initializare RST a microcontrolerului AT89C51 este 0 intrare intr-un trigger Schmitt, activa pe nivel 1 logic. Pentru a se realiza initializarea microcontrolerului este necesar ca oscilatorul de tact sa fie operational minim 24 perioade de tact eu semnalul RST activo Dupa 0 temporizare de maxim 12 perioade de tact ale oseilatorului de tact se genereaza intern un semnal de reset care initializeaza microcontrolerul; totodata, semnalele de cornanda ALE ~i PSEN sunt eonfigurate ca intrari prin fortarea aeestora in 1 logic (sernnale cvasibidirectionale). Semnalul intern de reset realizeaza initializarea microcontrolerului in timpul celui de al doilea ciclu masina in care RST este activ; operatia de initializare a microcontrolerului este repetata in fiecare ciclu masina daca RST se mentine activ ~i se termina de executat, atunci cand RST devine inactiv.

Dupa initializarea microcontrolerului, resursele interne se incarca cu urmatoarele valori:

PC+-OOOOH, dupa initializare se executa instructiunile care se afla in memoria program de . la adresa OOOOH;

A, B, PSW+-OOH; registrul aeumulator A, registrul B si registrul cu indieatorii de conditii PSW se initializeaza cu zero (este selectat bancul 0 de registre generale);

SP+-07H, indicatorul de stiva este initializat eu adresa 07H din memoria de date interna a rnicrocontrolerului; stiva este definita in memoria de date interna incepand de la adresa 08H; DPTR+-OOOOH, registrul care adreseaza memoria externa se initializeaza cu zero;

PO, PI, P2, P3+-0FFH, porturile paralele sunt incarcate cu FFH pentru a putea fi utilizate dupa initializare ea porturi paralele de intrare;

-1.16-

TMOD, TCON, THO, TLO, THI, TLI +-OOH, numaratoarele TO si TIsunt initializate; SCON+-OOH, interfata seriala este initializata;

SBUF+-XXXXXXXXB (X semnifica 0 valoare binara nedeterminata); IE+-OXXOOOOOB, dezactivarea surselor de intrerupere;

IP+- XXXOOOOOB, stabilirea nivelului inferior de prioritate pentru toate sursele de

intrerupere interne si exteme;

PCON+-OXXXOOOOB, dezactivare mod de lucru consum redus; ALE, PSEN+-I, semnalele de comanda sunt dezactivate.

Memoria de date interns (partea low ~i partea high) ~i memoria externa de date nu este afectata de initializarea microcontrolerului.

Structura hard minimala necesara pentru initializarea microcontrolerului AT89CSI este redata in fig. 1.10; aceasta structura trebuie sa realizeze initializarea automata a microcontrolerului la fiecare conectare a sursei de alimentare ~i initializarea manuala de catre utilizator prin actionarea unui comutator. .

AT89C51

Fig. l.10.

La conectarea sursei de alimentare de tensiune continua, condensatorul C de 1 O~F este scurtcircuitat, iar intrarea de initializare a microcontrolerului RST este conectata la +SY. in acest mod, se realizeaza initializarea automata a microcontrolerului cand se conecteaza sursa de aliment are de tensiune continua prin plasarea intrarii RST la nivelul 1 logic. in continuare, condensatorul C incepe sa se incarce prin intermediul rezistentei R de 10 ill, iar tensiunea pe rezistenta R incepe sa scada. Atunci cand tensiunea de la intrarea de initializare RST a scazut sub nivelul pragului de jos al triggerului Schmitt intern aflat la intrarea RST, se comuta iesirea triggerului din 1 logic in 0 logic. Dioda 1 N4148 are rolul de a scurtcircuita condensatorul C, atunci cand se intrerupe aliment area de la sursa de tensiune continua.

Se incheie astfel operatia de initializare a microcontrolerului, dupa care se executa programul de comanda utilizator aflat in memoria program de la adresa OOOOH.

In timpul executarii programelor utilizator, dar cu precadere in timpul testarii unor programe de aplicatie, este po sibil ca microprocesorul din microcontroler sa intre in executarea

-1.17-

unor bucle infinite de instructiuni. De asemenea, este posibil sa se blocheze functionarea microprocesorului din microcontroler datorita unor factori externi, a structurii hard nefiabile a sistemului, etc. in aceste situatii este necesar sa se realizeze 0 initializare rnanuala a microcontrolerului prin actionarea unui comutator.

La actionarea comutatorului K de catre utilizator, condensatorul C de lOflF se descarca pe rezistenta de 100 Q, iar tensiunea la intrarea de initializare RST devine 4,95V (dupa descarcarea condensatorului C). Practic, in timpul descarcarii condensatorului C, tensiunea pe rezistenta R de 10 ill incepe sa creasca. Atunci cand tensiunea de la intrarea RST a crescut peste nivelul pragului de sus al triggerului Schmitt intern de la intrarea RST, se cornuta iesirea triggerului din 0 logic in 1 logic. Se realizeaza astfel initializarea manuala a microcontrolerului. Operatia de initializare se incheie atunci cand utilizatorul deschide comutatorul K. Condensatorul C incepe sa se incarce prin intermediul rezistentei R, iar cand tensiunea de la intrarea RST a scazut sub nivelul pragului de jos al triggerului Schmitt intern se cornuta iesirea acestuia din 1 logic in 0 logic; initializarea este astfel incheiata, iar microprocesorul incepe executarea programului de comanda de la adresa OH.

1.4.4. Configurarea microcontrolerului

Microcontrolerele din familia ATMEL (AT89C51) sunt configurate cu magistrale externe in functie de nivelullogic aplicat la terminalul EA, astfel:

- daca EA este conectat la 0 logic (GND), atunci microsistemul de comanda cu microcontroler are magistrale externe care se obtin din porturile paralele; programul de cornanda se afla in memoria program externa, iar utilizatorul nu mai poate beneficia de porturile paralele utilizate ca magistrale (fig. 1.11).

AT89C51

BAo..7/BD~7 ~IS

RD

WR

PIJE!}'7

PIlEu-s

Fig. 1.11.

- daca EA este conectat la 1 logic (V cd, atunci microcontrolerul nu are magistrale ext erne; programul de cornanda se afla in memoria program interna, iar cele patru porturi paralele ale microcontrolerului AT89C51 se utilizeaza pentru diverse aplicatii (fig. 1.12).

-1.18-

AT89C51

+5V EA

Fig. 1.12.

in cazul utilizarii microcontrolerului cu magistrale ext erne, porturile paralele PO, P2 si P3 indeplinesc functia de busuri de date, adrese si comenzi astfel:

- portul PO furnizeaza partea Iowa busului de adresa BAo_7 multiplexata cu busul de date BDo_7; in cadrul ciclurilor masina la fiecare accesare a memoriei program sau de date ext erne, pe liniile portului PO este furnizata partea Iowa busului de adresa care va fi memorata intr-un latch extern, apoi portul PO devine bus de date;

- portul P2 furnizeaza partea high a busului de adresa BA8_I5;

- portul P3 furnizeaza pe linia P3.6 semnalul de comanda pentru scrierea (WR) unei date

in memoria externa de date, iar pe linia P3.7 semnalul de comanda pentru citirea (RD) unei date din memoria externa de date.

1.4.5. Demultiplexarea busurilor

In cazul unui microsistem de comanda cu microcontroler cu magistrale ext erne este necesara demultiplexarea busurilor. in structura interna a microcontrolerului a fost necesara operatia de multiplexare a partii Iowa busului de adresa cu busul de date pentru a micsora numarul de conexiuni externe.

Cu semnalul de comanda ALE se realizeaza demultiplexarea partii Iowa busului de adresa de busul de date. Pentru demultiplexarea busurilor se utilizeaza un circuit latch (registru) extern eu opt bistabile de tip D (de exemplu, se poate utiliza circuitul 74373).

Cu structura hard din fig. 1.13 se demultiplexeaza busurile; pe frontul descendent al semna1ului ALE se memoreaza in latchul extern 74373 partea Iowa busului de adresa, apoi liniile portului PO devin bus de date. Iesirile din latchul extern contin din acest moment partea Iowa busului de adresa; partea high a busului de adresa este furnizata de liniile portului P2.

Circuitul 74373 contine opt circuite bistabile de tip D; fiecare bistabil are cate 0 intrare de date D ~i care 0 iesire Q. Cele opt bistabile sunt validate daca intrarea E este conectata la 0 logic.

-1.19-

AT89C51

BD0-7

74373

BAo.7

Fig. l.13.

Pe frontul descendent al semnalului tact T comun celor opt bistabile se realizeaza memorarea datelor binare de la intrarile D in bistabilele corespunzatoare; la iesirile Q ale bistabilelor sunt furnizate datele binare memorate pana cand se realizeaza urmatoarea operatie de memorare

(urmatorul front descendent de pe semnalul de tact T).

1.4.6. Selectia memoriei program externe

Selectia memoriei program externe se realizeaza cu semnalul de comanda PSEN (iesire act iva pe 0 logic). Selectarea unei memorii program externe de tipul EPR0M27256 care are 0 capacitate de 32 kocteti in spatiul de adrese 0000-:-7FFFH se face ca in fig. 1.14.

:MP - EPR0M27256

0000-7FFFH

Fig. l.14.

Pe liniile de adrese ~i de date ale memoriei program se conecteaza liniile omoloage din busul de adrese si date al rnicrosistemului cu microcontroler (dupa demultiplexarea busurilor).

La pinul OE al memoriei program se conecteaza semnalul PSEN pentru a selecta circuitul numai cand se citeste codul instructiunii, iar la pinul CE al memoriei program se conecteaza linia de adresa BA15 pentru a selecta memoria in spatiul de adrese 0000-:-7FFFH.

Memoria program este adresata intotdeauna in spatiul de memorie care incepe de la adresa OOOOH; dupa initializarea rnicrocontrolerului (PC+-OOOOH) se incepe executarea instructiunilor aflate in memoria program de la adresa OOOOH.

- 1.20 -

1.4.7. Selectia memoriei de date externe

Selectia memoriei de date ext erne se realizeaza cu ajutorul semnalelor de comanda RD si WR care sunt sernnale de iesire din portul P3 al rnicrocontrolerului. Activarea sernnalului de comanda RD determina citirea memoriei de date externe de la adresa precizata de registrul DPTR sau de portul P2 (pentru partea high) ~i de registrul Rj 0=0 sau j=1 pentru partea low); continutul locatiei de memorie este incarcat intotdeauna in registrul acumulator. Activarea sernnalului de comanda WR determina scrierea memoriei de date ext erne cu valoarea continuta in registrul acumulator la adresa precizata de registrul DPTR sau de portul P2 (pentru partea high) si de registrul Rj 0=0 sauj=l pentru partea low).

Selectarea unei memorii de date ext erne de tipul SRAM55257 cu 0 capacitate de 32 kocteti in spatiul de adrese 800070FFFFH se face ca in fig. 1.15.

MD - SRAM55257 8000H-OFFFFH

Vee +5V

7404

Fig. 1.15.

Pe liniile de adrese ~i de date ale memoriei de date se conecteaza liniile omoloage din busul de adrese ~i de date al microsistemului cu rnicrocontroler (dupa demultiplexarea busurilor).

La pinul W al memoriei de date se conecteaza sernnalul de comanda WR pentru scrierea datelor in memorie. La pinul OE al memoriei de date se conecteaza 0 poarta logica SI (7408) care are la cele doua intrari sernnalele de comanda RD si WR in acest caz, circuitul este selectat numai cand se citeste 0 data din memorie, respectiv cand se scrie 0 data in memorie. La pinul CE a1 memoriei de date se conecteaza linia de adresa BA15 negata prin intermediul unui circuit logic inversor (7404) care selecteaza memoria de date in spatiul de adresa 800070FFFFH.

in spatiul de memorie externa pot fi selectate memorii cu 0 capacitate maxima de 64 kocteti.

Este indicat sa se utilizeze un singur cip de memorie cu capacitatea necesara (:::;64 kocteti),

- 1.21 -

1.5. Structura mierosistemului eu microeontrolerul A T89C51 pentru aplicatii

Orice microcontroler are un numar ridicat de intrari si iesiri care permit 0 interfatare simpla cu diferite aplicatii din mediul extern. Structura hard a unui microsistem cu microcontrolerul AT89C51 se reduce practic la un circuit integrat, ceea ce conduce la urmatoarele avantaje: volum mic, fiabilitate ridicata, consum de energie redus, pre] de cost mic.

In aceste conditii, structura hard pentru un proces de aplicatie este foarte simpla (fig. 1.16).

AT89C51

2x39PF

.rl XTALI

24MHzCl

r1 XTAL2

+5V EA PO

~ 100 IOIJF PI

RST Interfata

P2 Proces

P3

GND

Fig. 1.16. Aceasta structura hard contine sistemul cu microcontroler ( elementele pentru circuitul de tact, eireuitul de initializare ~i blocul de alimentare), interfata proeesului ~i procesul utilizator respectiv. Domeniile de utilizare eficienta ale unui mierocontroler sunt acelea in care eel putin unul dintre avantajele anterioare este esential, ca in cazul bunurilor de larg consum, al unitatilor de comanda si control industrial, in tehnica de calcul, in aparatura de masura si de automatizare, etc.

1.6. Instructiunile microcontrolerului A T89C51

o instructiune este un set de earactere binare care este recunoscut si executat de microprocesorul din microcontroler, conducand intotdeauna la realizarea acelorasi actiuni. Instructiunile se exprima sub forma de siruri binare (sau hexazeeimale prin gruparea bitilor cate patru) sau sub forma de mnemonice (grupari de litere care sugereaza actiunea de executat).

Instructiunile microcontrolerelor de 8 biti din familia A TMEL se clasifica in instructiuni de transfer de date, instructiuni aritmetice ~i logiee ~i instructiuni de ramificare. Pentru fieeare tip de instructiune se prezinta in eontinuare forma simbolica si 0 descriere sumara a acestora.

- 1.22 -

1.6.1. Instructiuni de transfer de date

Transferurile de date constau in copierea datelor din unele resurse ale rnicrocontrolerului In alte resurse ale acestuia (memoria de date interna, spatiul registrelor cu functii speciale, memoria de date externa, memoria program).

1.6.1.1. Instructiuni de incarcare imediata eu date

Forma simbolica

A~d8H

Descriere Registrul acumulator A este incarcat imediat eu data d8H.

Forma simbolica A ~OOH

Descriere Registrul acumulator A este incarcat imediat eu data OOH (instructiune de un octet).

Forma simbolica Ri~d8H

Descriere Registrul general Ri (i=O, 1, ... 7) este incarcat imediat eu data d8H.

Forma simbolica (a8H)~d8H

Descriere Locatia de memorie de date interna cu adresa a8H este incarcata imediat eu data d8H.

Forma simbolica (Rj)~d8H

Descriere Locatia de memorie de date intema eu adresa precizata in registrul general Rj G=O sau j= 1) este incarcata imediat eu data d8H.

Forma simbolica DPTR~d16H

Descriere Registrul DPTR pentru adresarea memoriei exteme este incarcat imediat eu data d 16H

1.6.1.2. Instructiuni de transfer de date intre registre si/sau locatii de memorie de date interne

Forma simbolica

Descriere Continutul registrului general Ri (i=O, 1, ... 7) este transferat in aeumulatorul A

Forma simbolica

Ri~A

Descriere Continutul aeumulatorului A este transferat in registrul general Ri (i=O, 1, ... 7).

Forma simbolica A~(a8H)

Descriere Continutul locatiei de memorie de date intema eu adresa a8H este transferat in

- 1.23 -

registrul acumulator A.

Forma simbolica (a8H)+-A

Descriere Continutul registrului acumulator A este transferat in locatia de memorie de date interns eu adresa a8H.

Forma simbolica

Ri+-(a8H)

Descriere Continutul locatiei de memorie de date interna eu adresa a8H este transferat in registrul general Ri (i=O, 1, ... 7).

Forma simbolica (a8H)+-Ri

Descriere Continutul registrului general Ri (i=O, 1, ... 7) este transferat in locatia de memorie de date interna eu adresa a8H.

Forma simbolica A+-(Rj)

Descriere Continutul locatiei de memorie de date internacu adresa precizata in registrul general Rj 0=0 sau j= 1) este transferat in registrul aeumulator A.

Forma simbolica (Rj)+-A

Descriere Continutul registrului acumulator A este transferat in locatia de memorie de date interna eu adresa precizata in registrul general Rj 0=0 sau j= 1 ).

Forma simbolica (a8H)+-(Rj)

Descriere Continutul locatiei de memorie de date interna eu adresa precizata in registrul general Rj 0=0 sau j= 1) este transferat in locatia de memorie de date interns eu adresa a8H.

Forma simbolica (Rj)+-(a8H)

Descriere Continutul locatiei de memorie de date interna eu adresa a8H este transferat in locatia de memorie de date interna eu adresa precizata in registrul general Rj G=O sau j= 1).

Forma simbolica (a8dH)+-(a8sH)

Descriere Continutul locatiei de memorie de date interna eu adresa a8sH (sursa) este transferat in locatia de memorie de date interna eu adresa a8dH (destinatie).

1.6.1.3. Instructiuni de transfer de date Intre acumulator si memoria externa

Forma simbolica

(DPTR)+-A

Descriere Continutul registrului acumulator este transferat in locatia de memorie de date externa eu adresa precizata in registrul DPTR.

- 1.24 -

Forma simbolica

A+-(DPTR)

Deseriere Continutul locatiei de memorie de date externa cu adresa precizata in registrul DPTR este transferat in registrul acumulator A

Forma simbolica

(Rj)+-A

Deseriere Continutul registrului acumulator este transferat in locatia de memorie de date externa eu adresa precizata in registrul general Rj 0=0 sau j= 1). Pentru aceste instructiuni adresa memoriei de date externa este de 8 biti. Instructiunile sunt utilizate cand in structura hard a microsistemului cu microcontroler avem circuite periferice specializate tratate ca locatii de memorie sau circuite de memorie de capacitate mica (maxim 256 octeti). Daca se realizeaza 0 adresare pe 16 biti a circuite periferice sau a memoriei de date externa ~i se utilizeaza aceste instructiuni, atunci este necesar sa transmitem in portul P2 al microcontrolerului partea high a adresei, inainte de utilizarea instructiunii.

Forma simbolica A+-(Rj)

Descriere Continutul locatiei de memorie de date externa cu adresa precizata in registrul Rj 0=0 sau j= 1) este transferat in registrul acumulator.

Forma simbolica

A+-(A+DPTR)

Descriere Continutul locatiei de memorie program cu adresa precizata de suma dintre registrele A si DPTR este transferat in registrul acumulator A Acest mod de adresare indirecta indexata realizeaza numai citirea unor structuri (tabele) de date; registrul DPTR are rol de pointer.

Forma simbolica PC+-PC+ 1 A+-(A+PC)

Se utilizeaza ~i forma simbolica prescurtata A+-(A+PC+ 1).

Descriere Continutul locatiei de memorie program cu adresa precizata de suma dintre acumulatorul A ~i numaratorul de program PC este transferat in registrul acumulator A (PC a fast incrernentat in prealabil cu 0 unitate deoarece instructiunea are lungimea de un octet).

1.6.1.4. Instructiuni de lueru eu stiva

Forma simbolica

SP+-SP+l (SP)+-(a8H)

Se utilizeaza si forma simbolica prescurtata: (SP)+-(a8H)

- 1.25 -

Descriere Continutul locatiei de memorie de date interna eu adresa a8H este salvat in stiva la adresa precizata de indieatorul de stiva SP. Salvarea datelor in stiva se face la adrese crescatoare astfel: se incrementeaza eu 0 unitate SP ~i la adresa precizata de SP este salvat (seris) in stiva continutul locatiei de memorie de date interna eu adresa a8H.

Forma simbolica

(aSH)+-(SP) SP+-SP-l

Se utilizeaza ~i forma simbolica prescurtata (a8H)+-(SP).

Descriere Locatia de memorie de date interna eu adresa a8H este incarcata eu continutul stivei de la adresa precizata de indieatorul de stiva SP. Incarcarea datelor din stiva se face de la adrese descrescatoare astfel: continutul stivei de la adresa precizata de SP este transferat in locatia de memorie de date interna eu adresa a8H, apoi se decrementeaza eu 0 unitate SP.

1.6.1.5. Instructiuni de interschimbare

Forma simbolica

Descriere Continutul registrului aeumulator A este intersehimbat eu al registrului general Ri (i=O,l, ... 7).

Forma simbolica

A<H-(aSH)

Descriere Continutul registrului aeumulator A este intersehimbat eu al locatiei de memorie de date interna eu adresa a8H.

Forma simbolica

A<H-(Rj)

Descriere Continutul registrului aeumulator A este intersehimbat eu al locatiei de memorie interna de date eu adresa precizata in registrul general Rj 0=0 sau j= 1 ).

Forma simbolica

Descriere Continutul celor mai semnificativi patru biti din registrul aeumulator este intersehimbat eli al celor mai putin semnifieativi patru biti din acelasi registru acumulator (se realizeaza practic permutarea celor doua eifre hexazeeimale din aeumulator intre ele).

Forma simbolica

Descriere Continutul eelor mai putin semnifieativi patru biti din registrul aeumulator este intersehimbat eu al celor mai putin semnifieativi patru biti din locatia de memorie de date interna eu adresa precizata in registrul general Rj 0=0 sau j= 1). .

- 1.26 -

1.6.1.6. Instructiuni de incarcare ~i transfer de date la nivel de bit

Instructiunile de incarcare ~i transfer de date la nivel de bit opereaza eu locatiile de memorie de date intema care au adresele de la 20H pana la 2FH sau eu locatiile de memorie de date interna care au adresele divizibile eu opt din spatiul registrelor cu functii speciale (SFR).

Adresele la nivel de bit pentru zona de memorie de date interna cu adresele de la 20H pana la 2FH sunt redate in tabelul 1.6.

AdresaMD Adrese la nivel de bit pentru MD interns (20H - 2FH)

intema bit 7 bit6 bit5 bit4 bit3 bit2 bit I bitO

20H 07H 06H 05H 04H 03H 02H OIH OOH

2IH OFH OEH ODH OCH OBH OAR 09H 08H

22H I7H I6H I5H I4H 13H I2H llH IOH

23H IFH IEH IDH ICH IBH IAR I9H I8H

24H 27H 26H 25H 24H 23H 22H 21H 20H

25H 2FH 2EH 2DH 2CH 2BH 2AR 29H 28H

26H 37H 36H 35H 34H 33H 32H 31H 30H

27H 3FH 3EH 3DH 3CH 3BH 3AR 39H 38H

28H 47H 46H 45H 44H 43H 42H 41H 40H

29H 4FH 4EH 4DH 4CH 4BH 4AR 49H 48H

2AH 57H 56H 55H 54H 53H 52H 51H 50H

2BH 5FH 5EH 5DH 5CH 5BH 5AR 59H 58H

2CH 67H 66H 65H 64H 63H 62H 6lH 60H

2DH 6FH 6EH 6DH 6CH 6BH 6AR 69H 68H

2EH 77H 76H 75H 74H 73H 72H 7IH 70H

2FH 7FH 7EH 7DH 7CH 7BH 7AR 79H 78H Tabelul 1. 6.

Adresele locatiilor de memorie din spatiul registrelor eu functii speciale divizibile cu opt sunt: 80H (port PO), 88H (registrul de control TCON a1 nurnaratoarelor TO ~i TI), 90H (port PI), 98H (registrul de control al interfetei seriale SCON), AOH (port P2), A8H (registrul de validare a sistemului de intreruperi IE), BOH (port P3), B8H (registrul pentru stabilirea nivelului de prioritate la intrerupere IP), COH (-), C8H (-), DOH (registrul de flaguri PSW), D8H (-), EOH (registrul acumulator ACC), E8H (-), FOH (registrul B), F8H (-).

in tabelul 1.7 sunt redate adresele la nivel de bit pentru zona de memorie de date interna care au adresele divizibile cu opt din spatiul registrelor cu functii speciale; in paranteza sunt treeute cu litere mai miei denurnirile registrelor ~i a bitilor respectivi din SFR.

- l.27 -

Adresa Adrese la nivel de bit pentru registrele din SFR eu adresele divizibile prin opt

SFR (Denumire bit)

(Registru) bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit I bit 0

080H 87H 86H 85H 84H 83H 82H 8IH 80

(PO) (PO.7-AD7) (PO.6-AD6) (pO.S-ADS) (POA-AD4) (PO.3-AD3) (pO.2-AD2) (PO.I-ADI) (PO.O-ADO)

088H 8FH 8EH 8DH 8CH 8BH 8AH 89H 88H

(TCON) (TFI) (TRI) (TFO) (TRO) (IEI) (ITI) (lEO) (ITO)

090H 97H 96H 95H 94H 93H 92H 9IH 90H

(PI) (PI.7) (P1.6) (Pl.5) (PIA) (pl.3) (P1.2) (PU) (Pl.O)

098H 9FH 9EH 9DH 9CH 9BH 9AH 99H 98H

(SCON) (SMO) (SMl) (SM2) (REN) (TBB) (TB8) (TI) (RI)

OAOH OA7H OA6H OA5H OA4H OA3H OA2H OAIH OAOH

(P2) (P2.7-AlS) (p2.6-A14) (P2.S-A13) (P2A-AI2) (p2.3-All) (p2.2-AIO) (P2.1-A9) (P2.0-A8)

OA8H OAFH OAEH OADH OACH OABH OAAH OA9H OA8H

(IE) (EA) - - (ES) (EIl) (EXl) (ETO) (EXO)

OBOH OB7H OB6H OB5H OB4H OB3H OB2H OBIH OBOH

(P3) (P3.7-RD) (P3.6-WR) (P3.S-Il) (P3A-TO) (p3 .3-lNTl ) (P3.2-lNTO) (p3.I-TxD) (P3.0-RxD)

OB8H OBFH OBEH OBDH OBCH OBBH OBAH OB9H OB8H

(IP) - - - (PS) (pTl) (PXl) (PTO) (PXO)

OCOH OC7H OC6H OC5H OC4H OC3H OC2H OCIH OCOH

- - - - - - - - -

OC8H OCFH OCEH OCDH OCCH OCBH OCAH OC9H OC8H

- - - - - - - - -

ODOH OD7H OD6H OD5H OD4H OD3H OD2H ODIH ODOH

(PSW) (C) CAC) (FO) (RSI) (RSO) (Oy) (PSW.l) (P)

OD8H ODFH ODEH ODDH ODCH ODBH ODAH OD9H OD8H

- - - - - - - - -

OEOH OE7H OE6H OE5H OE4H OE3H OE2H OEIH OEOH

(ACC) (ACC.7) (ACC.6) (ACC.5) (ACC.4) (ACC.3) (ACC.2) (ACC.I) (ACC.O)

OE8H OEFH OEEH OEDH OECH OEBH OEAH OE9H OE8H

- - - - - - - - -

OFOH OF7H OF6H OF5H OF4H OF3H OF2H OFIH OFOR

(B) (B.7) (B.6) (B.S) (BA) (B.3) (B.2) (B. 1) (B.O)

OF8H OFFH OFEH OFDH OFCH OFBH OFAH OF9H OF8H

- - - - - - - - - Tabelul 1.7.

Forma simbolica C+-O

Descriere Indieatorul de transport C este resetat.

Forma simbolica bd+-O

Descriere Bitul destinatie bd este reset at (incarcat eu valoarea logica 0).

Forma simbolica C+-l

Descriere Indicatorul de transport C este setat.

Forma sim bolica bd+-l

- 1.28 -

Descriere Bitul destinatie bd este setat (incarcat eu valoarea logica 1).

Forma simbolica C~bs

Descriere ·Continutul bitului sursa bs este transferat in indieatorul de transport C.

Forma simbolica bd+C

Descriere Continutul indieatorului de transport C este transferat in bitul destinatie bd.

1.6.2. Instructiuni aritmetice ~i logice

Mieroeontrolerul AT89C51 prelucreaza date numeriee numai pe 8 biti {singura exceptie este increment area registrului DPTR de 16 biti). Operanzii pentru instructiunile aritmetiee ~i logice sunt registrele generale, locatiile de memorie de date interna, datele imediate, etc. Instructiunile aritmetiee si logice afecteaza indieatorii din PSW in conformitate eu rezultatul operatiei executate.

1.6.2.1. Instructiuni aritmetice

Forma simbolica

A~A+s

Descriere Continutul registrului aeumulator A este adunat eu al sursei s, iar rezultatul operatiei este incarcat in aeumulator. Sursa s poate fi un registru general Ri (i=O, 1, ... 7), 0 locatia de memorie de date interna eu adresa a8H, 0 locatia de memorie de date interna cu adresa precizata in registrul general Rj G=O sau j= 1) sau 0 data imediata de opt biti d8H.

Forma simbolica

A~A+s+C

Descriere Continutul registrului aeumulator A este adunat eu al sursei s ~i al indieatorului de transport C, iar rezultatul operatiei este incarcat in aeumulator.

Forma simbolica A~A-s-C

Descriere Din continutul registrului acumulator A este scazuta sursa s si indicatorul de transport C, iar rezultatul operatiei este incarcat in acumulator.

Forma simbolica d~d+ 1

Descriere Continutul destinatiei d este incrementat cu 0 unitate. Destinatia d poate fi acumulatorul A, un registru general Ri (i=O, 1, ... 7),0 locatie de memorie de date interna cu adresa a8H, 0 locatie de memorie de date interna eu adresa precizata in registrul general Rj G=O sau j= 1 ) sau registrul pentru adresarea memoriei ext erne DPTR. .

- 1.29 -

Forma simbolica

d--d-I

Descriere Continutul destinatiei d este deerementat eu 0 unitate. Destinatia d poate fi registrul aeumulator A, un registru general Ri (i=O, 1, ... 7),0 locatie de memorie de date interna eu adresa a8H, 0 locatie de memorie de date interna cu adresa precizata in registrul general Rj (j=O sau j= 1).

Forma simbolica BA~A·B (B~high A·B, As-low A-B)

Descriere Continutul registrului acumulator A este inmultit cu al registrului B; partea high a rezultatului (cei mai sernnifieativi opt biti) este incarcata in registrul B, iar partea Iowa rezultatului (eei mai putin semnificativi opt biti) este incarcata in registrul aeumulator A.

Forma simbolica

AB~A:B

(A+-[A:B] - cat; B+-{AB} - rest)

Descriere Continutul registrului acumulator A este impartit la registrul B; catul impartirii [A:B] este incarcat in registrul A, iar restul impartirii {A:B} este incarcat in registrul B.

Forma simbolica

BCD A

Descriere Instructiunea ajusteaza zeeimal continutul registrului acumulator A dupa executarea unei instructiuni.aritmetice de adunare pentru care operanzii sunt cifre zecimale (de la 0-9).

1.6.2.2. Instructiuni logice pe octet

Forma simbolica

Descriere Intre continutul registrului acumulator A ~i al sursei s se efectueaza operatia logica SAU bit cu bit, iar rezuItatul este incarcat in aeumulatorul A. Sursa s poate fi un registru general Ri (i=O, 1, ... 7), 0 locatie de memorie de date interna cu adresa a8H, 0 locatie de memorie de date interns eu adresa precizata in registrul general Rj (j=O sau j= 1) sau 0 data imediata de opt biti d8H.

Forma simbolica (a8H)~(a8H) U S'

Descriere Intrc continutul locatiei de memorie de date interna eu adresa a8H ~i sursa s' se efectueaza operatia logica SAU bit cu bit, iar rezultatul este incarcat in locatia de memorie de date interna cu adresa a8H. Sursa s' poate fi registrul aeumulator A sau 0 data imediata de opt biti d8H.

Forma simbolica A~A n s

Descriere Intre continutul registrului aeumulator A si al sursei s se efectueaza operatia logica SI bit eu bit, iar rezultatul este incarcat in aeumulatorul A.

Forma simbolica

(a8H)~(a8H) n S'

Descriere Intre continutul locatiei de memorie de date interna eu adresa a8H ~i sur sa s' se

- 1.30 -

efectueaza operatia logica SI bit eu bit, iar rezultatul este incarcat in locatia de memorie de date interna eu adresa a8H.

Forma simbolica

A+-A EB s

Descriere Intre continutul registrului aeumulator A ~i al sursei s se efectueaza operatia logica SAD EXCLUSIV bit eu bit, iar rezultatul este incarcat in aeumulatorul A.

Forma simbolics

(aSH)+-(aSH) EB s'

Descriere lntre continutul locatiei de memorie de date interna eu adresa a8H si sursa s' se efectueaza operatia logica SAD EXCLDSIV bit eu bit, iar rezultatul este incarcat in locatia de memorie de date interna eu adresa a8H.

Forma simbolica

A+-A

Descriere Continutul registrului aeumulator este complement at (neg at) bit cu bit.

1.6.2.3. Instructiuni logice pe bit

Forma simbolica

C+-C U bs

Descriere Se realizeaza operatia logica SAD intre continutul indieatorului de transport C ~i al bitului sursa bs, iar rezultatul se incarca in C.

Forma simbolica C+-C U bs

Descriere Se realizeaza operatia Iogica SAD intre continutul indieatorului de transport C si valoarea binara negata a bitului sursa bs, iar rezultatul se incarca in C.

Forma simbolica C+-C n bs

Descriere Se realizeaza operatia logica SI intre continutul indicatorului de transport C ~i al bitului sursa bs, iar rezultatul se incarca in C.

Forma simbolica C+-C n bs

Descriere Se realizeaza operatia logica ~I intre continutul indicatorului de transport C ~i valoarea binara.negata a bitului sursa bs, iar rezultatul se incarca in C.

Forma simbolica

C+-C

Descriere Continutul indicatorului de transport C este negat.

Forma simbolica

bd+- bd

Descriere Valoarea logica binara a bitului destinatie bd este negata.

- 1.31 -

1.6.2.4. Instructiuni de rotire

Forma simbolica

Descriere Continutul aeumulatorului este rot it eu un bit (un rang) spre stanga; bitul Ai _ I este transferat in Ai pentru i=1,2, ... 7 (Ai +-Ai-l), iar bitul A7 este transferat in Av (Ao+- A7)'

Forma simbolica

Descriere Continutul aeumulatorului este rotit eu un bit (un rang) spre dreapta; bitulA i + I este transferat in Ai pentru i=O, 1, ... 6 (Ai +-Ai+ I)' iar bitul Ao este transferatin A7 (A7+- Ao)·

Forma simbolica

Descriere Continutul acumulatorului este rotit cu 0 pozitie (un rang) spre stanga prin indieatorul de transport C; in indieatorul de transport C este transferat bitul A 7 (C+-A 7)' bitul A; _ I este transferat in bitul Ai pentru i=1,2, ... 7 (Ai +-Ai_l), iar C este transferat in bitul Ao (Ao+-C).

Forma simbolica

Descriere Continutul acumulatorului este rotit cu 0 pozitie (un rang) spre dreapta prin indicatorul de transport C; indieatorul de transport C este transferat in bitul A 7 (A 7+-C), bitul Ai + 1 este transferat in bitul Ai pentru i=O, 1, ... 6 (Ai +-Ai+ 1), iar bitul Ao este transferat in C (C+-Ao).

1.6.3. Instructiuni de ramificare

Aceste instructiuni sunt deosebit de importante deoarece permit obtinerea programelor care realizeaza 0 aplicatie concreta. Instructiunile de ramifieare constau din teste si salturi, iar varietatea ~i eomplexitatea acestora depind de tipul mieroproeesorului.

1.6.3.1. Instructiuni de salt neconditionat

Forma simboliea

PC+-a16H

Descriere Numaratorul de program PC este incarcat eu adresa absoluta a16H (de 16 biti); dupa exeeutarea aeestei instructiuni mieroproeesorul executa instructiunile aflate la adresa a 16H.

Forma simbolica

PC+-A+DPTR

Descriere Numaratorul de program PC este incarcat eu adresa de 16 biti obtinuta din sumarea continutului registrului aeumulator A si al registrului DPTR; se va realiza un salt neconditionat.

- 1.32 -

Forma simbolicii

PC~PC+2

(PCIS _ 11 nu se modifica)

Se utilizeaza de regula forma simbolica prescurtata: PC ~a 11 H.

Descriere Numaratorul de program este increment at cu doua unitati (deoarece instructiunea are doi octeti), apoi se incarca In cei mai putin semnificativi 11 biti ai acestuia adresa imediata a l l H, iar cei mai semnificativi 5 biti ai numaratorului de program nu se modifica; dupa executarea acestei instructiuni se vor executa instructiunile programului aflate la adresa de salt. Se executa un salt neconditionat in interiorul unei zone de memorie program cu lungimea de 2 Kocteti (pagina).

Forma simbolica

PC~PC+2+drH

Descriere Adresarea relativa determina executia instructiunilor aflate inaintea instructiunii de salt sau dupa instructiunea de salt ~i are avantajul codurilor relocabile de program utilizator. Adresa de salt este indicata in instructiune printr-un deplasament relativ care nu depinde de adresa absoluta la care apar instructiunile in memorie. Cand se efectueaza calculul adresei de salt, numaratorul de program coniine adresa instructiunii urmatoare (a fost incrementat cu doua unitati deoarece instructiunea are doi octeti) la care se adauga deplasamentul relativ.

Se poate executa un salt la 0 instructiune de dupa instructiunea de salt relativ daca numarul de octeti dintre cele doua instructiuni este mai mic sau eel mult egal cu 7FH octeti, exclusiv octetii celor dona instructiuni; numarul de octeti dintre cele doua instructiuni reprezinta in acest caz deplasamentul relativ drH. Se poate executa un salt la 0 instructiune aflata inaintea instructiunii de salt relativ daca numarul de octeti dintre cele doua instructiuni este mai mic sau eel mult egal eu 80H octeti, inclusiv octetii celor doua instructiuni. In acest caz, deplasamentul relativ dr se calculeaza scazand din lOOH numarul de octeti dintre cele doua instructiuni.

1.6.3.2. Instructiuni de salt conditionat relative

Forma simbolica

I~

PO- PC+2+ch- PC+-PC+2

(Salt) (Com)

Descriere Se testeaza daca conditia logica (CI) de salt este adevarata (A) sau falsa si se

incrementeaza numaratorul de program cu doua unitati deoarece instructiunea are doi octeti. Daca conditia logica de salt este adevarata, atunci la continutul.numaratorului de program se adauga

- 1.33 -

valoarea deplasamentului relativ dr (se realizeaza saltul) ~i se incepe executarea segmentului de program de la aceasta adresa calculata; daca conditia de salt este falsa, atunci se continua programul cu executarea instructiunilor urmatoare.

Conditia logica de salt (CI) are sernnificatiile: C (carry) - se realizeaza saltul daca indicatorul de transport C este 1 logic; NC (not carry) - se realizeaza saltul daca indicatorul de transport C este 0 logic; Z (zero) - se realizeaza saltul daca continutul registrului acumulator A este OOH; NZ (not zero) - se realizeaza saltul daca continutul registrului acumulator A este diferit de OOH.

Forma simbolica

D~

r I

PC+-ro+3+dr ~PC+3

(Salt) (Cant)

Descriere Se testeaza daca conditia logica pe bit (Clb) de salt este adevarata (A) sau falsa si se

incrementeaza numaratorul de program cu trei unitati deoarece instructiunea are trei octeti. Daca conditia logica de salt pe bit este adevarata, atunci la continutul numaratorului de program se adauga valoarea deplasamentului relativ dr ~i se incepe executarea segmentului de program de la aceasta adresa calculata, iar daca conditia logica pe bit este falsa atunci se continua programul cu instructiunea urmatoare.

Conditia logica de salt pe bit (Clb) consta in a testa bitul oricarei locatii de memorie de date interna din zona 20H-2FH sau registrele din SFR cu adresele divizibile cu opt (80H, 88H, 90H, ... ).

Semnificatiile conditiilor logice pe bit sunt: B (bit) - se realizeaza saltul daca bitul testat este 1 logic; NB (not bit) - se realizeaza saltul daca bitul testat este 0 logic; BC (bit clear) - se realizeaza saltul daca bitul testat este 1 logic ~i totodata acesta este resetat.

1.6.3.3. Instructiuni de decrementare ~i salt conditionat relativ

Forma simbolica Ri..-Ri-l

NUMnA

I I

PC-PC+2+dr PC-PC+2

(Salt) (Coot)

Descriere Continutul registrului general Ri (i=O, 1, ... 7) este decrement at cu 0 unitate, iar

numaratorul de program este increment at cu doua unitati (deoarece instructiunea are doi octeti). Daca continutul registrului general Ri este diferit de zero, atunci la continutul numaratorului de program se adauga valoarea deplasamentului relativ drH ~i se executa saltul, iar daca continutul

- 1.34 -

registrnlui general Ri este zero se continua executarea instructiunii urmatoare (nu se executa salt).

Forma simbolica (a8H)+-(a8B}-1

~~DA,

PC+-PC+3+dr PC+- PC+3

(Salt) (Cont)

Descriere Continutul locatiei de memorie de date interns cu adresa a8H este decrementat cu 0 unitate, iar numaratorul de program este incrementat cu trei unitati ( instructiunea are trei octeti). Daca continutul locatiei de memorie interna de date cu adresa a8H este diferit de zero, atunci la continutul numaratorului de program se adauga valoarea deplasamentului dr ~i se executa saltul, iar in caz contrar se continua executarea instructiunii urmatoare.

1.6.3.4. Instructiuni de comparare ~i salt conditionat relativ

Forma simbolica A-a

~A

I j

PC+-PC+3+dr PC+-PC+3

(Salt) (Coat)

Descriere Se compara continutul acumulatorului A cu sursa s; operatia de comparare este 0 operatic de scad ere al carei rezultat se pierde, dar care afecteaza indicatornl de transport C din registrul PSW. Totodata se incrementeaza cu trei unitati continutul numaratorului de program (deoarece instructiunea are trei octeti). Daca continutul acumulatorului A este diferit de sursa s, atunci la continutul numaratorului de program se adauga valoarea deplasamentului relativ dr si se executa saltul, iar daca continutul acumulatorului A este egal cu sursa s se continua executarea instructiunii urmatoare din program (nu se executa saltul). Pentru aceste instructiuni sursa s este o data imediata d8H (de 8 biti) sau 0 locatie de memorie de date interna cu adresa a8H (de 8 biti).

Forma simbolica a-d8H

INU~DA,

PC+-PC~ PC+-PC+3

(Salt) (Coat)

Descriere Se com para continutul sursei s cu data imediata d8H; indicatorul de transport C din PSW este afectat in conforrnitate cu rezultatul scaderii care se pierde ~i se incrementeaza cu trei unitati continutul numaratorului de program. Daca continutul sursei s este diferit de data imediata d8H, atunci la continutul numaratorului de program se adauga valoarea deplasamentului dr si se executa saltul, iar daca continutul sursei s este egal cu data imediata d8H se continua executarea

- 1.35 -

instructiunii urmatoare din program (nu se executa saltul). Pentru aceste instructiuni sursa s este un registru general Ri (i=O, 1, ... 7) sau 0 locatie de memorie de date interna cu adresa precizata in registrul general Rj 0=0 sau j= 1 ).

1.6.3.5. Instructiuni de apel subrutina ~i de revenire din subrutina

Forma simbolica

PC+-PC+3 SP+-SP+l (SP)+-PC7 _ 0 SP+-SP+l (SP)+-PC15 _ 8 PC+-a16H

Forma simbolica prescurtata este: (SP)+-PC; PC+-aI6H, dar de cele mai muIte ori se

utilizeaza mnemonicul instructiunii,

Descriere Numaratorul de program este increment at cu trei unitati (deoarece instructiunea are trei octeti), apoi continutul acestuia este salvat in varful stivei; cei mai putin semnificativi opt biti ai numaratorului de program (partea low) sunt salvati in stiva la adresa SP+ 1, iar cei mai semnificativi opt biti ai acestuia (partea high) sunt salvati in stiva la adresa SP+2. Numaratorul de program este incarcat cu adresa de inceput a subrutinei a 16H, iar continutul indicatorului de stiva este incrementat cu doua unitati.

Forma simbolica

PC+-PC+2 SP+-SP+l (SP)+- PC7 _ 0 SP+-SP+l (SP)+-PC15 -8 PC10 _ 0 +-allH

(PCl5 _ 11 - nu se modifica)

Forma simbolica prescurtata este: (SP)+-PC; PC+-allH, dar de cele mai multe ori se utilizeaza mnemonicul instructiunii.

Descriere Numaratorul de program este incrementat cu doua unitati (deoarece instructiunea are doi octeti), apoi continutul acestuia estesalvat in stiva ca la instructiunea de mai sus. In cei mai putin semnificativi 11 biti ai PC este incarcata adresa a 11 H (de 11 biti), iar cei mai semnificativi 5 biti ai PC nu se modifica. Continutul indicatorului de stiva este incrementat cu doua unitati. Cu

" ,

aceasta instructiune se apeleaza 0 subrutina in interiorul unei zone de memorie program (pagina) de 2Kocteti.

- 1.36 -

Forma simbolica

pelS _ 8+-(SP) SP+-SP-l PC7 _ 0 +-(SP) SP+-SP-l

Se utilizeaza forma simbolica prescurtata: PC+-(SP) sau mnemonicul instructiunii.

Descriere Dupa exeeutarea unei subrutine, adresa de revenire in programul de baza se afla in varfiil stivei. Aceasta adresa este incarcata in numaratorul de program astfel: in partea high a PC este incarcat din stiva continutul Iocatiei de memorie cu adresa precizata de SP, iar in partea low a PC este incarcat din stiva continutul locatiei de memorie cu adresa precizata de SP-I. Indicatorul de stiva este decrementat cu doua unitati. In continuare, se efectueaza saltul in programul de baza (intrerupt) ~i se executa instructiunile respective.

Instructiunea de revenire din rutina de tratare a intreruperilor este 0 instructiune obisnuita de revenire din subrutina care in plus reactualizeaza starea sistemului de intreruperi. In urma acceptarii unei cereri de intrerupere se salveaza ill stiva PC; alte registre ale programului intrerupt sunt salvate cu primele instructiuni din subrutina de tratare a cererii de intrerupere, iar inainte de revenirea din subrutina cu ultimele instructiuni sunt restaurate registrele programului intrerupt,

1.6.3.6. Alte instruetiuni

Forma simbolica

PC+-PC+l

Descriere Instructiunea nu realizeaza nici 0 operatic. Se incrementeaza numaratorul de program cu 0 unitate ~i se trece la executarea instructiunii urmatoare (utilizata pentru temporizari).

1. 7. Porturile paralele de intrare/iesire

Transferul datelor intre microcontrolerul AT89C51 ~i mediul extern se realizeaza prin intermediul porturilor paralele de intrare sau iesire. Mediul extern este constituit din multimea interfetelor din aplicatiile care nu Iucreaza direct eu microprocesorul din microcontroler.

In cazul unui transfer numai pentru date, microprocesorul executa 0 scriere in portul de iesire in cazul transmiterii unei date in mediul extern (portul de iesire consta dintr-un registru cu opt circuite baseulante bistabile; datele raman memo rate in portul de iesire pana la inscrierea urmatoarei valori) sau 0 citire din portuI de intrare in cazul receptionarii unei date din mediul extern (portul de intrare consta din circuite buffer eu trei stan).

- l.37 -

Microcontrolerul AT89C51 are patru porturi paralele de cate opt biti fiecare pentru date . care pot fiutilizate ca intrari sau iesiri la nivel de octet (port) sau de bit (linie). Deoarece numarul de pini In care este incapsulat rnicrocontrolerul este lirnitat (40 pini), atunci a fost necesar ca porturile sa fie prevazute ~i cu functii auxiliare. In urma initializarii microcontrolerului, cele opt bistabile ale fiecarui port sunt incarcate cu valoarea 1 logic, iar porturile pot fi utilizate ca intrari; In acest mod se protejeaza liniile porturilor. Daca un bistabil are iesirea Q In 0 logic ~i linia corespunzatoare este de intrare, atunci sernnalul de intrare este conectat la masa, iar acest conflict duce inevitabilla defectarea circuitului din mediul extern sau a structurii hard din portul respectiv.

1.7.1. Structura generala a unui port paralel

Un port are structura generals redata ill fig. 1.17 si contine pentru fiecare linie de iesire sau intrare cate un circuit basculant bistabil de tip D (eBB), doua buff ere cu trei stan (BL' Bp), un etaj de amplifieare de iesire (EA) eu 0 structura usor diferita de la un port la altul datorita functiilor auxiliare asociate si un buffer al portului (B).

RDL

EA

B

Fig. 1.17.

In cireuitul basculant bistabil de tip D se inscrie data furnizata de pe magistrala interna (M!) sub comanda sernnalului de seriere WRL. Data inscrisa este memorata in bistabilul de tip D pana la urmatoarea operatie de seriere si este furnizata la pinul eircuitului prin intermediul etajului de amplificare (EA) si al bufferului (B). Iesirea Q a bistabilului este conectata printr-un buffer cu trei stan ~ la magistrala interna; prin aetivarea semnalului de comanda de citire RDL este posibil sa se citeasca continutul bistabilului (latehului) respeetiv.

Un alt buffer eu trei stari Bp realizeaza conectarea pinului de la port la magistrala interna; prin activarea semnalului de comanda de citire RDp se citeste data de la intrarea pinului.

- 1.38 -

1.7.1.1. Structura portului PI

. In fig. 1. 18 este redata structura unei linii din cele 8 ale portului PI care include ~i detaliile etajului de iesire; aceasta structura sta de asemenea, la baza celorlalte porturi, dar cu unele modificari.

+5V

MI ---1-----1

RDp

Fig. 1.18.

Pentru microcontrolerul AT89CS1 portul PI esteutilizat numai ca port de iesire sau de irrtrare la nivel de octet sau de bit; unele linii ale portului pot fi utilizate ca intrari, iar celelalte ca iesiri dupa cum se citesc date de pe liniile de intrare respective sau sunt serise date pe liniile de iesire corespunzatoare.

Etajul de iesire al portului este alcatuit din tranzistorul N 1 si din alte trei tranzistoare nefigurate care sunt echivalente cu rezistenta R conectata la +SV.