Documente Academic

Documente Profesional

Documente Cultură

Rr310403 Digital Ic Applications

Încărcat de

sivabharathamurthyDescriere originală:

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Rr310403 Digital Ic Applications

Încărcat de

sivabharathamurthyDrepturi de autor:

Formate disponibile

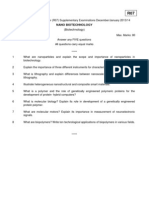

Code No: RR310403 RR

III B.Tech I Semester(RR) Supplementary Examinations, November 2010

DIGITAL IC APPLICATIONS

(Electronics & Communication Engineering)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

?????

1. (a) Explain how to estimate sinking current for low output and sourcing current for high output of

CMOS gate?

(b) Analyze the fall time of CMOS inverter output with RL = 1K?, VL = 2.5V and CL = 100PF.

Assume VL as stable state voltage. [8+8]

2. (a) Draw the circuit diagram of basic CMS gate and explain the operation?

(b) Discuss the steps in VHDL design flow? [8+8]

3. (a) Design the logic circuit and write a data-flow style VHDL program for the following function?

F (W) = ΠA,B,C,D (1,4,5,7,9,13,15)

(b) Write data-flow style VHDL program for full adder and use this entity to develop a 2-bit adder?

[8+8]

4. (a) It is necessary to identify the position of mechanical disk, when rotates with a step of 450 . Give

the necessary encoding mechanism and draw the logic circuit?

(b) Using two 74×138 decoders design a 4 to 16 decoder? [8+8]

5. (a) Show the logic diagram of 74×283 binary adder? Explain the principle of generating sum and

carry at every stage using the logic diagram? [4+4]

(b) Design a 24-bit group ripple adder using 74×283 Ics? [8]

6. (a) Draw the logic diagram of 74×74 IC and explain the operation? Develop the VHDL model for

this IC?

(b) With the help of logic diagram discuss PAL16R8? [8+8]

7. (a) Design an 8-bit parallel-in and serial-out shift register? Explain the operation of the above shift

register with the help of timing waveforms?

(b) Draw the logic diagram of 74×194 and explain the operation? [8+8]

8. (a) Discuss how PROM, EPROM and EEPROM technologies differ from each other?

(b) With the help of timing waveforms, explain read and write operations of static SRAM? [8+8]

?????

S-ar putea să vă placă și

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5795)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (895)

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (345)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- Repair Manual For Claas Mega 202 218 Combine HarvesterDocument382 paginiRepair Manual For Claas Mega 202 218 Combine Harvesterramunas100% (7)

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (121)

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (74)

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- Fire Alarm Sys Nec 760Document10 paginiFire Alarm Sys Nec 760nadeem Uddin100% (1)

- DIN EN 179 I 1125 PDFDocument3 paginiDIN EN 179 I 1125 PDFDushan RomicÎncă nu există evaluări

- Barossa ATV - Quaterback 250 E - Spare Parts List PDFDocument45 paginiBarossa ATV - Quaterback 250 E - Spare Parts List PDFgabysurfÎncă nu există evaluări

- Control Systems (CS) Notes As Per JntuaDocument203 paginiControl Systems (CS) Notes As Per Jntuasivabharathamurthy100% (3)

- R7311506 Operating SystemsDocument1 paginăR7311506 Operating SystemssivabharathamurthyÎncă nu există evaluări

- 07A4EC01 Environmental StudiesDocument1 pagină07A4EC01 Environmental StudiessivabharathamurthyÎncă nu există evaluări

- R7410506 Mobile ComputingDocument1 paginăR7410506 Mobile ComputingsivabharathamurthyÎncă nu există evaluări

- SSC Social Textbook (AP)Document100 paginiSSC Social Textbook (AP)sivabharathamurthyÎncă nu există evaluări

- R7311205 Distributed DatabasesDocument1 paginăR7311205 Distributed DatabasessivabharathamurthyÎncă nu există evaluări

- R7312301 Transport Phenomena in BioprocessesDocument1 paginăR7312301 Transport Phenomena in BioprocessessivabharathamurthyÎncă nu există evaluări

- R5410201 Neural Networks & Fuzzy LogicDocument1 paginăR5410201 Neural Networks & Fuzzy LogicsivabharathamurthyÎncă nu există evaluări

- 9A05707 Software Project ManagementDocument4 pagini9A05707 Software Project ManagementsivabharathamurthyÎncă nu există evaluări

- 9A13701 Robotics and AutomationDocument4 pagini9A13701 Robotics and AutomationsivabharathamurthyÎncă nu există evaluări

- 9A14503 Principles of Machine DesignDocument8 pagini9A14503 Principles of Machine DesignsivabharathamurthyÎncă nu există evaluări

- 9A23501 Heat Transfer in BioprocessesDocument4 pagini9A23501 Heat Transfer in BioprocessessivabharathamurthyÎncă nu există evaluări

- Code: R7311306: (Electronics & Control Engineering)Document1 paginăCode: R7311306: (Electronics & Control Engineering)sivabharathamurthyÎncă nu există evaluări

- R7311006 Process Control InstrumentationDocument1 paginăR7311006 Process Control InstrumentationsivabharathamurthyÎncă nu există evaluări

- R5310204 Power ElectronicsDocument1 paginăR5310204 Power ElectronicssivabharathamurthyÎncă nu există evaluări

- R7310106 Engineering GeologyDocument1 paginăR7310106 Engineering GeologysivabharathamurthyÎncă nu există evaluări

- R7310206 Linear Systems AnalysisDocument1 paginăR7310206 Linear Systems AnalysissivabharathamurthyÎncă nu există evaluări

- R7310406 Digital CommunicationsDocument1 paginăR7310406 Digital CommunicationssivabharathamurthyÎncă nu există evaluări

- 9A10505 Principles of CommunicationsDocument4 pagini9A10505 Principles of CommunicationssivabharathamurthyÎncă nu există evaluări

- 9A15502 Digital System DesignDocument4 pagini9A15502 Digital System Designsivabharathamurthy100% (1)

- 9A21506 Mechanisms & Mechanical DesignDocument8 pagini9A21506 Mechanisms & Mechanical DesignsivabharathamurthyÎncă nu există evaluări

- 9A04504 Digital IC ApplicationsDocument4 pagini9A04504 Digital IC ApplicationssivabharathamurthyÎncă nu există evaluări

- R7412310 Nano BiotechnologyDocument1 paginăR7412310 Nano BiotechnologysivabharathamurthyÎncă nu există evaluări

- 9A03505 Heat TransferDocument4 pagini9A03505 Heat TransfersivabharathamurthyÎncă nu există evaluări

- R7411510 Neural NetworksDocument1 paginăR7411510 Neural NetworkssivabharathamurthyÎncă nu există evaluări

- R7412311 Metabolic EngineeringDocument1 paginăR7412311 Metabolic EngineeringsivabharathamurthyÎncă nu există evaluări

- R7411306 Robotics & AutomationDocument1 paginăR7411306 Robotics & AutomationsivabharathamurthyÎncă nu există evaluări

- 9A02505 Electrical Machines-IIIDocument4 pagini9A02505 Electrical Machines-IIIsivabharathamurthyÎncă nu există evaluări

- R7411509 Distributed DatabasesDocument1 paginăR7411509 Distributed DatabasessivabharathamurthyÎncă nu există evaluări

- R7411307 Instrumentation & Control in Manufacturing SystemsDocument1 paginăR7411307 Instrumentation & Control in Manufacturing SystemssivabharathamurthyÎncă nu există evaluări

- Sewa bill-AED 559Document1 paginăSewa bill-AED 559muhdazarÎncă nu există evaluări

- Commercial Sales Associate FY - 19: Kavyaa KDocument12 paginiCommercial Sales Associate FY - 19: Kavyaa KKavya PradeepÎncă nu există evaluări

- SP25Y English PDFDocument2 paginiSP25Y English PDFGarcia CruzÎncă nu există evaluări

- Rosemount 2120 Vibrating Fork Liquid Level SwitchDocument16 paginiRosemount 2120 Vibrating Fork Liquid Level SwitchTariqMalikÎncă nu există evaluări

- Flyover Construction ThesisDocument4 paginiFlyover Construction ThesisLeyon Delos Santos60% (5)

- J Proc CTRL Vol 19 2009 Q Wang K Astrom - Guaranteed Dominant Pole PlacementDocument4 paginiJ Proc CTRL Vol 19 2009 Q Wang K Astrom - Guaranteed Dominant Pole PlacementmtichyscribdÎncă nu există evaluări

- CV Kevin Ikhwan Muhammad Pt. Hasakona BinaciptaDocument6 paginiCV Kevin Ikhwan Muhammad Pt. Hasakona BinaciptaKevin MuhammadÎncă nu există evaluări

- Neurophone Ebook EnglDocument19 paginiNeurophone Ebook EnglViolin_teacher100% (3)

- Learn PowerShell Core 6.0Document800 paginiLearn PowerShell Core 6.0Felippe Coelho100% (2)

- I Know Many BeginnersDocument5 paginiI Know Many BeginnersOsmar Tavares JuÎncă nu există evaluări

- Why JSON in PostgreSQL Is AwesomeDocument7 paginiWhy JSON in PostgreSQL Is AwesomeTeo TokisÎncă nu există evaluări

- Sony DCR Sr47Document101 paginiSony DCR Sr47Mitesh ChauhanÎncă nu există evaluări

- SIL99-2C: Service Information LetterDocument22 paginiSIL99-2C: Service Information LettersandyÎncă nu există evaluări

- Compresores TecumsehDocument139 paginiCompresores TecumsehRicardo EstrellaÎncă nu există evaluări

- Six Stroke EngineDocument19 paginiSix Stroke EngineSai deerajÎncă nu există evaluări

- AASHTO - LRFD (Design Example For Steel Girder Superstructure Bridge - 2003)Document698 paginiAASHTO - LRFD (Design Example For Steel Girder Superstructure Bridge - 2003)Ridwan Kris50% (2)

- PanasonicBatteries NI-MH HandbookDocument25 paginiPanasonicBatteries NI-MH HandbooktlusinÎncă nu există evaluări

- Y y Y Y Y: Design of Machinery 86Document1 paginăY y Y Y Y: Design of Machinery 86Star GlacierÎncă nu există evaluări

- Pumps and Filters: 345D, 349D, and 349D Excavator Hydraulic SystemDocument2 paginiPumps and Filters: 345D, 349D, and 349D Excavator Hydraulic SystemTeknik MakinaÎncă nu există evaluări

- Pete443 Chapter3 PDFDocument38 paginiPete443 Chapter3 PDFQaiser HafeezÎncă nu există evaluări

- CT ManualDocument543 paginiCT ManualwindroidÎncă nu există evaluări

- POCLP010101 Wood PelletsDocument1 paginăPOCLP010101 Wood PelletsPratiwi CocoÎncă nu există evaluări

- Toyota's JIT Revolution 1Document6 paginiToyota's JIT Revolution 1Shambu PatilÎncă nu există evaluări

- Hydraulic & Pneumatic EquipmentDocument183 paginiHydraulic & Pneumatic EquipmentArintoÎncă nu există evaluări

- Recycled Concrete Roadbase Swis 4003Document45 paginiRecycled Concrete Roadbase Swis 4003Mircea BobarÎncă nu există evaluări