Documente Academic

Documente Profesional

Documente Cultură

Cmos Device Structure: The Pull-Up Network The Pull-Down Network V A B C D Inputs Yfa, B, C, D

Încărcat de

pallab869343Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Cmos Device Structure: The Pull-Up Network The Pull-Down Network V A B C D Inputs Yfa, B, C, D

Încărcat de

pallab869343Drepturi de autor:

Formate disponibile

11/14/2004 CMOS Device Structure.

doc 1/4

CMOS Device Structure

For every CMOS device, there are essentially two separate

circuits:

1) The Pull-Up Network

2) The Pull-Down Network

The basic CMOS structure is:

VDD

A

B

C PUN

D

Inputs Y = f (A, B ,C ,D )

A

B

C PDN Output

D

A CMOS logic gate must be in one of two states!

Jim Stiles The Univ. of Kansas Dept. of EECS

11/14/2004 CMOS Device Structure.doc 2/4

State 1: PUN is open and PDN is conducting.

VDD

PUN

In this state,

the output is

Y =0 LOW (i.e., Y =0).

PDN

State 2: PUN is conducting and PDN is open.

VDD

PUN

In this state,

Y =0 the output is

HIGH (i.e.,Y =1).

PDN

Jim Stiles The Univ. of Kansas Dept. of EECS

11/14/2004 CMOS Device Structure.doc 3/4

Thus, the PUN and the PDN essentially act as switches,

connecting the output to either VDD or to ground:

VDD VDD

OR

Y =0 Y =VDD

* Note that the key to proper operation is that one switch

must be closed, while the other must be open.

* Both switches closed or both switches open would cause an

ambiguous digital output!

* To prevent this from occurring, the PDN and PUN must be

complementary circuits.

Jim Stiles The Univ. of Kansas Dept. of EECS

11/14/2004 CMOS Device Structure.doc 4/4

For example, consider the CMOS inverter:

VDD

PUN

A Y =A

PDN

For more complex digital CMOS gates (e.g., a 4-input OR

gate), we find:

1) The PUN will consist of multiple inputs, therefore

requires a circuit with multiple PMOS transistors.

2) The PDN will consist of multiple inputs, therefore

requires a circuit with multiple NMOS transistors.

Jim Stiles The Univ. of Kansas Dept. of EECS

S-ar putea să vă placă și

- Chapter6-1 Part I 12-10-2003Document81 paginiChapter6-1 Part I 12-10-2003Blue StarÎncă nu există evaluări

- Designing Static CMOS Logic Circuits: © Forrest Brewer and © Digital Integrated Circuits Combinational CircuitsDocument65 paginiDesigning Static CMOS Logic Circuits: © Forrest Brewer and © Digital Integrated Circuits Combinational CircuitsKulanthaivelu RamaswamyÎncă nu există evaluări

- Lecture 6Document65 paginiLecture 6mituancaandreeaÎncă nu există evaluări

- Designing Combinational Logic CircuitsDocument113 paginiDesigning Combinational Logic Circuitssteves0118Încă nu există evaluări

- Circuit Layout EulerDocument72 paginiCircuit Layout Eulerជើងកាង ភូមិÎncă nu există evaluări

- Digital Integrated Circuits: A Design PerspectiveDocument113 paginiDigital Integrated Circuits: A Design PerspectiveSulochana VermaÎncă nu există evaluări

- Lecture 4Document39 paginiLecture 4arsalan.jawedÎncă nu există evaluări

- 2017 Ch3-2-Circuit Layout Rev1 EulerDocument72 pagini2017 Ch3-2-Circuit Layout Rev1 EulerNhân LêÎncă nu există evaluări

- Digital Circuit Design: An Overview Digital IC Technologies and Logic Circuit FamiliesDocument13 paginiDigital Circuit Design: An Overview Digital IC Technologies and Logic Circuit FamiliesReneesh C ZachariaÎncă nu există evaluări

- Coe 236 Digital Electronics: Dr. Mohannad H. Al-Ali Department of Computer Engineering University of Basrah Spring 2020Document14 paginiCoe 236 Digital Electronics: Dr. Mohannad H. Al-Ali Department of Computer Engineering University of Basrah Spring 2020لطيف احمد حسنÎncă nu există evaluări

- VLSI Design-R19-Unit-4-ToTAL-CMOS Combinational & Sequential Logic Circuit DesignDocument91 paginiVLSI Design-R19-Unit-4-ToTAL-CMOS Combinational & Sequential Logic Circuit Designvineethkumar3223Încă nu există evaluări

- Lec 10 Combinational Logic CircuitsDocument59 paginiLec 10 Combinational Logic CircuitsNaim UddinÎncă nu există evaluări

- Dynamic CMOS DesignDocument30 paginiDynamic CMOS DesignAllwyn Anand SÎncă nu există evaluări

- Week 11-12-13 (CMOS) Page 85-112 (MFRDT)Document77 paginiWeek 11-12-13 (CMOS) Page 85-112 (MFRDT)Mohamed Abdirashid AhmedÎncă nu există evaluări

- Mod 03 Lec 12Document16 paginiMod 03 Lec 12Srikanth PasumarthyÎncă nu există evaluări

- B LogicDocument64 paginiB Logicwqy15902896758Încă nu există evaluări

- Tional Logic (Or Non-Regenerative) Circuits That Have The Property That at Any Point in TimeDocument7 paginiTional Logic (Or Non-Regenerative) Circuits That Have The Property That at Any Point in Timeميسر محسنÎncă nu există evaluări

- Digital Integrated Circuits EE 431: Fall 2015 Week 8Document28 paginiDigital Integrated Circuits EE 431: Fall 2015 Week 8Mohamed shabanaÎncă nu există evaluări

- Chap16 2 CMOS Inverter ModifiedDocument14 paginiChap16 2 CMOS Inverter ModifiedSai Kiran OrugantiÎncă nu există evaluări

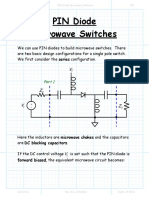

- PIN Diode Microwave SwitchesDocument5 paginiPIN Diode Microwave Switchesabdo-dzÎncă nu există evaluări

- CMOS Logic Circuit DesignDocument47 paginiCMOS Logic Circuit DesignKohilan VenugopalÎncă nu există evaluări

- CMOS Technology: Combinational Device Wish ListDocument6 paginiCMOS Technology: Combinational Device Wish Listkunalsekhri123Încă nu există evaluări

- Performance analysis of 2:1 multiplexer using CMOS logic families at 180 nmDocument24 paginiPerformance analysis of 2:1 multiplexer using CMOS logic families at 180 nmDilip Kumar100% (1)

- Unit-Ii Cmos CircuitsDocument34 paginiUnit-Ii Cmos CircuitsgnitsiceÎncă nu există evaluări

- Combinational Logic Part 1 KavindraDocument30 paginiCombinational Logic Part 1 KavindraSAKSHI PALIWALÎncă nu există evaluări

- Subject Code:18EC2019: Digital Integrated Circuit DesignDocument29 paginiSubject Code:18EC2019: Digital Integrated Circuit Designshiny johnÎncă nu există evaluări

- Dynamic Analysis of Cmos Inverter and Cmos Nand&Nor: Prepared By: Saloni DesaiDocument9 paginiDynamic Analysis of Cmos Inverter and Cmos Nand&Nor: Prepared By: Saloni DesaiAryanSharmaÎncă nu există evaluări

- Tle 7263eDocument62 paginiTle 7263eCarlos PenagosÎncă nu există evaluări

- 28-Pseudo Nmos, DCVSL and Dynamic Logic-12!09!2020 (12-Sep-2020) Material I 12-Sep-2020 CMOS Combinational Circuit DesignDocument22 pagini28-Pseudo Nmos, DCVSL and Dynamic Logic-12!09!2020 (12-Sep-2020) Material I 12-Sep-2020 CMOS Combinational Circuit DesignParth VijayÎncă nu există evaluări

- A Novel High Speed Differential Ultra Low-Voltage CMOS Flip-Flop For High Speed ApplicationsDocument6 paginiA Novel High Speed Differential Ultra Low-Voltage CMOS Flip-Flop For High Speed ApplicationsIgorXavierÎncă nu există evaluări

- Designing Combinational Logic CircuitsDocument60 paginiDesigning Combinational Logic CircuitsFaiz MohdÎncă nu există evaluări

- Advance CMOS LogicDocument31 paginiAdvance CMOS LogicRaja VidyaÎncă nu există evaluări

- Infineon TLE6209R DS v03 02 enDocument30 paginiInfineon TLE6209R DS v03 02 enRoger SegoÎncă nu există evaluări

- Check communication error between front sub-OPB and DOC-200Document1 paginăCheck communication error between front sub-OPB and DOC-200Daniel GatdulaÎncă nu există evaluări

- Introduction to CMOS technology and logic gate fundamentalsDocument39 paginiIntroduction to CMOS technology and logic gate fundamentalsvenkateshÎncă nu există evaluări

- Designing Combinational Logic Gates in CMOSDocument125 paginiDesigning Combinational Logic Gates in CMOSArqam Ali KhanÎncă nu există evaluări

- ECE 6130/4130: Advance VLSI Systems: Combinational Logic Styles: Part-II Dynamic Logic Other StylesDocument26 paginiECE 6130/4130: Advance VLSI Systems: Combinational Logic Styles: Part-II Dynamic Logic Other StylesRupesh ParabÎncă nu există evaluări

- 7 A H-Bridge For DC-Motor Applications TLE 7209-2R: Final DatasheetDocument32 pagini7 A H-Bridge For DC-Motor Applications TLE 7209-2R: Final DatasheetMecaSoftwareÎncă nu există evaluări

- Vlsi Lab 1Document11 paginiVlsi Lab 1Shawon karmokar JotyÎncă nu există evaluări

- Lecture 18Document33 paginiLecture 18Gameplay OrIgInAlIÎncă nu există evaluări

- 7 A H-Bridge For DC-Motor Applications TLE 6209 R: 1 1.1 FeaturesDocument29 pagini7 A H-Bridge For DC-Motor Applications TLE 6209 R: 1 1.1 Featureswtn2013Încă nu există evaluări

- Contents:: CMOS Inverter Cmos Nand Gate Cmos Nor GateDocument13 paginiContents:: CMOS Inverter Cmos Nand Gate Cmos Nor GateTilottama DeoreÎncă nu există evaluări

- Lecture 5Document36 paginiLecture 5arsalan.jawedÎncă nu există evaluări

- Eetop - CN - Chapter 5 Differential Pair AmpDocument39 paginiEetop - CN - Chapter 5 Differential Pair Ampshuhaoyi5Încă nu există evaluări

- Solving Door Motor Overheating Issues (TCD 194Document17 paginiSolving Door Motor Overheating Issues (TCD 194Fabian VirgiliÎncă nu există evaluări

- AP3041 Oscilador TV Haier 50yca PDFDocument14 paginiAP3041 Oscilador TV Haier 50yca PDFmaroÎncă nu există evaluări

- AP3041 Ic Driver Placa Simply Syled37i Que Se QuemaDocument14 paginiAP3041 Ic Driver Placa Simply Syled37i Que Se QuemaAndres Alegria0% (1)

- CMOS Inverter and Multiplexer Circuit DesignDocument20 paginiCMOS Inverter and Multiplexer Circuit DesigncngindiÎncă nu există evaluări

- EE 4313 Homework 2 Chapter 14 CMOS Inverter DesignDocument1 paginăEE 4313 Homework 2 Chapter 14 CMOS Inverter DesignEngr. Naveed MazharÎncă nu există evaluări

- PHYSICAL ONLY CELLS - VLSI - Physical Design For FreshersDocument14 paginiPHYSICAL ONLY CELLS - VLSI - Physical Design For FreshersRA NDYÎncă nu există evaluări

- VLSI Design NotesDocument130 paginiVLSI Design NotesThilakavathi100% (1)

- 3-Channel LED Constant Current Circuit Controls Lights with Single WireDocument11 pagini3-Channel LED Constant Current Circuit Controls Lights with Single WiredsfgdsfgÎncă nu există evaluări

- A. SAS Requirement For 20kv MV Panel Integration - According SPLN TID SOGI 2014Document2 paginiA. SAS Requirement For 20kv MV Panel Integration - According SPLN TID SOGI 2014Braham Lawas LawuÎncă nu există evaluări

- Digital Integrated Circuits: A Design PerspectiveDocument113 paginiDigital Integrated Circuits: A Design Perspectiveapi-127299018Încă nu există evaluări

- ECE467: Introduction To VLSI Design: Lecture-9Document18 paginiECE467: Introduction To VLSI Design: Lecture-9snagaraj.cool7813Încă nu există evaluări

- CMOS Integrated CircuitsDocument24 paginiCMOS Integrated CircuitserneeravmehanÎncă nu există evaluări

- REN cd4504bms DST 19920626Document8 paginiREN cd4504bms DST 19920626elias rangelÎncă nu există evaluări

- A Very Fast Learning Method For Neural Networks Based On Sensitivity AnalysisDocument24 paginiA Very Fast Learning Method For Neural Networks Based On Sensitivity Analysispallab869343Încă nu există evaluări

- Cmos Device Structure: The Pull-Up Network The Pull-Down Network V A B C D Inputs Yfa, B, C, DDocument4 paginiCmos Device Structure: The Pull-Up Network The Pull-Down Network V A B C D Inputs Yfa, B, C, Dpallab869343Încă nu există evaluări

- 02.wimax Network SurveyDocument3 pagini02.wimax Network Surveypallab869343Încă nu există evaluări

- Adaptive Multi-Pattern Reuse in Multi-Cell NetworksDocument10 paginiAdaptive Multi-Pattern Reuse in Multi-Cell Networkspallab869343Încă nu există evaluări

- HO Init Ict Mobile Summit 09 FinalDocument10 paginiHO Init Ict Mobile Summit 09 Finalpallab869343Încă nu există evaluări

- Nucleos Vs Hilos WhitepaperDocument11 paginiNucleos Vs Hilos WhitepaperDIDIERMORANTESÎncă nu există evaluări

- A Very Fast Learning Method For Neural Networks Based On Sensitivity AnalysisDocument24 paginiA Very Fast Learning Method For Neural Networks Based On Sensitivity Analysispallab869343Încă nu există evaluări

- Nigel Warburton - Cum Sa Gandim Corect Si EficientDocument221 paginiNigel Warburton - Cum Sa Gandim Corect Si EficientRoxanita RoxÎncă nu există evaluări

- CSE 304-Digital Signal Processing: Dr. Amir A. Khan Office: A-218, SEECS 9085-2162 Amir - Ali@seecs - Edu.pkDocument22 paginiCSE 304-Digital Signal Processing: Dr. Amir A. Khan Office: A-218, SEECS 9085-2162 Amir - Ali@seecs - Edu.pkAlamgir Ahmad KhattakÎncă nu există evaluări

- Earthworks Computations and MethodsDocument24 paginiEarthworks Computations and MethodsBryan ResullarÎncă nu există evaluări

- LKJHGFVDocument2 paginiLKJHGFVGautam KryptoÎncă nu există evaluări

- Reference Manual Standard Interface Command ... - Mettler Toledo PDFDocument92 paginiReference Manual Standard Interface Command ... - Mettler Toledo PDFRastiÎncă nu există evaluări

- European Mouflon - English - CA09Document8 paginiEuropean Mouflon - English - CA09Denis TancevÎncă nu există evaluări

- Assignment 2Document2 paginiAssignment 2yathasamboÎncă nu există evaluări

- Mangaldan Distric Ii Pogo-Palua Elementary School: ND RDDocument3 paginiMangaldan Distric Ii Pogo-Palua Elementary School: ND RDFlordeliza Manaois RamosÎncă nu există evaluări

- Automata and Quantum ComputingDocument34 paginiAutomata and Quantum ComputingJorge LeandroÎncă nu există evaluări

- Operation ManagementDocument15 paginiOperation ManagementRabia RasheedÎncă nu există evaluări

- Calculate stock indices and returnsDocument5 paginiCalculate stock indices and returnsSiddhant AggarwalÎncă nu există evaluări

- Matrix Operations / ManipulationDocument4 paginiMatrix Operations / ManipulationRyan5443Încă nu există evaluări

- ME 171 SyllabusDocument7 paginiME 171 SyllabusLucas Penalva Costa SerraÎncă nu există evaluări

- Powershape: Training CourseDocument18 paginiPowershape: Training CourseZulhendriÎncă nu există evaluări

- Docs Slides Lecture1Document31 paginiDocs Slides Lecture1PravinkumarGhodakeÎncă nu există evaluări

- Fisika Zat Padat I: Dosen: Dr. Iwantono, M.Phil Jurusan Fisika Fmipa-UrDocument78 paginiFisika Zat Padat I: Dosen: Dr. Iwantono, M.Phil Jurusan Fisika Fmipa-UrMailestari Wina YanceÎncă nu există evaluări

- Solid State PhysicsDocument281 paginiSolid State PhysicsChang Jae LeeÎncă nu există evaluări

- Risk, Return, and The Capital Asset Pricing ModelDocument52 paginiRisk, Return, and The Capital Asset Pricing ModelFaryal ShahidÎncă nu există evaluări

- IT-Glossary French - EnglishDocument56 paginiIT-Glossary French - EnglishGosia SielickaÎncă nu există evaluări

- No SystemDocument15 paginiNo SystemAjeet Singh RachhoyaÎncă nu există evaluări

- USL - Problem StatementDocument3 paginiUSL - Problem StatementMarket CharchaÎncă nu există evaluări

- HIMA - WhitePaper - Hybrid Systems For Smart Pipeline Management - finalEUDocument6 paginiHIMA - WhitePaper - Hybrid Systems For Smart Pipeline Management - finalEUAndrew XuguomingÎncă nu există evaluări

- Linear Slot Diffusers 1Document13 paginiLinear Slot Diffusers 1AlihassanÎncă nu există evaluări

- Phy1 11 - 12 Q1 0603 PF FDDocument68 paginiPhy1 11 - 12 Q1 0603 PF FDhiroÎncă nu există evaluări

- Poisson's and Laplace Equations ExplainedDocument19 paginiPoisson's and Laplace Equations ExplainedMnskSaroÎncă nu există evaluări

- Mechanical Vibration NotesDocument56 paginiMechanical Vibration NotesYadanaÎncă nu există evaluări

- Data Exploration in Python PDFDocument1 paginăData Exploration in Python PDFTuncay SakaogluÎncă nu există evaluări

- Splunk Quick Reference GuideDocument6 paginiSplunk Quick Reference GuideLsniperÎncă nu există evaluări

- Mathematics HL Paper 2 TZ2 PDFDocument16 paginiMathematics HL Paper 2 TZ2 PDFMADANÎncă nu există evaluări

- Tom M. Apostol - Calculus 2Document4 paginiTom M. Apostol - Calculus 2Milena Romero0% (2)