Documente Academic

Documente Profesional

Documente Cultură

Circuitos Secuenciales 6

Încărcat de

Gustavo PaisDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Circuitos Secuenciales 6

Încărcat de

Gustavo PaisDrepturi de autor:

Formate disponibile

Capítulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores

CIRCUITOS SECUENCIALES:

ANALISIS Y DISEÑO DE

CIRCUITOS CONTADORES

• Contadores y Divisores de frecuencia Asíncronos

• Contadores y Divisores de frecuencia Sincronos

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 1

Diagrama de bloques de un contador y un

divisor de frecuencia

Salida 1

Salida 2

Entrada de impulsos Contador n Salidas

Salida n

Divisor de

Entrada de impulsos Salida

frecuencia

Un flanco de bajada por

cada n flancos de entrada

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 2

Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 1

Capítulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores

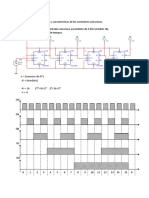

Circuito contador binario de módulo 16

Q0 Q1 Q2 Q3

"1"

2 IC1A 7 IC1B 2 IC2A 7 IC2B

4 PR PR PR PR

J Q 15 9

J Q 11 4

J Q 15 9

J Q 11

1 6 1 6

CLK CLK CLK CLK

16 14 12 10 16 14 12 10

K Q K Q K Q K Q

CL CL CL CL

Entrada de 3

7476 8

7476 3

7476 8

7476

impulsos

S R1

"1"

10 k

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 3

Cronograma de funcionamiento del contador

binario de módulo 16

CLK

t

Q0

t

Q1

t

Q2

t

Q3

t

0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 0000

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 4

Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 2

Capítulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores

Retardo de propagación al pasar del estado

1111 al 0000

T

CLK

t

Q0

t

Q1

t

Q2

t

Q3

t

tpb tpb tpb tpb

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 5

Cronograma de funcionamiento con tiempos

de retardo

CLK

t

QA

t

QB

t

QC

t

QD

t

0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 0000

Estados no 0000 0010 0000 0110 0100 0000 1000 1010 1000 1100 1110 1100 1000

deseados

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 6

Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 3

Capítulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores

Contador binario descendente de módulo 16

"1"

Q0 Q1 Q2 Q3

R1

10 k)

S

IC1A IC1B IC2A IC2B

PR PR PR PR

J Q J Q J Q J Q

CLK CLK CLK CLK

K Q K Q K Q K Q

CL CL CL CL

Entrada de 7476 7476 3

7476 8

7476

impulsos

"1"

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 7

Cronograma de funcionamiento del contador

binario descendente de módulo 16

CLK

t

Q0

t

Q1

t

Q2

t

Q3

t

1111 1110 1101 1100 1011 1010 1001 1000 0111 0110 0101 0100 0011 0010 0001 0000 1111

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 8

Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 4

Capítulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores

Contador Up-Down de modulo 8

Q0 Q1 Q2

"1"

PR PR PR

J Q J Q J Q

CLK CLK CLK

K Q K Q K Q

CL CL CL

Entrada de 7476

impulsos

UP/DOWN S R1

Vcc

10 k

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 9

Contador Up-Down de modulo 8 mejorado

Q0 Q1 Q2

"1" "1" "1"

PR PR PR

J Q J Q J Q

CLK CLK CLK

K Q K Q K Q

CL CL CL

Entrada de 8

impulsos

UP/DOWN S R1

Vcc

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 10

Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 5

Capítulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores

Contador BCD asíncrono

Q0 Q1 Q2 Q3

"1"

PR PR PR PR

J Q J Q J Q J Q

CLK CLK CLK CLK

K Q K Q K Q K Q

CL CL CL CL

Entrada de

impulsos

S R1

"1"

10 k

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 11

Cronograma del contador asíncrono BCD

CLK

t

Q0

t

Q1

t

Q2

t

Q3

t

Valor binario 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 0000

Valor decimal 0 1 2 3 4 5 6 7 8 9 0

Tiempo

de retardo

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 12

Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 6

Capítulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores

Dado electrónico con biestables J-K

Q0 Q1 Q2

"1"

PR PR PR

S J Q J Q J Q

CLK CLK CLK

K Q K Q K Q

CL CL CL

Entrada de

impulsos 10 kHz

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 13

EL 7490

7490

CTR

R0(1) (2) &

CT = 0 Control

CPA 14 A 12 R0(2) (3)

QA

1

CPB B 9

QB

(6)

QC

8 R9(1) &

Z2

2 11 (7)

R0(1) QD R9(2)

3

R0(2)

6 DIV 2

R9(1)

7 A (14) + (12)

QA

R9(2) –3 CT = 1

7490 DIV 5

(9)

QB

0

B (1) + (8)

CT QC

–3 CT = 4 (11)

3 QD

ANSI/IEEE 91-1973 ANSI/IEEE 91-1984

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 14

Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 7

Capítulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores

R9(1)

(6)

Contador 7490

(7)

R9(2)

(12)

J Q QA

INPUT (14)

A CK

QB (9)

J Q

INPUT (1)

B CK

(8) Q

J Q C

CK

(11) Q

S Q D

CK

R Q

(2)

R0(1)

R0(2) (3)

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 15

Cronograma del modo 1 de funcionamiento

del 7490

CLK

t

QA

t

QB

t

QC

t

QD

t

0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 0000

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 16

Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 8

Capítulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores

Contador de 0 a 999 en BCD

a b c d e f g IC4 a b c d e f g IC5 a b c d e f g IC6

7448 7448 7448

1 2 4 8 BI/RB0 RBI LT "1" 1 2 4 8 BI/RB0 RBI LT "1" 1 2 4 8 BI/RB0 RBI LT "1"

QA QB QC QD IC1 QA QB QC QD IC2 QA QB QC QD IC3

7490 7490 7490

VCC A B R0(1) R0(2) R9(1) R9(2) A B R0(1) R0(2) R9(1) R9(2) A B R0(1) R0(2) R9(1) R9(2)

+ C1

1 µF

R1

10 k

CLK

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 17

El Contador 7493

7493

14 CTR Control

A QA

12

R0(1) (2) &

1

B 9 CT = 0

QB (3)

8 R0(2)

QC

2 11

R0(1) QD

DIV 2

3 (14)

R0(2) CP0 + (12)

Q0

7493 (9)

DIV 8 0 Q1

(1) + (8)

CP1 CT Q2

(11)

2 Q3

ANSI/IEEE 91-1973 ANSI/IEEE 91-1984

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 18

Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 9

Capítulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores

El Contador 7493

(12) [13]

J Q QA

INPUT (14) [14]

A CK

(9) [9] QB

J Q

INPUT (1) [8]

B CK

(8) [10]

J Q QC

CK

(11) [12]

J Q QD

CK

K

(2) [1]

R0(1)

R0(2) (3) [2]

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 19

Divisor de frecuencia por 13

QA QB QC QD

"1" "1" "1" "1"

J Q J Q J Q J Q

CLK

CLK CLK CLK CLK

K Q K Q K Q K Q

CL CL CL CL

CPB

7493

7408

CLK

t

QA

t

QB

t

QC

t

QD

tp

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 20

Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 10

Capítulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores

Divisor de frecuencia de varias etapas

Divisor de Divisor de Divisor de

Entrada frecuencia frecuencia frecuencia Salida

por K por L por N

Frecuencia Frecuencia Frecuencia Frecuencia

de entrada de entrada de entrada de entrada

K K·L K·L·N

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 21

Divisor de frecuencia por 91

Conexión en cascada

Entrada IC1 IC2

A QA A QA

B B

QB QB

QC QC Salida

R0(1) QD R0(1) QD

R0(2) R0(2)

7493 7493

IC3A IC3B

7408 Frecuencia de entrada 7408 Frecuencia de entrada

13 13·7

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 22

Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 11

Capítulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores

Divisor de frecuencia por 91

con un menor tiempo de retardo

Salida

IC4A

3 7400

IC3A IC3B

1 2

7411 7411

IC1 IC2

Entrada A QA A QA

B B

QB QB

QC QC

R0(1) QD R0(1) QD

R0(2) R0(2)

7493 7493

Divisor por 7 Divisor por 13

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 23

Diagrama de bloques Reloj digital

Circuito visualizador Circuito visualizador

de los minutos de las horas

Señal de

entrada

50 Hz Divisor de Divisor de Contador Contador

frecuencia frecuencia BCD BCD

por 50 por 60 de módulo 60 de módulo 24

1 impulso por segundo 1 impulso por minuto 1 impulso por hora

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 24

Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 12

Capítulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores

Divisor de frecuencia por 50

Señal de

entrada

a 50 Hz 14 14

A 12 A 12

QA QA

1 1

B 9 B 9

QB QB

8 8

QC QC Señal

2 11 2 11 de 1 Hz

R0(1) QD R0(1) QD

3 Señal 3

R0(2) R0(2)

de 5 Hz

6 6

R9(1) R9(1)

7 7

R9(2) R9(2)

7490 7490

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 25

Divisor de frecuencia por 60

Señal de

entrada;

1 impulso

por minuto 14 12 14 12

A QA A QA

1 1

B 9 B 9

QB QB

8 8

QC QC

2 11 2 11 1 impulso

R0(1) QD R0(1) QD cada 60

3 3 segundos

R0(2) R0(2)

6 6

R9(1) R9(1)

7 7

R9(2) R9(2)

7490 7490

Señal de 1 impulso

cada 10 segundos

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 26

Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 13

Capítulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores

Circuito contador de unidades y decenas de

minutos Display unidades Display decenas

de minutos de minutos

13 12 11 10 9 15 14 13 12 11 10 9 15 14

a b c d e f g 7448 a b c d e f g 7448

1 2 4 8 BI/RB0 RBI LT "1" 1 2 4 8 BI/RB0 RBI LT "1"

7 1 2 6 4 5 3 7 1 2 6 4 5 3

1 impulso

por hora

12 9 8 11 7490 12 9 8 11 7490

QA QB QC QD QA QB QC QD

A B A B

R0(1) R0(2) R9(1) R9(2) R0(1) R0(2) R9(1) R9(2)

1 impulso 14 1 2 3 6 7 14 1 2 3 6 7

por minuto

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 27

Circuito contador de Unidades y decenas de

horas Display unidades Display decenas

de hora de hora

13 12 11 10 9 15 14 13 12 11 10 9 15 14

a b c d e f g 7448 a b c d e f g 7448

1 2 4 8 BI/RB0 RBI LT "1" 1 2 4 8 BI/RB0 RBI LT "1"

7 1 2 6 4 5 3 7 1 2 6 4 5 3

12 9 8 11 7490 12 9 8 11 7490

QA QB QC QD QA QB QC QD

A B A B

R0(1) R0(2) R9(1) R9(2) R0(1) R0(2) R9(1) R9(2)

1 impulso 14 1 2 3 6 7 14 1 2 3 6 7

por hora

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 28

Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 14

Capítulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores

Dado electrónico realizado con el 74191

13 12 11 10 9 15 14

a b c d e f g IC2

7448

1 2 4 8 BI/RB0 RBI LT

7 1 2 6 4 5 3

U3 Vcc

1

12 2

13

7410

3 2 6 7 13 12

QA QB QC QD RCO MAX/MIN IC1

74191

A B C D CLK G D/U LOAD

15 1 10 9 14 4 5 11

Vcc

Entrada de

S impulsos

10 kHz

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 29

EL 74190

74190

CTEN (4) G1

CTR DIV 10

(12)

15 2(CT = 0) Z6 MAX/MIN

3 (5)

A QA D/U M2 [DOWN] 3(CT = 9) Z6

1

B 2 M3 [UP]

10 QB (14) (13)

C 6 CLK 6, 1, 4 RCO

9 QC 1,2–/1,3+

D 7 G4

QD

LOAD (11) C5

13

14 RCO

CLK

4 A (15) 5D [1] +– (3)

QA

G

(2)

5

D/U B (1) [2] QB

11 12

LOAD MAX/MIN C (10) [4] (6)

QC

74190 D (9) [8] (7)

QD

ANSI/IEEE 91-1973

ANSI/IEEE 91-1984

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 30

Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 15

Capítulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores

Cronograma de funcionamiento del 74190

LOAD

B

DATA

INPUTS

C

CLOCK

D/U

CTEN

QA

QB

QC

QD

MAX/MIN

RCO

7 8 9 0 1 2 2 2 1 0 9 8 7

LOAD COUNT UP INHIBIT COUNT DOWN

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 31

Contador de 0 a 999 con C.I 74190

conexión asíncrona

Unidades Decenas Centenas

IC1 IC2

74190 74190 IC3

74190

QA QB QA QD RCO MAX/MIN QA QB QA QD RCO MAX/MIN QA QB QA QD RCO MAX/MIN

CLK G D/U LOAD CLK G D/U LOAD

A B C D A B C D CLK G D/U LOAD

A B C D

"1"

CLK

DOWN/UP

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 32

Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 16

Capítulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores

Contador de 0 a 9999 con C.I 74190

conexión síncrona o propagación anticipada

UNIDADES DECENAS CENTENAS UNIDADES DE MILLAR

IC1 IC2 IC3 IC4

74190 74190 74190 74190

QA QB QC QD RCO MAX/MIN QA QB QC QD RCO MAX/MIN QA QB QC QD RCO MAX/MIN QA QB QC QD RCO MAX/MIN

A B C D CLK G D/U LOAD A B C D CLK G D/U LOAD A B C D CLK G D/U LOAD A B C D CLK G D/U LOAD

"1"

CLK

DOWN/UP

IC5A IC6A

7400 7410

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 33

Contador de 0 a 999 con C.I 74190

conexión seudoasíncrona

UNIDADES DECENAS CENTENAS

IC1 IC2 IC3

74190 74190 74190

QA QB QC QD RCO MAX/MIN QA QB QC QD RCO MAX/MIN QA QB QC QD RCO MAX/MIN

A B C D CLK G D/U LOAD A B C D CLK G D/U LOAD A B C D CLK G D/U LOAD

CLK

"1"

DOWN/UP

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 34

Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 17

Capítulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores

El 74191

74191

CTEN (4) G1

CTR DIV 16

(12)

15 2(CT = 0) Z6 MAX/MIN

3 (5)

A QA D/U M2 [DOWN] 3(CT = 15) Z6

1

B 2 M3 [UP]

10 QB (13)

C (14) 6, 1, 4 RCO

6 CLK 1,2–/1,3+

9 QC

D 7 G4

QD

LOAD (11) C5

13

14 RCO

CLK

4 A (15) 5D [1] +– (3)

QA

G

(2)

5

D/U B (1) [2] QB

11 12

LOAD MAX/MIN C (10) [4] (6)

QC

74191 D (9) [8] (7)

QD

ANSI/IEEE 91-1973 ANSI/IEEE 91-1984

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 35

Cronograma de funcionamiento del 74191

LOAD

B

DATA

INPUTS

C

CLOCK

D/U

CTEN

QA

QB

QC

QD

MAX/MIN

RCO

13 14 15 0 1 2 2 2 1 0 15 14 13

LOAD COUNT UP INHIBIT COUNT DOWN

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 36

Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 18

Capítulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores

El 74192

74192

(14) CTR DIV 10

CLR CT = 0

(12)

1 CT = 9 C0

15

A QA

3 UP (5) 2+

1

B 2 G1

10 QB (13)

C 6 DOWN (4) 1–

2 CT = 0 B0

9 QC

D 7 G2

QD (11)

LOAD C3

5

UP

4 12 A (15) 3D [1] (3)

QA

DN C0

11 13 (1) (2)

LOAD B0 B [2] QB

14

CLR C (10) [4] (6)

QC

74192 D (9) [8] (7)

QD

ANSI/IEEE 91-1972 ANSI/IEEE 91-1984

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 37

Cronograma de funcionamiento del 74192

CLR

LOAD

B

DATA

INPUTS

C

UP

DOWN

QA

QB

OUTPUTS

QC

QD

CO

BO

0 7 8 9 0 1 2 1 0 9 8 7

CLEAR PRESET COUNT UP COUNT DOWN

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 38

Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 19

Capítulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores

Contador de 0 a 999 con C.I 74192

conexión en cascada

Unidades Decenas Centenas

A B C D A B C D A B C D

Contaje Salida

UP CO UP CO UP CO

(Up) arrastre

74192 74192 74192

Descontaje DOWN BO DOWN BO DOWN BO Salida

(Down) acreadora

LOAD CLEAR LOAD CLEAR LOAD CLEAR

Carga

Puesta a cero

Capitulo 6: Circuitos Secuenciales:Análisis y Diseño de Circuitos Contadores 39

Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 20

S-ar putea să vă placă și

- Lista Salsa para Orquesta 25-08-2021Document59 paginiLista Salsa para Orquesta 25-08-2021Renato RenatoÎncă nu există evaluări

- Ejercicios prácticos con Electrónica: Proyectos de electrónica con Arduino y Raspberry PiDe la EverandEjercicios prácticos con Electrónica: Proyectos de electrónica con Arduino y Raspberry PiEvaluare: 5 din 5 stele5/5 (1)

- Movistar-Auditoria FinancieraDocument39 paginiMovistar-Auditoria FinancieraLisbeth AYALA GARIBAY0% (1)

- República de Panamá TAMBORITOSDocument12 paginiRepública de Panamá TAMBORITOSBella Vista0% (1)

- Actividad de ReconocimientoDocument3 paginiActividad de ReconocimientoDavid Arboleda RamirezÎncă nu există evaluări

- El Grito Del AmorDocument278 paginiEl Grito Del AmorFlaviospinetta100% (2)

- Informe Final ContadoresDocument9 paginiInforme Final ContadoresBrayan TGÎncă nu există evaluări

- Informe-Proyecto de Tacometro DigitalDocument29 paginiInforme-Proyecto de Tacometro DigitalBrian CwÎncă nu există evaluări

- Examen Sep06 Res234aDocument3 paginiExamen Sep06 Res234apctronicÎncă nu există evaluări

- Circuitos Secuenciales: Analisis Y Diseño Con RegistrosDocument17 paginiCircuitos Secuenciales: Analisis Y Diseño Con RegistrosluisutorÎncă nu există evaluări

- Contadores digitales: tipos, circuitos y aplicacionesDocument19 paginiContadores digitales: tipos, circuitos y aplicacionesdaniÎncă nu există evaluări

- 4 Contadores Preinforme (Autoguardado)Document10 pagini4 Contadores Preinforme (Autoguardado)Renatto LoyolaÎncă nu există evaluări

- Lab 4Document7 paginiLab 4Marco Antonio Ergueta YujraÎncă nu există evaluări

- 02 Ejercicios Contadores Asíncronos y Divisores de FrecuenciaDocument3 pagini02 Ejercicios Contadores Asíncronos y Divisores de FrecuenciarzzzjsfÎncă nu există evaluări

- Circuitos secuenciales y contadoresDocument15 paginiCircuitos secuenciales y contadoresArmando UsedaÎncă nu există evaluări

- Contador Sincrono y AsincronoDocument19 paginiContador Sincrono y AsincronoOzÎncă nu există evaluări

- Labo 4 FinalDocument6 paginiLabo 4 FinalAEA MONGOLÎncă nu există evaluări

- Contador Sincono G2Document3 paginiContador Sincono G2hefesto.blackÎncă nu există evaluări

- Contador AsincronoDocument16 paginiContador AsincronoDANIEL ANTONIO DANIEL ANTONIO DIAZ/SUAZOÎncă nu există evaluări

- Contador Mod 11Document1 paginăContador Mod 11AlvaÎncă nu există evaluări

- Ejercicios ContadoresDocument3 paginiEjercicios Contadoresvicky salazarÎncă nu există evaluări

- Informe 7Document12 paginiInforme 7Juan Luis Mamani SirpaÎncă nu există evaluări

- 8-6 Banda Transportadora Inspección y Sistema de Apilado VIRTUALDocument4 pagini8-6 Banda Transportadora Inspección y Sistema de Apilado VIRTUALWilson C VargasÎncă nu există evaluări

- Diseño de Sistemas Controladores SecuencialesDocument8 paginiDiseño de Sistemas Controladores SecuencialesGadiel Armijos VÎncă nu există evaluări

- Guia Laboratorio 555 y Flip FlopDocument4 paginiGuia Laboratorio 555 y Flip FlopXavier PositivoÎncă nu există evaluări

- SIMULACIONES Pre-Informe #6-7Document6 paginiSIMULACIONES Pre-Informe #6-7Luis Angel MercadoÎncă nu există evaluări

- Preparatori0 09 Sistemas Digitales EPNDocument16 paginiPreparatori0 09 Sistemas Digitales EPNBryan CeliÎncă nu există evaluări

- Practica 4Document12 paginiPractica 4Viktor AlarconÎncă nu există evaluări

- Informe 9Document5 paginiInforme 9Jeff RoblesÎncă nu există evaluări

- CSD - Producto Académico 02 RESDocument5 paginiCSD - Producto Académico 02 RESJoaquin Quispe NuñezÎncă nu există evaluări

- Soto Ricardo Taller4.Document10 paginiSoto Ricardo Taller4.ricardo.soto14Încă nu există evaluări

- Contador 0 - 12Document1 paginăContador 0 - 12Adolfo AguilarÎncă nu există evaluări

- PDF Lab 4 CompressDocument7 paginiPDF Lab 4 CompressTreason ggÎncă nu există evaluări

- Flip Flop 74ls76Document4 paginiFlip Flop 74ls76Giancarlo Villanueva Oropeza0% (1)

- Tarea 1 - Conversor Analógico-Digital Por Aproximaciones Sucesivas - 7DADocument4 paginiTarea 1 - Conversor Analógico-Digital Por Aproximaciones Sucesivas - 7DANely MÎncă nu există evaluări

- Pràctica6 Disseny de ContadorsDocument2 paginiPràctica6 Disseny de ContadorsbriceriveÎncă nu există evaluări

- Contador Mod 6 Con F-F Tipo RizoDocument1 paginăContador Mod 6 Con F-F Tipo RizoOscar CaizaÎncă nu există evaluări

- Experiencia #5Document18 paginiExperiencia #5Hector ValdiviaÎncă nu există evaluări

- PLLDocument6 paginiPLLart_ag7Încă nu există evaluări

- Labo 4 Sistemas ContadoresDocument11 paginiLabo 4 Sistemas ContadoresESPINOZA MONTESINOS ANGEL SAMUELÎncă nu există evaluări

- PRACTICA - 8 - PERIFERICO - DE - ENTRADA - TECLADO - EQ. MICROINF 9h20 - 19-03-2019Document5 paginiPRACTICA - 8 - PERIFERICO - DE - ENTRADA - TECLADO - EQ. MICROINF 9h20 - 19-03-2019Fabrice FeussiÎncă nu există evaluări

- Informe 9Document4 paginiInforme 9Alex GomezÎncă nu există evaluări

- 4to Informe de Digitales IiDocument19 pagini4to Informe de Digitales IiSamir50% (2)

- Circuito 555 Timer MonoestableDocument6 paginiCircuito 555 Timer MonoestableAngel Espinoza MontesinosÎncă nu există evaluări

- Practica Nro 4 Elt 2680 Digital 1Document3 paginiPractica Nro 4 Elt 2680 Digital 1Jamil Rodri ChoqueÎncă nu există evaluări

- lab2Document6 paginilab2LEONARDO ZENON VELASQUEZ MEJIAÎncă nu există evaluări

- Display 7seg CC con controlador 4511Document12 paginiDisplay 7seg CC con controlador 4511David ChuraÎncă nu există evaluări

- Tema 5 Contadores 2010Document33 paginiTema 5 Contadores 2010nohemy condo machacaÎncă nu există evaluări

- Lab11 Diseñoyaplicaciondecontadoressincronosyasincronos VALLE TACODocument15 paginiLab11 Diseñoyaplicaciondecontadoressincronosyasincronos VALLE TACOROMEL JIMENEZÎncă nu există evaluări

- Procedimiento Informe 7Document4 paginiProcedimiento Informe 7Eduardo EspinosaÎncă nu există evaluări

- Semáforo peatonal: objetivos, diseño y tabla de verdad para práctica de contadoresDocument5 paginiSemáforo peatonal: objetivos, diseño y tabla de verdad para práctica de contadoresVincent MenciaÎncă nu există evaluări

- Prob 4Document7 paginiProb 4Leandro SchenoneÎncă nu există evaluări

- Prob 4Document7 paginiProb 4Leandro SchenoneÎncă nu există evaluări

- lab1Document7 paginilab1LEONARDO ZENON VELASQUEZ MEJIAÎncă nu există evaluări

- Sistemas Digitales - Pre Informe 4Document21 paginiSistemas Digitales - Pre Informe 4Ruben HuaytanÎncă nu există evaluări

- Inversor Capitulo IIIDocument14 paginiInversor Capitulo IIIDiego ReyesÎncă nu există evaluări

- Informe RelojDocument6 paginiInforme RelojAndrés Garcés CÎncă nu există evaluări

- Rectificadores controladosDocument6 paginiRectificadores controladosqwer33Încă nu există evaluări

- SDDocument12 paginiSDCarlos EstradaÎncă nu există evaluări

- Diseño de PLL con frecuencímetro digitalDocument2 paginiDiseño de PLL con frecuencímetro digitalJoshs Basto SaénzÎncă nu există evaluări

- Guía contador binario 4 bitsDocument4 paginiGuía contador binario 4 bitsedry_12125707100% (1)

- Pepe Biondi, cómico argentinoDocument4 paginiPepe Biondi, cómico argentinoJonathan XÎncă nu există evaluări

- Recursos literarios: figuras retóricas enDocument6 paginiRecursos literarios: figuras retóricas enEduardo SamÎncă nu există evaluări

- Los Pliegues Del Tiempo Kronos, Aión y KairósDocument6 paginiLos Pliegues Del Tiempo Kronos, Aión y KairósRoman Ruiz100% (1)

- Resultados Onem Tercera Etapa 2012Document11 paginiResultados Onem Tercera Etapa 2012viterickÎncă nu există evaluări

- La Muerte y Otras SorpresasDocument2 paginiLa Muerte y Otras SorpresasBryan PinanjotaÎncă nu există evaluări

- Himno NacionalDocument5 paginiHimno NacionalMariela MejiaÎncă nu există evaluări

- Inteligencias Múltiples en el AulaDocument21 paginiInteligencias Múltiples en el AulawilmerbalÎncă nu există evaluări

- 8.0-Fichas Tecnicas YanacochaDocument12 pagini8.0-Fichas Tecnicas Yanacochaelvis barreto sanchezÎncă nu există evaluări

- Partituras de Violin Las Mañanitas Con Notas Escrutas - Google SearchDocument1 paginăPartituras de Violin Las Mañanitas Con Notas Escrutas - Google SearchSara Lee CoriaÎncă nu există evaluări

- Mix POP en EspañolDocument3 paginiMix POP en EspañolJose Nieves BayonaÎncă nu există evaluări

- Guía para La Catalogación Descriptiva de Materiales MusicalesDocument7 paginiGuía para La Catalogación Descriptiva de Materiales MusicalesgabriesilÎncă nu există evaluări

- Lección 1 - Pronombres Personales y Verbo To BeDocument2 paginiLección 1 - Pronombres Personales y Verbo To BeMaria IsabelÎncă nu există evaluări

- La Guerra Empieza en CubaDocument82 paginiLa Guerra Empieza en CubaVíctor Ruiz IriarteÎncă nu există evaluări

- GSS-FOR-073 Check List de Plataforma Elevadoras o Canastilla V01Document2 paginiGSS-FOR-073 Check List de Plataforma Elevadoras o Canastilla V01Isabel OliverosÎncă nu există evaluări

- Ensayo ArbolDocument4 paginiEnsayo ArbolarielÎncă nu există evaluări

- Degradacion de La Señal Que Causan La EMI y La RFIDocument10 paginiDegradacion de La Señal Que Causan La EMI y La RFIMaribel Yepes LeguiaÎncă nu există evaluări

- Estrella de Los Mares-Rocio GallegoDocument105 paginiEstrella de Los Mares-Rocio GallegoCele SchulzÎncă nu există evaluări

- Internet Celsia: Planes de banda ancha con velocidades de 25 a 100 MbpsDocument9 paginiInternet Celsia: Planes de banda ancha con velocidades de 25 a 100 MbpsYesid RojasÎncă nu există evaluări

- Los Ritmos Del EcuadorDocument33 paginiLos Ritmos Del EcuadorCarlos DuyÎncă nu există evaluări

- Es V 72 Actividad Esta Bien Que Alguien Te Haga Esto Ver 1Document3 paginiEs V 72 Actividad Esta Bien Que Alguien Te Haga Esto Ver 1clraÎncă nu există evaluări

- taller Fase 4 - Historia de La Música OccidentalDocument5 paginitaller Fase 4 - Historia de La Música OccidentalJavier Rodriguez LópezÎncă nu există evaluări

- Metodología y entrenamiento actoralDocument13 paginiMetodología y entrenamiento actoralRonie CusóÎncă nu există evaluări

- Presentacion IPTVDocument21 paginiPresentacion IPTVGonzalo Velastegui CoronelÎncă nu există evaluări

- Acorde NapolitanoDocument2 paginiAcorde Napolitanogzppczdss6Încă nu există evaluări