Documente Academic

Documente Profesional

Documente Cultură

This Is A 8 Bit Wide 16 Bytes Deep FIFO

Încărcat de

akramece912Descriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

This Is A 8 Bit Wide 16 Bytes Deep FIFO

Încărcat de

akramece912Drepturi de autor:

Formate disponibile

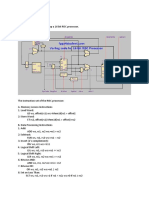

-- This is a 8 Bit Wide 16 Bytes Deep FIFO.

-- I have not synthesized but i feel that there should be no problem LIbrary IEEE; use IEEE.std_logic_1164.all; use IEEE.std_logic_arith.all; use IEEE.std_logic_unsigned.all; Entity fifo is Port ( Clk : in std_logic; Reset : in std_logic; WriteEnable : in std_logic; ReadEnable : in std_logic; DataIn : in std_logic_vector(7 downto 0); DataOut : out std_logic_vector(7 downto 0); FifoEmpty : out std_logic; FifoFull : out std_logic ); END fifo;-- entity declarations ends Architecture A_fifo of fifo is Component Rams Port ( Writeen Wclk Datain Addr Dataout ); END Component; Signal ReadPointer : std_logic_vector(3 downto 0); Signal WritePointer : std_logic_vector(3 downto 0); Signal ByteCounter : std_logic_vector(4 downto 0); Signal Signal Signal Signal WriteEnable_s Addr_s FifoFull_s FifoEmpty_s : : : : std_logic; std_logic_vector(3 downto 0); std_logic; std_logic; : in std_logic; : in std_logic; : in std_logic_vector(7 downto 0); : in std_logic_vector(3 downto 0); : out std_logic_vector(7 downto 0)

Begin FifoRam : Rams Port map ( Writeen Wclk Datain Dataout Addr ); ReadWriteFifoOut : Process(Clk,Reset) Begin IF ( Reset = '1') then ReadPointer <= "0000"; WritePointer <= "0000"; => WriteEnable_s, => Clk, => DataIn, => DataOut, => Addr_s

ByteCounter <= "00000"; ELSIF(Clk'event and Clk = '1') then IF ( WriteEnable = '1' and FifoFull_s = '0' and ReadEnable = '0') then WritePointer <= WritePointer + 1; ByteCounter <= ByteCounter + 1; END IF; IF ( ReadEnable = '1' and FifoEmpty_s = '0' and WriteEnable = '0') then ReadPointer ByteCounter <= ReadPointer + 1; <= ByteCounter - 1; END IF; END IF; END process;-- ReadWriteFifo Process ends ------------------------------------------------------------ Combinatorial Logic ----------------------------------------------------------FifoEmpty_s <= '1' when ( ByteCounter = "0000") else '0'; FifoFull_s <= ByteCounter(4); FifoFull <= FifoFull_s; FifoEmpty <= FifoEmpty_s; WriteEnable_s <= '1' when ( WriteEnable = '1' and FifoFull_s = '0') else '0'; when ( WriteEnable = '1') else ReadPointer; -----------------------------------------------------------END A_fifo;--Architecture Ends The following xnf File was used for Memory LCANET,6 PROG, MEMGEN, 5.2.0, "14-deep by 8-wide SYNC_RAM macro called 'sramd_s'" PART, 4013EPQ160 PWR,0,GND SYM,BANK0-00,RAMS,INIT=0000,=NEQGATES:61,LIBVER=2.0.0 PIN,A0,I,ADDR<0> PIN,A1,I,ADDR<1> PIN,A2,I,ADDR<2> PIN,A3,I,ADDR<3> PIN,WE,I,WRITEEN PIN,WCLK,I,WCLK PIN,D,I,DATAIN<0> PIN,O,O,DATAOUT<0> END SYM,BANK0-01,RAMS,INIT=0000,=NEQGATES:61,LIBVER=2.0.0 PIN,A0,I,ADDR<0> PIN,A1,I,ADDR<1> PIN,A2,I,ADDR<2> Addr_s <= WritePointer

PIN,A3,I,ADDR<3> PIN,WE,I,WRITEEN PIN,WCLK,I,WCLK PIN,D,I,DATAIN<1> PIN,O,O,DATAOUT<1> END SYM,BANK0-02,RAMS,INIT=0000,=NEQGATES:61,LIBVER=2.0.0 PIN,A0,I,ADDR<0> PIN,A1,I,ADDR<1> PIN,A2,I,ADDR<2> PIN,A3,I,ADDR<3> PIN,WE,I,WRITEEN PIN,WCLK,I,WCLK PIN,D,I,DATAIN<2> PIN,O,O,DATAOUT<2> END SYM,BANK0-03,RAMS,INIT=0000,=NEQGATES:61,LIBVER=2.0.0 PIN,A0,I,ADDR<0> PIN,A1,I,ADDR<1> PIN,A2,I,ADDR<2> PIN,A3,I,ADDR<3> PIN,WE,I,WRITEEN PIN,WCLK,I,WCLK PIN,D,I,DATAIN<3> PIN,O,O,DATAOUT<3> END SYM,BANK0-04,RAMS,INIT=0000,=NEQGATES:61,LIBVER=2.0.0 PIN,A0,I,ADDR<0> PIN,A1,I,ADDR<1> PIN,A2,I,ADDR<2> PIN,A3,I,ADDR<3> PIN,WE,I,WRITEEN PIN,WCLK,I,WCLK PIN,D,I,DATAIN<4> PIN,O,O,DATAOUT<4> END SYM,BANK0-05,RAMS,INIT=0000,=NEQGATES:61,LIBVER=2.0.0 PIN,A0,I,ADDR<0> PIN,A1,I,ADDR<1> PIN,A2,I,ADDR<2> PIN,A3,I,ADDR<3> PIN,WE,I,WRITEEN PIN,WCLK,I,WCLK PIN,D,I,DATAIN<5> PIN,O,O,DATAOUT<5> END SYM,BANK0-06,RAMS,INIT=0000,=NEQGATES:61,LIBVER=2.0.0 PIN,A0,I,ADDR<0> PIN,A1,I,ADDR<1> PIN,A2,I,ADDR<2> PIN,A3,I,ADDR<3> PIN,WE,I,WRITEEN PIN,WCLK,I,WCLK PIN,D,I,DATAIN<6> PIN,O,O,DATAOUT<6> END SYM,BANK0-07,RAMS,INIT=0000,=NEQGATES:61,LIBVER=2.0.0

PIN,A0,I,ADDR<0> PIN,A1,I,ADDR<1> PIN,A2,I,ADDR<2> PIN,A3,I,ADDR<3> PIN,WE,I,WRITEEN PIN,WCLK,I,WCLK PIN,D,I,DATAIN<7> PIN,O,O,DATAOUT<7> END EOF -- This entities are not tested ---Behavioral Code For RAM Library IEEE; use IEEE.std_logic_1164.all; use IEEE.std_logic_arith.all; use IEEE.std_logic_unsigned.all; Entity Rams is Port ( Writeen : in std_logic; Wclk : in std_logic; Datain : in std_logic_vector(7 downto 0); Dataout : out std_logic_vector(7 downto 0); Addr : in std_logic_vector(3 downto 0) ); END Rams;-- Entity Ends Architecture Behave of Rams is Type Mem is array ( 15 downto 0) of std_logic_vector( 7 downto 0); Signal Memory : Mem; Begin Write_Process : Process(Wclk) Begin if (Wclk'event and Wclk = '1') then if ( Writeen = '1') then Memory(Conv_Integer(Addr)) <= Datain; end if; end if; end process; -- Write Process Ends Dataout <= Memory(Conv_Integer(Addr)); End Behave;-- Architecture Ends

S-ar putea să vă placă și

- Python Programming for Beginners Crash Course with Hands-On Exercises, Including NumPy, Pandas and MatplotlibDe la EverandPython Programming for Beginners Crash Course with Hands-On Exercises, Including NumPy, Pandas and MatplotlibÎncă nu există evaluări

- Fifo Controller PresentationDocument26 paginiFifo Controller PresentationthemikulÎncă nu există evaluări

- Unit2 VHDL ProgDocument15 paginiUnit2 VHDL Progsayan.transcuratorsÎncă nu există evaluări

- 511X8 FIFOs DESIGN EXAMPLEDocument6 pagini511X8 FIFOs DESIGN EXAMPLE2110046346Încă nu există evaluări

- Keyboard InterfaceDocument16 paginiKeyboard InterfaceDinesh ChoudharyÎncă nu există evaluări

- DsadsasssdDocument5 paginiDsadsasssdAnonymous FPCYCdNBÎncă nu există evaluări

- Comp Arch ElevatorDocument24 paginiComp Arch ElevatorUtkarsh KumarÎncă nu există evaluări

- Bài 1: thiết kế mạch nhân 2 bit. Chương trìnhDocument17 paginiBài 1: thiết kế mạch nhân 2 bit. Chương trìnhHoa BíÎncă nu există evaluări

- Structural LabDocument69 paginiStructural LabNABIRASOOLÎncă nu există evaluări

- Bank Record PROJECT ReportDocument13 paginiBank Record PROJECT ReportD E W A N AÎncă nu există evaluări

- Banking Record System: Project ReportDocument13 paginiBanking Record System: Project ReportD E W A N AÎncă nu există evaluări

- Cad of Electronics LabDocument4 paginiCad of Electronics LabVaibhav PandeyÎncă nu există evaluări

- VlsiDocument37 paginiVlsiRitwik SoniÎncă nu există evaluări

- Rekonstrukt: FPGA Based Forth Development Environment / Forth Based FPGA Development EnvironmentDocument4 paginiRekonstrukt: FPGA Based Forth Development Environment / Forth Based FPGA Development EnvironmentSuraj Kumar100% (1)

- 64pointfftprocessor: / /FFT - 64P - 16B - Top - Testbench - VHDDocument7 pagini64pointfftprocessor: / /FFT - 64P - 16B - Top - Testbench - VHDDeepikaÎncă nu există evaluări

- Engr2015 Lab2Document13 paginiEngr2015 Lab2SUPER AMAZINGÎncă nu există evaluări

- VHDL KeypadDocument17 paginiVHDL Keypadtroid426Încă nu există evaluări

- Arduino Digital Indicator CodeDocument3 paginiArduino Digital Indicator CodeCody McCormack100% (1)

- Intro Vhdl1Document30 paginiIntro Vhdl1pandaros000Încă nu există evaluări

- AVR External Interrupts - INT0 ExampleDocument5 paginiAVR External Interrupts - INT0 ExampleNina FloydÎncă nu există evaluări

- C HandoutDocument14 paginiC HandoutAsep Bagja NugrahaÎncă nu există evaluări

- SIPO Register VHDL Code With TestbenchDocument2 paginiSIPO Register VHDL Code With TestbenchJyo Jetti100% (1)

- Proiecte ArduinoDocument46 paginiProiecte ArduinoSyad AlyÎncă nu există evaluări

- 8bit MiniproDocument7 pagini8bit MiniprodemononesÎncă nu există evaluări

- Adafruit ILI9341.CppDocument12 paginiAdafruit ILI9341.CpprokmasterkilÎncă nu există evaluări

- Môn học: Thực hành chuyên sâu Mô-đun: Xử lý tín hiệu và truyền thông Nhóm thực hành: Bài số: 01 NVDocument6 paginiMôn học: Thực hành chuyên sâu Mô-đun: Xử lý tín hiệu và truyền thông Nhóm thực hành: Bài số: 01 NVĐặng Văn TrườngÎncă nu există evaluări

- How To Interface I2C-EEPROM With LPC2148 - ARM7 SlickerDocument8 paginiHow To Interface I2C-EEPROM With LPC2148 - ARM7 SlickerabidparwezÎncă nu există evaluări

- Reviewof Cyclone IIFPGAStarter Development KitDocument7 paginiReviewof Cyclone IIFPGAStarter Development KitabdellahÎncă nu există evaluări

- KS0184 Keyestudio Multi-Purpose Shield V2Document9 paginiKS0184 Keyestudio Multi-Purpose Shield V2Xavier MuñozÎncă nu există evaluări

- Assignment3 2021HT80531Document14 paginiAssignment3 2021HT80531crypto.investnmentÎncă nu există evaluări

- Se 2011 01 STDocument13 paginiSe 2011 01 STВ'ячеслав ІльчукÎncă nu există evaluări

- VHDL Programs LabDocument20 paginiVHDL Programs LabVasu SiriÎncă nu există evaluări

- T Are A Multiplex orDocument5 paginiT Are A Multiplex orROD STEVEN CARRASCO BENAVENTEÎncă nu există evaluări

- VHDLDocument13 paginiVHDLSrijeeta SenÎncă nu există evaluări

- Aim: Hardware RequiredDocument12 paginiAim: Hardware RequiredfjhgfiuyufyjÎncă nu există evaluări

- C Based Embedded System Design Lab FileDocument28 paginiC Based Embedded System Design Lab FilePraney KalraÎncă nu există evaluări

- Globus: Lab Manual of Cmos & Vlsi DesignDocument15 paginiGlobus: Lab Manual of Cmos & Vlsi DesignanshujjainÎncă nu există evaluări

- MemoriaSRAM Chasi GutierrezDocument16 paginiMemoriaSRAM Chasi GutierrezJonathan Chasi0% (1)

- VHDL ProgramDocument5 paginiVHDL ProgramJaswanth TejaÎncă nu există evaluări

- Library IEEEDocument4 paginiLibrary IEEEAdeel HanifÎncă nu există evaluări

- VHDL CodesDocument8 paginiVHDL Codespooja_2408Încă nu există evaluări

- How To Use ESP8266 With PCF8574 - 4 Input and 4 Output: Step 1: ComponentsDocument5 paginiHow To Use ESP8266 With PCF8574 - 4 Input and 4 Output: Step 1: ComponentsedermadrugaÎncă nu există evaluări

- INFORME PRACTICA No 2Document30 paginiINFORME PRACTICA No 2MAURICIO REYES ROSEROÎncă nu există evaluări

- Exp9 Shresht GuptaDocument9 paginiExp9 Shresht GuptaLakshay SharmaÎncă nu există evaluări

- VHDL Coding Tips and TricksDocument209 paginiVHDL Coding Tips and TricksvinutaÎncă nu există evaluări

- Group Members: - Shermeen Tajammal (FA17-BEE-025) - Adeela Bashir (FA17-BEE-064) - Sana Nasir (FA17-BEE-091)Document12 paginiGroup Members: - Shermeen Tajammal (FA17-BEE-025) - Adeela Bashir (FA17-BEE-064) - Sana Nasir (FA17-BEE-091)shermeen445Încă nu există evaluări

- Simulation of Arp/Rarp: //source CodeDocument33 paginiSimulation of Arp/Rarp: //source CodeKiruthika PetchimuthuÎncă nu există evaluări

- FIFODocument3 paginiFIFOMansi LangadeÎncă nu există evaluări

- Beginning FPGA Programming - Partie72Document5 paginiBeginning FPGA Programming - Partie72ali alilouÎncă nu există evaluări

- Pic Micro Controller Based Led Moving Message DisplayDocument10 paginiPic Micro Controller Based Led Moving Message Displays_k_sahoo100% (2)

- Adsd Lab Experiments: NAME: Ankit Mukherjee REG NO: RA1911043040015 Class: Ece B'Document29 paginiAdsd Lab Experiments: NAME: Ankit Mukherjee REG NO: RA1911043040015 Class: Ece B'AnkitShubhoeMukherjeeÎncă nu există evaluări

- A Complete 8-Bit Microcontroller in VHDLDocument29 paginiA Complete 8-Bit Microcontroller in VHDLSidney O. EbotÎncă nu există evaluări

- Scheme Quartus ASC Pentru Primul Subiect Poarta ŞiDocument11 paginiScheme Quartus ASC Pentru Primul Subiect Poarta ŞiAlin ChiperÎncă nu există evaluări

- RouterDocument21 paginiRouterSantoshkumar MalabagiÎncă nu există evaluări

- Unit 6: Intel 8051 MicrcontrollerDocument19 paginiUnit 6: Intel 8051 Micrcontrollerachuu1987Încă nu există evaluări

- Arduino Language File For NotepadPlusPlusDocument2 paginiArduino Language File For NotepadPlusPlusosnarf706Încă nu există evaluări

- Lab 1 ReportDocument7 paginiLab 1 ReportNguyễn ThắngÎncă nu există evaluări

- Rapport 2:VHDL: Réalisé Par: RAIS Aya LAZREK GhitaDocument9 paginiRapport 2:VHDL: Réalisé Par: RAIS Aya LAZREK GhitaEssÎncă nu există evaluări

- Raisul Falah - (165060300111051) - Lab1Document11 paginiRaisul Falah - (165060300111051) - Lab1Wibi Wisnu WÎncă nu există evaluări

- Lab 5 DR Muslim (Latest)Document15 paginiLab 5 DR Muslim (Latest)a ThanhÎncă nu există evaluări

- Digital Pulse ProcessingDocument5 paginiDigital Pulse ProcessingNishant SinghÎncă nu există evaluări

- EPAgro CombiDocument2 paginiEPAgro CombimolinacarlosfÎncă nu există evaluări

- Digital Logic FamiliesDocument26 paginiDigital Logic FamiliessatheeshÎncă nu există evaluări

- US ITC Samsung V Apple (No. 337-TA-794) NoticeDocument3 paginiUS ITC Samsung V Apple (No. 337-TA-794) Noticenb_fanÎncă nu există evaluări

- Pioneer DDJ-1000SRT DJ Controller Service Manual (RRV4696)Document51 paginiPioneer DDJ-1000SRT DJ Controller Service Manual (RRV4696)Denoraffendy Maideen67% (3)

- Major Inventions in Control SystemsDocument4 paginiMajor Inventions in Control SystemsAli AkhterÎncă nu există evaluări

- Setup WizardDocument11 paginiSetup WizardMarlon CameyÎncă nu există evaluări

- Advanced Ev3 Robot ProgrammingDocument36 paginiAdvanced Ev3 Robot ProgrammingJaime TorresÎncă nu există evaluări

- MODEL NO.: N156B3-L0B: TFT LCD Preliminary SpecificationDocument29 paginiMODEL NO.: N156B3-L0B: TFT LCD Preliminary SpecificationJCP99Încă nu există evaluări

- A 2.4 GHZ Fully Integrated LC Vco Design Using 130 NM Cmos TechnologyDocument9 paginiA 2.4 GHZ Fully Integrated LC Vco Design Using 130 NM Cmos TechnologyAdam HernandezÎncă nu există evaluări

- Vs-Vsk.230..Pbf Series: Vishay SemiconductorsDocument9 paginiVs-Vsk.230..Pbf Series: Vishay SemiconductorsrenidwilÎncă nu există evaluări

- EasergyP3 Catalog NRJCAT17764ENDocument118 paginiEasergyP3 Catalog NRJCAT17764ENrainharÎncă nu există evaluări

- Surge Protection 1-Port Poe Injector: Pt-Pse106Gw-ArDocument16 paginiSurge Protection 1-Port Poe Injector: Pt-Pse106Gw-ArNuman AminÎncă nu există evaluări

- Power Semiconductor Drives Question BankDocument16 paginiPower Semiconductor Drives Question BankSaileela Reddy GangasaniÎncă nu există evaluări

- Lecture 56 - Components of LT SwitchgearDocument18 paginiLecture 56 - Components of LT SwitchgearSahil Dhapola100% (1)

- Data Sheet: MPS 225 E2 20 - 126645Document8 paginiData Sheet: MPS 225 E2 20 - 126645ZOO4YOU AnimalXXXÎncă nu există evaluări

- Service Manual - Rotel RMB 1095Document8 paginiService Manual - Rotel RMB 1095leorassiÎncă nu există evaluări

- AN-SM-037 FD500 Series - FD525-HALO Installation Instructions Rev ADocument19 paginiAN-SM-037 FD500 Series - FD525-HALO Installation Instructions Rev AAbdul QuadirÎncă nu există evaluări

- Exz110 enDocument242 paginiExz110 enMiguel SanchezÎncă nu există evaluări

- Jaunt VR Field GuideDocument68 paginiJaunt VR Field GuideRobertoJmzÎncă nu există evaluări

- 1987 Wienese The Performance of Diffuser Bagasse DewateringDocument4 pagini1987 Wienese The Performance of Diffuser Bagasse DewateringAhmed AlfatihÎncă nu există evaluări

- John Newlands,-WPS OfficeDocument3 paginiJohn Newlands,-WPS OfficeDeleteafter ThismlbbÎncă nu există evaluări

- Jem ZR33 Hi MassDocument2 paginiJem ZR33 Hi MassPatrick BarnesÎncă nu există evaluări

- Prepar3D View GroupsDocument22 paginiPrepar3D View GroupsTrevorHaleÎncă nu există evaluări

- Electrical Considerations For HVDC Transmission LinesDocument45 paginiElectrical Considerations For HVDC Transmission LinesNunna Baskar50% (2)

- ISIS Professional AMPLIFICADOR - Zener 200W Yiroshi.Document1 paginăISIS Professional AMPLIFICADOR - Zener 200W Yiroshi.Rafael MendozaÎncă nu există evaluări

- Not Marklin Metall Nor Meccano - Eitech KatalogDocument24 paginiNot Marklin Metall Nor Meccano - Eitech KatalogRocalinaudÎncă nu există evaluări

- 2012 Karakehayov - Data Acquisition ApplicationsDocument351 pagini2012 Karakehayov - Data Acquisition ApplicationsLEO_GONZALEZÎncă nu există evaluări

- BCU Based CRP Specs 1Document104 paginiBCU Based CRP Specs 1irfannshaikh11Încă nu există evaluări

- TransponderDocument43 paginiTransponderNguyễn NhậtÎncă nu există evaluări

- iPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsDe la EverandiPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsEvaluare: 5 din 5 stele5/5 (3)

- iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]De la EverandiPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]Evaluare: 5 din 5 stele5/5 (3)

- Chip War: The Fight for the World's Most Critical TechnologyDe la EverandChip War: The Fight for the World's Most Critical TechnologyEvaluare: 4.5 din 5 stele4.5/5 (82)

- Chip War: The Quest to Dominate the World's Most Critical TechnologyDe la EverandChip War: The Quest to Dominate the World's Most Critical TechnologyEvaluare: 4.5 din 5 stele4.5/5 (229)

- CompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102De la EverandCompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Evaluare: 5 din 5 stele5/5 (2)

- CompTIA A+ Certification All-in-One Exam Guide, Eleventh Edition (Exams 220-1101 & 220-1102)De la EverandCompTIA A+ Certification All-in-One Exam Guide, Eleventh Edition (Exams 220-1101 & 220-1102)Evaluare: 5 din 5 stele5/5 (2)

- Cyber-Physical Systems: Foundations, Principles and ApplicationsDe la EverandCyber-Physical Systems: Foundations, Principles and ApplicationsHoubing H. SongÎncă nu există evaluări

- CompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002De la EverandCompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002Evaluare: 5 din 5 stele5/5 (1)

- Computer Science: A Concise IntroductionDe la EverandComputer Science: A Concise IntroductionEvaluare: 4.5 din 5 stele4.5/5 (14)

- iPhone 15 Pro User Guide for Beginners and SeniorsDe la EverandiPhone 15 Pro User Guide for Beginners and SeniorsÎncă nu există evaluări

- Raspberry PI: Learn Rasberry Pi Programming the Easy Way, A Beginner Friendly User GuideDe la EverandRaspberry PI: Learn Rasberry Pi Programming the Easy Way, A Beginner Friendly User GuideÎncă nu există evaluări

- iPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XDe la EverandiPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XEvaluare: 3 din 5 stele3/5 (2)

- Samsung Galaxy S22 Ultra User Guide For Beginners: The Complete User Manual For Getting Started And Mastering The Galaxy S22 Ultra Android PhoneDe la EverandSamsung Galaxy S22 Ultra User Guide For Beginners: The Complete User Manual For Getting Started And Mastering The Galaxy S22 Ultra Android PhoneÎncă nu există evaluări

- Cancer and EMF Radiation: How to Protect Yourself from the Silent Carcinogen of ElectropollutionDe la EverandCancer and EMF Radiation: How to Protect Yourself from the Silent Carcinogen of ElectropollutionEvaluare: 5 din 5 stele5/5 (2)

- Essential iPhone X iOS 12 Edition: The Illustrated Guide to Using iPhone XDe la EverandEssential iPhone X iOS 12 Edition: The Illustrated Guide to Using iPhone XEvaluare: 5 din 5 stele5/5 (1)

- Hacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxDe la EverandHacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxÎncă nu există evaluări

- The comprehensive guide to build Raspberry Pi 5 RoboticsDe la EverandThe comprehensive guide to build Raspberry Pi 5 RoboticsÎncă nu există evaluări

- Arduino and Raspberry Pi Sensor Projects for the Evil GeniusDe la EverandArduino and Raspberry Pi Sensor Projects for the Evil GeniusÎncă nu există evaluări

- The User's Directory of Computer NetworksDe la EverandThe User's Directory of Computer NetworksTracy LaqueyÎncă nu există evaluări

- Raspberry Pi Retro Gaming: Build Consoles and Arcade Cabinets to Play Your Favorite Classic GamesDe la EverandRaspberry Pi Retro Gaming: Build Consoles and Arcade Cabinets to Play Your Favorite Classic GamesÎncă nu există evaluări

![iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]](https://imgv2-1-f.scribdassets.com/img/audiobook_square_badge/728318688/198x198/f3385cbfef/1715193157?v=1)