Documente Academic

Documente Profesional

Documente Cultură

module of D - FF

Încărcat de

api-37366610 evaluări0% au considerat acest document util (0 voturi)

40 vizualizări5 paginiTitlu original

new

Drepturi de autor

© Attribution Non-Commercial (BY-NC)

Formate disponibile

DOC, PDF, TXT sau citiți online pe Scribd

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Attribution Non-Commercial (BY-NC)

Formate disponibile

Descărcați ca DOC, PDF, TXT sau citiți online pe Scribd

0 evaluări0% au considerat acest document util (0 voturi)

40 vizualizări5 paginimodule of D - FF

Încărcat de

api-3736661Drepturi de autor:

Attribution Non-Commercial (BY-NC)

Formate disponibile

Descărcați ca DOC, PDF, TXT sau citiți online pe Scribd

Sunteți pe pagina 1din 5

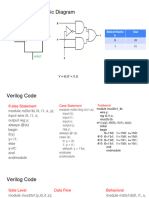

//module of D_FF //ALU:

module dff(q,qbar,d,clear,clk); module alu(out,in1,in2,control);

output q,qbar; input [3:0] in1,in2; //define 4 bit inputs

input d,clear,clk; input [2:0] control; //define 3bit input control

wire s,sbar,r,rbar,cbar; output [4:0] out;

assign cbar= ~clear; //create complement reg [4:0] out=0; //initialize 5bit output out

// of signal clear always @ (in1,in2,control)

assign sbar= ~(s & rbar), //ff using 3 SR case(control)

s= ~(sbar & cbar & ~clk), // Latches 3'd0:out=in1;

r= ~(s & rbar & ~clk), 3'd1:out=in1+in2;

rbar= ~(r & cbar & d); 3'd2:out=in1-in2;

assign q= ~(s & qbar), 3'd3:out=in1*in2;

qbar= ~(q & cbar & r); 3'd4:out=in1/in2;

endmodule 3'd5:out=in1%4;

3'd6:out=in2%8;

// module of t_flipflop 3'd7:out=in1<<in2;

module tff(q,clk,clear); endcase

output q; endmodule

input clk,clear; module testalu(); //stimulus module

dff df(q, ,~q,clear,clk); reg [3:0] in1,in2;

endmodule reg [2:0] control;

wire [4:0] out;

// 4-bit counter using bottomup approach alu talu(out,in1,in2,control);

module counterbottomup(out,clk,clear); initial in1=2;

output [3:0]out; initial in2=4;

input clk,clear; initial

tff tff0(out[0],clk,clear); //instantiate control=0;

tff tff1(out[1],out[0],clear); //t_flipflops always #5

tff tff2(out[2],out[1],clear); control=control+1;

tff tff3(out[3],out[2],clear); endmodule

endmodule

module tcounterb();//stimulus module //Bcd to 7 Segment Double display

reg clk,clear; module bcd(out,in,clk);

wire [3:0]out;//4 bit output input [3:0] in; //define 4 bit input in

counterbottomup cbu(out,clk,clear); input clk;

initial output [6:0] out;

clear =1;s reg [6:0] out=0; //initialize 7 bit output out

always #100 clear=!clear; always @ (posedge clk)

initial case(in)

clk=0; 4'd0:out=7'b1000000;

always #2 clk=!clk; 4'd1:out=7'b1111001;

endmodule 4'd2:out=7'b0100100;

4'd3:out=7'b0110000;

4'd4:out=7'b0011001;

4'd5:out=7'b0010010;

4'd6:out=7'b0000010;

4'd7:out=7'b1111000;

4'd8:out=7'b0000000;

4'd9:out=7'b0011000;

endcase

always @ (negedge clk) //o/p change at –ve //Mux

case(in) //edge of clk pulse module muxb(out,in1,in2);

4'd0:out=7'b1000000; output out;

4'd1:out=7'b1111001; input in1,in2;

4'd2:out=7'b0100100; reg out;

4'd3:out=7'b0110000; initial

4'd4:out=7'b0011001; out=0;

4'd5:out=7'b0010010; always

4'd6:out=7'b0000010; begin

4'd7:out=7'b1111000; #1 out=in1;

4'd8:out=7'b0000000; #1 out=in2;

4'd9:out=7'b0011000; end

endcase endmodule

endmodule module testmb(); //stimulus module

module testbcd(); //stimulus module wire out;

reg [3:0] in; reg in1,in2;

reg clk; muxb a(out,in1,in2);

wire [6:0] out; initial in1=0;

bcd tbcd(out,in,clk); initial in2=1;

initial clk=0; endmodule

always#2 clk=!clk;

initial in=0;

always#5 //Mux with case statement

in=in+1; module muxc(out,in0,in1,in2,in3,s0,s1);

endmodule input in0,in1,in2,in3,s0,s1;

output out;

//Bcd to 7 Segment reg out;

module bcd(out,in); always @ (in0,in1,in2,in3)

input [3:0] in; //4-bit input begin

output [6:0] out; //7-bit output case({s0,s1})

reg [6:0] out=0; 2'd0: out=in0;

reg com; 2'd1: out=in1;

initial com=1; 2'd2: out=in2;

always @ (in) 2'd3: out=in3;

case(in) endcase

4'd0:out=7'b1000000; end endmodule

4'd1:out=7'b1111001; module tmuxc(); //stimulus module

4'd2:out=7'b0100100; reg in0,in1,in2,in3,s0,s1;

4'd3:out=7'b0110000; wire out;

4'd4:out=7'b0011001; muxc mux(out,in0,in1,in2,in3,s0,s1);

4'd5:out=7'b0010010; initial in0=0;

4'd6:out=7'b0000010; always #5 in0=!in0;

4'd7:out=7'b1111000; initial in1=0;

4'd8:out=7'b0000000; always #10 in1=!in1;

4'd9:out=7'b0011000; initial in2=0;

endcase always #15 in2=!in2;

endmodule initial in3=0;

module testbcd(); //stimulus module always #20 in3=!in3;

reg [3:0] in; initial s0=0;

wire [6:0] out; always #1 s0=!s0;

bcd tbcd(out,in); initial s1=0;

initial in=0; always #2 s1=!s1;

always #1 endmodule

in=in+1;

endmodule

//Positive edge 8 bit UPDown counter //Negative edge 8 bit Up counter

module counter(out,clk,reset,select); module counter(out,clk);

input clk,reset,select; input clk;

output [7:0] out; output [7:0] out;

reg [7:0] out=0; reg [7:0] out=0;

always @ (posedge clk) always @ (negedge clk) //Negative edge

begin out=out+1; // up counter

if (reset==0&&select==0) endmodule

out=out+1; //up counter module testc8(); //stimulus module

else if(reset==0&&select==1) wire [7:0] out;

out=out-1; //down counter reg clk;

else counter c8(out,clk);

out=0; initial

end clk=0;

endmodule always

module testc8(); //stimulus module #1 clk=!clk;

wire [7:0] out; endmodule

reg clk,reset,select;

counter c8(out,clk,reset,select);

initial clk=0; //Positive edge 8 bit down counter

always module counter(out,clk);

#1 clk=!clk; input clk;

initial output [7:0] out;

begin reg [7:0] out=0;

reset=0; always @ (posedge clk)

#5 reset=1; out=out-1;

#10 reset=0; endmodule

end module testc8(); //stimulus module

initial begin wire [7:0] out;

select=0; reg clk;

#15 select=1; counter c8(out,clk);

#20 select=0; initial clk=0;

end always

endmodule #1 clk=!clk;

endmodule

//Positive edge 8 bit Upcounter

module counter(out,clk); //D_ff:

input clk; module dff(q,q0,d,clk,reset);

output [7:0] out; //8-bit output input d,clk,reset;

reg [7:0] out=0; output q,q0;

always @ (posedge clk) reg q,q0;

out=out+1; // up counter always @(negedge clk)

endmodule if (reset==0)

module testc8(); //stimulus module begin

wire [7:0] out; q=d;

reg clk; q0=!d;

counter c8(out,clk); end

initial else begin

clk=0; q=0;

always q0=1;

#1 clk=!clk; end

endmodule endmodule

initial

reset=0;

module tdff(); //stimulus module always #3 reset=!reset;

reg d,clk,reset; endmodule

wire q,q0;

dff dff0(q,q0,d,clk,reset);

initial

d=0;

always #2 d=!d; // traffic signals

initial module traffic(Ra,Ya,Ga,Rb,Yb,Gb,

clk=0; Rc,Yc,Gc,Rd,Yd,Gd);

always #1 clk=!clk; output reg Ra,Ya,Ga,Rb,Yb,Gb,Rc,

initial Yc,Gc,Rd,Yd,Gd;

reset=0; initial

always #5 reset=!reset; begin //initially all red lights ON

endmodule Ra=1; Rb=1; Rc=1; Rd=1;

Ya=0; Ga=0; Yb=0; Gb=0;

Yc=0; Gc=0; Yd=0; Gd=0;

//T_FF: end

module tff(q,q0,qt1,t,clk,reset); always

input t,clk,reset; begin

output q,q0,qt1; Ra<=#1 0;#1 Ya= 1;

reg q,q0,qt1; Ya<=#1 0;#1 Ga= 1;

initial Ga<=#10 0;#10 Ya=1;

qt1=0; Ra<=#1 1;#1 Ya=0;

always @(negedge clk) Rb<=#0 0;#0 Yb=1;

begin Yb<=#1 0;#1 Gb=1;

if(t==0&&reset==0) Gb<=#10 0;#10 Yb=1;

begin Rb<=#1 1;#1 Yb=0;

q=qt1; Rc<=#0 0;#0 Yc=1;

q0=!q; Yc<=#1 0;#1 Gc=1;

end Gc<=#10 0;#10 Yc=1;

else if(t==1&&reset==0) Rc<=#1 1;#1 Yc=0;

begin Rd<=#0 0;#0 Yd=1;

q=!qt1; Yd<=#1 0;#1 Gd=1;

q0=!q; Gd<=#10 0;#10 Yd=1;

end Rd<=#1 1;#1 Yd=0;

else end

begin endmodule

q=0;

q0=1; module testtraffic(); //stimulus module

end wire Ra,Ya,Ga,Rb,Yb,Gb,Rc,Yc,Gc,Rd,Yd,Gd;

qt1=q; traffic t (Ra,Ya,Ga,Rb,Yb,Gb,

end Rc,Yc,Gc,Rd,Yd,Gd);

endmodule endmodule

module ttff();

reg t,clk,reset;

wire q,q0,qt1;

tff tff0(q,q0,qt1,t,clk,reset);

initial

clk=0;

always #1 clk=!clk;

initial

t=0;

always #2 t=!t;

// traffic signals with control input

module traffic(Ra,Ya,Ga,Rb,Yb,Gb,

Rc,Yc,Gc,Rd,Yd,Gd,cont);

Output reg Ra,Ya,Ga,Rb,Yb,Gb,Rc,Yc,Gc,Rd,Yd,Gd;

input cont;

initial

begin //initially all red lights ON

Ra=1; Rb=1; Rc=1; Rd=1;

Ya=0; Ga=0; Yb=0; Gb=0;

Yc=0; Gc=0; Yd=0; Gd=0;

end

always

begin

Ra<=#1 0;#1 Ya= 1;

Ya<=#1 0;#1 Ga= 1;

if(cont==0)

begin Ga<=#10 0;#10 Ya=1; end

if(cont==1)

begin Ga<=#5 0;#5 Ya=1; end

Ra<=#1 1;#1 Ya=0;

Rb<=#0 0;#0 Yb=1;

Yb<=#1 0;#1 Gb=1;

if(cont==0)

begin Gb<=#10 0;#10 Yb=1; end

if(cont==1)

begin Gb<=#5 0;#5 Yb=1; end

Rb<=#1 1;#1 Yb=0;

Rc<=#0 0;#0 Yc=1;

Yc<=#1 0;#1 Gc=1;

if(cont==0)

begin Gc<=#10 0;#10 Yc=1; end

if(cont==1)

begin Gc<=#5 0;#5 Yc=1; end

Rc<=#1 1;#1 Yc=0;

Rd<=#0 0;#0 Yd=1;

Yd<=#1 0;#1 Gd=1;

if(cont==0)

begin Gd<=#10 0;#10 Yd=1; end

if(cont==1)

begin Gd<=#5 0;#5 Yd=1; end

Rd<=#1 1;#1 Yd=0;

end

endmodule

module testtraffic(); //stimulus module

wire Ra,Ya,Ga,Rb,Yb,Gb,Rc,Yc,Gc,Rd,Yd,Gd;

reg cont;

traffic

t(Ra,Ya,Ga,Rb,Yb,Gb,Rc,Yc,Gc,Rd,Yd,Gd,cont);

initial

cont=0;

always #50 cont=!cont;

endmodule

S-ar putea să vă placă și

- Solution Manual For Digital Systems Design Using VHDL 3rd Edition by RothDocument16 paginiSolution Manual For Digital Systems Design Using VHDL 3rd Edition by Rotha19397263914% (7)

- Digital Hardware Design Assignment: Verilog Codes and SimulationsDocument16 paginiDigital Hardware Design Assignment: Verilog Codes and SimulationsTeja Krishna Kopuri100% (2)

- Verilog Modules For Common Digital FunctionsDocument30 paginiVerilog Modules For Common Digital Functionssudarshan poojaryÎncă nu există evaluări

- 21BCT0093 VL2022230504083 Ast08Document15 pagini21BCT0093 VL2022230504083 Ast08Srinivasan UmaÎncă nu există evaluări

- Computer Architecture Lab 5aDocument9 paginiComputer Architecture Lab 5aHasan IqbalÎncă nu există evaluări

- Fpga Lab Reports 1-8 2Document17 paginiFpga Lab Reports 1-8 2Sohail AfridiÎncă nu există evaluări

- Verilog Mtech ProgramsDocument68 paginiVerilog Mtech ProgramsFarin FatimaÎncă nu există evaluări

- 04 - Verilog Codes For Basic Components (2021f)Document78 pagini04 - Verilog Codes For Basic Components (2021f)伍建瑋Încă nu există evaluări

- Lab 8Document3 paginiLab 8Guru priyaÎncă nu există evaluări

- Demux To ALUDocument13 paginiDemux To ALUkarry4galsÎncă nu există evaluări

- ASIC Design Lab ReportsDocument16 paginiASIC Design Lab ReportsNisar Ahmed RanaÎncă nu există evaluări

- Verilog Modules For Common Digital FunctionsDocument30 paginiVerilog Modules For Common Digital Functionselle868Încă nu există evaluări

- Abu Minhaj Farooqi 37560 Fpga Final ExamDocument20 paginiAbu Minhaj Farooqi 37560 Fpga Final ExamMinhaj FarooqiÎncă nu există evaluări

- Verilog HDL: ModuleDocument9 paginiVerilog HDL: ModuleAvinash ReddyÎncă nu există evaluări

- Interface Verilog CodeDocument21 paginiInterface Verilog CodeVishwanath B RajashekarÎncă nu există evaluări

- CounterDocument34 paginiCounterAishwarya GajendrulaÎncă nu există evaluări

- Advanced Computer Architechture Lab Assignment 3Document8 paginiAdvanced Computer Architechture Lab Assignment 3AbhishemÎncă nu există evaluări

- Problem 1.1: Let Be The Full 4-Bit Adder Described in The Following Verilog ModuleDocument5 paginiProblem 1.1: Let Be The Full 4-Bit Adder Described in The Following Verilog ModuleAna CărăvanÎncă nu există evaluări

- Verilog - Mux, Demux, Encoder, DecoderDocument9 paginiVerilog - Mux, Demux, Encoder, Decoderavinashmasani7Încă nu există evaluări

- Shift RegisterDocument9 paginiShift Registersilent nameÎncă nu există evaluări

- Verilog HDL: ModuleDocument9 paginiVerilog HDL: ModuleM Usman RiazÎncă nu există evaluări

- Vlsi - Digital - Lab ManualDocument23 paginiVlsi - Digital - Lab ManualVamsi KrishnanÎncă nu există evaluări

- Ver I Log ExamplesDocument22 paginiVer I Log ExamplesDayanand Gowda KrÎncă nu există evaluări

- Verified Interfacing ProgramDocument16 paginiVerified Interfacing ProgramVishwanath B RajashekarÎncă nu există evaluări

- Overview of Verilog HDL Design Session 2: BITS PilaniDocument22 paginiOverview of Verilog HDL Design Session 2: BITS PilaniShashwat KanhaiyaÎncă nu există evaluări

- Vlsi Exp 2 OutputsDocument6 paginiVlsi Exp 2 OutputsMANASA P (RA2011004010071)Încă nu există evaluări

- Deber 3Document9 paginiDeber 3Ale ZamÎncă nu există evaluări

- Lab 5 DSDDocument6 paginiLab 5 DSDRohaidÎncă nu există evaluări

- My First Program On D Flip FlopDocument39 paginiMy First Program On D Flip FlopAswinCvrnÎncă nu există evaluări

- Lab 12Document6 paginiLab 12ThoughtsÎncă nu există evaluări

- Nhom CT3 1 TuanNamHieuDuyDocument15 paginiNhom CT3 1 TuanNamHieuDuyPhan Duy LuanÎncă nu există evaluări

- Lab 1Document16 paginiLab 1vlsipranatiÎncă nu există evaluări

- 1.basic Gates and or Nor NandDocument32 pagini1.basic Gates and or Nor NandmrajkumarpatelÎncă nu există evaluări

- Behavioralmodeling CLC MultiplexersDocument5 paginiBehavioralmodeling CLC MultiplexersVenkata Appa Rao YempadaÎncă nu există evaluări

- Verilog Code For Fir FilterDocument58 paginiVerilog Code For Fir FilterKishore KumarÎncă nu există evaluări

- Digital Watch DSDDocument4 paginiDigital Watch DSDAwais ShamsÎncă nu există evaluări

- Birla Institute of Technology & Science, Pilani Lab Sheet - 2 Topic: Combinational Circuit ModelingDocument7 paginiBirla Institute of Technology & Science, Pilani Lab Sheet - 2 Topic: Combinational Circuit ModelingSATYAVRAT SHARMAÎncă nu există evaluări

- CSE460 Lab ReportDocument18 paginiCSE460 Lab ReportKISHANU ROY JOYÎncă nu există evaluări

- Fir Filter Verilog CodeDocument3 paginiFir Filter Verilog CodeSravan Kumar100% (1)

- VERILOG Code For Up and Down Counter of Varying FrequencyDocument11 paginiVERILOG Code For Up and Down Counter of Varying FrequencyKartik VermaÎncă nu există evaluări

- VerilogDocument6 paginiVerilogShaik IliyasÎncă nu există evaluări

- New Digital ExprimentDocument14 paginiNew Digital ExprimentSpoorthi BÎncă nu există evaluări

- Verilog Code For Parallel in Parallel Out Shift RegisterDocument3 paginiVerilog Code For Parallel in Parallel Out Shift Registermeaow88100% (1)

- Fall Semester 2022-2023 MVLD503P - Digital Design With FPGA Lab M. Tech VLSI Design School of Electronics Engineering Vellore Institute of TechnologyDocument5 paginiFall Semester 2022-2023 MVLD503P - Digital Design With FPGA Lab M. Tech VLSI Design School of Electronics Engineering Vellore Institute of TechnologyShrishty RawatÎncă nu există evaluări

- HDL Manual (18ecl58)Document20 paginiHDL Manual (18ecl58)lohith sÎncă nu există evaluări

- Vlsi Lab ProgramsDocument14 paginiVlsi Lab ProgramsThirumalai TrendchaserÎncă nu există evaluări

- Chapter - 05 - Sequential CircuitsDocument46 paginiChapter - 05 - Sequential Circuitskidgod2111Încă nu există evaluări

- Fix Me PlsDocument5 paginiFix Me PlsPhan TanÎncă nu există evaluări

- VLSI Design Lab EC-16203 Experiment 5Document6 paginiVLSI Design Lab EC-16203 Experiment 5Brajesh SainiÎncă nu există evaluări

- Mux4X1 Using Operators (Dataflow) : Test BenchDocument9 paginiMux4X1 Using Operators (Dataflow) : Test BenchAnonymous L3zAMqRlzUÎncă nu există evaluări

- 06 Verilog SynthDocument41 pagini06 Verilog SynthAlexandru OleinicÎncă nu există evaluări

- LAB 3 ReportDocument10 paginiLAB 3 ReportSuyash MishraÎncă nu există evaluări

- REPORT Assignment 2 HDMDocument36 paginiREPORT Assignment 2 HDMShaily GargÎncă nu există evaluări

- Digital Design Lab (Ec661) Experiment N0.:1: Brief Description of WorkDocument63 paginiDigital Design Lab (Ec661) Experiment N0.:1: Brief Description of WorkBhaskar KÎncă nu există evaluări

- 0 - Mec2019010 Report Assignment 2 HDM PDFDocument42 pagini0 - Mec2019010 Report Assignment 2 HDM PDFShaily GargÎncă nu există evaluări

- Code For All BlocksDocument4 paginiCode For All BlocksSabir AlieÎncă nu există evaluări

- Verilog Sequential Circuits CodeDocument14 paginiVerilog Sequential Circuits CodePVPPPÎncă nu există evaluări

- XlinkslibDocument8 paginiXlinkslibrudrarudraharaÎncă nu există evaluări

- Projects With Microcontrollers And PICCDe la EverandProjects With Microcontrollers And PICCEvaluare: 5 din 5 stele5/5 (1)

- ListDocument1 paginăListapi-3736661Încă nu există evaluări

- Assignment#2 2k2ee30,34,37,39Document9 paginiAssignment#2 2k2ee30,34,37,39api-3736661Încă nu există evaluări

- Circuit Diagram2nd CHDocument8 paginiCircuit Diagram2nd CHapi-3736661Încă nu există evaluări

- Assignment 1Document8 paginiAssignment 1api-3736661Încă nu există evaluări

- Assignment#3 (LASER)Document12 paginiAssignment#3 (LASER)api-3736661100% (2)

- Digital Electronics Lab Worksheet 1: Subject Code: 21ECH-101 AimDocument15 paginiDigital Electronics Lab Worksheet 1: Subject Code: 21ECH-101 AimRavinder singhÎncă nu există evaluări

- 3 Logic Gates and Logic CircuitsDocument2 pagini3 Logic Gates and Logic CircuitsMd. Samsul Arefin ShamimÎncă nu există evaluări

- DE Morgan's Theory and The Universal Gates: ObjectivesDocument14 paginiDE Morgan's Theory and The Universal Gates: ObjectivesSalam ShaikhÎncă nu există evaluări

- VLSI Lec 4Document54 paginiVLSI Lec 4nasim_majoka803Încă nu există evaluări

- Digital Electronics: CT 304N Unit-4 (Part:1) Flip Flops & Sequential Logic and CircuitsDocument39 paginiDigital Electronics: CT 304N Unit-4 (Part:1) Flip Flops & Sequential Logic and CircuitsLiyanshu patelÎncă nu există evaluări

- DW 4 BitDocument2 paginiDW 4 BitmirosehÎncă nu există evaluări

- IID2173 Digital Logic Design 41634 Final - Exam - QDocument8 paginiIID2173 Digital Logic Design 41634 Final - Exam - QswidyartoÎncă nu există evaluări

- Lab Experiment Design of Asynchronous and Synchronous CounterDocument6 paginiLab Experiment Design of Asynchronous and Synchronous CounterMani Bharathi40% (5)

- Arithmetic Circuits: Digital Electronics Bca Sem Ii JimsDocument57 paginiArithmetic Circuits: Digital Electronics Bca Sem Ii Jimsdinesh sharmaÎncă nu există evaluări

- Library IEEEDocument4 paginiLibrary IEEEAdeel HanifÎncă nu există evaluări

- Modified Low-Power and Area-Efficient Carry Select Adder Using D-LatchDocument8 paginiModified Low-Power and Area-Efficient Carry Select Adder Using D-LatchhemanthbbcÎncă nu există evaluări

- IJISAE Reversible LogicDocument10 paginiIJISAE Reversible LogicDhamini GowdaÎncă nu există evaluări

- EC8392Document2 paginiEC8392KISHORE SÎncă nu există evaluări

- Pseudo-Random Number Generator: Site WikipediaDocument5 paginiPseudo-Random Number Generator: Site WikipediaWah EedoÎncă nu există evaluări

- Adld l6Document117 paginiAdld l6prasanna prasannaÎncă nu există evaluări

- Digital System Design & Digital Ic ApplicationsDocument4 paginiDigital System Design & Digital Ic Applicationssaigdv1978Încă nu există evaluări

- Implementation of A Full Adder Circuit With A Decoder and Tow OR Gates.Document3 paginiImplementation of A Full Adder Circuit With A Decoder and Tow OR Gates.Mohayminul Al-Hamim100% (1)

- Logic Circuits and DesignDocument7 paginiLogic Circuits and DesignJayson CozÎncă nu există evaluări

- 06 Digital CircuitsDocument68 pagini06 Digital CircuitsasdsadasÎncă nu există evaluări

- Bugbook 0 PDFDocument174 paginiBugbook 0 PDFTony L HowardÎncă nu există evaluări

- 03 Digital Electronics BookletDocument40 pagini03 Digital Electronics BookletAbidinÎncă nu există evaluări

- Digital Logic Design Memory and Programmable Logic DevicesDocument25 paginiDigital Logic Design Memory and Programmable Logic Devicesnskprasad89Încă nu există evaluări

- DD Lab 4Document6 paginiDD Lab 4Martín Hurtado MongeÎncă nu există evaluări

- Digital Electronics Interview Questions: 1) What Is The Difference Between Latch and Flip-Flop?Document11 paginiDigital Electronics Interview Questions: 1) What Is The Difference Between Latch and Flip-Flop?yashuÎncă nu există evaluări

- Conversion of FlipDocument13 paginiConversion of FlipJohn Brix BalisterosÎncă nu există evaluări

- LAB 5-DIGITAL LOGIC SIMULATION (1112) FFFDocument28 paginiLAB 5-DIGITAL LOGIC SIMULATION (1112) FFFMuhd FaizÎncă nu există evaluări

- HSC ICT Sheet Chapter 03Document22 paginiHSC ICT Sheet Chapter 03Muhammad Masum Hosen100% (1)

- Chapter 10 Digital Integrated CircuitsDocument57 paginiChapter 10 Digital Integrated CircuitsMubeen NaeemÎncă nu există evaluări

- Esc201: Introducton To Electronics: Sequental CircuitsDocument26 paginiEsc201: Introducton To Electronics: Sequental CircuitsxdfweÎncă nu există evaluări