Documente Academic

Documente Profesional

Documente Cultură

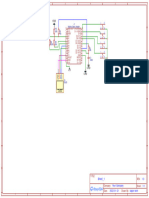

Jtag Cable

Încărcat de

api-3721578Descriere originală:

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Jtag Cable

Încărcat de

api-3721578Drepturi de autor:

Formate disponibile

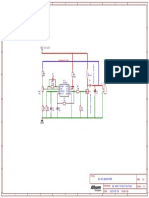

4 3 2 1

DB-25 Connector

and Cable JTAG Header

J3 R1 D2 D1 J2

15

VCC SENSE 1 VCC

100

D ERROR 1N5817 1N5817 D

(WHITE) FPGA Header

J1 Notes:

R13

R14 R8 1 VCC

U2

1K

C5

(1) All resistors

5.1K

100 74HC125 0.01UF 1/8W, 5%, SMT

J3 R2

13

DONE 3 2 J2 unless otherwise

100 2 noted.

SELECT 1 GND

GND

GND J1

(BROWN)

74HC125 2 GND (2) D6, BUSY, and PE

R9 J2

2 3 4

connected at the

TDO

1

100 DB25 end of data

U1 J1

GND

cable.

C1 4 D/P

100PF

C C

J3 R3 (3) U1 and U2 power:

6

PROG

300 GND VDD - pin 14

D4

(BLUE) GND - pin 7

U1

74HC125 J2

J3 R4 R10

2

DIN 5 6

5

300

TDI

D0 4 100

J1 U2

(RED)

C2 5 74HC125

100PF

DIN

J3 R5 5 6

5

CTRL

300 4

D3 GND

(GREEN)

U1 U2

74HC125 74HC125

J2

J3 R6 R11

3

CLK 9 8 3 9 8

300

TCK

B 100 B

D1 10 J1 10

(ORANGE) C3

3 CCLK

100PF U2

74HC125

12 11

GND

13

U1

74HC125 J2

J3 R7 R12 GND

4

TMS_IN 12 11

6

300

TMS

100

D2 13

(YELLOW) J1

C4

6 PROG

J3 100PF

20

GND GND See note (2)

GND

(BLACK) J3

J3

8

D6

A 25 A

J3

11

BUSY Title: JTAG/Parallel Download Cable

SHIELD

Comments:

J3

PC Chassis 12

PE

Ground Date:July 10, 1996 Ver:02

CGND Sheet Size: B Rev:

4 3 2 1

This information is being furnished as a service

Xilinx customers. Xilinx Inc. and its employees

shall not be held financially or legally

responsible for any usage or application

of this information.

S-ar putea să vă placă și

- Schematic Ardu Oscilloscope 2022-01-21 Kes1kt9bmpDocument1 paginăSchematic Ardu Oscilloscope 2022-01-21 Kes1kt9bmpinsincos administrativoÎncă nu există evaluări

- Tidr 261Document5 paginiTidr 261jay lowkeyÎncă nu există evaluări

- Sony SVF1441V6CW - DA0HKAMB6D0 - Quanta HKA - HKBDocument36 paginiSony SVF1441V6CW - DA0HKAMB6D0 - Quanta HKA - HKBLABORATORIO ACCOMPUTERÎncă nu există evaluări

- Schematic Ic Vipper 22a 2024-03-15Document1 paginăSchematic Ic Vipper 22a 2024-03-15Vansum NguyenÎncă nu există evaluări

- Manual Da Vida JamerDocument5 paginiManual Da Vida JamerVladimir CorreiaÎncă nu există evaluări

- L298 and L297 Based High Current Stepper Motor Driver With Mach 3 Interface 4Document2 paginiL298 and L297 Based High Current Stepper Motor Driver With Mach 3 Interface 4Ardiansyah Andry100% (1)

- Tesla Coil Driver Using SG3525 1 PDFDocument1 paginăTesla Coil Driver Using SG3525 1 PDFNguyen Phuoc HoÎncă nu există evaluări

- Esquema Eletrico-Ir BoardDocument2 paginiEsquema Eletrico-Ir BoardNelson Luís MarquesÎncă nu există evaluări

- Driver Motor Unipolar L297Document2 paginiDriver Motor Unipolar L297Hugo G.Încă nu există evaluări

- ADC 4-20 v1.2 EN PDFDocument1 paginăADC 4-20 v1.2 EN PDFFernando Vinícius G. MagroÎncă nu există evaluări

- ADC 4-20 v1.2 ENDocument1 paginăADC 4-20 v1.2 ENsaravananÎncă nu există evaluări

- ADC 4-20 v1.2 EN PDFDocument1 paginăADC 4-20 v1.2 EN PDFabhe prasetyaÎncă nu există evaluări

- ADC 4-20 v1.2 EN PDFDocument1 paginăADC 4-20 v1.2 EN PDFFernando Vinícius G. MagroÎncă nu există evaluări

- Schematic - X-LM 723 AKIM VE VOLTAJ AYARLI GÜÇ KAYNAĞI - 2024-01-01Document1 paginăSchematic - X-LM 723 AKIM VE VOLTAJ AYARLI GÜÇ KAYNAĞI - 2024-01-01brunonogueira33Încă nu există evaluări

- MT Siemens AdapterDocument1 paginăMT Siemens AdapterAlexandru FloricicăÎncă nu există evaluări

- 5volt: Dream 6800 Power SupplyDocument1 pagină5volt: Dream 6800 Power SupplyHernan BenitesÎncă nu există evaluări

- Schematic - DC DC BOOSTER - 2022-05-20Document1 paginăSchematic - DC DC BOOSTER - 2022-05-20Duzão Agnusrock Lembke BassÎncă nu există evaluări

- DC Motor Speed Controller 1 PDFDocument1 paginăDC Motor Speed Controller 1 PDFyukie heningÎncă nu există evaluări

- DC Motor Speed Controller 1Document1 paginăDC Motor Speed Controller 1Antonio BentoÎncă nu există evaluări

- DC-MOTOR-SPEED-CONTROLLER-1 Using 3525 Circuit of Oscillator PDFDocument1 paginăDC-MOTOR-SPEED-CONTROLLER-1 Using 3525 Circuit of Oscillator PDFChAmirShokatGujjar100% (2)

- DC Motor Speed Controller 1 PDFDocument1 paginăDC Motor Speed Controller 1 PDFRyn YahuFÎncă nu există evaluări

- EasyArc Zx7-200 Igbt Inverter WelderDocument1 paginăEasyArc Zx7-200 Igbt Inverter WelderSandeep Kumar67% (12)

- Half Bridge Driver Based On: C2 1uF/25V CN1 C5 10uF/25V D1 MBRS140T3G C3 220uF/63VDocument2 paginiHalf Bridge Driver Based On: C2 1uF/25V CN1 C5 10uF/25V D1 MBRS140T3G C3 220uF/63VratnaÎncă nu există evaluări

- Schematic Conversor Booster Vari├бvel, entrada 12V sa├нda 5 ├а 48V com CI UC3843 fvmlDocument1 paginăSchematic Conversor Booster Vari├бvel, entrada 12V sa├нda 5 ├а 48V com CI UC3843 fvmlMarcelo Rodrigues Barbosa100% (1)

- Regulated 5V power supplyDocument1 paginăRegulated 5V power supplyJuan CarlosÎncă nu există evaluări

- Circuit Access ControlDocument5 paginiCircuit Access Controlejim johnÎncă nu există evaluări

- Simple AND gate circuit diagramDocument1 paginăSimple AND gate circuit diagramMochammad PraditiaÎncă nu există evaluări

- H bridgeSG3525Document1 paginăH bridgeSG3525Saikat NandyÎncă nu există evaluări

- 1 19115823Document8 pagini1 19115823Netaji PatraÎncă nu există evaluări

- Rectification: AC Full Wave Rectification - LVWDocument1 paginăRectification: AC Full Wave Rectification - LVWalfred adukobirre adukobillaÎncă nu există evaluări

- Schematic - Turn A Multimeter Into A Tachometer - 2023-12-01Document1 paginăSchematic - Turn A Multimeter Into A Tachometer - 2023-12-01stellampuka5Încă nu există evaluări

- (New) Adjustable Voltage Power Supply 55 V - 20A High Power and Current - Automatic Fan On - OffDocument1 pagină(New) Adjustable Voltage Power Supply 55 V - 20A High Power and Current - Automatic Fan On - OffSek PyroÎncă nu există evaluări

- CH395Q测试底板Document1 paginăCH395Q测试底板kkkÎncă nu există evaluări

- Atmega328 Based Circuit Diagram of The ProjectDocument1 paginăAtmega328 Based Circuit Diagram of The ProjectKav Mav100% (2)

- LiPo Charger LS TP4056 SchematicDocument1 paginăLiPo Charger LS TP4056 SchematichidalgobÎncă nu există evaluări

- Schematic PrintsDocument1 paginăSchematic Printsthong lyÎncă nu există evaluări

- Bit3105 Push PullDocument1 paginăBit3105 Push PullServis SonicesÎncă nu există evaluări

- Arduino TempDocument1 paginăArduino TempSebastian LopezÎncă nu există evaluări

- Tait+Programming+Adapter T500and AllDocument1 paginăTait+Programming+Adapter T500and AllFloydiboy007Încă nu există evaluări

- D D D D D D D D D D: DescriptionDocument25 paginiD D D D D D D D D D: DescriptionSofywka SofaÎncă nu există evaluări

- OMF630Document3 paginiOMF630Nosdan LemosÎncă nu există evaluări

- SJ To Dyonics Power InterfaceDocument1 paginăSJ To Dyonics Power Interfacem_brodskyÎncă nu există evaluări

- Schematic - New 12V Battery Charger Circuit! - 2023-10-26Document1 paginăSchematic - New 12V Battery Charger Circuit! - 2023-10-26stellampuka5Încă nu există evaluări

- Schematic PrintsDocument1 paginăSchematic PrintsTNUT CK3Încă nu există evaluări

- Schematic - New Project - 2023-03-17Document1 paginăSchematic - New Project - 2023-03-17SATYAJEET KUMARÎncă nu există evaluări

- Schematic TP4056Document1 paginăSchematic TP4056Jose MiguelÎncă nu există evaluări

- Energizador YonusaDocument2 paginiEnergizador YonusaCarlos RoblesÎncă nu există evaluări

- Energizador Yonusa PDFDocument2 paginiEnergizador Yonusa PDFFrancisco MartinezÎncă nu există evaluări

- U1 U2 D12 C11 (1000U 16V) : Seccion de Poder +12V Seccion de Poder +5VDocument2 paginiU1 U2 D12 C11 (1000U 16V) : Seccion de Poder +12V Seccion de Poder +5VFrancisco MartinezÎncă nu există evaluări

- Dark Sensitive Switch 1Document2 paginiDark Sensitive Switch 1m7amadziadÎncă nu există evaluări

- Schematic - SW3518S Full Protocol Fast ChargingDocument1 paginăSchematic - SW3518S Full Protocol Fast CharginghaivivekÎncă nu există evaluări

- Schematic 1 - TransmitterDocument1 paginăSchematic 1 - TransmittermeghsnrynnÎncă nu există evaluări

- SCH - QD DRVR 13en.01Document1 paginăSCH - QD DRVR 13en.01fthsxÎncă nu există evaluări

- eMAX-LP1502 Installation GuideDocument20 paginieMAX-LP1502 Installation Guidetp.segarÎncă nu există evaluări

- AudioAnalyzerV2.0Document1 paginăAudioAnalyzerV2.0joxÎncă nu există evaluări

- LP1502 Intelligent Controller: 1. GeneralDocument9 paginiLP1502 Intelligent Controller: 1. GeneralLifarith Ortega MorenoÎncă nu există evaluări

- High Frequency Laser SoundDocument1 paginăHigh Frequency Laser SoundBunyamin AnilÎncă nu există evaluări

- Scard SerialDocument1 paginăScard SerialRayed Awad AlsahlaneeÎncă nu există evaluări

- C++ Tutorial For C UsersDocument48 paginiC++ Tutorial For C Usersapi-3721578100% (2)

- Efficient Programming Techniques For ARMDocument18 paginiEfficient Programming Techniques For ARMapi-3802111100% (1)

- Distribution of Marks For The Evaluation of Hardware Assignments (Total 40)Document5 paginiDistribution of Marks For The Evaluation of Hardware Assignments (Total 40)api-3721578Încă nu există evaluări

- RTOS KernelDocument73 paginiRTOS Kernelapi-3721578100% (4)

- Designing With The Advanced+ Boot Block Flash Memory ArchitectureDocument17 paginiDesigning With The Advanced+ Boot Block Flash Memory Architectureapi-3721578100% (1)

- Ti Jtag SeminarDocument7 paginiTi Jtag Seminarapi-3721578100% (1)

- Device DriversDocument120 paginiDevice Driversapi-3721578100% (2)

- ELF FormatDocument60 paginiELF Formatapi-3721578100% (3)

- Device DriverDocument114 paginiDevice Driverapi-3721578100% (2)

- !! Memory Management Algorithms and Implementation in C C++Document392 pagini!! Memory Management Algorithms and Implementation in C C++Anonymous gptX7l0ARXÎncă nu există evaluări

- uCOS ViewDocument48 paginiuCOS Viewapi-3721578Încă nu există evaluări

- The I2C Bus SpecificationsDocument46 paginiThe I2C Bus Specificationsshrivastav.ajay100% (14)

- Chapter 1Document39 paginiChapter 1api-3721578100% (2)

- C/OS-II Reference Manual: #DefineDocument128 paginiC/OS-II Reference Manual: #DefineVramesh4545Încă nu există evaluări

- JTAGDocument124 paginiJTAGshankar1505Încă nu există evaluări

- FT01Document4 paginiFT01api-3721578100% (1)

- Serial ProgrammingDocument177 paginiSerial ProgrammingkristofwoutersÎncă nu există evaluări

- TN06004 LPC2000 AdcDocument2 paginiTN06004 LPC2000 Adcapi-3721578100% (2)

- WP Arm 0103Document7 paginiWP Arm 0103api-3721578Încă nu există evaluări

- Interfacing The PC Serial Port RS232Document40 paginiInterfacing The PC Serial Port RS232Sneetsher Crispy100% (16)

- Compiler Design in CDocument55 paginiCompiler Design in Capi-3825528Încă nu există evaluări

- Interfacing A MAX6902 RTC With An 8051-Type Microcontroller: DescriptionDocument8 paginiInterfacing A MAX6902 RTC With An 8051-Type Microcontroller: Descriptionapi-3721578100% (3)

- Wriring A KernelDocument32 paginiWriring A Kernelapi-3701437100% (1)

- Tech Serial v1r0c0 PDFDocument15 paginiTech Serial v1r0c0 PDFsalehimohsen13514969100% (1)

- What Is Device DriverDocument8 paginiWhat Is Device Driverapi-26349602Încă nu există evaluări

- Real-Time and Embedded GuideDocument177 paginiReal-Time and Embedded Guideapi-3827556100% (3)

- 12 CanDocument39 pagini12 Canapi-3721578100% (2)

- CANopen protocol overview for CAN bus networksDocument23 paginiCANopen protocol overview for CAN bus networksvdevarajsaran100% (1)

- Introduction To The Controller Area Network (CAN) : Steve Corrigan HPLDocument17 paginiIntroduction To The Controller Area Network (CAN) : Steve Corrigan HPLRiyas VhÎncă nu există evaluări

- Chapter 3 - Cryptography and Encryption TechniquesDocument88 paginiChapter 3 - Cryptography and Encryption TechniquesEthio FanaÎncă nu există evaluări

- AIAG VDA DFMEA TrainingDocument68 paginiAIAG VDA DFMEA TrainingAtul SURVE100% (2)

- Interview Questions Topic Wise PDFDocument7 paginiInterview Questions Topic Wise PDFBalaji KommaÎncă nu există evaluări

- Pass Cisco 300-135 Exam With 100% Guarantee: Troubleshooting and Maintaining Cisco IP NetworksDocument26 paginiPass Cisco 300-135 Exam With 100% Guarantee: Troubleshooting and Maintaining Cisco IP NetworksTheodor AbahÎncă nu există evaluări

- CentOS 7 & 8 Self StudyDocument8 paginiCentOS 7 & 8 Self StudyLukki ArjunaÎncă nu există evaluări

- TC Electronic t2 Reverb Manual English PDFDocument28 paginiTC Electronic t2 Reverb Manual English PDFMobiwankÎncă nu există evaluări

- 1000 Ways To Pack The Bin PDFDocument50 pagini1000 Ways To Pack The Bin PDFafsarÎncă nu există evaluări

- Node - Js SQLite Tutorial - Connection & CRUD - TechiediariesDocument3 paginiNode - Js SQLite Tutorial - Connection & CRUD - TechiediariesMário Sésso JúniorÎncă nu există evaluări

- SketchUp 2016 HelpDocument175 paginiSketchUp 2016 Helpdimtcho jacksonÎncă nu există evaluări

- Posiflex OPOS Driver Installation V13xxDocument11 paginiPosiflex OPOS Driver Installation V13xxelbakri abd elhakimÎncă nu există evaluări

- Roadmap For Successful SAP Transformation: Ensuring Your SAP System Supports Your Corporate GoalsDocument1 paginăRoadmap For Successful SAP Transformation: Ensuring Your SAP System Supports Your Corporate Goalsleezro878Încă nu există evaluări

- Equotip 550 ManualDocument53 paginiEquotip 550 Manualmohamed ayadÎncă nu există evaluări

- Presentation On Longitudinal ResearchDocument5 paginiPresentation On Longitudinal ResearchAshish JaiswalÎncă nu există evaluări

- Leap Motion SeminarDocument10 paginiLeap Motion Seminarsunilms8464% (11)

- Ina Rahmawati Putri (D4TE3E) - Tugas AkhirDocument14 paginiIna Rahmawati Putri (D4TE3E) - Tugas AkhirInaÎncă nu există evaluări

- Excel Advanced CourseDocument4 paginiExcel Advanced CoursealilathÎncă nu există evaluări

- 8051 BasicsDocument29 pagini8051 Basicsapi-1995170783% (6)

- EXAMPLE-Penetration Testing Report v.1.0Document25 paginiEXAMPLE-Penetration Testing Report v.1.0Agrebi noor100% (1)

- ADA1 Notes F14Document376 paginiADA1 Notes F14Allan kimÎncă nu există evaluări

- Computer Science Notes On System SoftwareDocument52 paginiComputer Science Notes On System SoftwareYa'u NuhuÎncă nu există evaluări

- Dell Se2717h Monitor - User's Guide - en UsDocument51 paginiDell Se2717h Monitor - User's Guide - en UseruizalvaradoÎncă nu există evaluări

- AIAG B-10 Trading Partner Labels Implementation GuidlineDocument89 paginiAIAG B-10 Trading Partner Labels Implementation GuidlineTrexa Gyreue0% (1)

- Lista - Inteco (13may20) PDFDocument9 paginiLista - Inteco (13may20) PDFFabian MalagonÎncă nu există evaluări

- Zavrsni Rad - Konacna VerzijaDocument5 paginiZavrsni Rad - Konacna VerzijaNaida GolaćÎncă nu există evaluări

- Kinematics and Dynamics of Machinery Solution Manual 2-56-1Document1 paginăKinematics and Dynamics of Machinery Solution Manual 2-56-1GUSTAVO VINICIUS VIEIRA MELLOÎncă nu există evaluări

- Frequently Asked Questions MyABL LatestDocument11 paginiFrequently Asked Questions MyABL LatestTafseer HussainÎncă nu există evaluări

- List of Console Commands - Dota 2 WikiDocument82 paginiList of Console Commands - Dota 2 WikiOscar Taype Cayllahua50% (2)

- DRIVE CLiQ ConnectionDocument1 paginăDRIVE CLiQ ConnectionAnh HoàngÎncă nu există evaluări

- Rubrics and Outputs for TLE Grade 6 ExplorationDocument5 paginiRubrics and Outputs for TLE Grade 6 ExplorationRjPaglomutan Chén Hóng BāÎncă nu există evaluări

- Yaskawa Flyer j1000 Al 10-07-14Document2 paginiYaskawa Flyer j1000 Al 10-07-14Jorge PerezÎncă nu există evaluări