Documente Academic

Documente Profesional

Documente Cultură

LUPA 1300 2 Datasheet

Încărcat de

Muhammad MohsinDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

LUPA 1300 2 Datasheet

Încărcat de

Muhammad MohsinDrepturi de autor:

Formate disponibile

CYIL2SM1300AA

LUPA-1300-2 High speed CMOS Image Sensor

Features

n n

1280 x 1024 active pixels (SXGA resolution). 14 m2 square pixels [based on the high-fill factor active pixel sensor technology of FillFactory (US patent No. 6,225,670 and others))] On-chip 10-bit ADCs 12 LVDS serial outputs 500 fps frame rate Full snapshot shutter On-chip FPN correction Random programmable windowing 168-pin PGA package Sub sampling Programmable read out direction (X and Y)

n n n n n n n n n

achieved by setting multiple slopes. The sensor can also be read out non-destructively, that is, the pixel is reset and afterwards sampled and read out two or several times without additional resets in between. The initial reset level and all intermediate signals can be recorded. In this case, the reset level can simply be subtracted from the single level after a given integration period to perform Correlated Double Sampling (CDS) for very low noise applications. The Lupa1300-2 sensor has 12 LVDS high speed outputs which transfer the image data over longer distances, thus simplifying the surrounding system. The LVDS interface can receive high speed and wide bandwidth data signals when maintaining low noise and distortion. A special training mode allows the receiving system to synchronize the coming data stream when switching to master, slave, or triggered mode.

Functional Overview

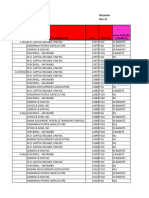

The Lupa1300-2 is a high speed CMOS image sensor with 1280 by 1024 pixels. The pixels are 14m x 14 m in size and all consist of high sensitivity 6T pipelined snapshot shutter capability (exposure during read out is possible). The image sensor has twelve 10-bit Digital LVDS outputs (serial). The image sensor also integrates a programmable offset and gain amplifier for each channel. Each channel runs at 61 MHz pixel rate which results in 500 fps frame rate at full resolution. Higher frame rates can be achieved by windowed or subsampled read out modes which are all programmable over the SPI interface. All internal exposure and read out timings are generated by an on-board sequencer. Extended optical dynamic range can be Table 1. Part Number Name CYIL2SM1300AA-GDCES 168-pin ceramic PGA CYIL2SC1300AA-GDCES 168-pin ceramic PGA

Note 1. The LUPA-1300-2 is also available in color or monochrome without the cover glass. Please contact Cypress for more information.

Package

Monochrome/Color Monochrome Color

Cypress Semiconductor Corporation Document Number: 001-24599 Rev. **

198 Champion Court

San Jose, CA 95134-1709 408-943-2600 Revised September 10, 2007

CYIL2SM1300AA

1. Overview

This document describes the interfacing and the driving of the LUPA-1300-2 image sensor. This SXGA resolution CMOS active pixel sensor features synchronous shutter and a maximal frame rate of 500 fps in full resolution. The read out speed can be boosted by means of sub sampling and windowed Region Of Interest (ROI) read out. High dynamic range scenes can be captured using the double and multiple slope functionality. User programmable row and column start and stop positions allow windowing. Sub sampling reduces resolution while maintaining the constant field of view and an increased frame rate. The Lupa1300-2 sensor has 12 LVDS high speed outputs which transfers the image data over longer distances thus simplifying the surrounding system. The LVDS interface can receive high speed and wide bandwidth data signals and maintain low noise and distortion. A special training mode allows the receiving system to synchronize the coming data stream when switching to master, slave, or triggered mode. The image sensor also integrates a programmable offset and gain amplifier for each channel. A 10-bit ADC converts the analog data to a 10-bit digital word stream. The sensor uses a 3-wire Serial-Parallel Interface (SPI). It requires only one master clock for operation up to 500 fps. It is housed in a 168-pin ceramic PGA package. The sensor is available in a Monochrome version or Bayer (RGB) patterned color filter array.

This data sheet allows the user to develop a camera system based on the described timing and interfacing.

1.1 Applications

n n

Machine vision Motion tracking Typical Value

Table 2. Specifications Parameter Active Pixels Pixel Size Pixel Type Shutter Type Master Clock Frame Rate Read out ADC resolution Sensitivity QE x FF 14m x 14 m

1280 (H) x 1024 (V) 6 Transistor Pixel Pipelined & Triggered Global Shutter 310 MHz 500fps @ 1.3Mpxl Windowed, flipped, mirrored, and subsampled read out possible 10-bit, on-chip 25 V/lux.s 35% (average 400-720 nm)

Full Well Charge 30.000 e-

2. Specifications

2.1 General Specifications

Table 3. General Specifications Parameter Pixel Architecture Pixel Size Resolution Pixel Rate Shutter Type Frame Rate Specifications 6 transistor pixel 14 m x 14 m 1280 x 1024 pixels 620 Mbps Pipelined or Triggered snapshot shutter 500 fps 12 serial LVDS outputs Integration during read out is possible Frame rate can be boosted by sub sampling and windowing. The pixel size and resolution result in a 17.92 mm x 14.34 mm optical active area. Remarks

2.2 Electro-optical Specifications

2.2.1 Overview Table 4. Electro-optical Specifications Parameter FPN PRNU Conversion gain Saturation charge Sensitivity Peak QE * FF Dark current (@ 21 C) 2% RMS 1% RMS 34 uV/e30.000 e7639 V/(J/m2) 40% 200 mV/s Page 2 of 42 @ 680nm @ output Specifications Remarks Column FPN corrected on-chip

Document Number: 001-24599 Rev. **

CYIL2SM1300AA

Parameter Noise electrons S/N ratio Parasitic sensitivity MTF Power dissipation 37e57.81 dB

Specifications

Remarks

< 1/10000 58% 1250 mW

2.2.2 Spectral Response Curve Figure 1. Spectral response of lupa-1300-2

Document Number: 001-24599 Rev. **

Page 3 of 42

CYIL2SM1300AA

2.2.3 Photo-voltaic Response Curve Figure 2. Photo-voltaic response of lupa-1300-2

2.3 Features and General Specifications

Table 5. General Specifications Feature Electronic shutter type Windowing (ROI) Sub-sampling Read out direction Extended dynamic range Programmable gain Programmable ADC offset Digital output Supply voltage VDD Logic levels Operational temperature range Interface Package Power dissipation Description Full snapshot shutter (integration during read out is possible). Randomly programmable ROI read out. Implemented as scanning of lines or columns from an uploaded position. Sub sampling is possible (X and Y direction) Sub-sampling pattern: X0X0X0X0 (mono) or XX00XX00 (color) Read out direction can be reversed in X and Y. Multiple slope (up to 90 dB optical dynamic range). range x1 to x4, in 6 steps using 3-bits programming. 256 steps (8-bit) 12 On-chip 10-bit serial LVDS outputs Nominal 2.5V (some supplies require 3.3V) 2.5V. -40C to 70C; with degradation of dark current. Serial-to Parallel Interface (SPI). 168-pin PGA 1250 mW

Document Number: 001-24599 Rev. **

Page 4 of 42

CYIL2SM1300AA

2.4 Electrical Specifications

Table 6. Absoulte Maximum Ratings Symbol VDD VIN VOUT IIO TL DC supply voltages DC input voltage DC output voltage DC current on any single pin Lead temperature (5 seconds soldering) Parameter Value -0.5 to 3.5 -0.5 to 3.5 -0.5 to 3.5 +/- 50 350 V V V mA C Unit

Note 2. Absolute Ratings are those values beyond which damage to the device may occur.

Table 7. Recommended Operating Conditions Symbol Parameter Vsamp Vres Vres_ds Vres_ts Vmem_l Vmem_h Vadc Vpix Vprech Vana Vdig Vbuf Vresab TA Power supply of the sampling circuitry. Power supply reset drivers Power supply of the dual slope Power supply of the triple slope Power supply of the pixels memory element (low level) Power supply of the pixels memory element (high level) Power supply of the on-chip ADCs Power supply of the pixel array Power supply of the precharge drivers Analog power supply Digital power supply Power supply of the on-board buffers Anti-blooming power supply Commercial operating temperature

Min

Typ 2.5 3.5 2.5 1.8 2.5 3.3 2.5 2.5 0.7 2.5 2.5 2.5 0.7

Max

Unit V V V V V V V V V V V V V

-40

30

70

Note 3. All parameters are characterized for DC conditions after thermal equilibrium has been established. 4. Unused inputs must always be tied to an appropriate logic level, for example, either VDD or GND. All cap_xxx pins must be connected to ground through a 100 nF capcitor. 5. This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is recomended that normal precautions be taken to avoid application of any voltages higher than the maximum rated voltages to this high impedance circuit.

Document Number: 001-24599 Rev. **

Page 5 of 42

CYIL2SM1300AA

3. Sensor Architecture

The floor plan of the architecture is shown in the following block diagram. The sensor consists of a pixel array, analog front end, data block, and LVDS transmitters and receivers. Separate modules for the SPI, clock division, and sequencer are also integrated. The image sensor of 1280 x 1024 pixels is read out in progressive scan. The architecture allows programmable addressing in the x-direction in steps of 24 pixels, and in the y-direction in steps of 1 pixel. The starting point of the address is uploadable by means of the Serial Parallel Interface (SPI). The AFE prepares the signal for the digital datablock where the data is multiplexed and prepared for the LVDS interface. Figure 3. Floor Plan of the Sensor

Image core 1280 x 1024

SPI

24 analog channels

31 Msps Clk X & Clk Y Analog front end Sequencer & Logic

24x 10-bit digital channels

31 Msps

31 MHz Clock Divider

Clk in

Local register

Data block 12x 10-bit digital channels 62 Msps 62 MHz

Clk o

LVDS TX and RX 310 MHz

12x LVDS outputs @ 620 Msps

Document Number: 001-24599 Rev. **

Page 6 of 42

CYIL2SM1300AA

3.1 The 6-T Pixel

To obtain the global shutter feature combined with a high sensitivity and good Parasitic Light Sensitivity (PLS), the pixel architecture given in the following figure is implemented. This pixel architecture is designed in a 14 x 14 m2 pixel pitch. The pixel is designed to meet the specifications as described in Table 1, Table 2, and Table 3. This architecture also allows the pipelined or triggered mode which is explained in Figure 4.

Figure 4. 6T-pixel Architecture

Vpix Vmem

Frame period = 5s + (1024 * (208ns + 1.34ns * 1280) = 1.97 ms => 506 fps The real speed of the LUPA-1300-2 is reduced to 500 fps due to overhead pixels being read out for black level calibration and other on-board features.

3.2.2 Windowing

Windowing can easily be achieved by the SPI. The starting point of the x- and y-address is uploadable, as well as the window size. The minimum step size in the x-direction is 24 pixels (only multiples of 24 can be chosen as start or stop addresses). The minimum step size in the y-direction is 1 line (every line can be addressed) in normal mode, and 2 lines in sub sampling mode. The sequencer section explains the use of the registers to achieve the desired ROI.

Table 9. Typical frame rates for 620 MHz clock Image resolu- Frame Frame read Comment tion (X * Y) rate (fps) out time (s)

Sample

Select

Reset

1280x1024 640 x 512 256 x 256

506 1816 6846

1970 550 146 sub sampling windowing

3.2 Frame Rate and Windowing

3.2.1 Frame Rate

3.3 Analog to Digital Converter

The sensor has 24 10-bit pipelined ADCs on board. The ADCs nominally operate at 31 Msamples/s.

Table 10. ADC Parameters Parameter Specification

The frame rate depends on the input clock, the frame Overhead Time (FOT), and the Row Overhead Time (ROT). The frame period can be calculated as follows: Frame period = FOT + Nr. Lines * (ROT + Nr. Pixels * clock period)

Table 8. Frame Rate Parameters Parameter Comment Clarification

Data rate Quantization DNL INL

31 Msamples/s 10 bit Typ. < 1 DN Typ. < 1 DN

FOT

Frame Overhead Programmable: Default 310 Time granularity clock cycles (5 us @620 MHz) Row Overhead Time Number of Lines read out each frame Number of pixels read out each line. Programmable: Default 13 granularity clock cycles (208 ns @620 MHz)

3.4 Programmable Gain Amplifiers

The PGAs amplify the signal before sending it to the ADCs. The amplification inside the PGA is controlled by one SPI setting: afemode [5:3]. Six gain steps can be selected by means of the afemode<3:0> register. Table 9 gives the six gain settings. The unity gain selection of the PGA is done by the default afemode<5:3> setting.

Table 11. Gain Settings afemode<5:3> Gain

ROT

Nr. Lines

Nr. Pixels

clock period 1/62 MHz = 16.1 Every channel works at 62 ns MHz 12 channels result in 744 MHz data rate Example: read out of the full resolution at nominal speed (744 MHz pixel rate = 1.34 ns):

000 001 010 011 100 101

1 1.5 2 2.25 3 4

Document Number: 001-24599 Rev. **

Page 7 of 42

CYIL2SM1300AA

3.5 Operation and Signaling

3.5.1 Power Supplies

Every module, on-chip column amplifier, output stage, digital module, driver, ADC, LVD, and so on, has its own power supply and ground. Off-chip the grounds can be combined, but not all power supplies may be combined. This results in several different power supplies, but this is required to reduce electrical cross-talk and to improve shielding, dynamic range, and output swing. On chip, the ground lines of every module are kept separate to improve shielding and electrical cross-talk between them. An overview of the supplies is given in the following table.

Table 12. Power Supplies Name DC Current Peak Current Typ Description

Vsamp Vres Vres_ds Vres_ts Vmem_l Vmem_h Vadc Vpix Vprech Vana Vdig Vbuf Vresab GNDlvds GNDadc GNDdig GNDana GNDpix GNDbuf

2 mA 0 mA 0 mA 0 mA 0 mA 0 mA 185 mA 26 mA 0 mA 6 mA 241 mA 40 mA 0 mA

2.5V 3.5V 2.5V 1.8V 2.5V 3.3V 2.5V 2.5V 0.7V 2.5V 2.5V 2.5V 0.7V 0V 0V 0V 0V 0V 0V

Power supply of the sampling circuitry Power supply reset drivers Power supply of the dual slope Power supply of the triple slope Power supply of the pixels memory element (low level) Power supply of the pixels memory element (high level) Power supply of the on-chip ADCs Power supply of the pixel array Power supply of the precharge drivers Analog power supply Digital power supply Power supply of the onboard buffers Anti-blooming power supply Ground of the LVDS module Ground of the ADC module Ground of the digital modules Ground of the analog drivers Ground of the pixel array Ground of the analog buffers

The maximum currents mentioned in Table 12 are peak currents. All power supplies must be able to deliver these maximum currents. It is important to notice that no power supply filtering on chip is implemented and that noise on these power supplies can contribute immediately to the noise on the signal. The voltage supplies Vpix, Vana and Vadc are especially important to be noise free.

Document Number: 001-24599 Rev. **

Page 8 of 42

CYIL2SM1300AA

3.5.2 Digital signals

Depending on the operation mode (master or slave), the pixel array of the image sensor requires different digital control signals. The function of each signal is shown in the following table.

Table 13. Overview of Digital Signals Signal Name IO Comments

MONITOR_1 MONITOR_2 MONITOR_3 INT_TIME_3 INT_TIME_2 INT_TIME_1 RESET_N CLK SPI_CS SPI_CLK SPI_IN SPI_OUT

Output Output Output Input Input Input Input Input Input Input Input Output

Output pin for integration timing, high during integration Output pin for dual slope integration timing, high during integration Output pin for triple slope integration timing, high during integration Integration pin triple slope Integration pin dual slope Integration pin first slope Sequencer reset. Active LOW System clock (620 MHz) SPI chip select Clock of the SPI Data line of the SPI. Serial input Data line of the SPI. Serial output

3.6 Synchronous Shutter

In a synchronous (snapshot or global) shutter light integration takes place on all pixels in parallel, although subsequent read out is sequential. Figure 5 shows the integration and read out sequence for the synchronous shutter. All pixels are light sensitive at the same period of time. The whole pixel core is reset simultaneously, and after the integration time, all pixel values are sampled together on the storage node inside each pixel. The pixel core is read out line by line after integration. Note that the integration and read out cycle can occur in parallel or in sequential mode (pipelined or triggered). (See Timing and Read out of the Image Sensor on page 18.)

Figure 5. Synchronous Shutter Operation

Line number COMMON SAMPLE&HOLD

Flash could occur here

COMMON RESET

Time axis Integration time Burst Readout time

Document Number: 001-24599 Rev. **

Page 9 of 42

CYIL2SM1300AA

3.7 Non-destructive Read Out (NDR)

Figure 6. Principle of Non-destructive Read Out

time

The sensor can also be read out in a nondestructive way. After a pixel is initially reset, it can be read multiple times, without resetting. The initial reset level and all intermediate signals can be recorded. High light levels saturate the pixels quickly, but a useful signal is obtained from the early samples. For low light levels, the later or latest samples must be used. Essentially, an active pixel array is read multiple times, and reset only once. The external system intelligence takes care of the interpretation of the data. The following table summarizes the advantages and disadvantages of nondestructive read out.

Table 14. Advantages and Disadvantages of Nondestructive Read Out Advantages Disadvantages

Low noise because it is true CDS.

System memory required to record the reset level and the intermediate samples.

High sensitivity as the conversion capacitance is kept Requires multiples readings of each pixel, thus higher data rather low. throughput. High dynamic range because the results include signals Requires system level digital calculations. for short and long integrations times. Note that the amount of samples to be taken with one initial reset is programmable in the nr_of_ndr_steps register. If nr_of_ndr_steps is 1, the sensor operates in the default way, namely one reset and one sample, that is. disable nondestructive read out mode. When nr_of_ndr_steps is 2, there is one reset and two samples, and so on. In case of Slave mode, nothing changes on the protocol of the signals int_time_*. The sequencer takes care of suppressing the internal reset signal to the pixel array.

3.8 Sequencer

The sequencer generates the complete internal timing of the pixel array and the read out. The timing can be controlled by the user through the SPI register settings. The sequencer operates on the same clock as the data block. This is a division by 10 of the input clock (internally divided). The following table shows a list of the internal registers with a short description. In the next section, the registers are explained more in detail.

Table 15. Internal Registers Block Register Name Address [6..0] Field Reset Value Description

Mbs (reserved)

Fix1 Fix2 Fix3 Fix4 Fix5

0 1 2 3 4

[7:0] [7:0] [7:0] [7:0] [7:0]

0x00 0xFF 0x00 0x00 0x08

Reserved, Fixed value Reserved, Fixed value Reserved, Fixed value Reserved, Fixed value Reserved, Fixed value

Document Number: 001-24599 Rev. **

Page 10 of 42

CYIL2SM1300AA

Block

Register Name

Address [6..0]

Field

Reset Value

Description

lvds clk divider

lvdsmain lvdspwd1 lvdspwd2

5 6 7

[3:0] [7:4] [7:0] [5:0] [6] [7]

0110 0 0x00 0 0 0 0x00 1000 111 000 0 0x00 0x00 0 1 0 000 0 1 1 0 1 0 0x00 0x00 1000 1000 1000 1000 1000 1000 1000 1000 0x20 0xC0 0x00 0 0 0 0 0x03

lvds trim clkadc phase power down channel 7:0 power down channel 13:8 power down all channels lvds test mode Reserved, Fixed value afe current biassing vrefp, vrefm settings Pga settings power down AFE power down adc_channel_2x 7 to 0 power down adc_channel_2x 11 to 8 power down bandgap and currrents external resistor external voltage reference bandgap trimming power down enable vrefcol regulator enable precharge regulator Disable internal bias for vprech Disable column load clkmain invert Reserved, Fixed value Reserved, Fixed value Bias colfpn DAC buffer Bias precharge regulator Bias pixel precharge level Bias column ota Bias column unip fast Bias column unip slow Bias column load Bias column precharge Reserved, Fixed value Reserved, Fixed value Reserved, Fixed value 1: Enables user upload of the dacvrefadc register value 0: keep default value Enable PRBS generation Reserved, Fixed value Reserved, Fixed value Training pattern inserted to sync LVDS receivers

Fix6 afe afebias afemode

8 9 10

[7:0] [3:0] [2:0] [5:3] [6]

afepwd1 afepwd2 biassing bandgap

11 12 13

[7:0] [3:0] [0] [1] [2] [5:3]

image core imcmodes 14

[0] [1] [2] [3] [4] [5]

Fix7 Fix8 imcbias1 imcbias2 imcbias3 Imcbias4 Data block Fix9 Fix10 dataconfig1

15 16 17 18 19 20 21 22 23

[7:0] [7:0] [3:0] [7:4] [3:0] [7:4] [3:0] [7:4] [3:0] [7:4] [7:0] [7:0] [1:0] [2] [3] [4] [5] [7:6]

Document Number: 001-24599 Rev. **

Page 11 of 42

CYIL2SM1300AA

Block

Register Name

Address [6..0]

Field

Reset Value

Description

dataconfig2 Fix11 dacvrefadc Fix12 Fix13 Fix14

24 25 26 27 28 29

[7:0] [7:0] [7:0] [7:0] [7:0] [7:0] [0] [1] [2] [3] [5:4]

0x2A 0 0x80 0x80

Training pattern inserted to sync LVDS receivers Reserved, Fixed value Input to DAC to set the offset at the input of the ADC (black calibration) Reserved, Fixed value Reserved, Fixed value Reserved, Fixed value

datachannel0_1 30

0 0 0 0 0x00 0x00 0 0 0 0 0x00 0x00 0 0 0 0 0x00 0x00 0 1

Bypass the data block Enables the FPN correction Overwrite incoming ADC data by the data in the testpat register Reserved, Fixed value Pattern inserted to generate a test image Pattern inserted to generate a test image Bypass the data block Enables the FPN correction Overwrite incoming ADC data by the data in the testpat register Reserved, fixed value Pattern inserted to generate a test image Pattern inserted to generate a test image Bypass the data block Enables the FPN correction Overwrite incoming ADC data by the data in the testpat register Reserved, Fixed value Pattern inserted to generate a test image Pattern inserted to generate a test image Enables image capture 1: Master mode, Integration timing is generated on-chip 0: Slave mode, integration timing is controlled off-chip through INT_TIME1, INT_TIME2 and INT_TIME3 pins 0: pipelined mode 1: triggered mode Enables(1)/Disables(0) Subsampling 1: color subsampling scheme: 1:1:0:0:1:1:0:0 0: B&W subsampling scheme: 1:0:1:0:1 Enable dual slope Enable Triple slope Enables continued row select (i.e. assert rowsel during pixel read out) Reserved, write 10001 to this register

datachannel0_2 31 datachannel1_1 32

[7:0] [0] [1] [2] [3] [5:4]

datachannel1_2 33 datachannel12_ 54 1

[7:0] [0] [1] [2] [3] [5:4]

datachannel12_ 55 2 sequencer seqmode1 56

[7:0] [0] [1]

[2] [3] [4] [5] [6] [7] seqmode2 57 [4:0]

0 0 0 0 0 0 10000

Document Number: 001-24599 Rev. **

Page 12 of 42

CYIL2SM1300AA

Block

Register Name

Address [6..0]

Field

Reset Value

Description

[6:5]

00

The number of active windows: 00: 1 window 01: 2 windows 10: 3 windows 11: 4 windows Enables the generation of the CRC10 on the data and sync channels Enable black level calibration Enable column fpn calibration Number of frames in non destructive read out: 000: invalid 001: one reset, one sample (default mode) 010: one reset, two samples Controls the granularity of the timer settings (only for those that have granularity selectable in the description): 0: expressed in number of lines 1: expressed in clock cycles (multiplied by 2**seqmode4 [3:0]) Allows syncing of events that happen outside of ROT to be delayed to the next ROT, to avoid image artefacts. Multiplier factor (=2**seqmode4[3:0]) for the timers when working in clockcycle mode Selects the source signals to put on the digital test pins: 00: integration time settings 01: EOS signals 10: frame sync signals 11: functional test mode reverse read out in X direction reverse read out in Y direction Y start address for window 1 Y start address for window 1 X start address for window 1 Y end address for window 1 Y end address for window 1 X width for window 1 Y start address for window 2 Y start address for window 2 X start address for window 2 Y end address for window 2 Y end address for window 2 X width for window 2 Y start address for window 3 Y start address for window 3 X start address for window 3 Y end address for window 3 Y end address for window 3 X width for window 3 Y start address for window 4

seqmode3

58

[0] [1] [2] [5:3]

1 0 0 001

[6]

[7] seqmode4 59 [3:0] [5:4]

0 0x00 0x0

[6] [7] window1_1 window1_2 window1_3 window1_4 window2_1 window2_2 window2_3 window2_4 window3_1 window3_2 window3_3 window3_4 window4_1 60 61 62 63 64 65 66 67 68 69 70 71 72 [7:0] [1:0] [7:2] [7:0] [1:0] [7:2] [7:0] [1:0] [7:2] [7:0] [1:0] [7:2] [7:0] [1:0] [7:2] [7:0] [1:0] [7:2] [7:0]

0 0 0x00 0x00 0x00 0xFF 0x3 0x36 0x00 0x00 0x00 0xFF 0x3 0x36 0x00 0x00 0x00 0xFF 0x3 0x36 0x00

Document Number: 001-24599 Rev. **

Page 13 of 42

CYIL2SM1300AA

Block

Register Name

Address [6..0]

Field

Reset Value

Description

window4_2 window4_3 window4_4 res_length1 res_length2 tint_timer1 tint_timer2 tint_ds_timer1 tint_ds_timer2 tint_ts_timer1 tint_ts_timer2 Fix15 Fix16 Fix17 Fix18 Fix19 Fix20 Fix21 Fix22 Fix23 Fix24 Fix25 Fix26 Fix27 Fix28 Fix29 Fix30 Fix31 Fix32 Fix33 Fix34

73 74 75 76 77 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104

[1:0] [7:2] [7:0] [1:0] [7:2] [7:0] [7:0] [7:0] [7:0] [7:0] [7:0] [1:0] [7:0] [1:0] [7:0] [7:0] [7:0] [1:0] [7:0] [1:0] [7:0] [7:0] [7:0] [1:0] [7:0] [7:0] [7:0] [7:0] [7:0] [7:0] [7:0] [7:0] [7:0] [7:0]

0x00 0x00 0xFF 0x3 0x36 0x02 0x00 0x01 0xFF 0x03 0x40 0x00 0x0C 0x00 0x06 0x0D 0x36 0x01 0x7C 0x00 0x03 0x09 0xF8 0x00 0x10 0x01 0 0 0 0 0 0 0 0

Y start address for window 4 X start address for window 4 Y end address for window 4 Y end address for window 4 X width for window 4 Length of pix_rst (granularity selectable) Length of pix_rst (granularity selectable) Length of resetds and resetts (granularity selectable) Length of integration time (granularity selectable) Length of integration time (granularity selectable) Length of DS integration time (granularity selectable) length of DS integration time (granularity selectable) length of TS integration time (granularity selectable) length of TS integration time (granularity selectable) Reserved, Fixed value Reserved, Fixed value Reserved, Fixed value Reserved, Fixed value Reserved, Fixed value Reserved, Fixed value Reserved, Fixed value Reserved, Fixed value Reserved, Fixed value Reserved, Fixed value Reserved, Fixed value Reserved, Fixed value Reserved, Fixed value Reserved, Fixed value Reserved, Fixed value Reserved, Fixed value Reserved, Fixed value Reserved, Fixed value Reserved, Fixed value Reserved, Fixed value, write 0x4 to it

res_dsts_length 78

3.8.1 Detailed Description of the Internal Registers

Cypress advises that the registers should only be changed during Idle Mode, i.e. ehen seqmode1[0] is 0. Uploaded registers have an immediate effect on the way the frame is read out. Parameters uploaded during read out may have an undesired effect on the data coming out of the imagers.

MBS block LVDS Clock divider block

The register block contains registers for testing and debugging of the sensor. All registers in this block must remain unchanged after startup.

This block controls division of the input clock for the LVDS transmitters or receivers. This block also allows shutting down one or all LVDS channels. For normal operation, this register block must remain untouched after startup.

Document Number: 001-24599 Rev. **

Page 14 of 42

CYIL2SM1300AA

AFE block

This register block contains registers to shut down ADC channels or the complete AFE block. This block also contains the register for setting the PGA gain: ......... AFE_mode[5:3]. See Electrical Specifications on page 5 for more details on the PGA settings.

Biasing block

Seqmode1[4]: This bit sets the type of subsampling scheme used when subsampling is enabled. '1': color (1:1:0:0:1:1:0:0:1) '0': B&W (1:0:1:0:1) Seqmode1[5]: This bit enables or disables the dual slope integration. Seqmode1[6]: This bit enables or disables the triple slope integration.

Seqmode2

This block contains several registers for setting biasing currents for the sensor. Default values after startup must remain unchanged for normal operation of the sensor.

Image core block

The seqmode2 register consists of only 2 sub-registers: Seqmode2[4:0]: Default value after startup is '10000' but this must be overwritten with the new value '10001' immediately after startup. Seqmode3[6:5]: These two bits set the number of active windows: '00': 1 window '01': 2 windows '10': 3 windows '11': 4 windows (max)

Seqmode3

The registers in this block have an impact on the pixel array itself. Default settings after startup must remain unchanged for normal operation of the image sensor.

Datablock block

The data block is positioned in between the analog front-end (output stage + ADCs) and the LVDS interface. It muxes the outputs of 2 ADCs to one LVDS block and performs some minor data handling: CRC calculation and insertion Training and test pattern generation The most important registers in this block are:

Dataconfig

The seqmode3 register consists of the following sub-registers: Seqmode3[0]: This bit enables or disables the CRC10 generation on the data and sync channels Seqmode3[1]: Enable or disable black level calibration Seqmode3[2]: Enable or disable column FPN correction Seqmode3[5:3]: Enabling or disabling, and setting number of frames grabbed in nondestructive read out mode '000': Invalid '001': Default, 1 reset, 1 sample '010': 1reset, 2 samples '011': 1 reset, 3 samples Seqmode3[6]: Controls the granularity of the timer settings (only for those that have 'granularity selectable' in the description), so that all timer settings can be set either in number of applied clock cycles, or in the number of 'read out lines'. '0': expressed in number of lines '1': expressed in clock cycles (multiplied by 2**seqmode4 [3:0]) Seqmode3[7]: Allows syncing of events that happen outside of ROT (Row Overhead Time, the time between read out of two rows) to be Seqmode3[7]: Allows syncing of events that happen outside of ROT (Row Overhead Time, the time between read out of two rows) to be delayed to the next ROT to avoid image artefacts.

The dataconfig1[7:6] and dataconfig2[7:0] registers inserts a training pattern in the LVDS channels to sync the LVDS receivers.

Datachannels

DatachannelX_1 and DatachannelX_2 (with X=0 to 12) are registers which allow the user to enable or disable the FPN correction (DatachannelX_1[1]), and generate a test pattern if necessary (datachannelX_1[5:4] and datachannelX_2[7:0]).

Sequencer block

The sequencer block group registers allow enabling or disabling of image sensor features which are driven by the on-board sequencer. This block consists of the following registers.

Seqmode1

The seqmode1 registers have the following sub-registers: Seqmode1[0]: Enable image capture, must be '1' during image acquisition. Seqmode1[1]: '1': In this default mode the integration timing is generated on-chip. '0': In this slave mode, the integration timing has to be generated through the int_time1, int_time2, and int_time3 pins. Seqmode1[2]: This bit allows pipelined (0) or triggered (1) mode. Seqmode1[3]: Enable (1) or disable (0) subsampling.

Document Number: 001-24599 Rev. **

Page 15 of 42

CYIL2SM1300AA

Seqmode4

X3_kernels (71, 6 bit)

This register consists of 4 sub-registers: Seqmode4[3:0]: Multiplier factor (=2**seqmode4[3:0]) for the timers when working in clockcycle mode. Seqmode4[5:4]: Selects which source signals to be put on the digital test pins (monitor1, monitor2 and monitor3 pins) "00": integration time settings "01": EOS signals "10": frame sync signals "11": functional test mode Seqmode4[6]: Enable (1) and disable (0) reverse X read out. Seqmode4[7]: Enable (1) and disable (0) reverse Y read out.

Y1_start (60 and 61, 10 bit)

This register sets the number of kernels or X width to be read out for window 3 (if enabled).

Y4_start (72 and 73, 10 bit)

These registers set the Y start address for window 4 (if enabled).

X4_start (73, 6bit)

This register sets the X start address for window 4 (if enabled).

Y4_end (74 and 75, 10 bit)

These registers set the Y end address for window 4 (if enabled).

X4_kernels (75, 6 bit)

This register sets the number of kernels or X width to be read out for window 4 (if enabled).

Res_length (76 and 77)

These registers set the Y start address for window 1 (default window).

X1_start (61, 6bit)

This register sets the X start address for window 1 (default window).

Y1_end (62 and 63, 10 bit)

This register sets the length of the internal pixel array reset (how long are all pixel reset simultaneously). This value can be expressed in 'number of lines' or in clock cycles (depends on seqmode3[6], see page 15).

Res_dsts_length

These registers set the Y end address for window 1 (default window).

X1_kernels (63, 6 bit)

This register sets the length of the internal dual and triple slope reset pulses when enabled. This value can be expressed in 'number of lines' or in clock cycles (depends on seqmode3[6], see page 15).

Tint_timer (79 and 80)

This register sets the number of kernels or X width to be read out for window 1 (default window).

Y2_start (64 and 65, 10 bit)

These registers set the Y start address for window 2 (if enabled).

X2_start (65, 6bit)

This register sets the length of the integration time. This value can be expressed in 'number of lines' or in clock cycles (depends on seqmode3[6], see page 15).

Tint_ds_timer (81 and 82)

This register sets the X start address for window 2 (if enabled).

Y2_end (66 and 67, 10 bit)

This register sets the length of the dual slope integration time. This value can be expressed in 'number of lines' or in clock cycles (depends on seqmode3[6], see page 15).

Tint_ts_timer (83 and 84)

These registers set the Y end address for window 2 (if enabled).

X2_kernels (67, 6 bit)

This register sets the number of kernels or X width to be read out for window 2 (if enabled).

Y3_start (68 and 69, 10 bit)

This register sets the length of the triple slope integration time. This value can be expressed in 'number of lines' or in clock cycles (depends on seqmode3[6], see page 15).

3.8.2 Data Interface (SPI)

These registers set the Y start address for window 3 (if enabled).

X3_start (69, 6bit)

This register sets the X start address for window 3 (if enabled).

Y3_end (70 and 71, 10 bit)

These registers set the Y end address for window 3 (if enabled)

The serial 4-wire interface (or Serial to Parallel Interface) uses a serial input or output to shift the data in or out the register buffer. The chip's configuration registers are accessed from the outside world through the SPI protocol. A 4-wire bus runs over the chip and connects the SPI IOs with the internal register blocks. The interface consists of: cs_n: chip select, when LOW the chip is selected clk: the spi clock in: master out, slave in, the serial input of the register. out: master in, slave out, the serial output of the register.

Document Number: 001-24599 Rev. **

Page 16 of 42

CYIL2SM1300AA

SPI protocol

The information on the data 'in' line is: a command bit C, indicating a write ('1') or a read ('0') access a 7-bit address a 8-bit data word (in case of a write access) The data 'out' line is mostly in High Z mode, except when a read request is performed. Data is always written on the bus on the falling edge of the clock, and sampled on the rising edge as can be seen in the following waveforms. This is valid both for the 'in' and 'out' bus. The system clock should be active in order to keep the SPI uploads stored on the chip. The SPI clock speed should be a factor 6 slower compared to the system clock.

Figure 7. Write Access (C='1')

The 'out' line is held to High Z. The data for the address A is transferred from the shift register to the active register bank (that is, sampled) on a rising edge of cs_n. Only the register block with address A can write its data on the 'out' bus. The data on 'in' is ignored.

Figure 8. Read Access (C='0')

Document Number: 001-24599 Rev. **

Page 17 of 42

CYIL2SM1300AA

4. Timing and Read out of the Image Sensor

The timing of the sensor consists of two parts. The first part is related with the exposure time and the control of the pixel. The second part is related with the read out of the image sensor. Integration and read out can be in parallel or triggered. In the first case, the integration time of frame I is ongoing during the read out of frame I-1. The following figure shows this parallel timing structure. The read out of every frame starts with a Frame Overhead Time (FOT), during which the analog value on the pixel diode is transferred to the pixel memory element. After this FOT, the sensor is read out line by line. The read out of every line starts with a Row Overhead Time (ROT), during which the pixel value is put on the column lines. Then the pixels are selected in groups of 24 (12 on rising edge, and 12 on the falling edge of the internal clock). So in total, 54 kernels of 12 pixels are read out per line. The internal timing is generated by the sequencer. The sequencer can operate in two modes: master mode and slave mode. In master mode all the internal timing is controlled by the sequencer, based on the SPI settings. In slave mode the integration timing is directly controlled over three pins, and the read out timing is still controlled by the sequencer. The selection between master and slave mode is done by the seqmode1[1] register of the SPI.

Figure 9. Global Read Out Timing (parallel)

Integration frame I+1 Integration frame I+2

Readout frame I Readout Lines FOT L1 L2 ...

Readout frame I+1

L480

ROT

K1

K2

... Readout Pixels

K160

4.1 Pipelined shutter

Integration and read out happen in parallel and are continuous. No interaction from the user is required except for starting and stopping the batch of image captures. Integration of frame N is always ongoing during read out of frame N-1. The read out of every frame starts with a Frame Overhead Time (FOT), during which the analog value on the pixel diode is transferred to the pixel memory element. After this FOT, the sensor is read out line per line. The read out of every line starts with a Row Overhead Time (ROT), during which the pixel value is put on the column lines. Then the pixels are muxed in the correct ADCs and after undergoing some processing sent to the LVDS output block.

Figure 10. Integration and Read Out for Pipelined Shutte

Int. Time Handling Readout Handling FOT

Reset N Exposure Time N Readout N-1 FOT

Reset N+1

Exposure Time Readout N

ROT Line Readout

In pipelined shutter mode, the user has the option to either program the reset and integration through the configuration interface and let the sequencer handle integration time automatically. This mode is called Master mode. The other option is to drive the integration time through an external pin. In that case, the sequencer is in Slave mode.

Document Number: 001-24599 Rev. **

Page 18 of 42

CYIL2SM1300AA

4.1.1 Programming the exposure time

In Master mode, the exposure time can be configured in two very distinct ways (controlled by register seqmode3[6]): #lines: Obvious, changing signals that control integration time are always changed during ROT to avoid any image artefacts. #clock cycles: Needs to be multiplied by (2**seqmode4[3:0]). When the counter expires, changes are put into effect immediately. Asserting the configuration signal (seqmode3[7]) forces delaying signal updates until the next ROT. Table 16 gives an overview of all user programmable timer settings and how they are interpreted by the hardware.

Table 16. User programmable timer settings Setting Granularity

reg_res_length reg_tint_timer reg_tint_ds_timer reg_tint_ts_timer reg_rot_timer reg_fot_timer reg_sel_pre_timer reg_precharge_timer reg_sample_timer reg_vmem_timer

Lines/cycles Lines/cycles Lines/cycles Lines/cycles clock cycles clock cycles clock cycles clock cycles clock cycles clock cycles

reg_delayed_rdt_timer Lines/cycles Note that the seqmode3[7] can also be used to sync the user signals in Slave mode. The behavior is exactly the same.

4.1.2 Master Mode

In Master mode the reset and exposure time is written in registers.

Figure 11. Integration and Image Read Out in Master mode

Care has to be taken that the added value of the registers res_length and tint_timer always exceeds the number of lines that are read out, because the sequencer samples a new image after integration is finished, without looking whether image read out was finished. Enlarging res_length to accommodate for this has no impact on image capture.

Document Number: 001-24599 Rev. **

Page 19 of 42

CYIL2SM1300AA

4.1.3 Slave Mode

In Slave mode the register values of res_length and tint_timer are ignored. The integration time is controlled by the int_time pin. The relationship between the input pin and the integration time is illustrated in the following figure. As soon as the input pin int_time is asserted, the pixel array goes out of reset and exposure can start. When int_time goes low again, the desired exposure time is reached, the image is sampled and read out can start.

Figure 12. Integration and Image Read Out in Slave mode

Changing a pixel's reset level during line read out might result in image artefacts during a small transient period. Therefore, it is advised to only change the value of int_time during ROT.

4.2 Triggered shutter

The two main differences with the pipelined shutter mode are: Upon every user action, 1 single image is read. Integration (and read out) is under control of the user through pin int_time.

This means that for every frame, manual intervention from the user is required. The pixel array is kept in reset state until the user asserts the int_time input. Just like the pipelined shutter mode, there is a master mode in which the sequencer has control of the integration time or a slave mode in which the user can define it.

Figure 13. Integration and Read Out for Triggered Shutter

int_time1 Int. Time Handling Readout Handling ROT Line Readout Reset Exposure Time N Reset Exposure Time N Reset

Read outN+1

FOT

Readout N

FOT

N+1

The possible applications for this triggered shutter mode are: Synchronize external flash with exposure Apply extremely long integration times (only in slave mode)

Document Number: 001-24599 Rev. **

Page 20 of 42

CYIL2SM1300AA

4.2.1 Master Mode

4.2.2 Slave Mode

In this mode, a rising edge on int_time1 pin is used to trigger the start of integration and read out. The tint_timer defines the integration time no matter how long the input pin int_time1 is asserted. Automatically after the integration time counter runs out, the FOT starts and image read out is done. During read out, the image array is kept in reset. A request for a new frame is started again when a new rising edge on int_time is detected. The time of the falling edge is of no importance in this mode.

Integration time control is identical to the pipelined shutter slave mode. The int_time1 pin controls the start of integration. The moment that int_time gets deasserted, the FOT starts (analog value on the pixel diode is transferred to the pixel memory element). Only at that time, image read out can start (similar as for the pipelined read out). During read out the image array is kept in reset. A request for a new frame is started again when int_time goes high again.

4.3 Windowing

A fully configurable window can be selected for read out.

Figure 14. Window selected for Read Out

y start

1024 pixels y end

x kernel

x start 1280 pixels

The parameters to configure this window are: x_start: The sensor reads out 24 pixels in one single clock cycle. The granularity of configuring the X start position is also 24. Every value written to the windowX_2 register must be multiplied by 24 to find the corresponding column in the pixel array. x_kernels: The amount of columns that is read out (x_kernels*24 in full frame mode) In subsampling mode x_kernels*48 represents the number of columns over which subsampling is done. The x_kernels value needs to be written to the windowX_4 register. y_start: The starting line of the read out window, granularity of 1. Watch out: in subsample mode, the correct y_start position must

be uploaded (exact value depends on color or B/W subsampling mode). This value needs to be written to the windowX_1 and windowx_2 register. y_end: The end line of the read out window, granularity of 1. In all cases (even in reverse scan) y_end shall be larger than y_start. Watch out: in subsample mode, the correct y_end position must be uploaded (exact value depends on color or B/W subsampling mode) This value needs to be written to the windowX_3 and windowX_4 register. In case of windowing, the effective read out time is smaller than in full frame mode as only the relevant part of the image array is accessed. Therefore, it is possible to achieve higher frame rates.

Document Number: 001-24599 Rev. **

Page 21 of 42

CYIL2SM1300AA

4.4 Reverse Scan

Reverse scanning is supported in the X&Y direction. Line 0 (first line on the output) is the top line in normal mode and the bottom line in reverse scanning as shown in the following figure. So line numbers are always incrementing. When reverse scanning in X, the operation is analogous. To enable reverse read out in X and Y the seqmode4[6:7] bits need to be set. Also, the Y_start and X_start addresses must be changed to the new starting address.

Figure 15. Normal and Reverse Scanning in Y

4.5 Multiple windows

The sequencer supports the read out of four different windows, randomly positioned over the pixel array. The images are read out sequentially, that is, before starting reading out window 2, window 1 is entirely finished, even if both windows show some overlap. After that, windows 3 and 4 are read out. The user is capable of configuring how many windows are used in the application (1 up to 4). The following figure shows an example on how two windows can be spread over the image array, and how they are configured.

Figure 16. Multiple Windows Read from the same Pixel Array

Document Number: 001-24599 Rev. **

Page 22 of 42

CYIL2SM1300AA

The following figure shows the sequence how the integration and read out is done for multiple windows. Handling of integration time is identical to the single window mode (except in this case the maximal integration time is equal to the sum of the y_widths of the two windows). read out starts with a FOT that is also similar to single window mode. After the FOT, first all lines of window 1 are read, followed by the lines of window 2.

Figure 17. Exposure and Read Out of Multiple Windows

Int. Time Handling Readout Handling Reset N Exposure Time N Readout FOT N-1 Window 2 Window 1 ROT Line Readout Window 1 Line Readout Window 2 Window 2 Reset N+1 Exposure Time

FOT

Readout N-1

Readout N

Readout N

If the X size of the windows are not identical, the integration time in function of the number of lines read presents multiple slopes (proportional to the X size of these windows). Because this can cause confusion when programming the integration time, it could be easier to configure all timer registers using the clock cycle configuration instead of the 'line' configuration.

4.6 Multiple slopes

Dynamic range can be extended by the multiple slope capabilities of the sensor. The four colored lines in Figure 18 represent analog signals of the photodiode of 4 pixels, which decrease as a result of exposure. The slope is determined by the amount of light at each pixel (the more light, the steeper the slope). When the pixels reach the saturation level, the analog does not change despite further exposure. Without the multiple slope capabilities,

Figure 18. Multiple Slopes

the pixels p3 and p4 are saturated before the end of the exposure time, and no signal is received. However, when using multiple slopes, the analog signal is reset to a 2nd or 3th reset level (lower than the original one) before the end of the integration time. The analog signal starts decreasing with the same slope as before, and pixels that were saturated before could end up non saturated at read out time. For pixels that never reach any of the reset levels (for example, p1 and p2) there is absolutely no difference between single and multiple slope operation. By choosing the time stamps of the Double and Triple slope resets wisely (typical at 90% and 99% of the integration, configurable by the user), it is possible to have a non saturated pixel value even for pixels receiving a huge amount of light.

Document Number: 001-24599 Rev. **

Page 23 of 42

CYIL2SM1300AA

The Reset Levels are configurable either through the configuration interface (digital values going to a DAC, generating a voltage reference) or through external (power) pins. In Master mode, the time stamps of the double and triple slope resets are configured in a similar way as the exposure time. They are enabled through the registers seqmode1[5] and seqmode1[6] and their values are expressed in line or clock cycles in the registers reg_tint_ds_timer and reg_tint_ts_timer.

Figure 19. Triple Slope Timing in Master mode

In Slave mode, the values of res_length, tint_timer, tint_DS_timer, and tint_TS_timer in the configuration registers are ignored. The user has full control through the pins int_time, int_time_ds, and int_time_ts.

Figure 20. Triple Slope Timing in Slave Mode

It is the user's responsibility to configure the multiple slope parameters for the application, and interpret the pixel data accordingly.

Document Number: 001-24599 Rev. **

Page 24 of 42

CYIL2SM1300AA

4.7 Column FPN correction

The column FPN of the sensor can be improved by means of offset correction of the columns. At the start of every frame, before read out of the actual lines is done, a fixed voltage is applied at the columns and the these values are read out like a real data line. Inside the data block, the 'pixel' data for that line is stored in an on-chip FPN memory. When the correction is enabled, the incoming pixel data has the corresponding FPN value subtracted. This FPN correction has to be enabled for every output separately. The following registers are used to configure the correction: correction. The images shown are amplified 5 times.

datachannelX_1 with X from 0 to 11: field [1] of these registers enables the offset corrections of the specific output channel. Note: Do not change the settings of datachannel12_1. This channel contains not pixel data, but synchronization data. If fpn correction is enabled on this channel, the synchronization data becomes corrupt. seqmode3, field[2] must be '1'. It enables the generation of the line of reference voltages at the columns. The following images show the effect of enabling the column FPN

Figure 21. Dark image without FPN correction (5 x amplified)

Document Number: 001-24599 Rev. **

Page 25 of 42

CYIL2SM1300AA

Figure 22. Dark image with FPN correction enabled (5x amplified)

Document Number: 001-24599 Rev. **

Page 26 of 42

CYIL2SM1300AA

4.8 Image Format + Read Out Protocol

The active area, as read out by the sequencer in full frame mode, looks like the following figure. Before starting the read out of the actual pixels, one dummy line is read to allow column FPN calibration. A reference voltage is applied to the columns and the entire line is read just as if real pixel values are put on the columns. Pixels are always read in multiples of 24 (one value to every channel in the AFE). The last time slot contains not only valid pixels, but also 2 dummy columns, 6 grey columns, and 8 black columns.

Figure 23. Sensor Read Out Format

Document Number: 001-24599 Rev. **

Page 27 of 42

CYIL2SM1300AA

The following sections each list what the output looks like (data + synchronization codes) in several relevant configurations. Twelve of the output channels are connected to the 24 ADCs and take care of handling the data. One additional channel contains all the synchronization codes for the receiver, indicating, for example, the start of a frame, the end of a frame, whether the data channels contain data, CRC, a training pattern, and so on. The sequencer takes care of providing the synchronization channel with the correct synchronization or protocol signals as shown in the following figure. The synchronization codes can be found in Table 17. Please note that a FS serves as LS as well, just like a FE also serves as a LE.

Figure 24. Data + Sync Channel Overview

Table 17. Synchronization codes Sync code Abbrev

10-bit code

Input #

Frame Start Line Start Frame End Line End Grey/Black Cols CRC FPN stored values Normal Data Training Pattern

FS LS FE LE GBC CRC FPN D T

0x059 0x056 0x05A 0x055 0x0A9 0x0A6 0x13C 0x193 T

1 1 1/2 1/2 2 1 1+2 1/2 1/2

Document Number: 001-24599 Rev. **

Page 28 of 42

CYIL2SM1300AA

4.8.1 Full Frame Mode

In this operation mode, the entire sensor as shown in Figure 23 on page 27 is read out. Figure 25 shows the internal state of the sequencer, and the behavior of the data and sync channels (overview and detail of one line).

Figure 25. Full Frame mode Read Out

Sequencer internal state Data channel Sync Channel

FOT ROT

black

ROT line 0

ROT

line 1

line 1022

ROT

line 1023

Data Channel Sync Channel

T T FS D D

L E

GB CR C C

timeslot timeslot timeslot 1 2 3

timeslot timeslot CRC 53 54 timeslot

Document Number: 001-24599 Rev. **

Page 29 of 42

CYIL2SM1300AA

The following table gives a detailed overview of the remapping of one full row read out.

Table 18. Remapping scheme for 1 row timeslot ch0 ch1 ch2 ch3

ch4 8 9 39 38 56 57 87 86 104 105 135 134 152 153 183 182 200 201 231 230 248 249 279 278 ... ... 1256 1257 1287 1286

ch5 10 11 37 36 58 59 85 84 106 107 133 132 154 155 181 180 202 203 229 228 250 251 277 276 ... ... 1258 1259 1285 1284

ch6 12 13 35 34 60 61 83 82 108 109 131 130 156 157 179 178 204 205 227 226 252 253 275 274 ... ... 1260 1261 1283 1282

ch7 14 15 33 32 62 63 81 80 110 111 129 128 158 159 177 176 206 207 225 224 254 255 273 272 ... ... 1262 1263 1281 1280

ch8 16 17 31 30 64 65 79 78 112 113 127 126 160 161 175 174 208 209 223 222 256 257 271 270 ... ... 1264 1265 1279 1278

ch9 18 19 29 28 66 67 77 76 114 115 125 124 162 163 173 172 210 211 221 220 258 259 269 268 ... ... 1266 1267 1277 1276

ch10 20 21 27 26 68 69 75 74 116 117 123 122 164 165 171 170 212 213 219 218 260 261 267 266 ... ... 1268 1269 1275 1274

ch11 22 23 25 24 70 71 73 72 118 119 121 120 166 167 169 168 214 215 217 216 262 263 265 264 ... ... 1270 1271 1273 1272

1a 1b 2a 2b 3a 3b 4a 4b 5a 5b 6a 6b 7a 7b 8a 8b 9a 9b 10a 10b 11a 11b 12a 12b ... ... 53a 53b 54a 54b CRC

0 1 47 46 48 49 95 94 96 97 143 142 144 145 191 190 192 193 239 238 240 241 287 286 ... ... 1248 1249 1295 1294

2 3 45 44 50 51 93 92 98 99 141 140 146 147 189 188 194 195 237 236 242 243 285 284 ... ... 1250 1251 1293 1292

4 5 43 42 52 53 91 90 100 101 139 138 148 149 187 186 196 197 235 234 244 245 283 282 ... ... 1252 1253 1291 1290

6 7 41 40 54 55 89 88 102 103 137 136 150 151 185 184 198 199 233 232 246 247 281 280 ... ... 1254 1255 1289 1288

Document Number: 001-24599 Rev. **

Page 30 of 42

CYIL2SM1300AA

4.8.2 Single Window Mode containing timeslot 54

In this operation mode, only part of the sensor is read out, as shown by the shaded area in Figure 26. A clear distinction is made with the single window mode not containing timeslot 54 as the output synchronization protocol is slightly different.

Figure 26. Single Window containing Timeslot 54

The following figure shows the internal state of the sequencer, and the behavior of the data and sync channels (overview and detail of one line) for this window mode.

Figure 27. Waveform for Single Window containing Timeslot 54

FOT ROT Sequencer internal state Data Channel Sync Channel black ROT line Ys

ROT Line Ys+1 ROTline

Ye

Data Channel Sync Channel

T T L D S D D D D F GB CR E C C

T T

timeslot timeslot X X+1

timeslot timeslot CRC 53 54 timeslot

Document Number: 001-24599 Rev. **

Page 31 of 42

CYIL2SM1300AA

4.8.3 Single Window Mode NOT containing timeslot 54

In this operation mode, only part of the sensor is read out, as shown in Figure 28. Although the window is defined as not containing any data from timeslot 54, it is read out to provide the information on grey and black columns to both the black level calibration algorithm and the user. This results in some minor differences between the waveforms from Figure 27 on page 31 and Figure 29 on page 32.

Figure 28. Single window NOT containing timeslot 54

Figure 29 shows the internal state of the sequencer, and the behavior of the data and sync channels (overview and detail of one line) for this window mode.

Figure 29. Waveform for single window NOT containing timeslot 54

Sequencer internal state Data Channel Sync Channel

FOT ROT

black

ROT line Ys

ROT

line Ys+1

ROTline

Ye

T T L S D D D D D D L E T GB CR C C

T T

timeslot timeslot Xstart

timeslot timeslot timeslot CRC Xend-1 Xend 54 timeslot

Note that the dummy black line is read completely. Reading out multiple windows is in no way different from combining the windowed modes in Sections Single Window Mode containing timeslot 54 on page 31 and Single Window Mode NOT containing timeslot 54 on page 32. The dummy black line again spans the entire width of the sensor and is processed only once, before all configured windows are read, and is independent of the window sizes.

Document Number: 001-24599 Rev. **

Page 32 of 42

CYIL2SM1300AA

5. Pinlist

Figure 30. Pin Placement Layout (Top View)

1 B D E F G H J K L M N P Q R S *

10

11

12

13

14 96 95 94

15 93 92 91

16 90 89 88

17 87 86 85

18 84 83 82

19 81 80 79

20 78 77 76

21 75 74 73

22 72 71 70

23 24 69 65 68 * 67 66

A 134 130 127 124 121 118 115 112 109 106 103 100 99 131 128 125 122 119 116 113 110 107 104 101 98 C 133 132 129 126 123 120 117 114 111 108 105 102 97

TOP VIEW

T 135 139 140 137 145 U 136 144 141 138 146 V 149 147 142 W 150 148 143 * * 1 2

* * 3 4

5 8 9 10

7 6 11 12

* * 13 14

17 20 15 16

19 18 21 22

* * 23 24

* * 25 26

31 30 27 28

29 32 33 34

* * 35 36

43 42 37 38

41 44 39 40

* * 45 46

54 53 47 48

62 61 * *

60 55 52 51

59 64 58 63 57 50 56 49

Document Number: 001-24599 Rev. **

Page 33 of 42

CYIL2SM1300AA

Table 19. Pin List nr pin name

Type

Direction

Description

Position

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43

clkoutp clkoutn chp[0] chn[0] gndlvds gndadc vddadc vddlvds chp[1] chn[1] chp[2] chn[2] chp[3] chn[3] chp[4] chn[4] gndlvds gndadc vddadc vddlvds chp[5] chn[5] chp[6] chn[6] chp[7] chn[7] chp[8] chn[8] gndlvds gndadc vddadc vddlvds chp[9] chn[9] chp[10] chn[10] chp[11] chn[11] n/a n/a gndlvds gndadc vddadc

LVDS LVDS LVDS LVDS Supply Supply Supply Supply LVDS LVDS LVDS LVDS LVDS LVDS LVDS LVDS Supply Supply Supply Supply LVDS LVDS LVDS LVDS LVDS LVDS LVDS LVDS Supply Supply Supply Supply LVDS LVDS LVDS LVDS LVDS LVDS

O O O O IO IO IO IO O O O O O O O O IO IO IO IO O O O O O O O O IO IO IO IO O O O O O O

p clk output channel n clk output channel p output channel [0] n output channel [0] LVDS ground ADC gound ADC power LVDS power p output channel [1] n output channel [1] p output channel [2] n output channel [2] p output channel [3] n output channel [3] p output channel [4] n output channel [4] LVDS ground ADC gound ADC power LVDS power p output channel [5] n output channel [5] p output channel [6] n output channel [6] p output channel [7] n output channel [7] p output channel [8] n output channel [8] LVDS ground ADC gound ADC power LVDS power p output channel [9] n output channel [9] p output channel [10] n output channel [10] p output channel [11] n output channel [11] not assigned not assigned

V5 W5 V6 W6 T7 U8 T8 U7 V7 W7 V8 W8 V9 W9 V10 W10 T10 U11 T11 U10 V11 W11 V12 W12 V13 W13 V14 W14 T15 U14 T14 U15 V15 W15 V16 W16 V17 W17 V18 W18 T18 U17 T17

Supply Supply Supply

IO IO IO

LVDS ground ADC gound ADC power

Document Number: 001-24599 Rev. **

Page 34 of 42

CYIL2SM1300AA

nr

pin name

Type

Direction

Description

Position

44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84

vddlvds clkinp clkinn syncp syncn gnddig vdddig cap_vrefm cap_vrefp gndadc vddadc gnddig gndbuf vddbuf gndana vddana vpix gndpix vsamp gndadc vdddig nbias_colload test_ena int_time1 int_time2 int_time3 monitor1 monitor2 monitor3 cap_vrefadc vpix cap_vrefcm reset_n scan_en scan_clk scan_clk_en gndpix gnddig vdddig vpix pixdiode

Supply LVDS LVDS LVDS LVDS Supply Supply Analog Analog Supply Supply Supply Supply Supply Supply Supply Supply Supply Supply Supply Supply Analog CMOS CMOS CMOS CMOS CMOS CMOS CMOS Analog Supply Analog CMOS CMOS CMOS CMOS Supply Supply Supply Supply Analog

IO I I O O IO IO O O IO IO IO IO IO IO IO IO IO IO IO IO O I I I I O O O O IO O IO I I I IO IO IO IO O

LVDS power LVDS input clock 310 Mhz p-node LVDS input clock 310 Mhz n-node LVDS sync p output LVDS sync n output digital ground digital power supply lower limit adc range decoupling higher limit adc range decoupling ADC ground ADC power supply digital ground column buffers ground column buffers supply column buffers ground column buffers supply pixel core supply pixel core ground image core select and sample supply ADC ground digital power supply column bias decouple scan pin for sequencer integration pin first slope integration pin dual slope integration pin tripple slope

U18 V19 W19 V20 W20 W24 V24 W22 V22 U20 T20 U22 W23 V23 U23 T23 T22 U21 T21 U24 T24 A24 C24 C23 B23 A23

output pin for integration timing, high during integration C22 output pin for dual slope integration timing, high during B22 integration output pin for triple slope integration timing, high during A22 integration ADC black reference decoupling pixel core supply adc common mode decoupling chip reset (active low) DFT scan enable DFT clock DFT clock enable pixel core ground digital ground digital power supply pixel core supply pixel diode current pin C21 B21 A21 C20 B20 A20 C19 B19 A19 C18 B18 A18

Document Number: 001-24599 Rev. **

Page 35 of 42

CYIL2SM1300AA

nr

pin name

Type

Direction

Description

Position

85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127

gndpix vsamp vresetab vprech vmemh vmeml vreset vresetds vresetts vresetab gndpix vresetts vresetds vreset vsamp vmeml vmemh vprech n/a gndpix vresetab vresetts vresetds vreset vmeml vmemh vprech vresetab vsamp gndpix ibiaspre vpix vdddig gnddig gndpix thermkathtop thermanotop thermkathbot thermanobot cap_vrefcm vpix cap_vrefadc spics

Supply Supply Supply Supply Supply Supply Supply Supply Supply Supply Supply Supply Supply Supply Supply Supply Supply Supply Supply Supply Supply Supply Supply Supply Supply Supply Supply Supply Supply Analog Supply Supply Supply Supply Analog Analog Analog Analog Analog Supply Analog CMOS

IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO I IO IO IO IO O I O I O IO O I

pixel core ground image core select and sample supply anti blooming lower reset level pixel precharge level / decoupling pin pixel memory reference high pixel memory reference low pixel reset level pixel dual slope reset level / decoupling pin pixel tripple splope reset level / decoupling pin anti blooming lower reset level pixel core ground pixel tripple splope reset level / decoupling pin pixel dual slope reset level / decoupling pin pixel reset level image core select and sample supply pixel memory reference low pixel memory reference high pixel precharge level / decoupling pin not assigned pixel core ground anti blooming lower reset level pixel tripple splope reset level / decoupling pin pixel dual slope reset level / decoupling pin pixel reset level pixel memory reference low pixel memory reference high pixel precharge level / decoupling pin anti blooming lower reset level image core select and sample supply pixel core ground extermal current bias for vprech (not connected by default) pixel core supply digital power supply digital ground pixel core ground temperature sensor kathode bottom temperature sensor anode bottom temperature sensor kathode bottom temperature sensor anode bottom adc common mode decoupling pixel core supply ADC black reference decoupling SPI chip select

C17 B17 A17 C16 B16 A16 C15 B15 A15 C14 B14 A14 C13 B13 A13 A12 B12 C12 A11 B11 C11 A10 B10 C10 A9 B9 C9 A8 B8 C8 A7 B7 C7 A6 B6 C6 A5 B5 C5 A4 B4 C4 A3 Page 36 of 42

Document Number: 001-24599 Rev. **

CYIL2SM1300AA

nr

pin name

Type

Direction

Description

Position

128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143 144 145 146 147 148 149 150

spiclk spiin spiout mbsbus[0] mbsbus[1] refbg cmdmbs vdddig gndadc vsamp gndpix vpix vddana gndana vddbuf gndbuf gnddig vddadc gndadc cap_vrefp cap_vrefm vdddig gnddig

CMOS CMOS CMOS Analog Analog Analog Analog Supply Supply Supply Supply Supply Supply Supply Supply Supply Supply Supply Supply Analog Analog Supply Supply

I I O IO IO IO I IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO

SPI clock SPI serial input SPI serial output first mixed boundry scan bus second mixed boundry scan bus external bias resistor bias current for mbs buffers digital power supply ADC ground image core select and sample supply pixel core ground pixel core supply column buffers supply column buffers ground column buffers supply column buffers ground digital ground ADC power supply ADC ground higher limit ADC range decoupling lower limit ADC range decoupling digital power supply digital ground

B3 C3 A2 B2 C2 C1 A1 T1 U1 T4 U4 T2 T3 U3 V3 W3 U2 T5 U5 V2 W2 V1 W1

Document Number: 001-24599 Rev. **

Page 37 of 42

CYIL2SM1300AA

6. Package drawing

Figure 31. Package Drawing (A)

Document Number: 001-24599 Rev. **

Page 38 of 42

CYIL2SM1300AA

Figure 32. Package Drawing (B)

Document Number: 001-24599 Rev. **

Page 39 of 42

CYIL2SM1300AA

6.1 Package with Glass cross-section

Figure 33. Package Cross-section

6.2 Die Specifications

Figure 34. Die Specifications

Document Number: 001-24599 Rev. **

Page 40 of 42

CYIL2SM1300AA

7. Glass lid

A D263 glass is used as protection glass lid on top of the LUPA-1300-2 monochrome and color sensors. The following figure shows the transmission characteristics of the D263 glass.

Figure 35. Transmission characteristics of the D263 glass used as protective cover for the LUPA-1300-2 sensors

As can be seen in Figure 35, no infrared attenuating color filter glass is used. The user is required to provide this filter in the optical path when color devices are used.

equipment; grounded wrist straps at ESD protected workstations are recommended, including the use of ionized blowers. All tools must be ESD protected.

Manual Soldering:

8. Color filter

An optional color filter can be processed as well. The LUPA-1300-2 can also be processed with a Bayer RGB color pattern.

When a soldering iron is used the following conditions must be observed: Use a soldering iron with temperature control at the tip. The soldering iron tip temperature must not exceed 350C. The soldering period for each pin must be less than 5 seconds.

Precautions and cleaning:

9. Handling precautions

Special care must be given when soldering image sensors with color filter arrays (RGB color filters), onto a circuit board, since color filters are sensitive to high temperatures. Prolonged heating at elevated temperatures may result in deterioration of the performance of the sensor. The following recommendations are made to ensure that sensor performance is not compromised during end-users' assembly processes.

Board Assembly:

Avoid spilling solder flux on the cover glass; bare glass and particularly glass with antireflection filters may be adversely affected by the flux. Avoid mechanical or particulate damage to the cover glass. It is recommended that isopropyl alcohol (IPA) be used as a solvent for cleaning the image sensor glass lid. When using other solvents, it must be confirmed beforehand whether the solvent dissolves the package or the glass lid or both.

Device placement onto boards must be done in accordance with strict ESD controls for Class 0, JESD22 Human Body Model, and Class A, JESD22 Machine Model devices. Assembly operators must always wear all designated and approved grounding

Document Number: 001-24599 Rev. **

Page 41 of 42

CYIL2SM1300AA

Document History Page

Document Title: CYIL2SM1300AA LUPA-1300-2 High speed CMOS Image Sensor Document Number: 001-24599 Revision ECN Orig. of Change Description of Change

**

See ECN

FPW

Initial Cypress release

Cypress Semiconductor Corporation, 2007. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges. Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress. Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges. Use may be limited by and subject to the applicable Cypress software license agreement.

Document Number: 001-24599 Rev. **

Revised September 10, 2007

Page 42 of 42

All products and company names mentioned in this document may be the trademarks of their respective holders.

S-ar putea să vă placă și

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- Moving Target Indication - Wikipedia, The Free EncyclopediaDocument4 paginiMoving Target Indication - Wikipedia, The Free EncyclopediaMuhammad MohsinÎncă nu există evaluări

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- Signals Intelligence - Wikipedia, The Free Encyclopedia PDFDocument15 paginiSignals Intelligence - Wikipedia, The Free Encyclopedia PDFMuhammad MohsinÎncă nu există evaluări

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- Spread Spectrum - Wikipedia, The Free EncyclopediaDocument5 paginiSpread Spectrum - Wikipedia, The Free EncyclopediaMuhammad MohsinÎncă nu există evaluări

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- Acronyms and Abbreviations in Avionics - Wikipedia, The Free EncyclopediaDocument15 paginiAcronyms and Abbreviations in Avionics - Wikipedia, The Free EncyclopediaMuhammad MohsinÎncă nu există evaluări

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (894)

- Switched Capacitor NetworksDocument17 paginiSwitched Capacitor NetworksMuhammad MohsinÎncă nu există evaluări

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (399)

- Electronic Devices and Circuits Proect ListDocument1 paginăElectronic Devices and Circuits Proect ListMuhammad MohsinÎncă nu există evaluări

- Chaos MappingsDocument30 paginiChaos MappingsMuhammad MohsinÎncă nu există evaluări

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- Digital Signal Processing Lab Exercise No.10: BS Electrical Engineering ProgramDocument2 paginiDigital Signal Processing Lab Exercise No.10: BS Electrical Engineering ProgramMuhammad MohsinÎncă nu există evaluări

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- Verilog RTL Modeling Serial Communication: EncodingDocument4 paginiVerilog RTL Modeling Serial Communication: EncodingMUHAMMAD MOHSINÎncă nu există evaluări

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (587)

- Linux OS LabDocument2 paginiLinux OS LabSubaÎncă nu există evaluări

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (265)

- Applications and Interpretation Standard SpecimensDocument56 paginiApplications and Interpretation Standard SpecimensNahir ClaraÎncă nu există evaluări

- AP Calculus BC Study GuideDocument4 paginiAP Calculus BC Study GuideHarshil SahaiÎncă nu există evaluări

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (73)

- Z 80 HelptopicsDocument5 paginiZ 80 HelptopicsEverly NÎncă nu există evaluări