Documente Academic

Documente Profesional

Documente Cultură

Mosfet Irf2708

Încărcat de

ferdialvascribdDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Mosfet Irf2708

Încărcat de

ferdialvascribdDrepturi de autor:

Formate disponibile

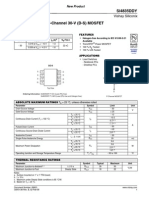

IRF2807

HEXFET

Power MOSFET

3/16/01

Parameter Typ. Max. Units

R

JC

Junction-to-Case 0.65

R

CS

Case-to-Sink, Flat, Greased Surface 0.50 C/W

R

JA

Junction-to-Ambient 62

Thermal Resistance

www.irf.com 1

V

DSS

= 75V

R

DS(on)

= 13m

I

D

= 82AC

S

D

G

TO-220AB

Advanced HEXFET

Power MOSFETs from International

Rectifier utilize advanced processing techniques to achieve

extremely low on-resistance per silicon area. This benefit,

combined with the fast switching speed and ruggedized

device design that HEXFET power MOSFETs are well

known for, provides the designer with an extremely efficient

and reliable device for use in a wide variety of applications.

The TO-220 package is universally preferred for all

commercial-industrial applications at power dissipation

levels to approximately 50 watts. The low thermal

resistance and low package cost of the TO-220 contribute

to its wide acceptance throughout the industry.

Advanced Process Technology

Ultra Low On-Resistance

Dynamic dv/dt Rating

175C Operating Temperature

Fast Switching

Fully Avalanche Rated

Description

PD - 91517

Absolute Maximum Ratings

Parameter Max. Units

I

D

@ T

C

= 25C Continuous Drain Current, V

GS

@ 10V 82C

I

D

@ T

C

= 100C Continuous Drain Current, V

GS

@ 10V 58 A

I

DM

Pulsed Drain Current C 280

P

D

@T

C

= 25C Power Dissipation 230 W

Linear Derating Factor 1.5 W/C

V

GS

Gate-to-Source Voltage 20 V

I

AR

Avalanche CurrentC 43 A

E

AR

Repetitive Avalanche EnergyC 23 mJ

dv/dt Peak Diode Recovery dv/dt C 5.9 V/ns

T

J

Operating Junction and -55 to + 175

T

STG

Storage Temperature Range

Soldering Temperature, for 10 seconds 300 (1.6mm from case )

C

Mounting torque, 6-32 or M3 srew 10 lbfin (1.1Nm)

IRF2807

2 www.irf.com

S

D

G

Parameter Min. Typ. Max. Units Conditions

I

S

Continuous Source Current MOSFET symbol

(Body Diode)

showing the

ISM Pulsed Source Current integral reverse

(Body Diode)C

p-n junction diode.

V

SD

Diode Forward Voltage 1.2 V T

J

= 25C, I

S

= 43A, V

GS

= 0V

t

rr

Reverse Recovery Time 100 150 ns T

J

= 25C, I

F

= 43A

Q

rr

Reverse Recovery Charge 410 610 nC di/dt = 100A/s

t

on

Forward Turn-On Time Intrinsic turn-on time is negligible (turn-on is dominated by L

S

+L

D

)

Source-Drain Ratings and Characteristics

82C

280

A

C Starting T

J

= 25C, L = 370H

R

G

= 25, I

AS

= 43A, V

GS

=10V (See Figure 12)

C Repetitive rating; pulse width limited by

max. junction temperature. (See fig. 11)

Notes:

C I

SD

43A, di/dt 300A/s, V

DD

V

(BR)DSS

,

T

J

175C

Pulse width 400s; duty cycle 2%.

This is a typical value at device destruction and represents

operation outside rated limits.

1 This is a calculated value limited to T

J

= 175C .

C Calculated continuous current based on maximum allowable

junction temperature. Package limitation current is 75A.

Parameter Min. Typ. Max. Units Conditions

V

(BR)DSS

Drain-to-Source Breakdown Voltage 75 V V

GS

= 0V, I

D

= 250A

V(BR)DSS/TJ Breakdown Voltage Temp. Coefficient 0.074 V/C Reference to 25C, I

D

= 1mA

R

DS(on)

Static Drain-to-Source On-Resistance 13 m V

GS

= 10V, I

D

= 43A

V

GS(th)

Gate Threshold Voltage 2.0 4.0 V V

DS

= V

GS

, I

D

= 250A

g

fs

Forward Transconductance 38 S V

DS

= 50V, I

D

= 43A

25

A

V

DS

= 75V, V

GS

= 0V

250 V

DS

= 60V, V

GS

= 0V, T

J

= 150C

Gate-to-Source Forward Leakage 100 V

GS

= 20V

Gate-to-Source Reverse Leakage -100

nA

V

GS

= -20V

Q

g

Total Gate Charge 160 I

D

= 43A

Q

gs

Gate-to-Source Charge 29 nC V

DS

= 60V

Q

gd

Gate-to-Drain ("Miller") Charge 55 V

GS

= 10V, See Fig. 6 and 13

t

d(on)

Turn-On Delay Time 13 V

DD

= 38V

t

r

Rise Time 64 I

D

= 43A

t

d(off)

Turn-Off Delay Time 49 R

G

= 2.5

t

f

Fall Time 48 V

GS

= 10V, See Fig. 10

Between lead,

6mm (0.25in.)

from package

and center of die contact

C

iss

Input Capacitance 3820 V

GS

= 0V

C

oss

Output Capacitance 610 V

DS

= 25V

C

rss

Reverse Transfer Capacitance 130 pF = 1.0MHz, See Fig. 5

E

AS

Single Pulse Avalanche EnergyC 12803401 mJ I

AS

= 50A, L = 370H

nH

Electrical Characteristics @ T

J

= 25C (unless otherwise specified)

L

D

Internal Drain Inductance

L

S

Internal Source Inductance

S

D

G

I

GSS

ns

4.5

7.5

I

DSS

Drain-to-Source Leakage Current

IRF2807

www.irf.com 3

Fig 4. Normalized On-Resistance

Vs. Temperature

Fig 2. Typical Output Characteristics Fig 1. Typical Output Characteristics

Fig 3. Typical Transfer Characteristics

10

100

1000

0.1 1 10 100

20s PULSE WIDTH

T = 25 C J

TOP

BOTTOM

VGS

15V

10V

8.0V

7.0V

6.0V

5.5V

5.0V

4.5V

V , Drain-to-Source Voltage (V)

I

,

D

r

a

i

n

-

t

o

-

S

o

u

r

c

e

C

u

r

r

e

n

t

(

A

)

DS

D

4.5V

10

100

1000

0.1 1 10 100

20s PULSE WIDTH

T = 175 C J

TOP

BOTTOM

VGS

15V

10V

8.0V

7.0V

6.0V

5.5V

5.0V

4.5V

V , Drain-to-Source Voltage (V)

I

,

D

r

a

i

n

-

t

o

-

S

o

u

r

c

e

C

u

r

r

e

n

t

(

A

)

DS

D

4.5V

10

100

1000

4.0 5.0 6.0 7.0 8.0 9.0

V = 25V

20s PULSE WIDTH

DS

V , Gate-to-Source Voltage (V)

I

,

D

r

a

i

n

-

t

o

-

S

o

u

r

c

e

C

u

r

r

e

n

t

(

A

)

GS

D

T = 25 C

J

T = 175 C

J

-60 -40 -20 0 20 40 60 80 100 120 140 160 180

0.0

0.5

1.0

1.5

2.0

2.5

3.0

T , Junction Temperature ( C)

R

,

D

r

a

i

n

-

t

o

-

S

o

u

r

c

e

O

n

R

e

s

i

s

t

a

n

c

e

(

N

o

r

m

a

l

i

z

e

d

)

J

D

S

(

o

n

)

V =

I =

GS

D

10V

71A

IRF2807

4 www.irf.com

Fig 8. Maximum Safe Operating Area

Fig 6. Typical Gate Charge Vs.

Gate-to-Source Voltage

Fig 5. Typical Capacitance Vs.

Drain-to-Source Voltage

Fig 7. Typical Source-Drain Diode

Forward Voltage

0 40 80 120 160

0

4

8

12

16

20

Q , Total Gate Charge (nC)

V

,

G

a

t

e

-

t

o

-

S

o

u

r

c

e

V

o

l

t

a

g

e

(

V

)

G

G

S

FOR TEST CIRCUIT

SEE FIGURE

I = D

13

43A

V = 15V

DS

V = 37V

DS

V = 60V

DS

0.1

1

10

100

1000

0.0 0.4 0.8 1.2 1.6 2.0 2.4

V ,Source-to-Drain Voltage (V)

I

,

R

e

v

e

r

s

e

D

r

a

i

n

C

u

r

r

e

n

t

(

A

)

SD

S

D

V = 0 V

GS

T = 25 C

J

T = 175 C

J

1 10 100

V

DS

, Drain-to-Source Voltage (V)

0

1000

2000

3000

4000

5000

6000

7000

C

,

C

a

p

a

c

i

t

a

n

c

e

(

p

F

)

Coss

Crss

Ciss

V

GS

= 0V, f = 1 MHZ

C

iss

= C

gs

+ C

gd

, C

ds

SHORTED

C

rss

= C

gd

C

oss

= C

ds

+ C

gd

1 10 100 1000

V

DS

, Drain-toSource Voltage (V)

1

10

100

1000

I

D

,

D

r

a

i

n

-

t

o

-

S

o

u

r

c

e

C

u

r

r

e

n

t

(

A

)

Tc = 25C

Tj = 175C

Single Pulse

1msec

10msec

OPERATION IN THIS AREA

LIMITED BY R

DS

(on)

100sec

IRF2807

www.irf.com 5

Fig 11. Maximum Effective Transient Thermal Impedance, Junction-to-Case

Fig 9. Maximum Drain Current Vs.

Case Temperature

0.01

0.1

1

0.00001 0.0001 0.001 0.01 0.1

Notes:

1. Duty factor D = t / t

2. Peak T =P x Z + T

1 2

J DM thJC C

P

t

t

DM

1

2

t , Rectangular Pulse Duration (sec)

T

h

e

r

m

a

l

R

e

s

p

o

n

s

e

(

Z

)

1

t

h

J

C

0.01

0.02

0.05

0.10

0.20

D = 0.50

SINGLE PULSE

(THERMAL RESPONSE)

25 50 75 100 125 150 175

0

20

40

60

80

100

T , Case Temperature ( C)

I

,

D

r

a

i

n

C

u

r

r

e

n

t

(

A

)

C

D

LIMITED BY PACKAGE

V

DS

90%

10%

V

GS

t

d(on)

t

r

t

d(off)

t

f

V

DS

Pulse Width 1 s

Duty Factor 0.1 %

R

D

V

GS

R

G

D.U.T.

V

GS

+

-

V

DD

Fig 10a. Switching Time Test Circuit

Fig 10b. Switching Time Waveforms

IRF2807

6 www.irf.com

Q

G

Q

GS

Q

GD

V

G

Charge

D.U.T.

V

DS

I

D

I

G

3mA

V

GS

.3F

50K

.2F

12V

Current Regulator

Same Type as D.U.T.

Current Sampling Resistors

+

-

V

GS

Fig 13b. Gate Charge Test Circuit Fig 13a. Basic Gate Charge Waveform

Fig 12b. Unclamped Inductive Waveforms

Fig 12a. Unclamped Inductive Test Circuit

t

p

V

(BR)DSS

I

AS

Fig 12c. Maximum Avalanche Energy

Vs. Drain Current

25 50 75 100 125 150 175

0

100

200

300

400

500

600

Starting T , Junction Temperature ( C)

E

,

S

i

n

g

l

e

P

u

l

s

e

A

v

a

l

a

n

c

h

e

E

n

e

r

g

y

(

m

J

)

J

A

S

I

D

TOP

BOTTOM

18A

30A

43A

R

G

I

AS

0.0 1 t

p

D.U. T

L

V

D S

+

-

V

DD

DRI VER

A

15V

20V VGS

IRF2807

www.irf.com 7

Peak Diode Recovery dv/dt Test Circuit

P.W.

Period

di/dt

Diode Recovery

dv/dt

Ripple 5%

Body Diode Forward Drop

Re-Applied

Voltage

Reverse

Recovery

Current

Body Diode Forward

Current

V

GS

=10V

V

DD

I

SD

Driver Gate Drive

D.U.T. I

SD

Waveform

D.U.T. V

DS

Waveform

Inductor Curent

D =

P.W.

Period

+

-

+

+

+ -

-

-

C

C

R

G

V

DD

dv/dt controlled by R

G

I

SD

controlled by Duty Factor "D"

D.U.T. - Device Under Test

D.U.T*

Circuit Layout Considerations

Low Stray Inductance

Ground Plane

Low Leakage Inductance

Current Transformer

C

* Reverse Polarity of D.U.T for P-Channel

V

GS

[ ]

[ ]

*** V

GS

= 5.0V for Logic Level and 3V Drive Devices

[ ] ***

Fig 14. For N-channel HEXFET

power MOSFETs

IRF2807

8 www.irf.com

LEAD ASSIGNMENTS

1 - GATE

2 - DRAIN

3 - SOU RC E

4 - DRAIN

- B -

1.32 (.052)

1.22 (.048)

3X

0.55 (.022)

0.46 (.018)

2.92 (.115)

2.64 (.104)

4.69 ( .185)

4.20 ( .165)

3X

0.93 (.037)

0.69 (.027)

4.06 (.160)

3.55 (.140)

1.15 (.045)

MIN

6.47 (.255)

6.10 (.240)

3.78 (.149)

3.54 (.139)

- A -

10.54 (.415)

10.29 (.405)

2.87 (.113)

2.62 (.103)

15.24 (.600)

14.84 (.584)

14.09 (.555)

13.47 (.530)

3X

1.40 (.055)

1.15 (.045)

2.54 (.100)

2X

0.36 (.014) M B A M

4

1 2 3

N OTES:

1 D IMENSIONING & TOLERANCING PER ANSI Y14.5M, 1982. 3 OUTLINE CONFORMS TO JEDEC OUTLINE TO-220AB.

2 C ONTROLLING DIMENSION : INCH 4 HEATSINK & LEAD MEASUREMENTS DO NOT INCLU DE BURRS.

Part Marking Information

TO-220AB

Package Outline

TO-220AB

Dimensions are shown in millimeters (inches)

PART NUMBER

I NTERNATI ONAL

RECTI FIER

LOGO

EXAMPLE : THI S I S AN IRF1010

W ITH ASSEMBLY

LOT CODE 9B1M

ASSEMBLY

LOT CODE

DATE CODE

(YYW W )

YY = YEAR

W W = W EEK

9246

IRF1010

9B 1M

A

IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245, USA Tel: (310) 252-7105

TAC Fax: (310) 252-7903

Visit us at www.irf.com for sales contact information. 3/01

Data and specifications subject to change without notice.

This product has been designed and qualified for the Automotive [Q101] market.

Qualification Standards can be found on IRs Web site.

Note: For the most current drawings please refer to the IR website at:

http://www.irf.com/package/

S-ar putea să vă placă și

- V R Max I: IRF1312 IRF1312S IRF1312LDocument11 paginiV R Max I: IRF1312 IRF1312S IRF1312LPanos DiamantoulakisÎncă nu există evaluări

- Irfp 064 VDocument9 paginiIrfp 064 VPerrote PerroÎncă nu există evaluări

- Datasheet IRFB11N50ADocument8 paginiDatasheet IRFB11N50AMartín SayagoÎncă nu există evaluări

- Irfr 5305Document11 paginiIrfr 5305LucaDirafÎncă nu există evaluări

- Irfi 3205 Power MosfetDocument9 paginiIrfi 3205 Power MosfetAndy WilsonÎncă nu există evaluări

- Irfz 24 NDocument9 paginiIrfz 24 Njmbernal7487886Încă nu există evaluări

- Irl 530 NDocument9 paginiIrl 530 NEric Lenin Marin MoncadaÎncă nu există evaluări

- Irf 540 NsDocument11 paginiIrf 540 NsLucas PascualÎncă nu există evaluări

- IRF9540NDocument8 paginiIRF9540Nhardik_patel182000Încă nu există evaluări

- Advanced Power MOSFET Drive and SwitchingDocument4 paginiAdvanced Power MOSFET Drive and SwitchingJacksonVelozÎncă nu există evaluări

- Advanced 55V MOSFET with 175°C Operation and 26A RatingDocument8 paginiAdvanced 55V MOSFET with 175°C Operation and 26A RatingNairo FilhoÎncă nu există evaluări

- F1010EDocument8 paginiF1010EKamran KhanÎncă nu există evaluări

- Irfp 150 NDocument8 paginiIrfp 150 NPerversso SkellingtonÎncă nu există evaluări

- International Rectifier IRFP2907Document9 paginiInternational Rectifier IRFP2907scribd20110526Încă nu există evaluări

- Sample MOSFET DatasheetDocument8 paginiSample MOSFET DatasheettolindoyÎncă nu există evaluări

- Irf 4905Document9 paginiIrf 4905Andre Vitor DobrychtopÎncă nu există evaluări

- Irfps 3810 PBFDocument8 paginiIrfps 3810 PBFCrisan Radu-HoreaÎncă nu există evaluări

- Advanced Power Electronics Corp.: AP15N03H/JDocument6 paginiAdvanced Power Electronics Corp.: AP15N03H/JShezan ShaniÎncă nu există evaluări

- Irfp 260 NDocument9 paginiIrfp 260 NJolaine MojicaÎncă nu există evaluări

- Irl 1004Document9 paginiIrl 1004Luiz RvÎncă nu există evaluări

- 5305SDocument10 pagini5305SHugo Camacho RamirezÎncă nu există evaluări

- Irfp 90 N 20 DDocument9 paginiIrfp 90 N 20 DAndré Frota PaivaÎncă nu există evaluări

- Advanced Process Technology Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching P-Channel Fully Avalanche RatedDocument9 paginiAdvanced Process Technology Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching P-Channel Fully Avalanche RatedPedro Cu AguirreÎncă nu există evaluări

- Irf 1407Document10 paginiIrf 1407Adilson BogadoÎncă nu există evaluări

- Irfp 140 NDocument9 paginiIrfp 140 NCodinasound CaÎncă nu există evaluări

- Irfz 34 NLDocument10 paginiIrfz 34 NLguerrero_27Încă nu există evaluări

- Irfp 460 ADocument8 paginiIrfp 460 AKasun Darshana PeirisÎncă nu există evaluări

- Qfet Qfet Qfet Qfet: FQP90N08Document8 paginiQfet Qfet Qfet Qfet: FQP90N08Hãy Cố LênÎncă nu există evaluări

- 15n03gh PDFDocument6 pagini15n03gh PDFdragon-red0816Încă nu există evaluări

- Irfp2907Pbf: Typical ApplicationsDocument9 paginiIrfp2907Pbf: Typical Applicationsrajeev_kumar_1231852Încă nu există evaluări

- U9024NDocument10 paginiU9024Nitm12Încă nu există evaluări

- IRL540NDocument8 paginiIRL540Nmestek123Încă nu există evaluări

- Switching Regulator Applications: Absolute Maximum RatingsDocument6 paginiSwitching Regulator Applications: Absolute Maximum RatingsSyed Azhar HussainÎncă nu există evaluări

- DatasheetDocument7 paginiDatasheetrene gonzÎncă nu există evaluări

- Si4835DDY: Vishay SiliconixDocument10 paginiSi4835DDY: Vishay SiliconixRoberto Celedón AguileraÎncă nu există evaluări

- Irfb4020Pbf: Digital Audio MosfetDocument8 paginiIrfb4020Pbf: Digital Audio Mosfetto_netiksÎncă nu există evaluări

- IRF3710Document8 paginiIRF3710Andrés MorochoÎncă nu există evaluări

- IRFZ48NDocument8 paginiIRFZ48NLuay IssaÎncă nu există evaluări

- CMF20120DDocument8 paginiCMF20120DDGBORISÎncă nu există evaluări

- Generation V Technology Ultra Low On-Resistance Complimentary Half Bridge Surface Mount Fully Avalanche RatedDocument10 paginiGeneration V Technology Ultra Low On-Resistance Complimentary Half Bridge Surface Mount Fully Avalanche RatedFidel ArroyoÎncă nu există evaluări

- Smps Mosfet: Irfb23N20Dpbf Irfs23N20Dpbf Irfsl23N20DpbfDocument11 paginiSmps Mosfet: Irfb23N20Dpbf Irfs23N20Dpbf Irfsl23N20DpbfΠΕΤΡΟΣ ΛΟΥΚΑΣÎncă nu există evaluări

- Irf1405 DatasheetDocument9 paginiIrf1405 DatasheetE Alejandro G. BenavidesÎncă nu există evaluări

- Fdms7670: N-Channel Powertrench MosfetDocument7 paginiFdms7670: N-Channel Powertrench MosfetDwi TjitosonÎncă nu există evaluări

- IRFP360LCDocument8 paginiIRFP360LCΗρακλης ΖερκελιδηςÎncă nu există evaluări

- Irfs4321-7Ppbf: Application V 150V R 11.7M 14.7M I 86ADocument10 paginiIrfs4321-7Ppbf: Application V 150V R 11.7M 14.7M I 86Anithinmundackal3623Încă nu există evaluări

- Irfb4410Zgpbf: V 100V R Typ. 7.2M Max. 9.0M I 97ADocument8 paginiIrfb4410Zgpbf: V 100V R Typ. 7.2M Max. 9.0M I 97AWalter Hurtado ToroÎncă nu există evaluări

- Radiation Hardened IRHNA57163SE Power Mosfet Surface Mount (Smd-2) 130V, N-CHANNELDocument8 paginiRadiation Hardened IRHNA57163SE Power Mosfet Surface Mount (Smd-2) 130V, N-CHANNELbmmostefaÎncă nu există evaluări

- IRF540NDocument7 paginiIRF540Nmichaelliu123456Încă nu există evaluări

- RFP50N05LDocument6 paginiRFP50N05LNegru P. PlantatieÎncă nu există evaluări

- Irfb3306Pbf Irfs3306Pbf Irfsl3306Pbf: V 60V R Typ. 3.3M: Max. 4.2M: I 160ADocument11 paginiIrfb3306Pbf Irfs3306Pbf Irfsl3306Pbf: V 60V R Typ. 3.3M: Max. 4.2M: I 160AalvarezsilvaÎncă nu există evaluări

- G 4 BC 20 KDDocument11 paginiG 4 BC 20 KDJuan Carlos Terrones NuñezÎncă nu există evaluări

- Advanced MOSFET for Power ApplicationsDocument7 paginiAdvanced MOSFET for Power ApplicationsLeonardo NavarroÎncă nu există evaluări

- Datasheet 2SK3797 Mosfet Fuente Proyector Viewsonic PJD5123Document6 paginiDatasheet 2SK3797 Mosfet Fuente Proyector Viewsonic PJD5123Rubén Nicanor Sandoval BascuñanÎncă nu există evaluări

- Irfb4310 MosfetDocument12 paginiIrfb4310 MosfetprasadÎncă nu există evaluări

- Irlz 24 NDocument9 paginiIrlz 24 NRobson PontinÎncă nu există evaluări

- Irfz 48 VDocument8 paginiIrfz 48 VZoltán HalászÎncă nu există evaluări

- Irf740b PDFDocument10 paginiIrf740b PDFMed SamiÎncă nu există evaluări

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsDe la EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsÎncă nu există evaluări

- 110 Waveform Generator Projects for the Home ConstructorDe la Everand110 Waveform Generator Projects for the Home ConstructorEvaluare: 4 din 5 stele4/5 (1)

- Invertec v350 ProDocument167 paginiInvertec v350 ProferdialvascribdÎncă nu există evaluări

- Sony KDL - 32L4000 Chasis MA2Document84 paginiSony KDL - 32L4000 Chasis MA2GustavoTovarÎncă nu există evaluări

- Sony Kdfe60a20Document144 paginiSony Kdfe60a20joe_cooper_10Încă nu există evaluări

- Samsung TXJ1966 TVDocument44 paginiSamsung TXJ1966 TVferdialvascribdÎncă nu există evaluări

- RCA 14M041 Service ManualDocument34 paginiRCA 14M041 Service ManualferdialvascribdÎncă nu există evaluări

- Sony Kdfe60a20Document144 paginiSony Kdfe60a20joe_cooper_10Încă nu există evaluări

- Sharp 25KM100 TV Service ManualDocument48 paginiSharp 25KM100 TV Service ManualferdialvascribdÎncă nu există evaluări

- Panasonic CT 20R6EDocument30 paginiPanasonic CT 20R6EferdialvascribdÎncă nu există evaluări

- Philips 32MF231D-37 Service ManualDocument128 paginiPhilips 32MF231D-37 Service ManualferdialvascribdÎncă nu există evaluări

- RCA 14F512T Chassis M123SP Schematic PDFDocument1 paginăRCA 14F512T Chassis M123SP Schematic PDFferdialvascribdÎncă nu există evaluări

- Home Theater User's GuideDocument37 paginiHome Theater User's GuideferdialvascribdÎncă nu există evaluări

- RCA 14M041 Service ManualDocument34 paginiRCA 14M041 Service ManualferdialvascribdÎncă nu există evaluări

- Sony Kdf-E42a10 - E50a10 TV SMDocument173 paginiSony Kdf-E42a10 - E50a10 TV SMferdialvascribdÎncă nu există evaluări

- Vizio 120HZ E Series User ManualDocument62 paginiVizio 120HZ E Series User ManualferdialvascribdÎncă nu există evaluări

- Home Theater User's GuideDocument37 paginiHome Theater User's GuideferdialvascribdÎncă nu există evaluări

- Philips 32PF7321D LCD TV User ManualDocument40 paginiPhilips 32PF7321D LCD TV User ManualferdialvascribdÎncă nu există evaluări

- Vizio 120HZ E Series User ManualDocument62 paginiVizio 120HZ E Series User ManualferdialvascribdÎncă nu există evaluări

- Vizio 120HZ E Series User ManualDocument62 paginiVizio 120HZ E Series User ManualferdialvascribdÎncă nu există evaluări

- 42LC3D ManualDocument68 pagini42LC3D ManualKeith ConradÎncă nu există evaluări

- KDF-46E2000 and OtherDocument139 paginiKDF-46E2000 and Othertman30297Încă nu există evaluări

- Panasonic PT 52lcx66Document83 paginiPanasonic PT 52lcx66ferdialvascribdÎncă nu există evaluări

- NEC PX42VR5A Model InformationDocument8 paginiNEC PX42VR5A Model InformationferdialvascribdÎncă nu există evaluări

- Homework 7 Traffic Accident Data AnalysisDocument5 paginiHomework 7 Traffic Accident Data AnalysisRagini P0% (1)

- Manual Aeroccino 3Document30 paginiManual Aeroccino 3UltrabetoÎncă nu există evaluări

- Assessment of Electronic Collection Development in Nigerian University LibrariesDocument24 paginiAssessment of Electronic Collection Development in Nigerian University Librariesmohamed hassanÎncă nu există evaluări

- Catalogue: See Colour in A Whole New LightDocument17 paginiCatalogue: See Colour in A Whole New LightManuel AguilarÎncă nu există evaluări

- Concrete Construction Article PDF Strategic Planning For ContractorsDocument4 paginiConcrete Construction Article PDF Strategic Planning For ContractorsMohammed NizamÎncă nu există evaluări

- LeadershipDocument5 paginiLeadershipapi-3850643Încă nu există evaluări

- LGDocument5 paginiLGPreetham Kiran RodriguesÎncă nu există evaluări

- Grader 14 M Caterpillar BrouchorDocument2 paginiGrader 14 M Caterpillar Brouchorjude tallyÎncă nu există evaluări

- Hydrostatic Test ReportsDocument3 paginiHydrostatic Test ReportsHanuman RaoÎncă nu există evaluări

- Digital Signature Certificate Subscription FormDocument7 paginiDigital Signature Certificate Subscription FormAneesh VelluvalappilÎncă nu există evaluări

- Aurora Fire Pump SpecsDocument16 paginiAurora Fire Pump SpecsJosé Martín Meza CabillasÎncă nu există evaluări

- Johannes GutenbergDocument6 paginiJohannes GutenbergMau ReenÎncă nu există evaluări

- VideosDocument5 paginiVideosElvin Joseph Pualengco MendozaÎncă nu există evaluări

- Pondicherry University: Examination Application FormDocument2 paginiPondicherry University: Examination Application FormrahulnkrÎncă nu există evaluări

- Eaton: Medium Duty Piston PumpDocument25 paginiEaton: Medium Duty Piston PumprazvanÎncă nu există evaluări

- Machine Learning: MACHINE LEARNING - Copy Rights Reserved Real Time SignalsDocument56 paginiMachine Learning: MACHINE LEARNING - Copy Rights Reserved Real Time SignalsLohith Ds BangloreÎncă nu există evaluări

- Core Strategy - Statement of Consultation February 2010Document168 paginiCore Strategy - Statement of Consultation February 2010Aimee-NonaÎncă nu există evaluări

- 10 PDFDocument5 pagini10 PDFIndira BanerjeeÎncă nu există evaluări

- Chapter 4: Analysis of Financial StatementsDocument8 paginiChapter 4: Analysis of Financial StatementsSafuan HalimÎncă nu există evaluări

- DO 178B DetailedDocument25 paginiDO 178B DetailedSenthil KumarÎncă nu există evaluări

- Nissan service bulletin DTC C1A12 C1A16 sensor cleaningDocument5 paginiNissan service bulletin DTC C1A12 C1A16 sensor cleaningABDULNAZER C P 001Încă nu există evaluări

- Module 1 The Nature of Strategic Management2Document8 paginiModule 1 The Nature of Strategic Management2Julienne LobchoyÎncă nu există evaluări

- 2 C Program StructureDocument13 pagini2 C Program StructurePargi anshuÎncă nu există evaluări

- Prateek Chhabra - (C.V.) 22-08Document4 paginiPrateek Chhabra - (C.V.) 22-08PrateekÎncă nu există evaluări

- G.R. No. 208393, June 15, 2016Document3 paginiG.R. No. 208393, June 15, 2016jeliena-malazarteÎncă nu există evaluări

- Eskom Tariff Book - 2018-19Document54 paginiEskom Tariff Book - 2018-19Sandro MasakiÎncă nu există evaluări

- Cepej Report 2020-22 e WebDocument164 paginiCepej Report 2020-22 e WebGjorgji AndonovÎncă nu există evaluări

- Opposition To Motion For InjunctionDocument29 paginiOpposition To Motion For InjunctionBasseemÎncă nu există evaluări

- MohammedTauhiduzzaman Resume LinkedInDocument3 paginiMohammedTauhiduzzaman Resume LinkedIntauhid_zaman6776Încă nu există evaluări

- AR15 Forging ReceiverDocument105 paginiAR15 Forging ReceiverNO2NWO100% (10)