Documente Academic

Documente Profesional

Documente Cultură

Vibra: Block Diagram of UIF

Încărcat de

anjirponselDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Vibra: Block Diagram of UIF

Încărcat de

anjirponselDrepturi de autor:

Formate disponibile

System Module US8

NSE6

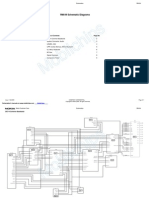

Block Diagram of UIF

VIBRA UISwitch Buzzer cntrl Blight cntl MICP MICN XMIC SGND XEAR EARP EARN PWR Slide detect PWR FLIP EAR Vibra cntl Headset conn. MIC

Original 08/98

3/A31

System Module US8

NSE6

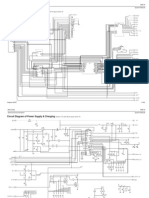

Circuit Diagram of UIF

(Version 7.0 Edit 218) for layout version 07

Original 08/98

3/A32

System Module US8

NSE6

Block Diagram of Baseband

2M

16M

Original 08/98

3/A33

System Module US8

NSE6

Circuit Diagram of Baseband

(Version 7.0 Edit 105) for layout version 07

Original 08/98

3/A34

System Module US8

NSE6

Circuit Diagram of Power Supply (Version 7.0

Edit 257) for layout version 07

Original 08/98

3/A35

System Module US8

NSE6

Circuit Diagram of SIM Connectors (Version 7.0

Edit 71) for layout version 07

Original 08/98

3/A36

System Module US8

NSE6

Circuit Diagram of CPU Block (Version 7.0

Edit 208) for layout version 07

Original 08/98

3/A37

System Module US8

NSE6

Circuit Diagram of Audio

(Version 7.0 Edit 126) for layout version 07

Original 08/98

3/A38

System Module US8

NSE6

Circuit Diagram of IR Module (Version 7.0

Edit 96) for layout version 07

Original 08/98

3/A39

System Module US8

NSE6

RF Block Diagram

SUMMA

TQFP32 TQFP48

PAmodule

Original 08/98

3/A310

System Module US8

NSE6

Circuit Diagram of RF Block (Version

1.0 Edit 244) for layout version 07

Original 08/98

3/A311

System Module US8

NSE6

Layout Diagram of US8 Top (Version 07)

Layout Diagram of US8 Bottom (Version 07)

Original 08/98

3/A312

System Module US8

NSE6

Testpoints of US8 Top (Version 07)

Testpoints of US8 Bottom (Version 07)

Original 08/98

3/A313

System Module US8

testpoint ref J101 J104 J108 J220 J223 J225 J226 J227 J228 J235 J251 J256 J500 name FBUS_TX CCONTCSX (CCONT chip select) CHRG_CTRL V5V CCONTINT (charger, RTC interrupt) EXTSYSRESETX VCXOPWR PURX (power on reset) SLEEPCLK (32kHz clock) ROM1SELX AGND COBBADAX Control voltage for UHF VCO module G600 condition active state active state charger connected active state interrupt power on power on power up/down power on active state pcb ground active state channel 60 channel 1 channel 124 dclevel pulsed DC (0V72.8V) pulse active 0V, nonactive 2.8V pulsed DC (0V/2.8V) nominal 5.0V (min 4.8V, max 5.2V) pulse active 2.8V, nonactive 0V reset state 0V, normal state 2.8V active state 2.8V, nonactive 0V reset state 0V, normal state 2.8V pulsed DC (0V/2.8V) pulse active 0V, nonactive 2.8V 0V pulse active 0V, nonactive 2.8V 2.25 +/ 0.25 V > 0.8 V < 3.7 V typ. 2.0 2.2 V min 0.5 / max 4.0 V 2.8 V min 2.7 / max 2.85 V 95 dBm @ X540 (ext. RF connector ) RXC at level of full calibrated gain 95 dBm @ X540 (ext. RF connector ) RXC at level of full calibrated gain typ ca. 1.0 1.1 V pulsed min. 0.7 / max. 1.4 V typ. 50 mVpp balanced voltage at 13 MHz aclevel

NSE6

J504 J508 J534&J536

Control voltage for VHF VCO circuit VSYN_2 ( regulated supply for PLLS ) 13 MHz IF output to N250

J538

13 MHz output from Z620 to N620

typ. ca. 1.5 V pulsed

typ. ca 600 uVrms

J542 J554 J556 J558 J560

VHF VCO output ( 232 MHz ) TXC ( TX power control voltage ) TXP ( TX enable ) TXQP ( other half of balanced Qsignal ) TXIP ( other half of balanced Isignal )

@level 19 typ. ca. 0.6 V pulse @level 5 typ ca. 1.8 V pulse 2.8 V logic level pulse, ( max. 0.8 V 0 / min 2.0 V 1 ) 0.8 V pulsed 0.8 V pulsed

typ. 400 mVpp. > 100 mVpp required

400 mVpp 400 mVpp

Original 08/98

3/A314

S-ar putea să vă placă și

- Digital Power Electronics and ApplicationsDe la EverandDigital Power Electronics and ApplicationsEvaluare: 3.5 din 5 stele3.5/5 (3)

- 110 Waveform Generator Projects for the Home ConstructorDe la Everand110 Waveform Generator Projects for the Home ConstructorEvaluare: 4 din 5 stele4/5 (1)

- Nokia 5110Document12 paginiNokia 5110Ionuţ CîrdeiÎncă nu există evaluări

- Block Diagram of System/RF Blocks: NSE-1 System Module UP8RDocument15 paginiBlock Diagram of System/RF Blocks: NSE-1 System Module UP8RCauVong JustinÎncă nu există evaluări

- LM5007 High Voltage (80V) Step Down Switching Regulator: FeaturesDocument17 paginiLM5007 High Voltage (80V) Step Down Switching Regulator: FeaturesbhushanchittaragiÎncă nu există evaluări

- Tps 65217 CDocument86 paginiTps 65217 CcosmicfundooÎncă nu există evaluări

- Fsdm0465re Fsdm0565re Fsdm07652reDocument20 paginiFsdm0465re Fsdm0565re Fsdm07652rejesus cautivoÎncă nu există evaluări

- Sepam Series 80 and Its Optional ModulesDocument4 paginiSepam Series 80 and Its Optional Modulesjellaso23Încă nu există evaluări

- VT-pro 525-625 Service ManualDocument13 paginiVT-pro 525-625 Service ManualMuhammad ShoaibÎncă nu există evaluări

- LM 2623Document21 paginiLM 2623alejo0091Încă nu există evaluări

- 1K-16K UNI/O Serial EEPROM Family Data SheetDocument48 pagini1K-16K UNI/O Serial EEPROM Family Data Sheetikaro181083Încă nu există evaluări

- Ad9851 Cmos 180 MHZ Dds/Dac SynthesizerDocument24 paginiAd9851 Cmos 180 MHZ Dds/Dac SynthesizerVijay VigneshÎncă nu există evaluări

- SPI Serial Eeprom: FeaturesDocument22 paginiSPI Serial Eeprom: FeaturesHmcc HoangÎncă nu există evaluări

- 24C64WPDocument15 pagini24C64WPaldo_suviÎncă nu există evaluări

- STB Promotion 2010.05Document33 paginiSTB Promotion 2010.05Jorge BulacioÎncă nu există evaluări

- Z86e0412psc PDFDocument44 paginiZ86e0412psc PDFhectorsevillaÎncă nu există evaluări

- 2-Wire Serial EEPROM: FeaturesDocument23 pagini2-Wire Serial EEPROM: FeaturesgillupilluÎncă nu există evaluări

- Syntek Semiconductor Co., LTD.: 1. FeaturesDocument7 paginiSyntek Semiconductor Co., LTD.: 1. FeaturesAngel Simo MoralesÎncă nu există evaluări

- A. Atmel ProductsDocument16 paginiA. Atmel ProductsJuan Jose MendozaÎncă nu există evaluări

- DRV 8811Document22 paginiDRV 8811nelson_loboÎncă nu există evaluări

- GS CMZ700B E 5th R1Document11 paginiGS CMZ700B E 5th R1Adi PrasetyoÎncă nu există evaluări

- Synchronous-Rectified Buck MOSFET Drivers: Features General DescriptionDocument12 paginiSynchronous-Rectified Buck MOSFET Drivers: Features General DescriptionAlbert PerozoÎncă nu există evaluări

- Irs27951s - RESONANT HALF-BRIDGE CONVERTER CONTROL ICDocument29 paginiIrs27951s - RESONANT HALF-BRIDGE CONVERTER CONTROL ICAnonymous R0s4q9X8Încă nu există evaluări

- Altivar 212 ATV212HD37N4Document11 paginiAltivar 212 ATV212HD37N4MECHANICAL FACILITY KNOÎncă nu există evaluări

- 2SA2040/2SC5707: Bipolar TransistorDocument10 pagini2SA2040/2SC5707: Bipolar Transistorblueword66Încă nu există evaluări

- SPI Serial Memory: FeaturesDocument18 paginiSPI Serial Memory: Featuresoskita79Încă nu există evaluări

- SPI Serial Eeproms: FeaturesDocument15 paginiSPI Serial Eeproms: FeaturesMarcus SilvaÎncă nu există evaluări

- Huong Dan Ket Noi S7-200Document9 paginiHuong Dan Ket Noi S7-200duyphuocÎncă nu există evaluări

- Atmel 24C02Document26 paginiAtmel 24C02kukinjosÎncă nu există evaluări

- DatasheetDocument13 paginiDatasheetebertecnicoÎncă nu există evaluări

- 2SA2040 / 2SC5707: High Current Switching ApplicationsDocument5 pagini2SA2040 / 2SC5707: High Current Switching ApplicationsJrsproulsÎncă nu există evaluări

- 08 PLC-Zelio Logic I TwidoDocument31 pagini08 PLC-Zelio Logic I TwidoZakSaboÎncă nu există evaluări

- 50/144/430 MHZ 5W FM Transceiver: The Brightest Star in The Ham Radio GalaxyDocument4 pagini50/144/430 MHZ 5W FM Transceiver: The Brightest Star in The Ham Radio Galaxyasot99Încă nu există evaluări

- Sepam RelayDocument46 paginiSepam RelayLawrence AlexÎncă nu există evaluări

- At93c46d TH B AtmelDocument6 paginiAt93c46d TH B Atmelatorresh090675Încă nu există evaluări

- Infineon 6EDL04X0XXX DataSheet v02 08 EN-3160006Document22 paginiInfineon 6EDL04X0XXX DataSheet v02 08 EN-3160006Paresh PanchalÎncă nu există evaluări

- Servo Motion Price List AustDocument44 paginiServo Motion Price List Austtry_nguyenÎncă nu există evaluări

- DS1307 Real Time ClockDocument14 paginiDS1307 Real Time Clockpraveen_kodgirwarÎncă nu există evaluări

- SPI Serial Eeproms 8K (1024 X 8) 16K (2048 X 8) 32K (4096 X 8) 64K (8192 X 8) AT25080A AT25160A AT25320A AT25640A Not Recommended For New DesignDocument26 paginiSPI Serial Eeproms 8K (1024 X 8) 16K (2048 X 8) 32K (4096 X 8) 64K (8192 X 8) AT25080A AT25160A AT25320A AT25640A Not Recommended For New Designpatelilesh32Încă nu există evaluări

- S 24 Cs 08Document34 paginiS 24 Cs 08mj15015100% (1)

- RDP Se - P1N85898Document4 paginiRDP Se - P1N85898Danilo SilvaÎncă nu există evaluări

- Project XDocument44 paginiProject XBiren PatelÎncă nu există evaluări

- LV76213 3C PDFDocument6 paginiLV76213 3C PDFjdrsant100% (1)

- Fan 7711Document21 paginiFan 7711uumpÎncă nu există evaluări

- RT9202Document16 paginiRT9202bachet56Încă nu există evaluări

- H-V Sync To Comp SyncDocument9 paginiH-V Sync To Comp SyncAzmi PlgÎncă nu există evaluări

- AC W2 PowerDocument46 paginiAC W2 PowerLucas SimiÎncă nu există evaluări

- STM6700, STM6710: Low-Voltage, High-Accuracy, Triple/quad Voltage Microprocessor Supervisory Circuit in SOT PackageDocument20 paginiSTM6700, STM6710: Low-Voltage, High-Accuracy, Triple/quad Voltage Microprocessor Supervisory Circuit in SOT PackageFuck YourBullshitMandatoryAccountÎncă nu există evaluări

- Ads 7870Document43 paginiAds 7870Moorthy VenkatachalamÎncă nu există evaluări

- Calculation Battery Load 150 KVVVDocument8 paginiCalculation Battery Load 150 KVVVfirmanÎncă nu există evaluări

- FSDH0265RN, FSDM0265RN: Green Mode Fairchild Power Switch (FPS)Document20 paginiFSDH0265RN, FSDM0265RN: Green Mode Fairchild Power Switch (FPS)Wsad WsadÎncă nu există evaluări

- Altivar 71 Plus - ATV71ES5C16N4Document7 paginiAltivar 71 Plus - ATV71ES5C16N4Nemitha LakshanÎncă nu există evaluări

- DS1307 64 X 8, Serial, I C Real-Time Clock: General Description FeaturesDocument14 paginiDS1307 64 X 8, Serial, I C Real-Time Clock: General Description FeaturesAn TrìnhÎncă nu există evaluări

- Cmos Sram K6T1008C2E Family: Document TitleDocument11 paginiCmos Sram K6T1008C2E Family: Document TitleOmar LeonÎncă nu există evaluări

- SN65HVD147x 3.3-V Full-Duplex RS-485 Transceivers With 16-kV IEC ESDDocument42 paginiSN65HVD147x 3.3-V Full-Duplex RS-485 Transceivers With 16-kV IEC ESDJoseph BernardÎncă nu există evaluări

- STR W6735 DatasheetDocument13 paginiSTR W6735 DatasheetloagerÎncă nu există evaluări

- Atmel 24C02Document24 paginiAtmel 24C02chichedemorenoÎncă nu există evaluări

- Operational Amplifier Circuits: Analysis and DesignDe la EverandOperational Amplifier Circuits: Analysis and DesignEvaluare: 4.5 din 5 stele4.5/5 (2)

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSIDe la EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSIÎncă nu există evaluări

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsDe la EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsEvaluare: 3.5 din 5 stele3.5/5 (6)

- 6101 SchematicsDocument10 pagini6101 SchematicsanjirponselÎncă nu există evaluări

- Mobilchips: RM-94 Schematic DiagramsDocument9 paginiMobilchips: RM-94 Schematic DiagramsanjirponselÎncă nu există evaluări

- rqqhfwlrqvehwzhhq5) Dqg%%0Rgxohv: &&67Hfkqlfdo'Rfxphqwdwlrq 6Fkhpdwlfv/D/Rxwv') Ybd 1$0Document9 paginirqqhfwlrqvehwzhhq5) Dqg%%0Rgxohv: &&67Hfkqlfdo'Rfxphqwdwlrq 6Fkhpdwlfv/D/Rxwv') Ybd 1$0anjirponselÎncă nu există evaluări

- 6012 SchematicsDocument24 pagini6012 SchematicsDexter DanielÎncă nu există evaluări

- 2600 SchemDocument10 pagini2600 SchemDexter DanielÎncă nu există evaluări

- Block Diagram 1 (Ver.0.0 Ed.4) : &XVWRPHU&DUH6ROXWLRQV Company Confidential 6Fkhpdwlfv/D/Rxwv7%B 1+Document32 paginiBlock Diagram 1 (Ver.0.0 Ed.4) : &XVWRPHU&DUH6ROXWLRQV Company Confidential 6Fkhpdwlfv/D/Rxwv7%B 1+anjirponselÎncă nu există evaluări

- 08 Rm37 SchematicsDocument30 pagini08 Rm37 SchematicsanjirponselÎncă nu există evaluări

- RF - BB RF SYS: Top LevelDocument24 paginiRF - BB RF SYS: Top LevelanjirponselÎncă nu există evaluări

- Antenna Description and Troubleshooting: Nokia Customer Care 2125/2125i/2126/2126i/2128i (RH-71) Mobile TerminalsDocument12 paginiAntenna Description and Troubleshooting: Nokia Customer Care 2125/2125i/2126/2126i/2128i (RH-71) Mobile TerminalsanjirponselÎncă nu există evaluări

- RF Description and Troubleshooting: Nokia Customer Care 2125/2125i/2126/2126i/2128i (RH-71) Mobile TerminalsDocument50 paginiRF Description and Troubleshooting: Nokia Customer Care 2125/2125i/2126/2126i/2128i (RH-71) Mobile TerminalsanjirponselÎncă nu există evaluări

- Disassembly/Assembly: Nokia Customer Care 2125/2125i/2126/2126i/2128i (RH-71) Mobile TerminalsDocument8 paginiDisassembly/Assembly: Nokia Customer Care 2125/2125i/2126/2126i/2128i (RH-71) Mobile TerminalsanjirponselÎncă nu există evaluări

- Service Software Instructions: Nokia Customer Care 2125/2125i/2126/2126i/2128i (RH-71) Mobile TerminalsDocument10 paginiService Software Instructions: Nokia Customer Care 2125/2125i/2126/2126i/2128i (RH-71) Mobile TerminalsanjirponselÎncă nu există evaluări

- Block Diagram of Baseband: After Sales Technical Documentation System Module NHE-6Document24 paginiBlock Diagram of Baseband: After Sales Technical Documentation System Module NHE-6anjirponselÎncă nu există evaluări

- Connection Between RF and Baseband Modules: NSM-3 System Module RM7L PAMS Technical DocumentationDocument10 paginiConnection Between RF and Baseband Modules: NSM-3 System Module RM7L PAMS Technical DocumentationanjirponselÎncă nu există evaluări

- General Information: Nokia Customer Care 2125/2125i/2126/2126i/2128i (RH-71) Mobile TerminalsDocument4 paginiGeneral Information: Nokia Customer Care 2125/2125i/2126/2126i/2128i (RH-71) Mobile TerminalsanjirponselÎncă nu există evaluări

- Parts Lists and Exploded View: Nokia Customer Care 2125/2125i/2126/2126i/2128i (RH-71) Mobile TerminalsDocument34 paginiParts Lists and Exploded View: Nokia Customer Care 2125/2125i/2126/2126i/2128i (RH-71) Mobile TerminalsanjirponselÎncă nu există evaluări

- SGDA1800-180 CR1800 MAFS1800 Data Engenharia OrderWriteup and Quote Confg For Impulse GeneratorDocument9 paginiSGDA1800-180 CR1800 MAFS1800 Data Engenharia OrderWriteup and Quote Confg For Impulse GeneratorAlessandro SouzaÎncă nu există evaluări

- Model ResumeDocument3 paginiModel ResumeRith VinayakaÎncă nu există evaluări

- Fujitsu - ASIC/COT - 180nm CMOS Technology CS86 SeriesDocument2 paginiFujitsu - ASIC/COT - 180nm CMOS Technology CS86 SeriesFujitsu Semiconductor EuropeÎncă nu există evaluări

- JFo 8 4 PDFDocument44 paginiJFo 8 4 PDFAkbar WisnuÎncă nu există evaluări

- Sket Remot 2313Document8 paginiSket Remot 2313Amron Zamzami amronzamzami.2020Încă nu există evaluări

- Osg-Final Test - Key - NokeyDocument26 paginiOsg-Final Test - Key - NokeyshinkiriloveforeverÎncă nu există evaluări

- System Software and Compiler Design LaboratoryDocument33 paginiSystem Software and Compiler Design LaboratoryBeing FantasticÎncă nu există evaluări

- Dell Latitude E6430 Compal LA-7782PDocument66 paginiDell Latitude E6430 Compal LA-7782Pmattew188Încă nu există evaluări

- (+) Why Are Termination Networks in CAN Transceivers So Important - Industrial - Technical Articles - TI E2E Support ForumsDocument6 pagini(+) Why Are Termination Networks in CAN Transceivers So Important - Industrial - Technical Articles - TI E2E Support ForumsEdmundo FrazãoÎncă nu există evaluări

- MS1R 100381 Patient Monitor Service Manual V1 - 3Document94 paginiMS1R 100381 Patient Monitor Service Manual V1 - 3CamilaCubidesÎncă nu există evaluări

- FactoryTalk View Studio Internal Error or RSLinx Enterprise OPC Service ErrorDocument8 paginiFactoryTalk View Studio Internal Error or RSLinx Enterprise OPC Service Errorzulfikar rochimÎncă nu există evaluări

- Assessment: 5: Ite 2002-Operating Systems Lab Lab Assessment QuestionsDocument16 paginiAssessment: 5: Ite 2002-Operating Systems Lab Lab Assessment QuestionsARIHANT SAXENAÎncă nu există evaluări

- TADM70 QuestionDocument4 paginiTADM70 Questionmanish agrawalÎncă nu există evaluări

- Web-Activated Network Licenses PDFDocument3 paginiWeb-Activated Network Licenses PDFdinhquangmaniaÎncă nu există evaluări

- UA723Document6 paginiUA723Gheorghe DanielÎncă nu există evaluări

- Project ReportDocument9 paginiProject ReportJameelAhmedÎncă nu există evaluări

- Car Products & AccessoriesDocument2 paginiCar Products & AccessoriesRAJKUMARSCRIBD_123Încă nu există evaluări

- Control Engineering Magazine May 2021 1621425288Document54 paginiControl Engineering Magazine May 2021 1621425288JACK_LIVEÎncă nu există evaluări

- CS101L Manual V1.1Document184 paginiCS101L Manual V1.1Muaz ShafiqÎncă nu există evaluări

- Bit4201 Mobile Computing PDFDocument156 paginiBit4201 Mobile Computing PDFVictor NyanumbaÎncă nu există evaluări

- Week 4 Module 4 Graded QuizDocument6 paginiWeek 4 Module 4 Graded QuizFatih FidanÎncă nu există evaluări

- Ofm 11g Arch MNGMT Chapter 3 411767Document41 paginiOfm 11g Arch MNGMT Chapter 3 411767singhskÎncă nu există evaluări

- Hjet Key BindingsDocument6 paginiHjet Key BindingsCristianoVelosodeQueirozÎncă nu există evaluări

- Static Crosstalk-Noise AnalysisDocument127 paginiStatic Crosstalk-Noise AnalysisNguyễn Hưng Idiots100% (1)

- JUMO cTRON 04/08/16: Compact Controller With Timer and Ramp FunctionDocument68 paginiJUMO cTRON 04/08/16: Compact Controller With Timer and Ramp Functionrafik1995Încă nu există evaluări

- SVOA Clevo M570tu Schematic DiagramDocument100 paginiSVOA Clevo M570tu Schematic DiagramKneih LimÎncă nu există evaluări

- LUminex Mainframe Tape Encription Solution PDFDocument3 paginiLUminex Mainframe Tape Encription Solution PDFLizeth1967Încă nu există evaluări

- Remote Logging, Electronic Mail, and File TransferDocument48 paginiRemote Logging, Electronic Mail, and File TransferDHANYASRI BOLLAÎncă nu există evaluări

- Operator Unit RMZ790 - enDocument6 paginiOperator Unit RMZ790 - enUmit DemirÎncă nu există evaluări

- IoT Lab ManualDocument30 paginiIoT Lab ManualDIGVIJAY SINH CHAUHANÎncă nu există evaluări