Documente Academic

Documente Profesional

Documente Cultură

Dual Port RAM

Încărcat de

Abbas Raza ZaidiDescriere originală:

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Dual Port RAM

Încărcat de

Abbas Raza ZaidiDrepturi de autor:

Formate disponibile

Freescale Semiconductor

Application Note

AN2754 Rev. 1, 01/2005

CPM Architecture and Downloading RAM Microcodes on the PowerQUICC II Family

by NCSD Applications Freescale Semiconductor, Inc. East Kilbride, Scotland

All devices in the PowerQUICC II family of processors (MPC825x, MPC826x, MPC827x, and MPC828x) implement an integrated communication processor module (CPM). This CPM has a RISC microcontroller that supports downloadable RAM-based sets of instructions used by this microcontroller. These RAM-based microcodes are required to patch or modify existing code in ROM to support the following: CPM errata (bug) fixes New protocols Protocol enhancements to existing functionality in microcode ROM, for example ATM AAL2

1. 2. 3. 4. 5. 6. 7.

Contents References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 Silicon Revisions . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 CPM Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Download Procedure . . . . . . . . . . . . . . . . . . . . . . . . . 12 Example C Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Document Revision History . . . . . . . . . . . . . . . . . . . 13

This application note describes the CPM microcode architecture and the microcode download procedure. It also includes example C code for downloading RAM-based microcode onto different silicon revisions of the PowerQUICC II family.

Freescale Semiconductor, Inc., 2004. All rights reserved.

References

References

Table 1. References

Document Category Document Title MPC8260 PowerQUICC II Family Reference Manual Reference Manual MPC8280 PowerQUICC II Family Reference Manual MPC8272 PowerQUICC II Family Reference Manual Document ID MPC8260UM MPC8280RM MPC8272RM

Users are encouraged to consult the reference documentation in Table 1 for additional information.

Silicon Revisions

The internal memory register IMMR contains a read-only field called Mask_Num, which is programmed with a code corresponding to the mask number of the part on which the SIU is located. It is intended to help factory test and user code determine the silicon revision of the PQ2 device soldered on a PCB board which is sensitive to part changes. In addition associated with each version of CPM microcode, is number (REV_NUM) that uniquely identifies that specific microcode. This number is hard-coded into the microcode which is stored in the CPM's internal ROM. At power-up, the Communication Processor (CP) reads this number, and stores it into a miscellaneous portion of the CPM's internal dual-port RAM (DPRAM). The user can then access this location in DPRAM to determine which version of CPM microcode is contained in that device. Table 2 gives the IMMR[Mask_Num] and CPM microcode revision number for all PQ2 silicon revisions available

Table 2. Silicon Revision Information

Silicon Revision A.1 B.3 C.2 Mask 1K22A 3K23A 6K23A Process IMMR[1631] 1 0x0011 0x0023 0x0024 Rev_Num 2 0x0001 0x003B 0x007B

0.29 m HIP3 0.29 m HIP3 0.29 m HIP3

MPC826xA (HIP4) Derivatives including 8260A, 8264A, 8265A and 8266A A.0 B.1 2K25A 4K25A

0.25 m HIP4 0.25 m HIP4

0x0060 0x0062

0x000D 0x002D

MPC8275, MPC8270 and MPC8280 (HIP7) Derivatives 0.1

1

1K49A

0.13 m HIP7

0x0A00

0x0070

The IMMR[1631] indicates the mask number, which changes only when metal layers are modified. Located at offset 0x101A8. 2 The Rev_Num located at offset 0x8AF0 in DPRAM indicates the CPM microcode revision number.

CPM Architecture and Downloading RAM Microcodes on the PowerQUICC II Family, Rev. 1 2 Freescale Semiconductor

CPM Architecture

CPM Architecture

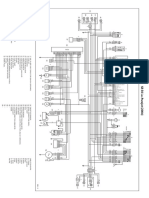

CP RISC microcontroller Dual-port RAM (DPRAM) ROM DMA unit Serial peripherals

Local Bus 60x Bus

A block diagram of the communication processor module (CPM) is given in Figure 1. The CPM consists of the following major components:

To SIU Interrupt Controller

Bus Interface

SDMA

Internal Bus

4 Timers Communications Processor ROM

Parallel I/O Ports

Dual-Port RAM

Baud Rate Generators Peripheral Bus

2 MCCs1

3 FCCs2

4 SCCs

2 SMCs

SPI

I2C

Serial Interface (SI), TC layer3, and Time-Slot Assigner (TSA) Note

1 One 2

MCC on the MPC8250, MPC8255, MPC8270, and MPC8275 Two FCCs on the MPC8255 3 MPC8264, MPC8266, and MPC8280 only

Figure 1. PowerQUICC II CPM Block Diagram

CPM Architecture and Downloading RAM Microcodes on the PowerQUICC II Family, Rev. 1 Freescale Semiconductor 3

CPM Architecture

3.1

RISC Microcontroller

The communications processor (CP), also called the RISC microcontroller, is a 32-bit controller for the CPM that resides on a separate bus from the G2 core, it can therefore perform tasks independently of the G2 core. The CP handles lower-layer communications tasks and DMA control, freeing the G2 core to handle higher-layer activities. The CP works with the peripheral controllers and parallel ports to implement user-programmable protocols and manage the serial DMA (SDMA) channels that transfer data between the I/O channels and memory. It also manages the IDMA (independent DMA) channels and contains an internal timer used to implement up to 16 additional software timers. The CP RISC is a request driven engine. Requests can be generated by peripherals, timers, or external commands. The CP RISC has a hardware block called the scheduler, responsible for storing requests and dispatching the appropriate task. When several requests are present at the same time, the one with the highest priority will be serviced. Since the CP RISC is request-driven, tasks are atomic and cannot preempt each other. The CPs architecture and instruction set are optimized for data communications and data processing required by many wire-line and wireless communications standards. An example of this is instructions that trigger CRC calculations of transmitted or received data, this provides a performance increase as these tasks are offloaded from the RISCs instruction set.

3.2

DPRAM

A custom, downloadable RAM microcode for the CP RISC Parameters used by peripherals Buffer descriptors for slow serials (SMC, SPI, I2C, and SCC) Temporary data

DPRAM can be accessed by either the CP RISC or the G2 core and is primarily used for storing any or all of the following:

The CPM has 24 Kbytes of DPRAM on 0.29-m (HiP3) devices and 32-Kbytes of DPRAM on 0.25-m (HiP4) devices. Figure 2 shows the memory map of dual-port RAM on 0.29-m (HiP3) devices and 0.25-m (HiP4) devices.

CPM Architecture and Downloading RAM Microcodes on the PowerQUICC II Family, Rev. 1 4 Freescale Semiconductor

CPM Architecture 0x0000 0x4000 0x8000

Bank 1 BD/Data/Code 2 Kbytes

Bank 13 Microcode 2 Kbytes1

Bank 9 Parameter RAM 2 Kbytes

0x0800

Bank 2 BD/Data/Code 2 Kbytes

0x4800

Bank 14 Microcode 2 Kbytes1

0x8800

Bank 10 Parameter RAM 2 Kbytes (Partially Reserved) Bank #11 BD/Data/Code 2 KBytes Bank #1 BD/Data/Code 2 KBytes Reserved Bank #1 BD/Data/Code 2 KBytes Bank #1 BD/Data/Code

0x1000

Bank 3 BD/Data/Code 2 Kbytes

0x5000

Bank 15 Microcode 2 Kbytes1

0x9000

0x1800

Bank 4 BD/Data/Code 2 Kbytes

0x5800

Bank 16 Microcode 2 Kbytes1

0x2000

Bank 5 BD/Data/Code 2 Kbytes

0x6000

0x2800

Bank 6 BD/Data/Code 2 Kbytes Reserved 0xB000

2 KBytes Bank 11 FCC Data 2 Kbytes 0xB800 Bank 12 FCC Data 2 Kbytes

0x3000

Bank 7 BD/Data 2 Kbytes

0x3800

Bank 8 BD/Data 2 Kbytes

Reserved on .29 m (HiP3) devices.

Figure 2. Dual-Port RAM (DPRAM) Memory Map

Only parameter RAM and RAM microcodes require fixed addresses to be used. Buffer descriptors, data buffers, and scratchpad RAM can be located in DPRAM or in any unused parameter RAM (that is, any area made available when a peripheral controller or sub-block is not being used). Note that buffer descriptors for the FCC and MCC protocols must reside in external memory on the 60x or local bus; the CPM accesses these BDs through an SDMA transaction. On 0.29 m (HiP3) devices, DPRAM is divided into twelve memory banks. The first 12 Kbytes (Banks 1 through 6) can be used for custom RAM microcode execution. RAM microcode has to start at the beginning of Bank 1, and it has to use subsequent banks. This means a RAM microcode could overlay an area of DPRAM required for MCC1 and MCC2 channel-specific parameters. For example, if a RAM microcode occupies the first 2 Kbytes of DPRAM, MCC1 channels 031 are no longer available. On 0.25-m (HiP4) devices, DPRAM is divided into sixteen memory banks. The first 12 Kbytes (Banks 1 through 6) can be used for custom RAM microcode execution. In addition, an extra 8 Kbytes of DPRAM (Banks 13 through 16) are available for microcode execution only and cannot be used for data buffers or BDs. Banks 7, 8, 11, and 12 of the DPRAM can be used for storing buffer descriptors, parameters, temporary data, or any data specific to a particular task.

CPM Architecture and Downloading RAM Microcodes on the PowerQUICC II Family, Rev. 1 Freescale Semiconductor 5

CPM Architecture

Therefore on HiP3 devices, 12 Kbytes of DPRAM starting at address IMMR + 0x0000 is available for RAM microcode downloads. On HiP4 devices, 20 Kbytes of DPRAM starting at address IMMR + 0x4000 (for the first 8 Kbytes) and address IMMR + 0x0000 (for the remaining 12 Kbytes) is available for RAM microcode downloads. On 0.13-m (HiP7) devices, the CPM has 64 Kbytes of static RAM. This RAM is divided into two 32-Kbyte blocks as follows: 32-Kbyte CP-RISC instruction RAM. This RAM is used to store a microcode package of up to 32-Kbyte instructions, and cannot be used for data buffers, BDs, or protocol parameters 32-Kbyte CP-RISC data RAM. This RAM is used to store CP-RISC parameter RAM and data structures as defined in the MPC8260 PowerQUICC II Family Reference Manual.

Figure 3 shows a memory map of the internal instruction RAM 0.13-m (HiP7) devices.

0X20000 Bank 1 CPM Instruction 0X20800 2K Bank 2 CPM Instruction 2K 0X21000 0X25000 Bank 3 CPM Instruction 2K 0X21800 0X25800 Bank 4 CPM Instruction 2K 0X22000 Bank 5 CPM Instruction 2K 0X22800 Bank 6 CPM Instruction 2K 0X23000 Bank 7 CPM Instruction 2K 0X23800 Bank 8 CPM Instruction 2K 0X27800 0X27000 0X26800 Bank 14 CPM Instruction/ Trace Buffer 2K Bank 15 CPM Instruction/ Trace Buffer 2K Bank 16 CPM Instruction / Trace Buffer 2K 0X26000 Bank 13 CPM Instruction/ Trace Buffer 2K Bank 12 CPM Instruction 2K Reserved Reserved Bank 11 CPM Instruction 2K 0X24800 Bank 10 CPM Instruction 2K 0X24000 0X28000 Bank 9 CPM Instruction 2K 0X2C000

Figure 3. Instruction RAM Partitioning

CPM Architecture and Downloading RAM Microcodes on the PowerQUICC II Family, Rev. 1 6 Freescale Semiconductor

CPM Architecture

Figure 4 shows a memory map of the internal data RAM on 0.13 m (HiP7) devices. Note that the addresses refer to CPU address space.

0X0000 Bank 1 BD / DATA 0X0800 2K 0X8800 Bank 2 BD / DATA 2K 0X1000 Bank 3 BD / DATA 2K 0X1800 Bank 4 BD / DATA 2K 0Xs00 Bank 5 BD / DATA 2K 0X2800 Bank 6 BD / DATA 2K 0X3000 Bank 7 BD / DATA 2K 0X3800 Bank 8 BD / DATA 2K 0XB800 0XB000 Bank 15 BD / DATA 2K Bank 16 BD / DATA 2K 0XA800 Bank 14 BD / DATA 2K Reserved 0XA000 Bank 13 BD / DATA 2K 0X9800 Bank 12 BD / DATA 2K Reserved 0X9000 Bank 11 BD / DATA 2K Bank 10 Parameter RAM 2K (Partly reserved for future serials) 0X4000 0X8000 Bank 9 Parameter RAM 2K 0XC000

Figure 4. Internal Data RAM Memory Map

The internal data RAM data bus is 64 bits wide. The RAM is used for five possible tasks: 1. To store parameters associated with the FCCs, SCCs, SMCs, SPI, I2C, and IDMAs in the 2,048-byte parameter RAM 2. To store the BDs that describe where data is to be received and transmitted on slow peripherals 3. To store parameters required to implement a given communications protocol, for example, APC tables when the FCC is running in ATM mode 4. Temporary storage between FCC FIFO and external memory for FCC data that is transferred by the block transfer module (BTM) which moves data between FCC FIFOs.

CPM Architecture and Downloading RAM Microcodes on the PowerQUICC II Family, Rev. 1 Freescale Semiconductor 7

CPM Architecture

5. For additional RAM space for user software Note that all banks of internal data RAM on 0.13-m (HiP7) devices are interleaved supporting concurrent accesses for improved performance. It is recommended that FCC, BTM, and SDMA-based parameters and APC parameters are placed in the interleaved banks of DPRAM. Table 3 summarizes which banks should contain these FCC parameters.

Table 3. Interleaved DPRAM Banks vs. Silicon Revision

Revision 0.29 m and 0.25 m (Hip3 and Hip4) 0.13 m (Hip7) DPRAM Banks For FCC-, BTM-, and SDMA-Based Parameters 7,8, 11, and 12 1, 2, 3, 4, 5, 6, 7, 8, 11, 12, 13, 14, 15, and 16

The following FCC parameters should therefore contain pointers to these banks. HDLC, Ethernet, and Transparent Mode: RIPTR and TIPTR ATM Mode: TCELL_TMP_BASE, RCELL_TMP_BASE, APC Tables, INT_RCT_BASE, INT_TCT_BASE, and INT_TCTE_BASE (if used) For AAL2: RxQD_Base_Int and CID_Mapping_Table_Base (assuming internal table)

3.3

ROM

ROM is reserved for the microcode developed by Freescale. This microcode implements several protocols such as HDLC, ATM, and Ethernet. The MPC8260 PowerQUICC II Family Reference Manual explains in detail the protocols implemented by the ROM microcode and provides information on how to use them.

3.4

DMA Unit

The DMA unit provides the CP RISC with access to additional memory located on either the PPC or local buses. When instructed, the DMA unit can transfer a block of data between dual-port RAM and external memory or vice versa, without intervention by the CP RISC.

3.5

Serial Peripherals

The CP RISC has access to the set of communication controllers through the peripheral bus. The peripheral bus is internal to the CPM and visible only to the CP RISC. The communication controllers have hardware specialized for handling various streams of data. Each FCC and each SCC has separate receive and transmit FIFOs. The FCC FIFOs are 192 bytes. The SCC FIFOs are 32 bytes. The SMCs, SPI, and I2C are all double-buffered, creating effective FIFO sizes of two characters. The MPC8260 PowerQUICC II Family Reference Manual gives a general overview of each type of controller as well as the information to properly configure them.

CPM Architecture and Downloading RAM Microcodes on the PowerQUICC II Family, Rev. 1 8 Freescale Semiconductor

Registers

4

4.1

Registers

RISC Configuration Control Register

The CP has an option to execute microcode from a portion of user RAM located in the DPRAM. In this mode, the CP fetches instructions from both the dual-port RAM and its own private ROM. This mode allows new protocols or enhancements to the PowerQUICC II to be added in the form of RAM microcode packages. The amount of DPRAM (number of banks) used for RAM microcodes is configured by setting the ERAM field of the RCCR register. RAM microcode has to be placed in the DPRAM prior to setting RCCR[ERAM]. As long as RCCR[ERAM] is set, banks selected for microcode can be accessed only by the CP RISC instruction fetcher. Attempts to access this RAM area through the RISC load/store bus, the PowerPC 60x slave, or the SDMA unit have no effect on the content of RAM. Reads are returned with arbitrary values, and writes are ignored. It is illegal to place any parameter in a locked portion of DPRAM. The reason for this behavior is explained by the CPMs dual-bus architecture. Instructions fetched from the banks of DPRAM, as selected by the setting of RCCR[ERAM], are transferred using an internal RAM instruction bus. All other data is transferred using the RISCs load/store bus, so in essence, the CP RISC is based on the Harvard architecture. This ensures that a new instruction is fetched each clock cycle regardless of whether the RAM data bus is busy. The RCCR[ERAM] settings for HiP3 and Hip4 devices to configure the CP to execute microcode from a portion of user RAM are shown in Table 4.

Table 4. RCCR [ERAM] Field Description for HiP3 and HiP4 Devices

Bits 1618 Name ERAM Description .29 m (HiP3) devices: Enable RAM microcode. Configure as instructed in the download process of a Freescale-supplied RAM microcode package. (For 25 m (HiP4) devices RCCR[ERAM] = [1619]. See the following for settings.) 000 Disable microcode program execution from the dual-port RAM. 001 Microcode uses the first 2 Kbytes of the dual-port RAM. 010 Microcode uses the first 4 Kbytes of the dual-port RAM. 011 Microcode uses the first 6 Kbytes of the dual-port RAM. 100 Microcode uses the first 8 Kbytes of the dual-port RAM. 101 Microcode uses the first 10 Kbytes of the dual-port RAM. 110 Microcode uses the first 12 Kbytes of the dual-port RAM. 111 Reserved

CPM Architecture and Downloading RAM Microcodes on the PowerQUICC II Family, Rev. 1 Freescale Semiconductor 9

Registers

Table 4. RCCR [ERAM] Field Description for HiP3 and HiP4 Devices (continued)

Bits 19 Name ERAM .29-m (HiP3) devices: Reserved .25-m (HiP4) devices: ERAM[1619].Enable RAM microcode. Configure as instructed in the download process of a Freescale-supplied RAM microcode package. 0000 Disable microcode program execution from the dual-port RAM. (That is, microcode execution starts at ROM address 0x0000 after reset.) In the following configurations, RAM microcode execution starts at address 0x0000 after reset: 0010 Microcode uses the first 2 Kbytes of the dual-port RAM + 8 Kbytes starting from 0x4000. 0100 Microcode uses the first 4 Kbytes of the dual-port RAM + 8 Kbytes starting from 0x4000. 0110 Microcode uses the first 6 Kbytes of the dual-port RAM + 8 Kbytes starting from 0x4000. 1000 Microcode uses the first 8 Kbytes of the dual-port RAM + 8 Kbytes starting from 0x4000. 1010 Microcode uses the first 10 Kbytes of the dual-port RAM + 8 Kbytes starting from 0x4000. 1100 Microcode uses the first 12 Kbytes of the dual-port RAM + 8 Kbytes starting from 0x4000. In the following configurations, microcode execution starts at RAM address 0x4000 after reset: 0011 Microcode uses 2 Kbytes starting from dual-port RAM address 0x4000. 0101 Microcode uses 4 Kbytes starting from dual-port RAM address 0x4000. 0111 Microcode uses 6 Kbytes starting from dual-port RAM address 0x4000. 1001 Microcode uses 8 Kbytes starting from dual-port RAM address 0x4000. All other configurations not listed are reserved. Description

The RCCR[ERAM] settings for HiP7 devices to configure the CP to run microcode from ROM or RAM are shown below in Table 5.

Table 5. RCCR [ERAM] Field Description for HiP7 Devices

Bits 1619 Name ERAM Description Enable RAM microcode. Configure this field as instructed during the downloading process of a Freescale-supplied RAM microcode package. Otherwise, it should not be used. 0000 Disable microcode program execution from the internal RAM. 0100 Microcode is executed from the Instruction RAM. Other combinations of these bits are not valid and must not be used.

4.2

Trap Registers

Trap registers allow the flow of microcode to be changed. Each trap register allows ROM code to be patched and has a dedicated RAM entry address. A match between the register contents and the program counter causes a trap to RAM. There are four trap registers on 0.29-m (HiP3) and 0.25-m (HiP4) devices. On 0.13-m (HiP7) devices there are eight trap registers.

CPM Architecture and Downloading RAM Microcodes on the PowerQUICC II Family, Rev. 1 10 Freescale Semiconductor

Registers

Table 6 below shows the number of trap registers available and their location in the internal memory map.

Table 6. Trap Registers

Register 1 RCCR[ERAM] RCTR1 RCTR2 RCTR3 RCTR4 RCTR5 RCTR6 RCTR7 RCTR8

1

Address Offset IMMR + 0x119C4 IMMR + 0x119CC IMMR + 0x119CE IMMR + 0x119D0 IMMR + 0x119D2 IMMR + 0x119B8 IMMR + 0x119BA IMMR + 0x119BC IMMR + 0x119BE

Trap registers 58 only available on 0.13-m

(HiP7) devices. Trap registers should be programmed to the value stated in the user download instructions accompanying the s record or C language array. Note that there are many advantages in this ROM/RAM-based microcode architecture. This allows custom microcode or enhancements to existing microcodes without the need for a PCB re-spin or another revision of silicon.

4.3

CPCR

The communication processor configuration register (CPCR) allows the G2 core to instruct the RISC to perform a pre-defined microcoded host command or host commands. This register usage is essential for proper configuration and operation of the CPM peripherals. Both the MCC- and FCC-based protocols must be provided an INIT command; otherwise, erratic operation will occur. When the G2 writes a command to this memory-mapped register, a request is placed in the RISC scheduler at a high priority (priority 4). This means that host commands take precedence over serial FIFO-based requests. These host commands are essential in order to give the application software full control over the communications tasks running on the CP RISC. For example, a host command could be issued to stop a particular protocol or channel and then another host command could be issued later in order to restart the protocol or even another protocol on the same serial channel. By using this register, the application can yield full control over the CP RISC.

CPM Architecture and Downloading RAM Microcodes on the PowerQUICC II Family, Rev. 1 Freescale Semiconductor 11

Download Procedure

Download Procedure

The RAM microcode package can be downloaded to PowerQUICC II silicon by completing Steps 1-5. There should not be any CPM activity until RAM microcode is downloaded (Steps 1-3) and enabled, via the trap registers (Step 4) and the RCCR (Step 5). 1. Clear RCCR[ERAM]. 2. Download the RAM microcode package provided in three formats as follows: ads script (Downloadable via internal low-level debugger) c array (To be added to user source code during initialization) s record (Binary file downloadable via debugger on the COP interface) 3. Users must ensure that software is downloaded to the correct address for IMMR. NOTE Silicon-specific starting address HiP3IMMR + 0x0000 HiP4IMMR + 0x4000 and/or IMMR +0x0000 HiP7IMMR + 0x20000 4. Set the RCCR[ERAM] according to the silicon revision and RAM microcode documentation. 5. Set trap registers according to the silicon revision and RAM microcode documentation. Users should never set trap registers without first locking the microcode by setting the RCCR[ERAM] field to the value instructed in the user download documentation.

Example C Code

This example C code for RAM microcode initialization was generated and compiled specifically to run on the MPC82xx FADS pilot board. However, it can be readily adapted to run on other hardware platforms. The source files implemented include two C files, two header files, and one assembly startup file as listed below. These files accompany this application note. download.cMain RAM microcode initialization C source file. ucode.cC arrays for RAM microcode (In this example microcode patch for errata CPM115) mpc82xx.hGeneral data structures for the FCC parameter RAM and internal memory map (IMMR) for the MPC82xx registers. netcomm.hHeader file containing global data type definitions. startup.sInitializes the stack, Instruction and Data Caches, Memory Management Unit (MMU), and local bus initialization.

CPM Architecture and Downloading RAM Microcodes on the PowerQUICC II Family, Rev. 1 12 Freescale Semiconductor

Document Revision History

The download.c driver uses certain functions to initialize and implement microcode initialization on the MPC82xx. The functions and their purpose are given in Table 7 below.

Table 7. download.c Functions

Function main() RevNum() LoadUCODE(DPR_BASE) SetRegs() GP1led() FlashGP1led() Purpose Responsible for calling the respective initialization routines. Generates internal memory map pointer, initializes RCCR and microcode trap registers. This function determines the silicon revision from the IMMR[Mask_Num] and CPM Revision Number. This function loads the correct RAM microcode patch using a C array for errata CPM115 based on the silicon revision. This function initializes the RCCR and microcode trap registers based on the silicon revision. Turns ON LED GP1 on MPC82xx FADs board Flashes ON / OFF LED GP1 on MPC82xx FADs board

Document Revision History

Table 8. Document Revision History

Rev. No. 1 0 Date 01/06/2005 09/25/2004 Substantive Change(s) Updated Section 5, Download Procedure. Made minor edits. Initial release of document.

Table 8 below provides a revision history on this document

CPM Architecture and Downloading RAM Microcodes on the PowerQUICC II Family, Rev. 1 Freescale Semiconductor 13

Document Revision History

THIS PAGE INTENTIONALLY LEFT BLANK

CPM Architecture and Downloading RAM Microcodes on the PowerQUICC II Family, Rev. 1 14 Freescale Semiconductor

Document Revision History

THIS PAGE INTENTIONALLY LEFT BLANK

CPM Architecture and Downloading RAM Microcodes on the PowerQUICC II Family, Rev. 1 Freescale Semiconductor 15

How to Reach Us:

Home Page: www.freescale.com email: support@freescale.com USA/Europe or Locations Not Listed: Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 (800) 521-6274 480-768-2130 support@freescale.com Europe, Middle East, and Africa: Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com Japan: Freescale Semiconductor Japan Ltd. Technical Information Center 3-20-1, Minami-Azabu, Minato-ku Tokyo 106-0047 Japan 0120 191014 +81 3 3440 3569 support.japan@freescale.com Asia/Pacific: Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate, Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com For Literature Requests Only: Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 (800) 441-2447 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@ hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document. Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Typical parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including Typicals must be validated for each customer application by customers technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part. Freescale and the Freescale logo are trademarks of Freescale Semiconductor, Inc. The PowerPC name is a trademark of IBM Corp. and is used under license. All other product or service names are the property of their respective owners.

Freescale Semiconductor, Inc. 2004.

AN2754 Rev. 1 01/2005

S-ar putea să vă placă și

- Tiva - C Tm4C123G Launchpad For Blinking Led: Name Aqdas Nadeem Reg. # 2017-Ee-410 MarksDocument6 paginiTiva - C Tm4C123G Launchpad For Blinking Led: Name Aqdas Nadeem Reg. # 2017-Ee-410 MarksSONAÎncă nu există evaluări

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.De la EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Încă nu există evaluări

- PIC16F8X: 8-Bit CMOS Flash/EEPROM MicrocontrollersDocument122 paginiPIC16F8X: 8-Bit CMOS Flash/EEPROM MicrocontrollerssebastienÎncă nu există evaluări

- C Programming for the PIC Microcontroller: Demystify Coding with Embedded ProgrammingDe la EverandC Programming for the PIC Microcontroller: Demystify Coding with Embedded ProgrammingÎncă nu există evaluări

- PIC16F8X: 8-Bit CMOS Flash/EEPROM MicrocontrollersDocument122 paginiPIC16F8X: 8-Bit CMOS Flash/EEPROM MicrocontrollersCagatay KaynakÎncă nu există evaluări

- ARM Microcontrollers Programming for Embedded SystemsDe la EverandARM Microcontrollers Programming for Embedded SystemsEvaluare: 5 din 5 stele5/5 (1)

- Project Report (Sample)Document80 paginiProject Report (Sample)Swapnith VarmaÎncă nu există evaluări

- PlayStation Architecture: Architecture of Consoles: A Practical Analysis, #6De la EverandPlayStation Architecture: Architecture of Consoles: A Practical Analysis, #6Încă nu există evaluări

- Image Capture Using PRP, Csi, and I C: Mc9328Mx21Document18 paginiImage Capture Using PRP, Csi, and I C: Mc9328Mx21Sharmili Nukapeyi NÎncă nu există evaluări

- Unit I Embedded Computing: 2 Marks QuestionsDocument28 paginiUnit I Embedded Computing: 2 Marks Questionslogu87Încă nu există evaluări

- ARM Micro Controller Differences Between Microprocessor and MicrocontrollerDocument18 paginiARM Micro Controller Differences Between Microprocessor and Microcontrollersrc e-solutionsÎncă nu există evaluări

- PC Engine / TurboGrafx-16 Architecture: Architecture of Consoles: A Practical Analysis, #16De la EverandPC Engine / TurboGrafx-16 Architecture: Architecture of Consoles: A Practical Analysis, #16Încă nu există evaluări

- DMA Controller For A Credit-Card Size Satellite Onboard ComputerDocument20 paginiDMA Controller For A Credit-Card Size Satellite Onboard ComputerRamanujam O SÎncă nu există evaluări

- Your Guide To Getting The STM32F427VIT6 32-Bit MicrocontrollerDocument5 paginiYour Guide To Getting The STM32F427VIT6 32-Bit MicrocontrollerjackÎncă nu există evaluări

- Digital Electronics, Computer Architecture and Microprocessor Design PrinciplesDe la EverandDigital Electronics, Computer Architecture and Microprocessor Design PrinciplesÎncă nu există evaluări

- Gsm-Gps Vehicle Theft Control SystemDocument78 paginiGsm-Gps Vehicle Theft Control SystemMrunalini Spandana100% (1)

- An Gen Cbus 868acode 2 1Document22 paginiAn Gen Cbus 868acode 2 1mojinjoÎncă nu există evaluări

- Dokumen - Tips Mastering Emmc Device Programming Mastering Emmc Device Programming How To MaximizeDocument19 paginiDokumen - Tips Mastering Emmc Device Programming Mastering Emmc Device Programming How To Maximizeisnain chainÎncă nu există evaluări

- Introduction To Programming STM32 ARM Cortex-M 32-Bit MicrocontrollersDocument13 paginiIntroduction To Programming STM32 ARM Cortex-M 32-Bit MicrocontrollersNanda KumarÎncă nu există evaluări

- EE6008 MBSDDocument34 paginiEE6008 MBSDHans John D'cruzÎncă nu există evaluări

- Micromite ManualDocument79 paginiMicromite ManualasdfQWERTÎncă nu există evaluări

- 3 RD ChapterDocument6 pagini3 RD ChaptergouttÎncă nu există evaluări

- C Programming of Microcontroller For Hobby RoboticsDocument14 paginiC Programming of Microcontroller For Hobby RoboticsCMPEÎncă nu există evaluări

- AbsolutelyDocument7 paginiAbsolutelyRonel BragaÎncă nu există evaluări

- Decode Mpeg-2 Video With Virtex FpgasDocument3 paginiDecode Mpeg-2 Video With Virtex FpgasBlesson GeorgeÎncă nu există evaluări

- Technical Note: Booting From Embedded MMCDocument16 paginiTechnical Note: Booting From Embedded MMCLeszek WisniewskiÎncă nu există evaluări

- Microchip 16-Bit PIC 24 BrochureDocument6 paginiMicrochip 16-Bit PIC 24 Brochureram_rpe14Încă nu există evaluări

- DSP Lab DemoDocument37 paginiDSP Lab Demosurendraloya99Încă nu există evaluări

- Chapter 1 Introduction To Microcontrollers - 2023Document64 paginiChapter 1 Introduction To Microcontrollers - 2023trucdo0411Încă nu există evaluări

- Motorola M6800 Programming Reference Manual M68PRM (D) Nov76Document130 paginiMotorola M6800 Programming Reference Manual M68PRM (D) Nov76LANREÎncă nu există evaluări

- Introduction To Arm ProcessorDocument10 paginiIntroduction To Arm Processorkeerthidhoni100% (1)

- 8051 Unit 1 NotesDocument19 pagini8051 Unit 1 NotesSOMESH B S100% (13)

- Module 1Document18 paginiModule 1Rohit AnejaÎncă nu există evaluări

- Solved Tutorial With Tiny Bugs27-8-12Document24 paginiSolved Tutorial With Tiny Bugs27-8-12WondosenEshetieÎncă nu există evaluări

- DocumentDocument64 paginiDocumentpallesreeja0% (1)

- MCES Group ActivityDocument55 paginiMCES Group ActivitykartiksdanÎncă nu există evaluări

- Arm Cortex M3Document66 paginiArm Cortex M3Hitarth ParikhÎncă nu există evaluări

- Mpc8349E Powerquicc™ Ii Pro Integrated Host Processor Hardware SpecificationsDocument88 paginiMpc8349E Powerquicc™ Ii Pro Integrated Host Processor Hardware Specificationscatsoithahuong84Încă nu există evaluări

- Atmel White Paper Introducing New Breed of Microcontrollers For 8-16-Bit ApplicationsDocument15 paginiAtmel White Paper Introducing New Breed of Microcontrollers For 8-16-Bit ApplicationsJim GunterÎncă nu există evaluări

- It 2354 QBDocument28 paginiIt 2354 QBlogu87Încă nu există evaluări

- Module 1 - 411Document43 paginiModule 1 - 411رفال الجهنيÎncă nu există evaluări

- A Microcontroller Is A Programmable Digital Processor With Necessary PeripheralsDocument77 paginiA Microcontroller Is A Programmable Digital Processor With Necessary PeripheralsPrem KumarÎncă nu există evaluări

- The MOS 6567/6569 Video Controller (VIC-II)Document52 paginiThe MOS 6567/6569 Video Controller (VIC-II)Zachary LeeÎncă nu există evaluări

- Pic 16 C 505Document85 paginiPic 16 C 505Joel LopezÎncă nu există evaluări

- i.MX23, i.MX25, and i.MX28Document52 paginii.MX23, i.MX25, and i.MX28samÎncă nu există evaluări

- PIC12C509ADocument113 paginiPIC12C509AsandrorrrÎncă nu există evaluări

- 14mte02 Embedded Programming For Mechatronics Systems: Course OutcomesDocument104 pagini14mte02 Embedded Programming For Mechatronics Systems: Course OutcomesHari PrasadÎncă nu există evaluări

- 2 MarksDocument30 pagini2 MarksAnitha Kumari SivathanuÎncă nu există evaluări

- 12C509Document85 pagini12C509Choco MalaÎncă nu există evaluări

- Overview of Microcontrollers, Embedded Control and The Motorola HC12 FamilyDocument15 paginiOverview of Microcontrollers, Embedded Control and The Motorola HC12 FamilyJuanÎncă nu există evaluări

- Unit 1Document44 paginiUnit 1TakeItEasyDude TIEDÎncă nu există evaluări

- Unit 1&2Document97 paginiUnit 1&2manoj3e9329Încă nu există evaluări

- Datasheet BCM2835 ARM PeripheralsDocument205 paginiDatasheet BCM2835 ARM PeripheralsrickyjamesÎncă nu există evaluări

- NUST Entry Test 2013 Sample PaperDocument3 paginiNUST Entry Test 2013 Sample PaperShawn Parker79% (29)

- CrateDB The DBMS For IoT.v2Document10 paginiCrateDB The DBMS For IoT.v2Amandio SilvaÎncă nu există evaluări

- DALI Application Note (Usefull)Document14 paginiDALI Application Note (Usefull)b42eluÎncă nu există evaluări

- Minimal Arm OsDocument38 paginiMinimal Arm OsAbbas Raza ZaidiÎncă nu există evaluări

- Porting U-Boot To Your Board: Top-Level BuildDocument8 paginiPorting U-Boot To Your Board: Top-Level BuildAbbas Raza ZaidiÎncă nu există evaluări

- Questions of IQ From NET-1 2014 Entry Test PreparationDocument4 paginiQuestions of IQ From NET-1 2014 Entry Test PreparationAbbas Raza Zaidi100% (4)

- Jerome TijaDocument30 paginiJerome TijaAbbas Raza ZaidiÎncă nu există evaluări

- Ohci 11Document210 paginiOhci 11Abbas Raza ZaidiÎncă nu există evaluări

- Building, Porting and Debugging YAMONDocument14 paginiBuilding, Porting and Debugging YAMONAbbas Raza ZaidiÎncă nu există evaluări

- Free Electrons LabsDocument46 paginiFree Electrons LabsAbbas Raza ZaidiÎncă nu există evaluări

- USB 2.0 Architecture OverviewDocument51 paginiUSB 2.0 Architecture OverviewAbbas Raza ZaidiÎncă nu există evaluări

- Beagleboard Manual Guide (For Dummies) : BorradorDocument23 paginiBeagleboard Manual Guide (For Dummies) : BorradorAbbas Raza ZaidiÎncă nu există evaluări

- Demo Program From Lecture #1: RegistersDocument15 paginiDemo Program From Lecture #1: RegistersNaresh BopparathiÎncă nu există evaluări

- Ehci r10Document155 paginiEhci r10Latha MurugappanÎncă nu există evaluări

- Interfacing The PC Serial Port RS232Document40 paginiInterfacing The PC Serial Port RS232Sneetsher Crispy100% (16)

- SawalatWaJawabat سوالات و جوابات از علامہ علی شرف الدین موسوی بلتستانیDocument99 paginiSawalatWaJawabat سوالات و جوابات از علامہ علی شرف الدین موسوی بلتستانیReviving Deen MovementÎncă nu există evaluări

- John Howard EhciDocument43 paginiJohn Howard EhciAbbas Raza ZaidiÎncă nu există evaluări

- GallstonesDocument3 paginiGallstonesAbbas Raza ZaidiÎncă nu există evaluări

- Usbch9 120606112347 Phpapp02Document169 paginiUsbch9 120606112347 Phpapp02Abbas Raza ZaidiÎncă nu există evaluări

- GS-Oolite Spec V1.14Document5 paginiGS-Oolite Spec V1.14Abbas Raza ZaidiÎncă nu există evaluări

- STA2X11Linux Drivers Rel 20120309Document25 paginiSTA2X11Linux Drivers Rel 20120309Abbas Raza ZaidiÎncă nu există evaluări

- 124152Document46 pagini124152Abbas Raza ZaidiÎncă nu există evaluări

- TOSHIBA SD Card SpecificationDocument50 paginiTOSHIBA SD Card Specificationnreddim2634Încă nu există evaluări

- DS 300 HB 40 80kVA Manual Industrial Three Phase UPS TescomDocument68 paginiDS 300 HB 40 80kVA Manual Industrial Three Phase UPS TescomSam OyelowoÎncă nu există evaluări

- GPU KhoruzhenkoDocument5 paginiGPU KhoruzhenkoOlhaÎncă nu există evaluări

- Ricoh GG 2017Document3.318 paginiRicoh GG 2017Acevedo OrlandoÎncă nu există evaluări

- DTB113ZKT146 PDFDocument6 paginiDTB113ZKT146 PDFshezad shezadÎncă nu există evaluări

- Item 1-3C X 6.0MM BLACKDocument1 paginăItem 1-3C X 6.0MM BLACKSyazwan AzharanÎncă nu există evaluări

- Lista Preliminarde ExpositoresDocument58 paginiLista Preliminarde Expositorestesting accountÎncă nu există evaluări

- Everdigm EHB30Document28 paginiEverdigm EHB30ALI RAZAVI100% (1)

- TL783 RegulatorDocument5 paginiTL783 RegulatorVenkatesh KarriÎncă nu există evaluări

- V"AJH13: Nunber of Swilchmg Are TrippmgDocument2 paginiV"AJH13: Nunber of Swilchmg Are TrippmgrizwanÎncă nu există evaluări

- DTSC-200A Product TrainingDocument45 paginiDTSC-200A Product TrainingEliyanto E BudiartoÎncă nu există evaluări

- Technical Handbook RAYCHEM PDFDocument60 paginiTechnical Handbook RAYCHEM PDFSINIŠA PRETKOVIĆÎncă nu există evaluări

- He O&mDocument9 paginiHe O&mAffez Anuar100% (1)

- Babylock BL18 SMDocument22 paginiBabylock BL18 SMDavid GarnerÎncă nu există evaluări

- MR615 Product GuideDocument16 paginiMR615 Product GuideDinesh RajaÎncă nu există evaluări

- Intertek UL 508A Standard UpdatesDocument2 paginiIntertek UL 508A Standard UpdatesWilfredo MolinaÎncă nu există evaluări

- Generator Protection PDFDocument162 paginiGenerator Protection PDFhemantgupta226100% (1)

- Chapter 25 Equipment - FurnishingDocument63 paginiChapter 25 Equipment - FurnishingHartomo DK.Încă nu există evaluări

- OBJECTIVE TYPE QUESTIONS AND ANSWERS FOR ETO - Electro Technical OfficerDocument39 paginiOBJECTIVE TYPE QUESTIONS AND ANSWERS FOR ETO - Electro Technical Officeramit100% (2)

- ACL TOP 500 Service Manual Rev 01Document764 paginiACL TOP 500 Service Manual Rev 01suny8781Încă nu există evaluări

- Aprilia SR50 Purejet Wiring Diagram 2004Document1 paginăAprilia SR50 Purejet Wiring Diagram 2004mylitter5391Încă nu există evaluări

- Foremost DR24HD - EnglishDocument9 paginiForemost DR24HD - EnglishJorge RodriguezÎncă nu există evaluări

- Model of Automatic Bottle Filling and Capping Mechanism: Logistics and Supply Chain ManagementDocument17 paginiModel of Automatic Bottle Filling and Capping Mechanism: Logistics and Supply Chain ManagementNguyễn QuỳnhÎncă nu există evaluări

- File 1438715980Document3 paginiFile 1438715980ical iculÎncă nu există evaluări

- NEW Atlanta DWV 2019 - 0 PDFDocument2 paginiNEW Atlanta DWV 2019 - 0 PDFjansenrosesÎncă nu există evaluări

- Inspection & Maintenance - IntroductionDocument16 paginiInspection & Maintenance - IntroductionJabbar RahmyÎncă nu există evaluări

- Motor Hidrostatico SauerDocument80 paginiMotor Hidrostatico SauerAlexis Peña100% (1)

- TLE Project ProposalDocument10 paginiTLE Project ProposalGine FrencilloÎncă nu există evaluări

- Important Factors Rotary Indexer: To Consider When Choosing ADocument5 paginiImportant Factors Rotary Indexer: To Consider When Choosing AManoj TiwariÎncă nu există evaluări

- SK-600I - Brochure (En) PDFDocument2 paginiSK-600I - Brochure (En) PDFZákány ZoltánÎncă nu există evaluări

- Manual Cargadores de Carros GolfDocument4 paginiManual Cargadores de Carros GolfLuis Carlos PerezÎncă nu există evaluări