Documente Academic

Documente Profesional

Documente Cultură

2 - FPGA Implementation of Pipelined 2D-DCT and Quantization Architecture For JPEG Image Compression.

Încărcat de

Mahesh MahiDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

2 - FPGA Implementation of Pipelined 2D-DCT and Quantization Architecture For JPEG Image Compression.

Încărcat de

Mahesh MahiDrepturi de autor:

Formate disponibile

FPGA Implementation of Pipelined 2D-DCT and Quantization Architecture for JPEG Image Compression

Enas Dhuhri Kusuma, Thomas Sri Widodo

Electrical Engineering Dept., Faculty of Engineering Gadjah Mada University Yogyakarta, Indonesia enas@te.ugm.ac.id, thomas@mti.ugm.ac.id

ABSTRACT Two dimensional DCT takes important role in JPEG image compression. Architecture and VHDL design of 2D DCT, combined with quantization and zig-zag arrangement, is described in this paper. The architecture is used in JPEG image compression. DCT calculation used in this paper is made using scaled DCT. The output of DCT module needs to be multiplied with post-scaler value to get the real DCT coefficients. Post-scaling process is done together with quantization process. 2-D DCT is computed by combining two 1-D DCT that connected by a transpose buffer. This design aimed to be implemented in cheap Spartan-3E XC3S500 FPGA. The 2-D DCT architecture uses 3174 gates, 1145 Slices, 21 I/O pins, and 11 multipliers of one Xilinx Spartan-3E XC3S500E FPGA and reaches an operating frequency of 84.81 MHz. One input block with 8 x 8 elements of 8 bits each is processed in 2470 ns and pipeline latency is 123 clock cycles . I. INTRODUCTION

II. DISCRETE COSINE TRANSFORM(DCT) Using DCT-2D, pixel values of a spatial image in the region will be transformed into a set of DCT coefficients in the frequency region. Before compression, image data in memory is divided into several blocks MCU (minimum code units). Each block consists of 8x8 pixels. Compression operations including DCT-2D in it will be done on each block [5]. Two dimensional DCT, because of its advantage in image compression, is an interesting research subject that invite many researcher [1] ,[2], [3], [4], [7] and others to participate in. That makes many algorithms of DCT is developed. A. 1-D Discrete Cosine Transform (DCT) There are several ways to compute 1-D DCT. It can be computed with straightforward computation just multiply input vector by raw DCT coefficients without any algorithm [3]. This method is fast but need large logic utilization, especially multiplier. The other ways is computing DCT with multiplier reduction algorithm [1],[2],[4]. Reduced multiplier means reduced complexity. FPGA chip usually has only a few multipliers. In this case, Spartan-3E XCS500E has only 20 multipliers. This paper adopts the work of Agostini [1] that implemented Arai scaled 1-D DCT algorithm [2]. It means the DCT coefficients produced by the algorithm are not the real coefficients. To get the real coefficients, the scaled ones must be multiplied with post-scaler value. Equation (1) is showing scaled 1-D DCT process. y' = C x Variable x is 8 point vector. C is Arai's DCT matrix and y' is vector of scaled DCT coefficients. To get the real DCT coefficients, y' must be element by element multiplicated with post-scaling factor. It is shown in (2). y = s .* y' (2) (1)

A. JPEG Image Compression Data compression method is different depending on the type of data. For information in the form of images, one of the most popular compression method is JPEG. JPEG stands for Joint Photographic Expert Group. According to Magli [5], widely used in JPEG image included on the internet web pages. Use JPEG create a web page with a picture can be accessed faster than a web page with an image without compression Color image JPEG compression consists of five steps [1]. This is shown in figure 1. The steps are: color space conversion, down sampling, 2-D DCT, quantization and entropy coding. Grayscale image compression uses only last three steps.

Figure 1 JPEG compression steps of color images However, this papers main interest is only on hardware implementation of 2-D DCT combined with quantization and zig-zag process. To achieve high throughput, this paper uses pipelined architecture, rather than single clock architecture designed by Basri et.al [4].

Constant s is vector of post-scaling factor. Element by element multiplication is shown with .*' operator adopted from MATLAB. Output vector y is the real DCT coefficients. The DCT matrix C will not be discussed in this paper. The complete 1D-DCT algorithm from Agostini el.al. [1] is presented in Table. 1, where:

978-1-4244-6716-7/10/$26.00 2010 IEEE

m1 = cos(4/16) m3 = cos(2/16) cos(6/16) m2 = cos(6/16) m4 = cos(2/16)+ cos(6 /16)) Table 1. 1D DCT Algorithm from Agostini et.al.[1] Step 1: a0 = x0 + x7 a1 = x1 + x6 a2 = x3 x4 a3 = x1 - x6 a4 = x2 + x5 a5 = x3 + x4 a6 = x2 x5 a7 = x0 x7 b 0 = a0 + a5 b 1 = a1 - a4 b 2 = a2 + a6 b 3 = a1 + a4 b 4 = a0 - a5 b 5 = a3 + a7 b 6 = a3 + a6 b 7 = a7 d0 = b0 + b3; d1 = b0 - b3; d2 = b2; d3 = b1 + b4; d4 = b2 - b5; d5 = b4; d6 = b5; d7 = b6; d8 = b7; e0 = d0; e1 = d1; e2 = m3 * d2; e3 = m1 * d7; e4 = m4 * d6; e5 = d5; e6 = m1 * d3; e7 = m2 * d4; e8 = d8; f0 = e0; f1 = e1; f2 = e5 + e6; f3 = e5 - e6; f4 = e3 + e8; f5 = e8 - e3; f6 = e2 + e7; f7 = e4 + e7; y'0 = f0; y'1 = f4 + f7; y'2 = f2; y'3 = f5 - f6; y'4 = f1; y'5 = f5 + f6; y'6 = f3; y'7 = f4 - f7;

c4 c7/c6 c6 /c4 c5/c2 s = c4 c3/c2 c2/c4 c1/c6

where cn = cos (n/16).

[]

(3)

B. Two Dimensional Discrete Cosine Transform (2DDCT) 2D-DCT is made from two 1D-DCT. Using DCT matrix, scaled 2D-DCT operation was shown in (4). Y'= [C] [X] [C]T X = 8x8 input matrix Y' =Scaled 2D-DCT 8x8 output matrix C = DCT matrix , same as matrix in equ. 1. To get 2D-DCT real value, Y' must be element by element multiplied by post-scaler as shown in (5). Now, the post-scaler is in matrix form. Y = [S].*[Y'] (5) (4)

Step 2:

Step 3:

with S = post scaler matrix and Y = real DCT coefficients. Post scaler matrix S is computed in (6). S = s sT (6)

Step 4:

C. Quantization Quantized output is made by divide each DCT coefficient by quantization value. It is done by doing element by element matrix multiplication between DCT output and quantization matrix as shown in (7) and (8). Yq = [Q] .*[Y] Yq = Q .* [S].*[Y'] (7) (8)

Step 5:

Step 6:

Since the image used in this paper is only grayscale picture, the quantization matrix applied is only for the luminance. The matrix was modified from [6] and postscaled by matrix S then multiplied with 212 to produce integer number in order to be applied in VHDL. The scaled quantization matrix was shown in (9).

The algorithm produces y' vector as scaled DCT coefficients from input vector x. The 1D DCT post-scaler in equ. 1, s vector is defined in (3). 978-1-4244-6716-7/10/$26.00(c)2010 IEEE

32 31 28 31 Q= 28 27 19 26

34 22 22 18 17 13 11 15

39 20 19 15 11 9 9 15

27 17 14 13 8 9 9 16

21 14 10 9 8 8 9 17

16 8 9 6 6 8 19 24

19 11 10 10 9 11 15 33

30 24 25 25 24 26 34 68

(9)

D. Zig-zag process Quantized output is sent sequentially byte-by-byte in zig-zag pattern. Zig-zag operation is done for every 8X8 block. The pattern is shown in figure 2 [6]. Numbers listed in the figure are the address of 64 data that is arranged in a zigzag pattern. 0 17 12 27 35 29 58 53 1 24 19 20 42 22 59 60 8 32 26 13 49 15 52 61 16 25 33 6 56 23 45 54 9 18 40 7 57 30 38 47 2 11 48 14 50 37 31 55 3 4 41 21 43 44 39 62 10 5 34 28 36 51 46 63

modules are similar but the bit widths at each module are different. The transpose buffer operates like a temporal barrier between the first and the second 1D DCT. It made from static RAM with two sets of data and address bus. One for read process and the other for write. C. 1D- DCT pipeline process Algorithm defined in table 1 from [1] is used to compute 1D-DCT. The algorithm itself has 6 steps. Since the DCT input/output has 8 points and data has to be entered and released in sequential manner, it takes 8 clock cycles for each input and output process. Totally, 8 points 1D-DCT computation needs 22 clock cycles. Design for data input and output in this paper is inspired by design from [7]. The input and output process visualization is shown in figure 5. The difference from system [1] is that it computes every single operation in a clock cycle, so every step needs 8 9 clock cycles. In this paper, system computes every step in a clock cycle, so DCT computation can be done faster.

data_in output registers Out 7 clock 22

Figure 2 Zig-zag pattern for output data

III.

FPGA IMPLEMENTATION

A. Entire System Block diagram of entire system to be implemented in FPGA is shown in figure 3. Input data is inserted into the system every 8 bit sequentially. Actually, many DCT designs insert the input to the DCT in parallel. For example is 8 x 8 bit [1],[3],[4]. This is ideal for DCT computing because it only consumes a clock cycle to insert data to 1D-DCT unit. With sequential manner, it takes 8 clock cycles to insert a set of data (8 points) to the DCT unit. The sequential architecture is chosen to save I/O port in FPGA chip. Some 2D-DCT intellectual property designs from Xilinx also use 8-bit input [10]. The 8-bit input architecture is also fit to many camera modules like OV9620. The camera module has 8-bit output [9]. 2D-DCT+ Quantization+ data_in (8 bit) zigzag en clk clr data_out (9 bit) rdy

clock 1

in 7

clock 2

in 6 8 points 1D -DCT process

Out 6

clock 21

clock 3

in 5

Out 5

clock 20

...

clock 8

...

in 0

...

...

...

Out 0

...

clock 15

Input registers

clock 9 - 14

data_out

Figure 3 Block representation of entire system B. System Architecture

in 8 bit 1D DCT addr in-t 11 bit TransPose buffer addr stat out-t 11 bit 1D DCT 13 bit Quantizer addr in-z 9 bit Zigzag buffer addr out-z out 9 bit

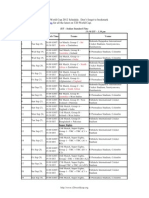

Figure 5 Data input/output process visualization of 8 points 1D-DCT 1D-DCT computation is done in pipeline process. The pipeline process is made in three stages. Thus, one pipeline stage is done in 8 clock cycles. The timing detail is described in table 2(a-c). Table 2 describes overall process including input, 2DDCT quantization zigzag, and output process. In pipeline mode, it is needed 24 clock cycles to complete overall process of quantized zigzag 2D DCT. Table 2a : process from 1st to 8th clock

clock Data-n stage 1 x0 = inp x1 = inp x2 = inp x3 = inp x4 = inp x5 = inp x6 = inp x7 = inp 2 3 1 0 2 1 3 2 4 3 5 4 6 5 7 6 8 7

stat

en

en

addr

controller

Figure 4 2D-DCT combined with zigzag and quantizer architecture The 2D-DCT architecture, combined with zigzag and quantization used in this paper is shown in Fig. 4. The 2DDCT module construction is modified from [7], that also puts the data sequentially into the module. Thus, the architecture of 2D-DCT was divided into two 1D DCT modules and one transpose buffer. The two 1D DCT 978-1-4244-6716-7/10/$26.00(c)2010 IEEE

Table 2b : process from 9th to 16th clock

clock Data-n stage 1 x0 = inp x1 = inp x2 = inp x3 = inp x4 = inp x5 = inp x6 = inp x7 = inp 2 step1 3 step2 step3 step4 step5 step6 outp=y0 outp=y1 9 8 10 9 11 10 12 11 13 12 14 13 15 14 16 15

(b) Table 2c : process from 17th to 24th clock

clock Data-n stage 1 x0 = inp x1 = inp x2 = inp x3 = inp x4 = inp x5 = inp x6 = inp x7 = inp 2 step1 step2 step3 step4 step5 step6 outp=y0 outp=y1 3 outp=y2 outp=y3 outp=y4 outp=y5 outp=y6 outp=y7 17 16 18 17 19 18 20 19 21 20 22 21 23 22 24 23

Figure 7 Input (a) and output (b) data of transpose buffer. Output data is generated in 65th sequence, count from first input entrance. The output of transpose buffer is fed directly to the input of second 1D-DCT unit. E. Quantizer Originally, quantization process in JPEG compression is done by divide every 2D-DCT coefficient by quantizing value from quantization table. To apply the operation in VHDL, division is converted into multiplication. The modified quantization table will be post-scaled with some post-scaling table. The post-scaled quantization table, written in matrix form in (9), is the table that will be applied to the VHDL code. To implement the quantization process, the output of 2D-DCT is multiplied by quantization value. The value is generated by quantization ROM that made for store the quantizing-post scaling value. Block Diagram of the implementation is shown in figure 8. F. Zigzag Buffer Like transpose buffer, zigzag buffer is made from static RAM. Its construction is like transpose buffer. It has two sets of data address bus. Input address bus is accessed by normal sequence, but output address is given some zigzag sequence described in figure 2. Zigzag address is generated by a zigzag ROM. The sequence is stored or preprogrammed in the ROM. When the ROM address bus is accessed by normal address sequence, ROM data bus will emit zigzag value. Figure 8 describe zigzag buffer and ROM construction in the system.

quantizer 2D-DCT Out (13 bit) Quantized Zigzag 2D-DCT coeff Zigzag buffer addr_out (7 bit) zigzag ROM Z_addr (7 bit) 9 bit

The 25th clock process and the following are the same as table 2c. From the table, it can be seen that first 1DDCT output from first data set (8 data) come at 15th clock and last output from first data set come at 22nd clock. Processes in step 1 6 are referred from table 1. D. Transpose Buffer Transpose buffer is static RAM, designed with two set of data and address bus. It has input and output dataaddress buses. The module block symbol is shown in fig. 6.

data_in (11 bit) addr_in (7 bit)

Transpose Buffer

data_out (11 bit) WE

addr_out (7 bit)

Figure 6 - Transpose buffer primitive symbol Data input come from output of first 1D-DCT. Address in, out, and WE (write enable) are generated from controller module. Input address is generated in normal sequence (0,1,2,3,4,5,6, , 63) but output address is generated in transposed sequence (0,8,16,24,32,40,48,56,1,9,17,..,55, 63). Output process begins after the entry of 64th input. It gives time latency between first input and first output. Figure 7a shows the first entry of transpose buffer input and 7b shows generated output sequence was delayed 65 clock cycles from first input.

9 bit

Q_value (12 bit) Quantizer ROM

addr_in (7 bit)

WE

Q_addr (6 bit)

controller

Figure 8 - Zigzag and Quantization Section (a)

978-1-4244-6716-7/10/$26.00(c)2010 IEEE

G. Implementation Result The 2-D DCT architecture was described in VHDL. This VHDL was synthesized into an Xilinx Spartan 3E family FPGA [8]. Nevertheless, there is a requirement to use this architecture. The FPGA must have at least 11 multipliers, because the system utilizes only internal multiplier. System is tested with real photographic image. Simulation results give the quantized 2D DCT coefficients. To verify the numerical result, the system is given by data from grayscale picture in figure 9. Data from the picture was converted to VHDL test bench. The result then compared to the result from MATLAB computation.

multiplier, it takes more slices to construct multiplier modules. Table 4 Device Utilization Using Xilinx Spartan-3E Logic Unit Number of Slices Number of Slices FFs

Number of 4 input LUTs Number of Bonded IOBs Number of Multipliers 18X18

Used 1145 1696 1750

21 11

Available 4656 9312 9312

232 20

Utilization 24% 18% 18%

9% 55%

Table 5 Device utilization comparison between this work and 2D-DCT designed in [3] Figure 9 Grayscale picture used as test bench Comparison result between VHDL and MATLAB computation of quantized 2D-DCT is enlisted in table 3. Generally, mean squared error between VHDL and nonrounded MATLAB result is 0.060552 for 64 data. Using figure 9 as sample, there is no error between VHDL and rounded MATLAB result. The result only displayed in table 3 only for 16 data. The complete synthesis results to Spartan-3E FPGA are presented in table 4, whose hardware was fit in an XCS500E device. The table 5 presents the comparison between this work (quantized 2D-DCT) and the pure 2DDCT designed in [3]. System designed in [3] uses Virtex FPGA and straightforward multiplication without special algorithm. Table 3 - Comparison between VHDL and MATLAB computation of quantized 2D-DCT (first 16 data) no vhdl matlab 0 1 2 3 4 5 6 7 1 -13 2 -3 3 18 8 6 matlab no rounded 1,25 18 -13 -13 9 1,81 2 10 -3,14 -3 11 2,54 3 12 18,23 18 13 8,4 8 14 5,6 6 15 vhdl matlab 3 1 -1 -2 -3 -3 -1 1 matlab rounded 2,72 3 1,44 1 -0,86 -1 -1,67 -2 -2,78 -3 -3,03 -3 -0,57 -1 0,61 1 Logic Unit Number Slices Number Slices FFs of of This work 1145 1696 1750

21 11

Presented in [3] 7260 9644 11194

101 -

Number of 4 input LUTs Number of Bonded IOBs Number of Multipliers 18X18

According to synthesis result, maximum time delay produced is 5.895 ns. That constraint yields minimum clock period 11.790 ns. Maximum clock frequency can be used is 84.818 MHz. Maximum delay synthesized is much smaller than delay produced in [4]. 1D-DCT designed in [4] yields maximum time delay 76.03 ns. System [4] uses fully parallel processing without clock to compute 8 points 1D-DCT. That system is used as comparison reference because it uses same FPGA with this system. Since the system in paper [3] uses Virtex FPGA that has higher frequency than Spartan, the delay is much smaller than this system and maximum frequency is higher. Maximum frequency in [3] is 308.182 MHz. This system is also faster than 2D-DCT described in [1]. System [1] has minimum period 82.1 ns. The use of pipeline process gives the system latency. The output exists several clock cycles after the first input. Latency produced in 2D-DCT is 94 clock cycles. Overall system (quantized and zigzag 2D-DCT) has latency 124 clock cycles. As comparison, 2D-DCT designed in [1] has latency 160 clock cycles. The better result reached by system in [3]. It takes 37 clock cycles as system latency to compute 2D-DCT.

System designed in [3] uses 64 bits input, so it takes more pins than system proposed in this paper. it also needs 8 multiplications in every single clock to compute 1D-DCT. So, to compute 2D-DCT via transpose buffer, it takes 16 multiplications. Because it doesnt use internal

978-1-4244-6716-7/10/$26.00(c)2010 IEEE

IV.

CONCLUSION

[1]

V. REFERENCES

L. Agostini, S. Bampi, Pipelined Fast 2-D DCT Architecture for JPEG Image Compression Proceedings of the 14th Annual Symposium on Integrated Circuits and Systems Design, Pirenopolis, Brazil. IEEE Computer Society 2001. pp 226-231. [2] Y. Arai, T. Agui, M. Nakajima. A Fast DCT-SQ Scheme for Images. Transactions of IEICE, vol. E71, n. 11, 1988, pp. 1095-1097. [3] D. Trang, N. Bihn, A High-Accuracy and High-Speed 2-D 8x8 Discrete Cosine Transform Design. Proceedings of ICGCRCICT 2010, vol. 1, 2010, pp. 135-138 [4] I. Basri, B. Sutopo, Implementasi 1D-DCT Algoritma FeigWinograd di FPGA Spartan-3E (Indonesian). Proceedings of CITEE 2009, vol. 1, 2009, pp. 198-203 [5] E. Magli, The JPEG Family of Coding Standard, Part of Document and Image Compression, New York: Taylor and Francis, 2004. [6] Wallace, G. K. ,''The JPEG Still Picture Compression Standard'', Communications of the ACM, Vol. 34, Issue 4, pp.30-44. 1991. [7] Sun, M., Ting C., and Albert M., VLSI Implementation of a 16 X 16 Discrete Cosine Transform, IEEE Transactions on Circuits and Systems, Vol. 36, No. 4, April 1989. [8] Xilinx, Inc., Spartan-3E FPGA Family : Data Sheet , Xilinx Corporation, 2009. [9] Omnivision, Inc., OV9620/9120 Camera Chip Data Sheet , Xilinx Corporation, 2002. [10] Xilinx, Inc., 2D Discrete Cosine Transform (DCT) V2.0 , Logicore Product Specification, Xilinx Corporation, 2002.

2D-DCT combined with quantization and zigzag buffer is designed using VHDL. System is tested with real grayscale image. The accuracy of computation is compared to Matlab computation result with similar operation. Comparison yields mean squared error MSE = 0. 060552, computed for 64 data. Pipeline process causes latency in the system. Latency produced from this system is 124 clock cycles. Maximum frequency can be achieved by this system is 84.818 MHz. Sequential pipeline design gives higher frequency than fully parallel design in [4]. The design takes 1145 slices, 1696 slice FF, and 1750 LUT including the control block that suitable for low cost FPGA like Xilinx XCS500E. The sequential operation of DCT saves much logic utilization in FPGA compared with [3]. Each step of DCT algorithm is executed on each clock cycle. Every step consists of 8-9 operation. It makes this design produces lower latency compared with [1].

978-1-4244-6716-7/10/$26.00(c)2010 IEEE

S-ar putea să vă placă și

- Active Disturbance Rejection Control for Nonlinear Systems: An IntroductionDe la EverandActive Disturbance Rejection Control for Nonlinear Systems: An IntroductionÎncă nu există evaluări

- Final Review DSPDocument17 paginiFinal Review DSPKota Krishna DheerajÎncă nu există evaluări

- Digital Communication Systems: ECE-4001 TASK-3Document12 paginiDigital Communication Systems: ECE-4001 TASK-3Aniket SaxenaÎncă nu există evaluări

- Computer OrganisationDocument71 paginiComputer OrganisationAnuragGuptaÎncă nu există evaluări

- (Signal Processing and Communications 13) Hu, Yu Hen - Programmable Digital Signal Processors - Architecture, Programming, and App PDFDocument386 pagini(Signal Processing and Communications 13) Hu, Yu Hen - Programmable Digital Signal Processors - Architecture, Programming, and App PDFGururaj BandaÎncă nu există evaluări

- Digital Signal Processors and Architectures (DSPA) Unit-2Document92 paginiDigital Signal Processors and Architectures (DSPA) Unit-2Chaitanya DuggineniÎncă nu există evaluări

- Design of Two-Stage Operational Amplifier: Shahin Shah (12116053), Abhinav Singhal (12116001)Document2 paginiDesign of Two-Stage Operational Amplifier: Shahin Shah (12116053), Abhinav Singhal (12116001)Shahin ShahÎncă nu există evaluări

- Design of 12-Bit DAC Using CMOS TechnologyDocument5 paginiDesign of 12-Bit DAC Using CMOS TechnologysanthoshÎncă nu există evaluări

- Low-Power and Area-Efficient Carry Select AdderDocument21 paginiLow-Power and Area-Efficient Carry Select AdderrajidisahithiÎncă nu există evaluări

- Gm7u PLCDocument10 paginiGm7u PLCedgarcooÎncă nu există evaluări

- Low Power Nine-Bit Sigma-Delta ADC Design Using TSMC 0.18micron TechnologyDocument5 paginiLow Power Nine-Bit Sigma-Delta ADC Design Using TSMC 0.18micron Technologyeditor_ijtel100% (1)

- VTU Computer Organization -Solution (18cs34Document19 paginiVTU Computer Organization -Solution (18cs34Pushpit AgrawalÎncă nu există evaluări

- Tiger SHARC ProcessorDocument36 paginiTiger SHARC ProcessorChintan PatelÎncă nu există evaluări

- Logic Exam - Bank Questions - Assuit UniversityDocument10 paginiLogic Exam - Bank Questions - Assuit Universityعبدالرحمن العجانÎncă nu există evaluări

- Unit 3 Programmable Digital Signal ProcessorsDocument25 paginiUnit 3 Programmable Digital Signal ProcessorsPreetham SaigalÎncă nu există evaluări

- DLD GTU Question Bank: Chapter-1 Binary SystemDocument5 paginiDLD GTU Question Bank: Chapter-1 Binary Systemnirav34Încă nu există evaluări

- Design, Fabrication and Testing of Analog IC AmplifiersDocument17 paginiDesign, Fabrication and Testing of Analog IC AmplifiersNurul Hanim HashimÎncă nu există evaluări

- 8.4 A Case Study: Using LCD Module On DE2 BoardDocument19 pagini8.4 A Case Study: Using LCD Module On DE2 BoardMas Shari0% (1)

- BK4811B Datasheet V1.2Document37 paginiBK4811B Datasheet V1.2BradMorse50% (2)

- Amplifier Project GradDocument5 paginiAmplifier Project Gradمحمد قاسم نفل سميرÎncă nu există evaluări

- CMOS Design RulesDocument21 paginiCMOS Design Rulesrakheep123Încă nu există evaluări

- Design and Implementation of High Gain, High Bandwidth CMOS Folded Cascode Operational Transconductance AmplifierDocument5 paginiDesign and Implementation of High Gain, High Bandwidth CMOS Folded Cascode Operational Transconductance AmplifierChristian Montano GalvezÎncă nu există evaluări

- High-Speed Area-Efficient VLSI Architecture of Three-Operand Binary AdderDocument10 paginiHigh-Speed Area-Efficient VLSI Architecture of Three-Operand Binary AdderM.Gopi krishnaÎncă nu există evaluări

- Neopis Frtu For LBS, Sectionalizer Epic-D300 Cat v2.4Document10 paginiNeopis Frtu For LBS, Sectionalizer Epic-D300 Cat v2.4Ngoc QuyenÎncă nu există evaluări

- 8k Bit Using 6t SramDocument8 pagini8k Bit Using 6t SramSwati Navdeep AggarwalÎncă nu există evaluări

- Introduction To Cmos Vlsi Design: Silicon-on-Insulator (SOI)Document27 paginiIntroduction To Cmos Vlsi Design: Silicon-on-Insulator (SOI)TygerYashanshuÎncă nu există evaluări

- Cmos Two Stage OpamppublishedDocument5 paginiCmos Two Stage Opamppublisheddeepak pandeyÎncă nu există evaluări

- Micro MouseDocument17 paginiMicro MouseFarshad yazdiÎncă nu există evaluări

- CS 8491 Computer ArchitectureDocument103 paginiCS 8491 Computer ArchitectureMUKESH KUMAR P 2019-2023 CSEÎncă nu există evaluări

- Dayananda Sagar College of Engineering: Mini-Project Report (Microprocessors)Document13 paginiDayananda Sagar College of Engineering: Mini-Project Report (Microprocessors)Nandan MaheshÎncă nu există evaluări

- MidtermsolutionsDocument3 paginiMidtermsolutionsRajini GuttiÎncă nu există evaluări

- Next - Js v14 DocumentationDocument739 paginiNext - Js v14 DocumentationDavid UkelereÎncă nu există evaluări

- Design and Implement of QPSK Modem Based On FPGADocument3 paginiDesign and Implement of QPSK Modem Based On FPGAAnil PatilÎncă nu există evaluări

- Resistor IC Design LayoutDocument120 paginiResistor IC Design LayoutTimothyAmadoÎncă nu există evaluări

- Performance Analysis of A Low-Power High-Speed Hybrid 1-Bit Full Adder Circuit Using Cmos Technologies Using CadanceDocument8 paginiPerformance Analysis of A Low-Power High-Speed Hybrid 1-Bit Full Adder Circuit Using Cmos Technologies Using CadanceAnonymous kw8Yrp0R5r100% (1)

- ECE3003 M A 2018: Icrocontroller and Its Applications SsignmentDocument43 paginiECE3003 M A 2018: Icrocontroller and Its Applications SsignmentAayoshi DuttaÎncă nu există evaluări

- Error Tolerant AddersDocument21 paginiError Tolerant AddersLibya ThomasÎncă nu există evaluări

- Anti FuseDocument2 paginiAnti FuseRahmatullah JatoiÎncă nu există evaluări

- Interfacing Keypad and LCD with PIC18F452Document11 paginiInterfacing Keypad and LCD with PIC18F452hira NawazÎncă nu există evaluări

- Xact UserDocument268 paginiXact Userwenyuchen96Încă nu există evaluări

- Modified Dual-Coupled Linear Congruential Generator Based Pseudorandom Bit GeneratorDocument11 paginiModified Dual-Coupled Linear Congruential Generator Based Pseudorandom Bit GeneratorGanesamoorthy BÎncă nu există evaluări

- TMS320F2812-Serial Communication InterfaceDocument28 paginiTMS320F2812-Serial Communication InterfacePantech ProLabs India Pvt Ltd75% (4)

- Unit 5 - A CASE STUDY - Using Pic MicrocontrollerDocument33 paginiUnit 5 - A CASE STUDY - Using Pic MicrocontrollerPoonthalirÎncă nu există evaluări

- Intelligent Line-Following Robot ProjectDocument7 paginiIntelligent Line-Following Robot ProjectAmla SingÎncă nu există evaluări

- CJ MCQDocument98 paginiCJ MCQMOHAMED SHAFEEÎncă nu există evaluări

- LPC2148 User ManualDocument62 paginiLPC2148 User ManualAri Krishnan0% (2)

- DSP Processor and ArchitectureDocument45 paginiDSP Processor and ArchitectureAlemayehu AsmareÎncă nu există evaluări

- Digital Integrated Circuits: A Design PerspectiveDocument113 paginiDigital Integrated Circuits: A Design Perspectiveapi-127299018Încă nu există evaluări

- Ee 215 ADocument8 paginiEe 215 AArjun Singhal100% (1)

- EMPro Workshop - Module1 - Introduction Version 2.0Document11 paginiEMPro Workshop - Module1 - Introduction Version 2.0Jagan RajagopalanÎncă nu există evaluări

- AVR DAC 328 TutorialDocument5 paginiAVR DAC 328 Tutorialsutekidane7435Încă nu există evaluări

- How To Interfacing Sensor With LPC2148 ARMDocument8 paginiHow To Interfacing Sensor With LPC2148 ARMSubir MaityÎncă nu există evaluări

- ECE 3002 VLSI Lab Task - D Latch and D Flip Flop CharacterizationDocument11 paginiECE 3002 VLSI Lab Task - D Latch and D Flip Flop CharacterizationKotha Hemanth100% (1)

- Lab10 Veriloga Adc TutorialDocument10 paginiLab10 Veriloga Adc TutorialmaxsilverÎncă nu există evaluări

- Systemc-Ams Tutorial: Institute of Computer Technology Vienna University of Technology Markus DammDocument26 paginiSystemc-Ams Tutorial: Institute of Computer Technology Vienna University of Technology Markus DammAamir HabibÎncă nu există evaluări

- Introduction To Sigma Delta ConvertersDocument72 paginiIntroduction To Sigma Delta Convertershjtseng1974100% (1)

- Two-Stage Operational Amplifier Design Using Gm/Id MethodDocument7 paginiTwo-Stage Operational Amplifier Design Using Gm/Id Methodabhinav kumarÎncă nu există evaluări

- Question PDFDocument12 paginiQuestion PDFjushwanth100% (1)

- Seven Segment Display Document PDFDocument16 paginiSeven Segment Display Document PDFRekha MudalagiriÎncă nu există evaluări

- Efficient Implementation of Low Power 2-D DCT ArchitectureDocument6 paginiEfficient Implementation of Low Power 2-D DCT ArchitectureIJMERÎncă nu există evaluări

- Modern Digital and Analog Communications Systems - Third Edition - B P LathiDocument399 paginiModern Digital and Analog Communications Systems - Third Edition - B P LathiRahim Khan100% (1)

- ItDocument1 paginăItMahesh MahiÎncă nu există evaluări

- ResumeDocument2 paginiResumeMahesh MahiÎncă nu există evaluări

- 8 Viterbi DecoderDocument3 pagini8 Viterbi DecoderMahesh MahiÎncă nu există evaluări

- ItDocument1 paginăItMahesh MahiÎncă nu există evaluări

- ItDocument1 paginăItMahesh MahiÎncă nu există evaluări

- ItDocument1 paginăItMahesh MahiÎncă nu există evaluări

- ItDocument1 paginăItMahesh MahiÎncă nu există evaluări

- ItDocument1 paginăItMahesh MahiÎncă nu există evaluări

- ItDocument1 paginăItMahesh MahiÎncă nu există evaluări

- ItDocument1 paginăItMahesh MahiÎncă nu există evaluări

- PostDocument1 paginăPostMahesh MahiÎncă nu există evaluări

- ItDocument1 paginăItMahesh MahiÎncă nu există evaluări

- New Microsoft Office Word DocumentDocument1 paginăNew Microsoft Office Word DocumentMahesh MahiÎncă nu există evaluări

- Schedule of ICC T20 World Cup 2012Document2 paginiSchedule of ICC T20 World Cup 2012Mahesh MahiÎncă nu există evaluări

- Tmahesh (TDS Alcatel 50)Document1 paginăTmahesh (TDS Alcatel 50)Mahesh MahiÎncă nu există evaluări

- Introduction To The Tmslf2407 DSP Controller: By: Dr. Dheeraj Joshi Associate ProfessorDocument17 paginiIntroduction To The Tmslf2407 DSP Controller: By: Dr. Dheeraj Joshi Associate ProfessorSameer SharmaÎncă nu există evaluări

- E7125v1 0Document135 paginiE7125v1 0uti12345Încă nu există evaluări

- Intel DP67DE Product GuideDocument78 paginiIntel DP67DE Product GuideStewart LaneÎncă nu există evaluări

- Unit 7 8279Document47 paginiUnit 7 8279subramanyam62Încă nu există evaluări

- Cortex-M4 Reference ManualDocument109 paginiCortex-M4 Reference ManualMustafa AkdenizÎncă nu există evaluări

- PL-2303 USB to Serial Install GuideDocument9 paginiPL-2303 USB to Serial Install GuideGraham WellingtonÎncă nu există evaluări

- Vinafix - VN - Quanta I5 U81Document37 paginiVinafix - VN - Quanta I5 U81psapwellÎncă nu există evaluări

- Fundamental of ComputerDocument2 paginiFundamental of ComputerDeep Raj JangidÎncă nu există evaluări

- Calcmet 4030 STD PRO Software Technical Data (v1.1)Document2 paginiCalcmet 4030 STD PRO Software Technical Data (v1.1)salekojic5332Încă nu există evaluări

- NGX BlueBoard LPC1768 H v2.0 PDFDocument8 paginiNGX BlueBoard LPC1768 H v2.0 PDFGuille RivasÎncă nu există evaluări

- Bscit 403Document3 paginiBscit 403api-3782519Încă nu există evaluări

- B57diag PDFDocument122 paginiB57diag PDFmjpandiaÎncă nu există evaluări

- Microprocessor - IntroductionDocument20 paginiMicroprocessor - IntroductionTanveer Ahmed HakroÎncă nu există evaluări

- Adv. Deld 3Document14 paginiAdv. Deld 3Kirti GuptaÎncă nu există evaluări

- ARM Instruction SetDocument29 paginiARM Instruction SetNeeshank MahajanÎncă nu există evaluări

- Multiprocessor System On ChipsDocument42 paginiMultiprocessor System On ChipsringopowÎncă nu există evaluări

- CP1E CPU Unit Software Users ManualDocument274 paginiCP1E CPU Unit Software Users ManualkabotalajuÎncă nu există evaluări

- 01 IntroductionDocument26 pagini01 IntroductionDaniel CrashOverride ShaferÎncă nu există evaluări

- COMPUTER ORGANIZATION SOLUTIONSDocument4 paginiCOMPUTER ORGANIZATION SOLUTIONSSai PrasadÎncă nu există evaluări

- Power Macintosh 5500Document2 paginiPower Macintosh 5500scriÎncă nu există evaluări

- ASIC-System On Chip-VLSI Design - Power PlanningDocument5 paginiASIC-System On Chip-VLSI Design - Power PlanningSumanth VarmaÎncă nu există evaluări

- PSR Ratio, Active Filter, Resolution, Logic FamilyDocument2 paginiPSR Ratio, Active Filter, Resolution, Logic FamilyNamaswini SureshÎncă nu există evaluări

- Difference Between Cache and BufferDocument2 paginiDifference Between Cache and BufferFrancesHsiehÎncă nu există evaluări

- Jy 997 D 26101 BDocument208 paginiJy 997 D 26101 BAgha Ali KhanÎncă nu există evaluări

- LNL TS 2220Document2 paginiLNL TS 2220David YHÎncă nu există evaluări

- CD54/74HC367, CD54/74HCT367, CD54/74HC368, CD74HCT368Document17 paginiCD54/74HC367, CD54/74HCT367, CD54/74HC368, CD74HCT368Cristian C. OlayaÎncă nu există evaluări

- Standard CellDocument53 paginiStandard CellShwethÎncă nu există evaluări

- 1166 DatasheetDocument4 pagini1166 DatasheetDivyanshu ShekharÎncă nu există evaluări

- Invoice - Noni CalvoDocument1 paginăInvoice - Noni Calvoapi-320418610Încă nu există evaluări