Documente Academic

Documente Profesional

Documente Cultură

Ies 11980 Only BJT

Încărcat de

Gaurav ShrimaliTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Ies 11980 Only BJT

Încărcat de

Gaurav ShrimaliDrepturi de autor:

Formate disponibile

CHAPTER 4 -

BIPOLAR JUNCTION TRANSISTOR

1980

1. Give reasons for the following (a) In a high junction transistor, the collector region has the highest resistivity and the emitter region has the lowest resistivity, the base region resistivity being in between. 2. Sketch the output V-I characteristics of an NPN transistor in common-emitter operation and indicate there on the different regions of importance. Explain how you would use these characteristics to determine hFE, ICBO and BVCBO of the transistor. 3. A silicon junction transistor operating at IE = 1 mA, VCE = 3V, has base-collector capacitory of 2 pf and base- emitter capacitance of 18pf. Determine the current gain bandwidth kT/q = 26mV at normal room temperature]

1981

1. Explain the following, with neat sketches wherever necessary: (a) Input and output V-I characteristics of a junction transistor. 2. Define the following terms relating to a bipolar transistor: (i) B VCEO (ii) fr (iii) Fmax (iv) Risc time (v) Storage time 3. A silicon n-p-n transistor with, hFE = 100 ICBO = 0.1 A. Calculate the IC for this transistor under following base circuit conditions: (i) IB = 0 (ii) IB = 20 A (iii) VBE = 0 (iv) VCB = 0. 4. Draw the Ebers Moll model for a bipolar transistor. And using this, show that the collector- emitter voltage drop of a saturated transistor is higher in the normal mode of operation than in the inverted mode of operation of the transistor. What is the practical use of this result?

1983

1. PROVE/ELABRATE the following: (i) Cut-off voltages of a silicon transistor and a germanium transistor.

2. For a small signal low frequency operation, write down v, I equations in terms of h parameters for common emitter (CE) configuration of a transistor. There from find out expressions for h parameters. 3. Draw an approximate h parameter model of a CE transistor configuration driven by voltage source R0 = 0, Ignore hre and hoe. Consider RL and RE as resistances in collector and emitter respectively.

4. The stability factor S for a transistor is defined as rate of change of collector current with respect to reverse saturation current. A CE configuration of a transistor utilizes self or emitter bias. Draw the circuit and derive the expression for the stability factor.

1984

1. The silicon transistor as connected in figure below has a minimum value of hFB of 30. +12V Ze E VA Is Z0 Q

100K

2K V0

12V

(a) If input voltage vi= 12 volts, show that the transistor is in Saturation. (b) If input voltage vi = 0.4 volt, show that the transistor is in cut-off. (c) For the case (b) find the maximum temperature at which the transistor remain just cut-off. Assume ICBO of 10 nano-amperes at 25 degrees Centigrade and doubles for every 10 degrees Centigrade rise in temperature.

1985

1. Draw the complete hybrid-vs equivalent circuit of a transistor and find an expression for the short-circuit current gain

1986

1. Sketch five different connections in which a bipolar junction transistor can be used as a diode. Determine the series resistance in each case, if the given transistor can be represented by the equivalent circuit shown in Fig. Q.2 (b). Which of these five connection has the lowest series resistance? Colloctor

rc Ic =Ib Ideal Transistor Actual Transistor

rb Base

Ib 2. The circuit shown in fig. 3(a) is known as a VBE multiplier, justify this by deriving an Emitter

expression for VA. Draw a sketch of VA versus I0. Identify clearly the regions in which Q is ON and Q is OFF. Q + VCC I

Ic = Ib R1 Q R2 Ib + VA -

3. In the circuit of Fig. 4(c), Q1 and Q2 are identical. Find I2 in the term of I0

+ Vcc R I0 I2 = 1b Q2 Ib

Q1

1987

1. Define the terms f , f and f as applied to a transistor and establish the relations between them 2. What do you mean by saturation of a transistor? In the circuit show in Fig. Q.2a, determine VDB to saturate the transistor. Assume VCE sat =0.1, Vgsat = 0.6V and hFE = 50 + 12 1 K 10 K

VBB

Fig. 2(a) 3. State and prove Millers theorem, Apply it to unilaterlize the hybrid equivalent circuit of a common emitter amplifier with a resistive load. State clearly the assumptions involved.

1988

1. Both emitter and collector junctions of a transistor are reverse biased by about 2 volts. Assume ICO (reverse saturation current of the collector-base diode) = 6 A, IEO(reverse saturation current of the emitter base diode) = 2 A, and (Emitter and collector currents). Note that I ICO = N IEO , where N and respectively, the common-base current gain under normal and reverse operations.

= 0.96 . Find IE and IC

are,

1989

1. You are given a transistor whose terminals are unmarked. State how you will determine if it is a pnp or npn transistor and identify all three terminals using only a multimeter. 2. An npn transistor with aN =0.98, ICO=2 a and IEO=1.6 a is used in a common emitter configuration with VCC = 12 and RC=4k. Find minimum base current required to saturate the transistor and the voltage across each junction. Neglect VVE(sat). 3. In the circuit shown, Q1 and Q2 are identical transistors with current gain and Q2 has current gain . Determine the relation between I2 and Io. ( IES-EC-89)(17Marks)

I0

R O3 Iz 1991

1. A transistor exhibits a change of 0.99 mA in its collector current for a change of 1.0mA O2 O in its emitter current.1 Calculate its common-base and common-emitter short-circuit

current gains.

1993

1. .A transistor used in the amplifier circuit show in Fig. 3(a) has the following hparameters: hie = 800 , hoe = 50 x 106 1 and hfe = 55. Calculate the voltage and power gains of circuit. Find also percentage error in the values obtained if hoe is neglected. -12v RL 20000 C1 R1 100K C2 R2 10K RZ

100K CE

1.

The parameters of a certain transistor are = 0.99 and ICBO = 100nA. while IB = 20 A. The transistor, connected in CE configuration, is in amplifying mode. Find ICEO, IC and IE. All symbols carry their usual meanings. For the circuit shown in fig 3(a), 1 = 0.98, 2 = 0.96 VCC = 24, RC = 120 and IE=100 mA. Calculate the current ICI IB1, IE1, IB2, IC2, IC the voltage VCE and the ratios IC/IB and IC/IE. Neglect reverse satuaration currents. VCC C IC RC

1995

1998

1.

IB = Q1 Q2

I C1

VCE

IE 1. Elucidate three consequences of the Early effect in bipolar junction transistors

2001

I C2

I E1

1.

Consider silicon n- -n transistors for the following circuit +12V 2K Vin

2004

IC1 100 1K

Vouty

2005

1. A bipolar transistor has two junctions either one of which may be forward or reverse biased, we have four mods of operations-normal, cut-off, saturation and iverse region. With the help of Ebers-moll equations model the transistor circuit with a single set of equations describing there four regions

1. Indicate whether the - value of a BJT increases or decreases with increase in the values of the following parameters: (i) base width. (ii) minority carrier lifetime in the base region. (iii) temperature. (iv) collector current. (v) collector voltage. 2. In the circuit shown in Fig. 2(c), what would be the minimum value of such that the transistor is in saturation? Assume VCE Sat = 0.2 V.

2007

+5V 1k + VBB Fig.2(c) 1. For the circuit shown in Fig. 1, assume = hFE = 100. Find if the transistor is in cutoff, saturation or in the active region. 0.1 mA 10 k

2009

-10 V 3K 7K 3V + Re V0

500

Fig.1

2010

1. Obtain Ebers-Moll equations for a p-n-p bipolar junction transistor. Show that these equations are true for any arbitrary geometry of the device.

S-ar putea să vă placă și

- Proposed Multimodal Terminal: Architect Rosauro H. Jamandri, M. ArchDocument7 paginiProposed Multimodal Terminal: Architect Rosauro H. Jamandri, M. Archpepito manalotoÎncă nu există evaluări

- PHM604 QB 2019 PDFDocument5 paginiPHM604 QB 2019 PDFAbhishek Yadav100% (1)

- Electric Circuits and Electron Devices Unit I Circuit Analysis Techniques Part-ADocument8 paginiElectric Circuits and Electron Devices Unit I Circuit Analysis Techniques Part-ASalai Kishwar JahanÎncă nu există evaluări

- Transistor ProblemsDocument9 paginiTransistor ProblemsAli AdnanÎncă nu există evaluări

- Sem 3 Module 3Document5 paginiSem 3 Module 3Joshua HernandezÎncă nu există evaluări

- Electronic Devices & Circuits SyllabusDocument4 paginiElectronic Devices & Circuits SyllabusShareef KhanÎncă nu există evaluări

- 9A02405 Analog Electronic CircuitsDocument4 pagini9A02405 Analog Electronic CircuitssivabharathamurthyÎncă nu există evaluări

- PDC 1Document3 paginiPDC 1Sravya LakshmiÎncă nu există evaluări

- AEC BankDocument9 paginiAEC BankprakashkerurÎncă nu există evaluări

- Edc - Assignment Questions - NbaDocument5 paginiEdc - Assignment Questions - Nbagunda manasaÎncă nu există evaluări

- 9A04402 Electronic Circuit AnalysisDocument8 pagini9A04402 Electronic Circuit AnalysissivabharathamurthyÎncă nu există evaluări

- Unsolved Problem SheetDocument20 paginiUnsolved Problem SheetDeveshÎncă nu există evaluări

- EDC Question-Papers Complete SetDocument13 paginiEDC Question-Papers Complete Setselvi04120% (1)

- rr221401 Electronic Devices and CircuitsDocument8 paginirr221401 Electronic Devices and CircuitsSRINIVASA RAO GANTAÎncă nu există evaluări

- Set No. 1: CEO CBODocument9 paginiSet No. 1: CEO CBO29viswa12Încă nu există evaluări

- Solution:: Fig. 2 Shows The Required Common Base ConnectionDocument9 paginiSolution:: Fig. 2 Shows The Required Common Base ConnectionSwathi Gudivada100% (1)

- AEC QuestionsDocument4 paginiAEC QuestionsVinay MadhavÎncă nu există evaluări

- PDC 1Document4 paginiPDC 1Lavanya_123Încă nu există evaluări

- EC6304 Electronic Circuits I Question BankDocument10 paginiEC6304 Electronic Circuits I Question BankAnonymous kQZgP8Încă nu există evaluări

- Semiconductor Devices - Sample QuestionsDocument3 paginiSemiconductor Devices - Sample QuestionsJohn Idun EssumanÎncă nu există evaluări

- Edc 7Document8 paginiEdc 729viswa12100% (1)

- EDC-Unit Wise Revision Test QPDocument4 paginiEDC-Unit Wise Revision Test QPDr G Hari KrishnanÎncă nu există evaluări

- 22ESC141 Basic ElectronicsDocument2 pagini22ESC141 Basic Electronicszwq4rrkkq8Încă nu există evaluări

- EC Question PaperDocument3 paginiEC Question PaperGna Senthil KumarÎncă nu există evaluări

- ALL The EIGHT Questions: Indian Ins-R:Itl:Jte of Technology, KharagpurDocument2 paginiALL The EIGHT Questions: Indian Ins-R:Itl:Jte of Technology, KharagpurIndranilÎncă nu există evaluări

- EN564 Analogue Electronics and InstrumentationDocument46 paginiEN564 Analogue Electronics and InstrumentationAl AidenÎncă nu există evaluări

- ADE (UNIT-II) Previous QuestionsDocument2 paginiADE (UNIT-II) Previous QuestionsKUMAR SÎncă nu există evaluări

- 4 Ece - 15.4.13 (Mod)Document2 pagini4 Ece - 15.4.13 (Mod)BIBIN CHIDAMBARANATHANÎncă nu există evaluări

- EDC - Old Question Papers For Unit 3, 4, 5Document19 paginiEDC - Old Question Papers For Unit 3, 4, 5Deepak SahuÎncă nu există evaluări

- Question Bank - Principles of ElectronicsDocument13 paginiQuestion Bank - Principles of ElectronicsADDELYN CYNTHIA ANAK TONYÎncă nu există evaluări

- ADE (UNIT-II) Previous QuestionsDocument1 paginăADE (UNIT-II) Previous QuestionsKUMAR SÎncă nu există evaluări

- Anallysis and Design of Analog Integrated Circuits QuestionsDocument5 paginiAnallysis and Design of Analog Integrated Circuits QuestionsshankarÎncă nu există evaluări

- Eee 2202 AssignmentDocument2 paginiEee 2202 AssignmentEnock OmariÎncă nu există evaluări

- Electronics: June/July, 2010Document7 paginiElectronics: June/July, 2010Prasad C MÎncă nu există evaluări

- Question Bank, BEDocument2 paginiQuestion Bank, BEKaniniAnbazhaganÎncă nu există evaluări

- Electronics PostDocument30 paginiElectronics PostAravind KarthikÎncă nu există evaluări

- Pulse and Digital CircuitsDocument8 paginiPulse and Digital Circuitssravya sriÎncă nu există evaluări

- R09220203 ElectroniccircuitsDocument12 paginiR09220203 ElectroniccircuitsAkramahmedMohammadÎncă nu există evaluări

- Experiment 8Document3 paginiExperiment 8Nathaniel MendozaÎncă nu există evaluări

- Common Emitter Transistor Common Emitter Transistor Amplifier AmplifierDocument9 paginiCommon Emitter Transistor Common Emitter Transistor Amplifier AmplifierMauro FernandoÎncă nu există evaluări

- Eee-III-Analog Electronic Circuits (15ee34) - AssignmentDocument6 paginiEee-III-Analog Electronic Circuits (15ee34) - AssignmentchaitanyaÎncă nu există evaluări

- Chapter 3 Msbte Asked QuestionsDocument10 paginiChapter 3 Msbte Asked Questionsrutu surve (Ru.)Încă nu există evaluări

- Edc 3Document10 paginiEdc 329viswa12Încă nu există evaluări

- TransistorsDocument23 paginiTransistorsKhalil AliÎncă nu există evaluări

- Question Paper Code:: (10×2 20 Marks)Document3 paginiQuestion Paper Code:: (10×2 20 Marks)GOJAN ECEÎncă nu există evaluări

- PDC Assignment IDocument4 paginiPDC Assignment IathomeÎncă nu există evaluări

- ES330 Laboratory Experiment No. 1: NPN Common-Emitter AmplifierDocument7 paginiES330 Laboratory Experiment No. 1: NPN Common-Emitter AmplifierAhmed SalehÎncă nu există evaluări

- 95bc0c78end Sem 2022Document2 pagini95bc0c78end Sem 2022Shreya SinghÎncă nu există evaluări

- Analog Lab ManualDocument57 paginiAnalog Lab ManualMukesh Sahu100% (1)

- Ecd Manuals 1-7Document46 paginiEcd Manuals 1-7Muhammad Hozaifa100% (1)

- Exp 8 - Common Base AmplifierDocument3 paginiExp 8 - Common Base AmplifierHatem DheerÎncă nu există evaluări

- Edc 4Document10 paginiEdc 429viswa12Încă nu există evaluări

- EEC ActivityDocument13 paginiEEC ActivityKerwin James AustriaÎncă nu există evaluări

- Question Paper Code:: Reg. No.Document5 paginiQuestion Paper Code:: Reg. No.Samraj JebasinghÎncă nu există evaluări

- V Semester B.E. (E&E) Degree Examination, January 2013 (2K6 Scheme) Ee 504: Power ElectronicsDocument3 paginiV Semester B.E. (E&E) Degree Examination, January 2013 (2K6 Scheme) Ee 504: Power ElectronicsSumant ReddyÎncă nu există evaluări

- Edctutorial BctII IDocument3 paginiEdctutorial BctII INeelesh MrzÎncă nu există evaluări

- Anna Ec-IDocument3 paginiAnna Ec-Ikrishna_ScrbidÎncă nu există evaluări

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1De la EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Evaluare: 4.5 din 5 stele4.5/5 (3)

- Electrical and Electronic Principles 3 Checkbook: The Checkbook SeriesDe la EverandElectrical and Electronic Principles 3 Checkbook: The Checkbook SeriesÎncă nu există evaluări

- Life D2013 KeyDocument11 paginiLife D2013 KeyGaurav ShrimaliÎncă nu există evaluări

- Birth, Life and Death of The EgoDocument18 paginiBirth, Life and Death of The EgoBuddhist Publication SocietyÎncă nu există evaluări

- SPMCILHRDocument1 paginăSPMCILHRGaurav ShrimaliÎncă nu există evaluări

- Hpa Phenol Toxicological Overview v2Document12 paginiHpa Phenol Toxicological Overview v2Gaurav ShrimaliÎncă nu există evaluări

- New Rev Peh II Manual 15 Aug 2013Document187 paginiNew Rev Peh II Manual 15 Aug 2013Gaurav ShrimaliÎncă nu există evaluări

- FS Calendar 2014 Wall ENGDocument17 paginiFS Calendar 2014 Wall ENGGaurav ShrimaliÎncă nu există evaluări

- Acc 2Document3 paginiAcc 2Gaurav ShrimaliÎncă nu există evaluări

- MPPDocument7 paginiMPPGaurav ShrimaliÎncă nu există evaluări

- Electronics: Venue:-Destination Academy, Garh Road Near Hotel Harmony S2S Restaurant MeerutDocument1 paginăElectronics: Venue:-Destination Academy, Garh Road Near Hotel Harmony S2S Restaurant MeerutGaurav ShrimaliÎncă nu există evaluări

- D 8805 Paper IiDocument12 paginiD 8805 Paper IirahulpelectronicsÎncă nu există evaluări

- Syllabus: India'S Best Institute For EngineersDocument6 paginiSyllabus: India'S Best Institute For EngineersGaurav ShrimaliÎncă nu există evaluări

- Cut-Off: India's Best Institute For EngineersDocument1 paginăCut-Off: India's Best Institute For EngineersGaurav ShrimaliÎncă nu există evaluări

- AnswersDocument51 paginiAnswersGaurav ShrimaliÎncă nu există evaluări

- Ugc Keys PDF 2005Document2 paginiUgc Keys PDF 2005Gaurav ShrimaliÎncă nu există evaluări

- Am 14Document1 paginăAm 14Gaurav ShrimaliÎncă nu există evaluări

- D 8804 Paper IiDocument12 paginiD 8804 Paper IiRamkrishna ChittooriÎncă nu există evaluări

- Am 1Document1 paginăAm 1Gaurav ShrimaliÎncă nu există evaluări

- Am 3Document1 paginăAm 3Gaurav ShrimaliÎncă nu există evaluări

- Am 14Document1 paginăAm 14Gaurav ShrimaliÎncă nu există evaluări

- TimeDocument5 paginiTimeGaurav ShrimaliÎncă nu există evaluări

- ACE Engineering Academy - Online Test:: Test-1 On Communications, Topic: Analog Communication SystemDocument1 paginăACE Engineering Academy - Online Test:: Test-1 On Communications, Topic: Analog Communication SystemGaurav ShrimaliÎncă nu există evaluări

- Am 3Document1 paginăAm 3Gaurav ShrimaliÎncă nu există evaluări

- ACE Engineering Academy - Online Test:: Test-1 On Communications, Topic: Analog Communication SystemDocument1 paginăACE Engineering Academy - Online Test:: Test-1 On Communications, Topic: Analog Communication SystemGaurav ShrimaliÎncă nu există evaluări

- Am 14Document1 paginăAm 14Gaurav ShrimaliÎncă nu există evaluări

- Ongc PdfsDocument1 paginăOngc PdfsGaurav ShrimaliÎncă nu există evaluări

- AllowanceDocument5 paginiAllowanceGaurav ShrimaliÎncă nu există evaluări

- Am 14Document1 paginăAm 14Gaurav ShrimaliÎncă nu există evaluări

- Am 14Document1 paginăAm 14Gaurav ShrimaliÎncă nu există evaluări

- Income Tax PrerequisiteDocument4 paginiIncome Tax PrerequisiteGaurav ShrimaliÎncă nu există evaluări

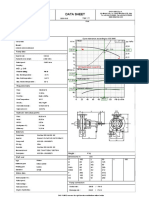

- Data Card FR Offshore PDFDocument4 paginiData Card FR Offshore PDFGaurav ShrimaliÎncă nu există evaluări

- Time Table & Instruction For Candidate - Faculty of Sci & TechDocument3 paginiTime Table & Instruction For Candidate - Faculty of Sci & TechDeepshikha Mehta joshiÎncă nu există evaluări

- Climatol GuideDocument40 paginiClimatol GuideFressiaÎncă nu există evaluări

- Input and Output Statements PDFDocument11 paginiInput and Output Statements PDFRajendra BuchadeÎncă nu există evaluări

- Ge 6 Art Appreciationmodule 1Document9 paginiGe 6 Art Appreciationmodule 1Nicky Balberona AyrosoÎncă nu există evaluări

- DC Motor: F Bli NewtonDocument35 paginiDC Motor: F Bli NewtonMuhammad TausiqueÎncă nu există evaluări

- On The Importance of Learning Statistics For Psychology StudentsDocument2 paginiOn The Importance of Learning Statistics For Psychology StudentsMadison HartfieldÎncă nu există evaluări

- Selecting Appropriate Instructional Materials For Edukasyong Pantahanan at Pangkabuhayan/ Technology and Livelihood EducationDocument35 paginiSelecting Appropriate Instructional Materials For Edukasyong Pantahanan at Pangkabuhayan/ Technology and Livelihood EducationJhenn Mhen Yhon100% (1)

- Technical Test 03Document13 paginiTechnical Test 03KartikÎncă nu există evaluări

- Email ID: Contact No: +971562398104, +917358302902: Name: R.VishnushankarDocument6 paginiEmail ID: Contact No: +971562398104, +917358302902: Name: R.VishnushankarJêmš NavikÎncă nu există evaluări

- Tree Based Machine Learning Algorithms Decision Trees Random Forests and Boosting B0756FGJCPDocument109 paginiTree Based Machine Learning Algorithms Decision Trees Random Forests and Boosting B0756FGJCPJulio Davalos Vasquez100% (1)

- Feasibility and Optimization of Dissimilar Laser Welding ComponentsDocument366 paginiFeasibility and Optimization of Dissimilar Laser Welding Componentskaliappan45490Încă nu există evaluări

- Rules and Fallacies For Categorical SyllogismsDocument5 paginiRules and Fallacies For Categorical SyllogismsFatima Ismael PortacioÎncă nu există evaluări

- Data Sheet: Item N°: Curve Tolerance According To ISO 9906Document3 paginiData Sheet: Item N°: Curve Tolerance According To ISO 9906Aan AndianaÎncă nu există evaluări

- Integration Plan Grade 9 Mapeh SeptemberDocument3 paginiIntegration Plan Grade 9 Mapeh Septemberbernie evaristo bacsaÎncă nu există evaluări

- Spelling Grammar Punctuation: Teacher BookDocument8 paginiSpelling Grammar Punctuation: Teacher BookNeil MenezesÎncă nu există evaluări

- The Theory of Production and Cost: Chapter FourDocument32 paginiThe Theory of Production and Cost: Chapter FourOromay Elias100% (1)

- Bohler Dcms T-MCDocument1 paginăBohler Dcms T-MCFlaviu-Andrei AstalisÎncă nu există evaluări

- Planning Theory Syllabus - 2016Document24 paginiPlanning Theory Syllabus - 2016LakshmiRaviChanduKolusuÎncă nu există evaluări

- Standard Dimensions Grooved and Shouldered Joints AMERICAN - The Right WayDocument2 paginiStandard Dimensions Grooved and Shouldered Joints AMERICAN - The Right WaySopon SrirattanapiboonÎncă nu există evaluări

- IPHPDocument4 paginiIPHPAliah CasilangÎncă nu există evaluări

- Activity 2Document5 paginiActivity 2DIOSAY, CHELZEYA A.Încă nu există evaluări

- In Search of Begum Akhtar PDFDocument42 paginiIn Search of Begum Akhtar PDFsreyas1273Încă nu există evaluări

- Help SIMARIS Project 3.1 enDocument61 paginiHelp SIMARIS Project 3.1 enVictor VignolaÎncă nu există evaluări

- Chapter 2 Axial and Torsional ElementsDocument57 paginiChapter 2 Axial and Torsional ElementsAhmad FaidhiÎncă nu există evaluări

- OOPS KnowledgeDocument47 paginiOOPS KnowledgeLakshmanÎncă nu există evaluări

- Catálogo StaubliDocument8 paginiCatálogo StaubliJackson BravosÎncă nu există evaluări

- All Papers of Thermodyanmics and Heat TransferDocument19 paginiAll Papers of Thermodyanmics and Heat TransfervismayluhadiyaÎncă nu există evaluări

- AT ChapIDocument48 paginiAT ChapIvigneshwaranbeÎncă nu există evaluări

- Backward Forward PropogationDocument19 paginiBackward Forward PropogationConrad WaluddeÎncă nu există evaluări