Documente Academic

Documente Profesional

Documente Cultură

HEF4104B: 1. General Description

Încărcat de

velizarkoTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

HEF4104B: 1. General Description

Încărcat de

velizarkoDrepturi de autor:

Formate disponibile

HEF4104B

Quad low-to-high voltage translator with 3-state outputs

Rev. 04 5 March 2009 Product data sheet

1. General description

The HEF4104B is a quad low voltage-to-high voltage translator with 3-state outputs. It provides the capability of interfacing low voltage circuits to high voltage circuits. For example low voltage Local Oxidation Complementary MOS (LOCMOS) and TTL to high voltage LOCMOS. It has four data inputs (A0 to A3), an active HIGH output enable input (OE), four data outputs (B0 to B3) and their complements (B0 to B3). With OE = HIGH, the outputs B0 to B3 and B0 to B3 are in the low impedance ON-state, either HIGH or LOW as determined by the inputs A0 to A3. With OE = LOW, the outputs B0 to B3 and B0 to B3 are in the high-impedance OFF-state. It uses a common negative supply (VSS) and separate positive supplies for the inputs (VDD(A)) and the outputs (VDD(B)). VDD(A) must always be less than or equal to VDD(B), even during power turn-on and turn-off. For the permissible operating range of VDD(A) and VDD(B) see Figure 4. Each input protection circuit is terminated between VDD(B) and VSS. This allows the input signals to be driven from any potential between VDD(B) and VSS, without regard to current limiting. When driving from potentials greater than VDD(B) or less than VSS, the current at each input must be limited to 10 mA. It operates over a recommended VDD power supply range of 3 V to 15 V referenced to VSS (usually ground). Unused inputs must be connected to VDD, VSS, or another input. It is also suitable for use over the full industrial (40 C to +85 C) temperature range.

2. Features

I I I I I I I Fully static operation 5 V, 10 V, and 15 V parametric ratings Standardized symmetrical output characteristics Inputs and outputs are protected against electrostatic effects Operates across the full industrial temperature range from 40 C to +85 C Complies with JEDEC standard JESD 13-B ESD protection: N HBM JESD22-A114E exceeds 2000 V N MM JESD22-A115-A exceeds 200 V

3. Applications

I Industrial

NXP Semiconductors

HEF4104B

Quad low-to-high voltage translator with 3-state outputs

4. Ordering information

Table 1. Ordering information All types operate from 40 C to +85 C. Type number HEF4104BP HEF4104BT Package Name DIP16 SO16 Description plastic dual in-line package; 16 leads (300 mil); plastic small outline package; 16 leads; body width 3.9 mm Version SOT38-4 SOT109-1

5. Functional diagram

VDD(A) 16 4 2 VDD(B) 1 3 A0 B0

B0 LEVEL CONVERTER

A1

A0 B1

B0

B0 7 11 LEVEL CONVERTER B1 A1 A2 10 B2 LEVEL CONVERTER LEVEL CONVERTER

B1

B1

9 A3 12

A2 B2

B2

B2 13 B3 A3 14 B3 LEVEL CONVERTER VDD(A) VDD(B)

001aag264

LEVEL CONVERTER

B3

OE

15

B3

OE 8 VSS

001aag262

Fig 1.

Logic symbol

Fig 2.

Logic diagram

HEF4104B_4

NXP B.V. 2009. All rights reserved.

Product data sheet

Rev. 04 5 March 2009

2 of 14

NXP Semiconductors

HEF4104B

Quad low-to-high voltage translator with 3-state outputs

6. Pinning information

6.1 Pinning

HEF4104B

VDD(B) B0 B0 A0 A1 B1 B1 VSS 1 2 3 4 5 6 7 8

001aag263

16 VDD(A) 15 OE 14 B3 13 B3 12 A3 11 A2 10 B2 9 B2

Fig 3.

Pin conguration

6.2 Pin description

Table 2. Symbol VDD(B) B0 to B3 B0 to B3 A0 to A3 VSS OE VDD(A) Pin description Pin 1 2, 7, 9, 14 3, 6, 10, 13 4, 5, 11, 12 8 15 16 Description supply voltage port B complementary data output data output data input common negative supply voltage (0 V) output enable input supply voltage port A

7. Functional description

Table 3. Control OE H L

[1]

Function table[1] Output Bn An Z Bn An Z

H = HIGH voltage level; L = LOW voltage level; Z = high-impedance OFF-state.

HEF4104B_4

NXP B.V. 2009. All rights reserved.

Product data sheet

Rev. 04 5 March 2009

3 of 14

NXP Semiconductors

HEF4104B

Quad low-to-high voltage translator with 3-state outputs

8. Limiting values

Table 4. Limiting values In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to VSS = 0 V (ground). Symbol VDD(A) VDD(B) IIK VI IOK II/O IDD Tstg Tamb Ptot Parameter supply voltage A supply voltage B input clamping current input voltage output clamping current input/output current supply current storage temperature ambient temperature total power dissipation Tamb = 40 C to +85 C DIP16 SO16 P

[1] [2] [3]

[2] [3] [1]

Conditions port A; VDD(A) VDD(B) port B; VDD(B) VDD(A) VI < 0.5 V or VI > VDD(A) + 0.5 V VO < 0.5 V or VO > VDD(B) + 0.5 V

Min 0.5 0.5 0.5 65 40 -

Max +18 +18 10 10 10 50 +150 +85 750 500 100

Unit V V mA mA mA mA C C mW mW mW

VDD(A) + 0.5 V

power dissipation

IDD is the combined current of IDD(A) and IDD(B).

per output

For DIP16 packages: above Tamb = 70 C, Ptot derates linearly at 12 mW/K. For SO16 packages: above Tamb = 70 C, Ptot derates linearly at 8 mW/K.

9. Recommended operating conditions

Table 5. Symbol VDD(A) VDD(B) VI Tamb t/V Recommended operating conditions Parameter supply voltage supply voltage input voltage ambient temperature input transition rise and fall rate in free air VDD(A)= 5 V VDD(A) = 10 V VDD(A) = 15 V Conditions Min 3 VDD(A) 0 40 Typ Max VDD(B) 15 VDD(A) +85 3.75 0.5 0.08 Unit V V V C ns/V ns/V ns/V

10. Static characteristics

Table 6. Static characteristics VDD(A) = VDD(B); VSS = 0 V; VI = VSS or VDD(A); unless otherwise specied. Symbol Parameter VIH HIGH-level input voltage Conditions |IO| < 1 A VDD[1] 5V 10 V 15 V Tamb = 40 C Tamb = +25 C Tamb = +85 C Unit Min 3.5 7.0 11.0 Max Min 3.5 7.0 11.0 Max Min 3.5 7.0 11.0 Max V V V

HEF4104B_4

NXP B.V. 2009. All rights reserved.

Product data sheet

Rev. 04 5 March 2009

4 of 14

NXP Semiconductors

HEF4104B

Quad low-to-high voltage translator with 3-state outputs

Table 6. Static characteristics continued VDD(A) = VDD(B); VSS = 0 V; VI = VSS or VDD(A); unless otherwise specied. Symbol Parameter VIL LOW-level input voltage Conditions |IO| < 1 A VDD[1] 5V 10 V 15 V VOH HIGH-level output voltage |IO| < 1 A 5V 10 V 15 V VOL LOW-level output voltage |IO| < 1 A 5V 10 V 15 V IOH HIGH-level output current VO = 2.5 V VO = 4.6 V VO = 9.5 V VO = 13.5 V IOL LOW-level output current VO = 0.4 V VO = 0.5 V VO = 1.5 V II IDD input leakage current supply current all valid input combinations; IO = 0 A HIGH level; VO = VDD(B) LOW level; VO = VSS CI

[1] [2]

Tamb = 40 C Tamb = +25 C Tamb = +85 C Unit Min 4.95 9.95 14.95 1.7 0.52 1.3 3.6 0.52 1.3 3.6 [2]

Max 1.5 3.0 4.0 0.05 0.05 0.05 0.3 20 40 80 1.6 1.6 -

Min 4.95 9.95 14.95 1.4 0.44 1.1 3.0 0.44 1.1 3.0 -

Max 1.5 3.0 4.0 0.05 0.05 0.05 0.3 20 40 80 1.6 1.6 7.5

Min 4.95 9.95 14.95 1.1 0.36 0.9 2.4 0.36 0.9 2.4 -

Max 1.5 3.0 4.0 0.05 0.05 0.05 1.0 150 300 600 12.0 V V V V V V V V V mA mA mA mA mA mA mA A A A A A

5V 5V 10 V 15 V 5V 10 V 15 V 15 V 5V 10 V 15 V 15 V 15 V -

IOZ

OFF-state output current

12.0 A pF

input capacitance

digital inputs

VDD is the same as VDD(A) and VDD(B). IDD is the combined current of IDD(A) and IDD(B).

HEF4104B_4

NXP B.V. 2009. All rights reserved.

Product data sheet

Rev. 04 5 March 2009

5 of 14

NXP Semiconductors

HEF4104B

Quad low-to-high voltage translator with 3-state outputs

15 VDD(B) (V) 10

001aag265

operating area

0 0 5 10 VDD(A) (V) 15

The shaded area shows the permissible operating range.

Fig 4.

VDD(B) as a function of VDD(A)

11. Dynamic characteristics

Table 7. Dynamic characteristics Tamb = 25 C; for test circuit see Figure 7; unless otherwise specied. Symbol Parameter tPHL HIGH to LOW propagation delay Conditions An to Bn, Bn; see Figure 5 VDD(A) = VDD(B) = 5 V VDD(A) = VDD(B) = 10 V VDD(A) = VDD(B) = 15 V tPLH LOW to HIGH propagation delay An to Bn, Bn; see Figure 5 VDD(A) = VDD(B) = 5 V VDD(A) = VDD(B) = 10 V VDD(A) = VDD(B) = 15 V tTHL HIGH to LOW output Bn or Bn; see Figure 6 transition time VDD(A) = VDD(B) = 5 V VDD(A) = VDD(B) = 10 V VDD(A) = VDD(B) = 15 V tTLH LOW to HIGH output Bn or Bn; see Figure 6 transition time VDD(A) = VDD(B) = 5 V VDD(A) = VDD(B) = 10 V VDD(A) = VDD(B) = 15 V tPHZ HIGH to OFF-state propagation delay OE to Bn, Bn; see Figure 6 VDD(A) = VDD(B) = 5 V VDD(A) = VDD(B) = 10 V VDD(A) = VDD(B) = 15 V 70 55 60 135 110 120 ns ns ns 143 + 0.55 CL 69 + 0.23 CL 62 + 0.16 CL 10 + 1.00 CL 9 + 0.42 CL 6 + 0.28 CL 10 + 1.00 CL 9 + 0.42 CL 6 + 0.28 CL 170 80 70 60 30 20 60 30 20 340 160 140 120 60 40 120 60 40 ns ns ns ns ns ns ns ns ns 143 + 0.55 CL 69 + 0.23 CL 57 + 0.16 CL 170 80 65 340 160 135 ns ns ns Extrapolation formula[1] Min Typ Max Unit

HEF4104B_4

NXP B.V. 2009. All rights reserved.

Product data sheet

Rev. 04 5 March 2009

6 of 14

NXP Semiconductors

HEF4104B

Quad low-to-high voltage translator with 3-state outputs

Table 7. Dynamic characteristics continued Tamb = 25 C; for test circuit see Figure 7; unless otherwise specied. Symbol Parameter tPLZ LOW to OFF-state propagation delay Conditions OE to Bn, Bn; see Figure 6 VDD(A) = VDD(B) = 5 V VDD(A) = VDD(B) = 10 V VDD(A) = VDD(B) = 15 V tPZH OFF-state to HIGH propagation delay OE to Bn, Bn; see Figure 6 VDD(A) = VDD(B) = 5 V VDD(A) = VDD(B) = 10 V VDD(A) = VDD(B) = 15 V tPZL OFF-state to LOW propagation delay OE to Bn, Bn; see Figure 6 VDD(A) = VDD(B) = 5 V VDD(A) = VDD(B) = 10 V VDD(A) = VDD(B) = 15 V

[1]

Extrapolation formula[1]

Min -

Typ 70 55 55 195 95 80 195 95 80

Max 135 105 110 395 195 165 395 190 160

Unit ns ns ns ns ns ns ns ns ns

Typical value of the propagation delay and output transition time can be calculated with the extrapolation formula (CL in pF).

Table 8. Dynamic power dissipation VDD(A) = VDD(B), VSS = 0 V; tr = tf 20 ns; Tamb = 25 C. Symbol Parameter PD dynamic power dissipation VDD[1] Typical formula 5V 10 V 15 V PD = 3000 fi + (fo CL) VDD (W)

2

where fi = input frequency in MHz; VDD2

PD = 12200 fi + (fo CL) (W) fo = output frequency in MHz; PD = 31000 fi + (fo CL) VDD2 (W) CL = output load capacitance in pF; (fo CL) = sum of the outputs; VDD = supply voltage in V.

[1]

VDD is the same as VDD(A) and VDD(B).

HEF4104B_4

NXP B.V. 2009. All rights reserved.

Product data sheet

Rev. 04 5 March 2009

7 of 14

NXP Semiconductors

HEF4104B

Quad low-to-high voltage translator with 3-state outputs

12. Waveforms

VI An input 0V VM

tPHL

VOH Bn output VOL

tPLH

VY

VM

VX tTHL tPLH tTLH tPHL

VOH Bn output VOL

VY VX tTLH tTHL 001aaj783

Measurement points are given in Table 9. Logic levels: VOL and VOH are typical output voltage levels that occur with the output load.

Fig 5.

Data input (An) to data output (Bn, Bn) propagation delays and output transition times

VI OE input VSS tPLZ output LOW-to-OFF OFF-to-LOW VOH tPZL VY VM

VOL tPHZ VOH

VX tPZH VY VX outputs on outputs off outputs on

001aaj782

output HIGH-to-OFF OFF-to-HIGH VOL

Measurement points are given in Table 9. Logic levels: VOL and VOH are typical output voltage levels that occur with the output load.

Fig 6. Table 9. Input VI

Enable and disable times Measurement points Output VM 0.5VDD(A) VM 0.5VDD(B) VX 0.1VDD(B) VY 0.9VDD(B) tr, tf 20 ns

NXP B.V. 2009. All rights reserved.

VSS or VDD(A)

HEF4104B_4

Product data sheet

Rev. 04 5 March 2009

8 of 14

NXP Semiconductors

HEF4104B

Quad low-to-high voltage translator with 3-state outputs

VI negative pulse VSS

tW 90 % VM 10 % tf tr tr tf 90 % VM 10 % tW

001aaj781

VM

VI positive pulse VSS

VM

a. Input waveforms

VEXT VDD VI VO

RL

G

RT

DUT

CL RL

001aaj784

b. Test circuit

Test data given in Table 10. Denitions for test circuit: DUT = Device Under Test; CL = load capacitance including jig and probe capacitance RL = load resistance RT = termination resistance should be equal to the output impedance Zo of the pulse generator;

Fig 7. Table 10. Supplies

Test circuit for measuring switching times Test data Input tr, tf 20 ns Load RL 1 k CL

50 pF

VEXT tPHL, tPLH open tPZH, tPHZ

VSS

VDD(A) = VDD(B)

5 V to 15 V

tPZL, tPLZ VDD(B)

HEF4104B_4

NXP B.V. 2009. All rights reserved.

Product data sheet

Rev. 04 5 March 2009

9 of 14

NXP Semiconductors

HEF4104B

Quad low-to-high voltage translator with 3-state outputs

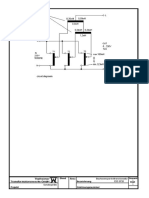

13. Package outline

DIP16: plastic dual in-line package; 16 leads (300 mil) SOT38-4

D seating plane

ME

A2

A1

c Z e b1 b 16 9 b2 MH w M (e 1)

pin 1 index E

5 scale

10 mm

DIMENSIONS (inch dimensions are derived from the original mm dimensions) UNIT mm inches A max. 4.2 0.17 A1 min. 0.51 0.02 A2 max. 3.2 0.13 b 1.73 1.30 0.068 0.051 b1 0.53 0.38 0.021 0.015 b2 1.25 0.85 0.049 0.033 c 0.36 0.23 0.014 0.009 D (1) 19.50 18.55 0.77 0.73 E (1) 6.48 6.20 0.26 0.24 e 2.54 0.1 e1 7.62 0.3 L 3.60 3.05 0.14 0.12 ME 8.25 7.80 0.32 0.31 MH 10.0 8.3 0.39 0.33 w 0.254 0.01 Z (1) max. 0.76 0.03

Note 1. Plastic or metal protrusions of 0.25 mm (0.01 inch) maximum per side are not included. OUTLINE VERSION SOT38-4 REFERENCES IEC JEDEC JEITA EUROPEAN PROJECTION

ISSUE DATE 95-01-14 03-02-13

Fig 8.

HEF4104B_4

Package outline SOT38-1 (DIP16)

NXP B.V. 2009. All rights reserved.

Product data sheet

Rev. 04 5 March 2009

10 of 14

NXP Semiconductors

HEF4104B

Quad low-to-high voltage translator with 3-state outputs

SO16: plastic small outline package; 16 leads; body width 3.9 mm

SOT109-1

A X

c y HE v M A

Z 16 9

Q A2 pin 1 index Lp 1 e bp 8 w M L detail X A1 (A 3) A

2.5 scale

5 mm

DIMENSIONS (inch dimensions are derived from the original mm dimensions) UNIT mm inches Note 1. Plastic or metal protrusions of 0.15 mm (0.006 inch) maximum per side are not included. OUTLINE VERSION SOT109-1 REFERENCES IEC 076E07 JEDEC MS-012 JEITA EUROPEAN PROJECTION A max. 1.75 A1 0.25 0.10 A2 1.45 1.25 A3 0.25 0.01 bp 0.49 0.36 c 0.25 0.19 D (1) 10.0 9.8 E (1) 4.0 3.8 0.16 0.15 e 1.27 0.05 HE 6.2 5.8 L 1.05 Lp 1.0 0.4 0.039 0.016 Q 0.7 0.6 0.028 0.020 v 0.25 0.01 w 0.25 0.01 y 0.1 Z (1) 0.7 0.3

0.010 0.057 0.069 0.004 0.049

0.019 0.0100 0.39 0.014 0.0075 0.38

0.244 0.041 0.228

0.028 0.004 0.012

8 o 0

ISSUE DATE 99-12-27 03-02-19

Fig 9.

HEF4104B_4

Package outline SOT109-1 (SO16)

NXP B.V. 2009. All rights reserved.

Product data sheet

Rev. 04 5 March 2009

11 of 14

NXP Semiconductors

HEF4104B

Quad low-to-high voltage translator with 3-state outputs

14. Abbreviations

Table 11. Acronym DUT ESD HBM MM Abbreviations Description Device Under Test ElectroStatic Discharge Human Body Model Machine Model

15. Revision history

Table 12. Revision history Release date 20090305 Data sheet status Product data sheet Change notice Supersedes HEF4104B_CNV_3 Document ID HEF4104B_4 Modications:

The format of this data sheet has been redesigned to comply with the new identity guidelines of NXP Semiconductors. Legal texts have been adapted to the new company name where appropriate. Pin names changed throughout the data sheet. Section 3 Applications added. Package SOT74 removed from Section 4 Ordering information and Section 13 Package outline. Section 8 Limiting values and Section 10 Static characteristics added, taken from the HE4000B Family Specications data sheet. Typical temperature coefcient for propagation delays and output transitions removed. Section 14 Abbreviations added. Product specication Product specication HEF4104B_CNV_2 HEF4104B_CNV_1

HEF4104B_CNV_3 HEF4104B_CNV_2

19950101 19950101

HEF4104B_4

NXP B.V. 2009. All rights reserved.

Product data sheet

Rev. 04 5 March 2009

12 of 14

NXP Semiconductors

HEF4104B

Quad low-to-high voltage translator with 3-state outputs

16. Legal information

16.1 Data sheet status

Document status[1][2] Objective [short] data sheet Preliminary [short] data sheet Product [short] data sheet

[1] [2] [3]

Product status[3] Development Qualication Production

Denition This document contains data from the objective specication for product development. This document contains data from the preliminary specication. This document contains the product specication.

Please consult the most recently issued document before initiating or completing a design. The term short data sheet is explained in section Denitions. The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL http://www.nxp.com.

16.2 Denitions

Draft The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information. Short data sheet A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales ofce. In case of any inconsistency or conict with the short data sheet, the full data sheet shall prevail.

malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customers own risk. Applications Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specied use without further testing or modication. Limiting values Stress above one or more limiting values (as dened in the Absolute Maximum Ratings System of IEC 60134) may cause permanent damage to the device. Limiting values are stress ratings only and operation of the device at these or any other conditions above those given in the Characteristics sections of this document is not implied. Exposure to limiting values for extended periods may affect device reliability. Terms and conditions of sale NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/prole/terms, including those pertaining to warranty, intellectual property rights infringement and limitation of liability, unless explicitly otherwise agreed to in writing by NXP Semiconductors. In case of any inconsistency or conict between information in this document and such terms and conditions, the latter will prevail. No offer to sell or license Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

16.3 Disclaimers

General Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. Right to make changes NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof. Suitability for use NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or

16.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

17. Contact information

For more information, please visit: http://www.nxp.com For sales ofce addresses, please send an email to: salesaddresses@nxp.com

HEF4104B_4

NXP B.V. 2009. All rights reserved.

Product data sheet

Rev. 04 5 March 2009

13 of 14

NXP Semiconductors

HEF4104B

Quad low-to-high voltage translator with 3-state outputs

18. Contents

1 2 3 4 5 6 6.1 6.2 7 8 9 10 11 12 13 14 15 16 16.1 16.2 16.3 16.4 17 18 General description . . . . . . . . . . . . . . . . . . . . . . 1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Ordering information . . . . . . . . . . . . . . . . . . . . . 2 Functional diagram . . . . . . . . . . . . . . . . . . . . . . 2 Pinning information . . . . . . . . . . . . . . . . . . . . . . 3 Pinning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 Pin description . . . . . . . . . . . . . . . . . . . . . . . . . 3 Functional description . . . . . . . . . . . . . . . . . . . 3 Limiting values. . . . . . . . . . . . . . . . . . . . . . . . . . 4 Recommended operating conditions. . . . . . . . 4 Static characteristics. . . . . . . . . . . . . . . . . . . . . 4 Dynamic characteristics . . . . . . . . . . . . . . . . . . 6 Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Package outline . . . . . . . . . . . . . . . . . . . . . . . . 10 Abbreviations . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Revision history . . . . . . . . . . . . . . . . . . . . . . . . 12 Legal information. . . . . . . . . . . . . . . . . . . . . . . 13 Data sheet status . . . . . . . . . . . . . . . . . . . . . . 13 Denitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Disclaimers . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Trademarks . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Contact information. . . . . . . . . . . . . . . . . . . . . 13 Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section Legal information.

NXP B.V. 2009.

All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com Date of release: 5 March 2009 Document identifier: HEF4104B_4

S-ar putea să vă placă și

- Stevie Wonder - As (V. George Michael)Document8 paginiStevie Wonder - As (V. George Michael)rfontanabr100% (1)

- Servo MotorDocument200 paginiServo MotorLuckyboybk FCÎncă nu există evaluări

- Audio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsDe la EverandAudio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsÎncă nu există evaluări

- HCC4051B/52B/53B HCF4051B/52B/53B: Analog Multiplexers-DemultiplexersDocument17 paginiHCC4051B/52B/53B HCF4051B/52B/53B: Analog Multiplexers-DemultiplexersJaiprasad ReddyÎncă nu există evaluări

- Power Transmission (Interview Questions)Document11 paginiPower Transmission (Interview Questions)Ntando MpiyakheÎncă nu există evaluări

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsDe la EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsÎncă nu există evaluări

- Analog Engineer S Circuit Cookbook Amplifiers 1683531194Document300 paginiAnalog Engineer S Circuit Cookbook Amplifiers 1683531194eric hudsonÎncă nu există evaluări

- Future Substation TechnologiesDocument22 paginiFuture Substation TechnologiesDevidas KulkarniÎncă nu există evaluări

- IR2110/IR2113 : High and Low Side Driver SDocument15 paginiIR2110/IR2113 : High and Low Side Driver SPepe ModstÎncă nu există evaluări

- Contador A Decadas HEF4040B PDFDocument14 paginiContador A Decadas HEF4040B PDFAnonymous hp6KDLIxEÎncă nu există evaluări

- IR2110/IR2113: High and Low Side DriverDocument16 paginiIR2110/IR2113: High and Low Side DriverguiknopÎncă nu există evaluări

- cd4066 DatasheetDocument9 paginicd4066 DatasheetAbubakar SidikÎncă nu există evaluări

- Quad 2-Channel Analog Multiplexer / Demultiplexer: BU4551B / BU4551BF / BU4551BFVDocument6 paginiQuad 2-Channel Analog Multiplexer / Demultiplexer: BU4551B / BU4551BF / BU4551BFVmaldomattÎncă nu există evaluări

- Data Sheet-IC 4017-NXP Philips PDFDocument16 paginiData Sheet-IC 4017-NXP Philips PDFGirish OniyilÎncă nu există evaluări

- AD775Document12 paginiAD775Shiwam IsrieÎncă nu există evaluări

- Ir 2010Document17 paginiIr 2010Naveed AhmedÎncă nu există evaluări

- Dual 3-Channel Analog MultiplexerDocument12 paginiDual 3-Channel Analog MultiplexerLuis AlbertoÎncă nu există evaluări

- HEF4013B: 1. General DescriptionDocument15 paginiHEF4013B: 1. General DescriptionMuhammad Iqbal RasyidiÎncă nu există evaluări

- HEF40106B: 1. General DescriptionDocument15 paginiHEF40106B: 1. General DescriptionyajujotosÎncă nu există evaluări

- CD4538BCDocument11 paginiCD4538BCImtiaz HussainÎncă nu există evaluări

- Ir 2110Document17 paginiIr 2110Nguyen KhangÎncă nu există evaluări

- Conversor D-A M62352FPDocument6 paginiConversor D-A M62352FPagus2kÎncă nu există evaluări

- CD4051B, CD4052B, CD4053B: CMOS Analog Multiplexers/Demultiplexers With Logic Level Conversion FeaturesDocument15 paginiCD4051B, CD4052B, CD4053B: CMOS Analog Multiplexers/Demultiplexers With Logic Level Conversion Featuresmithrandir91Încă nu există evaluări

- DS75176B/DS75176BT Multipoint RS-485/RS-422 Transceivers: Features DescriptionDocument14 paginiDS75176B/DS75176BT Multipoint RS-485/RS-422 Transceivers: Features DescriptionVũ TưởngÎncă nu există evaluări

- Ir 2113Document18 paginiIr 2113rohitsingh2909Încă nu există evaluări

- DS16F95, DS36F95 EIA-485/EIA-422A Differential Bus TransceiverDocument14 paginiDS16F95, DS36F95 EIA-485/EIA-422A Differential Bus Transceivervsc2012Încă nu există evaluări

- CD40106BMS: Features PinoutDocument9 paginiCD40106BMS: Features PinoutWilson Andres Benitez JulioÎncă nu există evaluări

- Hef 4094Document17 paginiHef 4094vasconcelosrvÎncă nu există evaluări

- Ir 2213Document14 paginiIr 2213Lampros LampropoulosÎncă nu există evaluări

- IR2110/IR2113 : High and Low Side Driver SDocument15 paginiIR2110/IR2113 : High and Low Side Driver SPandu Sandi PratamaÎncă nu există evaluări

- Unisonic Technologies Co., LTD: 8-Channel Analog Multiplexers/DemultiplexersDocument7 paginiUnisonic Technologies Co., LTD: 8-Channel Analog Multiplexers/DemultiplexersNaresh KsÎncă nu există evaluări

- 74LVC4245A: 1. General DescriptionDocument18 pagini74LVC4245A: 1. General DescriptionLeslie StewartÎncă nu există evaluări

- 4052Document9 pagini4052Brzata PticaÎncă nu există evaluări

- Starchips Starchips Starchips Starchips: TechnologyDocument15 paginiStarchips Starchips Starchips Starchips: TechnologyXFact0r100% (1)

- MC14017B Decade Counter: PDIP 16 P Suffix CASE 648Document9 paginiMC14017B Decade Counter: PDIP 16 P Suffix CASE 648JossuarmmÎncă nu există evaluări

- Ir2112 (S) & (PBF) : High and Low Side DriverDocument17 paginiIr2112 (S) & (PBF) : High and Low Side DriverMugahed DammagÎncă nu există evaluări

- 4072Document11 pagini4072Esneyder QuevedoÎncă nu există evaluări

- Ad7524 Ep PDFDocument8 paginiAd7524 Ep PDFjlfepeÎncă nu există evaluări

- LCD GDM12864HDocument13 paginiLCD GDM12864HSintesoftÎncă nu există evaluări

- HCF4051B: Single 8-Channel Analog Multiplexer/DemultiplexerDocument11 paginiHCF4051B: Single 8-Channel Analog Multiplexer/DemultiplexerInes Ben TibaÎncă nu există evaluări

- CD4008BMS - Full AdderDocument8 paginiCD4008BMS - Full AdderTony TohÎncă nu există evaluări

- In/Out A Out/In A Out/In B In/Out B Cont B Cont C VSS VDD Cont A Cont D In/Out D Out/In D Out/In C In/Out C 1 2 3 4 5 6 7 14 13 12 11 10 9 8Document9 paginiIn/Out A Out/In A Out/In B In/Out B Cont B Cont C VSS VDD Cont A Cont D In/Out D Out/In D Out/In C In/Out C 1 2 3 4 5 6 7 14 13 12 11 10 9 8alexdann68Încă nu există evaluări

- Advanced Power Electronics Corp.: AP85T03GH/JDocument4 paginiAdvanced Power Electronics Corp.: AP85T03GH/JDíaz Rivero Cesar EnriqueÎncă nu există evaluări

- CD4011BMS, CD4012BMS CD4023BMS: Pinouts FeaturesDocument9 paginiCD4011BMS, CD4012BMS CD4023BMS: Pinouts FeaturesNarendra BholeÎncă nu există evaluări

- CD4073BMS, CD4081BMS CD4082BMS: Pinout FeaturesDocument10 paginiCD4073BMS, CD4081BMS CD4082BMS: Pinout FeaturesAbarna AbuÎncă nu există evaluări

- FAN73832 (Half-Bridge Dead Time Control)Document16 paginiFAN73832 (Half-Bridge Dead Time Control)Ismael StarkÎncă nu există evaluări

- sc7001q Ay 961Document18 paginisc7001q Ay 961r2c1Încă nu există evaluări

- High and Low Side Driver: Features Product SummaryDocument14 paginiHigh and Low Side Driver: Features Product SummaryFernando Camargo100% (1)

- Quad Power Amplifier With Built-In Voltage Converter: DescriptionDocument10 paginiQuad Power Amplifier With Built-In Voltage Converter: DescriptionbakaninhaÎncă nu există evaluări

- PDF HCF4028Document10 paginiPDF HCF4028Urratul AqyuniÎncă nu există evaluări

- Ca3260, Ca3260A: 4Mhz, Bimos Operational Amplifier With Mosfet Input/Cmos Output FeaturesDocument4 paginiCa3260, Ca3260A: 4Mhz, Bimos Operational Amplifier With Mosfet Input/Cmos Output FeaturesPaulo Cesar SimonettiÎncă nu există evaluări

- cd4007 Intersil DatasheetDocument9 paginicd4007 Intersil DatasheetMarie HayesÎncă nu există evaluări

- MC 14052 DatasheetDocument12 paginiMC 14052 DatasheetgrooyoÎncă nu există evaluări

- 4.1hoja de Datos Del CD40106 PDFDocument6 pagini4.1hoja de Datos Del CD40106 PDFlookb64Încă nu există evaluări

- Rohm Bu2090Document12 paginiRohm Bu2090Alberto Carrillo GuerreroÎncă nu există evaluări

- Low-Power, Slew-Rate-Limited RS-485/RS-422 Transceiver: Description Pin ConfigurationDocument8 paginiLow-Power, Slew-Rate-Limited RS-485/RS-422 Transceiver: Description Pin ConfigurationHaytham SadikÎncă nu există evaluări

- TLC 7628Document12 paginiTLC 7628velizarkoÎncă nu există evaluări

- Low-Cost, Triple, 8-Bit Voltage-Output Dacs With Serial InterfaceDocument16 paginiLow-Cost, Triple, 8-Bit Voltage-Output Dacs With Serial InterfaceBboubrahim BbnnÎncă nu există evaluări

- AZ324Document10 paginiAZ324Franklim Miranda Dos SantosÎncă nu există evaluări

- TDA 6106qDocument12 paginiTDA 6106qqwertyuiÎncă nu există evaluări

- CD4093BM CD4093BC Quad 2-Input NAND Schmitt TriggerDocument8 paginiCD4093BM CD4093BC Quad 2-Input NAND Schmitt TriggerMoroni Zelaya AyalaÎncă nu există evaluări

- ULN2004AC-inversor LvadoraDocument8 paginiULN2004AC-inversor Lvadoraarturo_hernandez_78Încă nu există evaluări

- Precision Waveform Generator/Voltage Controlled Oscillator FeaturesDocument12 paginiPrecision Waveform Generator/Voltage Controlled Oscillator FeaturesCharles Tineo0% (1)

- TX IrhsDocument1 paginăTX IrhsvelizarkoÎncă nu există evaluări

- TLE2061 PrecisionDocument82 paginiTLE2061 PrecisionvelizarkoÎncă nu există evaluări

- Elpa SineDocument12 paginiElpa SinevelizarkoÎncă nu există evaluări

- XR2206Document16 paginiXR2206Himma FirdausÎncă nu există evaluări

- LPA05Document2 paginiLPA05velizarkoÎncă nu există evaluări

- Tsal7200: High Power Infrared Emitting Diode, 950 NM, Gaalas/GaasDocument6 paginiTsal7200: High Power Infrared Emitting Diode, 950 NM, Gaalas/GaasvelizarkoÎncă nu există evaluări

- SP ESS9720 Transformer DatasheetDocument1 paginăSP ESS9720 Transformer DatasheetvelizarkoÎncă nu există evaluări

- Coil-Lock ... Hold-in-Device: From Power Quality Solutions IncDocument2 paginiCoil-Lock ... Hold-in-Device: From Power Quality Solutions IncvelizarkoÎncă nu există evaluări

- Manual QS enDocument24 paginiManual QS envelizarkoÎncă nu există evaluări

- ADocument10 paginiAVictor PuglieseÎncă nu există evaluări

- Catalogue Analyzers and Probes PDFDocument12 paginiCatalogue Analyzers and Probes PDFvelizarkoÎncă nu există evaluări

- Manual QS enDocument24 paginiManual QS envelizarkoÎncă nu există evaluări

- Low Pin Count GuideDocument42 paginiLow Pin Count GuidethelutheranknightÎncă nu există evaluări

- Capacitor DatasheetDocument31 paginiCapacitor DatasheetvelizarkoÎncă nu există evaluări

- Power Sinks M 3000Document2 paginiPower Sinks M 3000velizarkoÎncă nu există evaluări

- IAR Embedded Workbench Version 3+ For MSP430Document31 paginiIAR Embedded Workbench Version 3+ For MSP430leobruno7Încă nu există evaluări

- Manual QS enDocument24 paginiManual QS envelizarkoÎncă nu există evaluări

- Tting StartedDocument51 paginiTting Startedsilviosz68Încă nu există evaluări

- MicroChip Low-Cost Development Tools GuideDocument18 paginiMicroChip Low-Cost Development Tools GuideAdam LundoÎncă nu există evaluări

- PICkit 2 v2.61 User GuideDocument86 paginiPICkit 2 v2.61 User GuideMechDRÎncă nu există evaluări

- Yamaha USB-MIDI Driver Installation GuideDocument8 paginiYamaha USB-MIDI Driver Installation GuideTeo IonelÎncă nu există evaluări

- Exelente Amplificador de 100w TDA7294Document17 paginiExelente Amplificador de 100w TDA7294Everson CorreaÎncă nu există evaluări

- For Pricing, Delivery, and Ordering Information, Please Contact Maxim/Dallas Direct! atDocument12 paginiFor Pricing, Delivery, and Ordering Information, Please Contact Maxim/Dallas Direct! atvelizarkoÎncă nu există evaluări

- Agilent 34401ADocument4 paginiAgilent 34401AvelizarkoÎncă nu există evaluări

- HF Shunts PPA Mar 2012Document1 paginăHF Shunts PPA Mar 2012velizarkoÎncă nu există evaluări

- Tda 7293Document16 paginiTda 7293AntónioRodriguesÎncă nu există evaluări

- TLC 7628Document12 paginiTLC 7628velizarkoÎncă nu există evaluări

- R3-10-15K-LV EN 50549-1 RENblad CertificateDocument2 paginiR3-10-15K-LV EN 50549-1 RENblad CertificateWaldemar Alvares RezendeÎncă nu există evaluări

- Analysis and Design Considerations of A Buck Converter With A Hysteresis PWM ControllerDocument6 paginiAnalysis and Design Considerations of A Buck Converter With A Hysteresis PWM ControllerRGinanjar Nur RahmatÎncă nu există evaluări

- Overall Understanding CT As Per IEC 61869 2 1679333290Document11 paginiOverall Understanding CT As Per IEC 61869 2 1679333290DineshÎncă nu există evaluări

- Electrochemistry 1Document74 paginiElectrochemistry 1Vipranshu GuptaÎncă nu există evaluări

- An Integrated 6 MV Linear Accelerator Model From Electron Gun To Dose in A Water TankDocument11 paginiAn Integrated 6 MV Linear Accelerator Model From Electron Gun To Dose in A Water TankFrançois IdjiwoleÎncă nu există evaluări

- Question 5Document7 paginiQuestion 5nkugwa6brianÎncă nu există evaluări

- WWW Learncbse in Lakhmir Singh Physics Class 10 Solutions Chapter 1 ElectricityDocument83 paginiWWW Learncbse in Lakhmir Singh Physics Class 10 Solutions Chapter 1 ElectricityakritiÎncă nu există evaluări

- Electrical Power Equipment Maintenance and TestingDocument3 paginiElectrical Power Equipment Maintenance and TestingSing Yew LamÎncă nu există evaluări

- Symptom Procedures: Multiport Fuel Injection (Mfi)Document167 paginiSymptom Procedures: Multiport Fuel Injection (Mfi)1342231Încă nu există evaluări

- Reference: LS40M51B11 Code: 1SBV011151R1211 LS40M51B11 Limit SwitchDocument3 paginiReference: LS40M51B11 Code: 1SBV011151R1211 LS40M51B11 Limit SwitchJaime MartinÎncă nu există evaluări

- How To Design Multi-Kw DC - DC Converters For Electric Vehicles (EVs) - Power Factor CorrectionDocument2 paginiHow To Design Multi-Kw DC - DC Converters For Electric Vehicles (EVs) - Power Factor CorrectionThien DinhÎncă nu există evaluări

- Diod S A0007229744 1Document26 paginiDiod S A0007229744 1123Încă nu există evaluări

- Atomic Structure FDocument10 paginiAtomic Structure FRaju SinghÎncă nu există evaluări

- TDJH 182018de 65f (Valdemar)Document1 paginăTDJH 182018de 65f (Valdemar)rauxmataÎncă nu există evaluări

- THAT 2252 DatasheetDocument12 paginiTHAT 2252 DatasheetJoonyoung YoonÎncă nu există evaluări

- Critical ThinkingDocument3 paginiCritical ThinkingJake Lobrigas67% (3)

- Emotron m20 Data Sheet 01-4134-01 enDocument8 paginiEmotron m20 Data Sheet 01-4134-01 enAungÎncă nu există evaluări

- WW LS4Document4 paginiWW LS4alperodabasiÎncă nu există evaluări

- Service Manual 252 769 480 - ADocument146 paginiService Manual 252 769 480 - AariserplÎncă nu există evaluări

- Guantes Dielectricos CATUDocument3 paginiGuantes Dielectricos CATUWilliam RaicoÎncă nu există evaluări

- Mono MaticDocument21 paginiMono MaticRomanChibisovÎncă nu există evaluări

- Karunya University: Division OF Electronics & Instrumentation EngineeringDocument325 paginiKarunya University: Division OF Electronics & Instrumentation EngineeringVishal NairÎncă nu există evaluări

- A Guide To IR - PIR Sensor Set-Up and Testing (2009)Document10 paginiA Guide To IR - PIR Sensor Set-Up and Testing (2009)FarhanaÎncă nu există evaluări

- LUXEON Versat 3030 HP CW 150: Industry-Leading Solutions For Exterior Automotive LightingDocument17 paginiLUXEON Versat 3030 HP CW 150: Industry-Leading Solutions For Exterior Automotive LightingMhmd GhanimÎncă nu există evaluări

- Review of Computers in Process Control 1.1 Data LoggersDocument30 paginiReview of Computers in Process Control 1.1 Data Loggerssisai12u242Încă nu există evaluări

- (Cp1068 A) Digiac UkDocument12 pagini(Cp1068 A) Digiac UkAlberto M FuentesÎncă nu există evaluări