Documente Academic

Documente Profesional

Documente Cultură

Altera Controlling Analog Output From A Digital CPLD Using PWM

Încărcat de

kn65238859Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Altera Controlling Analog Output From A Digital CPLD Using PWM

Încărcat de

kn65238859Drepturi de autor:

Formate disponibile

White Paper Controlling Analog Output From a Digital CPLD Using PWM

Although the Altera MAX IIZ CPLD is a digital programmable logic device, it is versatile enough to control analog systems. This white paper shows how the MAX IIZ CPLD, alone or with a few passive components, can replace a digital-to-analog converter, allowing it to drive an audio speaker and control LED intensity, motor speed, and servo position. This white paper also will explain pulse-width modulator (PWM) operation, as well as describe the efficient implementation and use of PWMs in a MAX IIZ CPLD.

Introduction

A pulse-width modulator (PWM) is a common way of generating analog outputs from a digital component. A PWM replaces a digital-to-analog converter (DAC), which generates analog voltage or current proportional to the digital input. As the name implies, a PWM generates a series of constant voltage or current digital pulses with pulse widths or duty cycles that are proportional to the intended analog strength. The series of modulated pulses can be converted to an analog voltage with a low-pass filter, but this is usually unnecessary. Figure 1 shows a typical analog signal and the digital PWM representation. In general, an analog signal has a maximum amplitude, a minimum amplitude, and many levels in between. In contrast, the PWM only has two levels: maximum and minimum. Figure 1. Analog Signal and Equivalent Pulse-Width Modulation

To convert from analog to digital, the analog signal first is sampled at a carrier frequency. For a given sample period, the area under the analog signal equals the area under the PWM pulse. The key principle behind the PWM is that a short pulse at maximum amplitude has the energy equivalent to a continuous analog signal at a lower amplitude. This simple equation determines the required sample frequency for a PWM circuit: F SAMPLE = 2 F RANGE , where FSAMPLE is the rate at which the analog signal is divided into digital packets, and FRANGE is maximum frequency of the analog signal to be reproduced by the PWM. For audio, this may be 4 KHz for a phone or 20 KHz for an MP3 player. The 2 in the equation comes from the Nyquist frequency, which is the accepted oversampling rate required to reproduce an analog signal from digital samples. The next step is to generate a clock to drive the PWM granularity. The following equation determines the PWM frequency: F PWM = 2 F RANGE R , where FPWM is the clock frequency driving the PWM block, and R is the resolution. The resolution is typically a multiple of 2N (where N = number of bits in the digital data stream words) but with the proposed MAX IIZ PWM, any resolution is possible.

PWM Analog Output Applications

The three most useful analog applications for MAX IIZ PWMs are an LED driver, audio output, and motor control. These allow the MAX IIZ CPLD to control light, sound, and motion for the following functions:

WP-01085-1.0

November 2008, ver. 1.0

Controlling Analog Output From a Digital CPLD Using PWM

Altera Corporation

Light Control LED blink intensity to save power Display back-light intensity Tri-color LED color mixing Sound Audio play back Audible warning messages Ringtones and sound effects Keyboard clicks and tones Motion Motors - Phone vibrators - Game motion feedback - Warning vibrations for controls - Cooling fan control - Keyboard tactile feedback Servos - Analog control voltage - Digital control pulse

Figure 2 shows how easy it is to connect a MAX IIZ CPLD to an LED, speaker, or motor. Typically, a minimal number of external components is required. One misconception about PWM outputs is that they must go through some type of filter to convert the digital signal back to analog before it can be used. In the following examples, only the analog servo motor requires a filter. Figure 2. Circuits for Converting the PWM Signal to Light, Sound, and Motion

V CCIO V CCIO V CCIO R LIMIT Open- drain buffer MAX IIZ Multiple open-drain buffers MAX IIZ DC MOTOR Standard buffer MAX IIZ DC MOTOR Open-drain buffer R MAX IIZ V CCIOV CCIO R LIMIT Standard buffer MAX IIZ R C

ANALOG SERVO

V CCIO V CCIO

Light

A PWM controlling the light intensity is perhaps the simplest function to understand. The human eye cannot detect a light flashing faster than 240 Hz (a period of 4.2 mS), yet it can distinguish thousands of levels of brightness. The percentage of time an LED is on during the 4.2 mS can be as small as 0.01%, or 4.2 uS, and the light still will be seen as dim but not blinking. At 50% of the duty cycle, or 2.1 mS, it is seen as half intensity, and at 100% duty cycle, it is seen as full intensity. A current-limiting resistor prevents the full intensity output from damaging the LED or the MAX IIZ I/O buffer. The MAX IIZ CPLD has an 8-mA I/O current setting that limits the output current and may eliminate a resistor from the bill of materials (BOM).

Motors

MAX IIZ CPLDs can drive some motors directly. Some micro-vibration motors have maximum stall currents and operation currents that are less then 100 mA, and it is possible to drive multiple adjacent outputs with a common PWM signal. For example, a micro-vibration motor has a maximum current of 95 mA. Each MAX IIZ I/O is rated for 16-mA drive. Therefore, six open-drain I/Os working together can drive the motor without damaging the MAX IIZ CPLD.

Altera Corporation

Controlling Analog Output From a Digital CPLD Using PWM

The motor-drive circuit has two Schottky diodes to power and ground. These diodes are normally reverse biased, but will clamp any overshoot or undershoot voltage spikes generated from the motor coil when power is removed or the motor is running after the controller is powered down. Figure 2 shows how to hook up a more powerful motor using a metal-oxide-semiconductor field-effect transistor (MOSFET) device. The gate of the MOSFET has a pull-down resistor that keeps the motor off during the boards power-up and power-down cycles. Speed control with a PWM is very simple. The amount of energy sent to the motor is voltage current time = joules . A motors power and RPM will be the same if the average voltage is 50 percent of the maximum over a set sample period, or if it is the maximum voltage for 50 percent of the sample period. The recommended sample period for a motor driver is F SAMPLE = 1 ( 2 ( RPM MAX 60 ) ) . Staying above this rate eliminates detectable vibration. In addition, a PWM resolution as small as 0.01% can be used for speed or power control.

Sound

It may be necessary to add a current-limiting series resistor to the audio output (speaker or headphone) circuit. Because a speaker is a coil, it is important to have Schottky clamp diodes to prevent coil discharge overshoot and undershoot that could damage the MAX IIZ I/Os. One common misconception is that an audio output requires a filter to convert the digital PWM signal to an analog voltage. A speaker is a machine just like the motor, so the amount of energy imparted on air molecules by the cone is also voltage current time = joules . The speakers ability to generate audio compression waves is the same if the average voltage is 50 percent of the maximum over a set sample period or if it is the maximum voltage for 50 percent of the sample period. A PWM carrier wave of 44.1 KHz generates a CD-quality frequency range, 11 KHz is used for MPEG audio, and 8 KHz is used for digital phone applications. Multiple open-drain I/Os can be used together to increase the power output of the PWM driving a speaker. Controlling the number of I/Os enabled is a simple volume control for an audio PWM system.

Servos

The traditional analog servo arm position is proportional to the control voltage value between the servo power and ground. The PWM output is converted to a stable DC voltage by a low-pass RC filter, and the RC filter value should be designed to have a low-pass cutoff frequency equal to the PWM sample frequency:

F SAMPLE = 1 ( 2 R C )

A cutoff frequency below FSAMPLE increases stability but reduces response time, while a cutoff frequency above FSAMPLE increases jitter but reduces settling time. A new generation of servos uses digital pulse width to specify the servo arm angle, so MAX IIZ PWMs can drive a digital servo directly.

Implementing a PWM

The MAX IIZ architecture supports arithmetic functions much more efficiently then other CPLD architectures. It can implement counters and adders using only one logic element (LE) per bit of word width, and the programmable nature of MAX IIZ CPLDs makes it very easy to make counters of any width and count length. Figure 3 shows the three parts of a MAX IIZ PWM, built using the Quartus II softwares Library of Parameterized Macros (LPM). These LPM blocks-LPM_FF, LPM_COUNTER, and LPM_ADD_SUB-are created using a GUI tool in Quartus II software, which generates Verilog, VHDL, and AHDL file formats. The PWM is clocked by an FPWM-Hz clock source.

Controlling Analog Output From a Digital CPLD Using PWM

Altera Corporation

Figure 3. MAX IIZ PWM

LPM_ADD_SUB LPM_COUNTER CO Q[N..0] CLK SSET N+1 A[N..0] 0 CI S[N..0] N+1 LPM_FF D[N..0] Q[N..0] CLK LOAD SAMPLE_EN N+1 B[N..0] CO N+1 PWM_OUT

DIGITAL DATA STREAM F PWM

The LPM_FF holds the digital value that is to be converted to analog by the PWM. The LPM_FF is loaded when the SAMPLE_EN signal is 1, and the width is set by the bit width of the digital data stream. The LPM_COUNTER is a binary counter that can be set synchronously by the SSET signal to any start value, but is typically 0. The LPM_COUNTER carry output (CO) is 1 when the counter reaches its maximum count. The LPM_COUNTER CO generates the sample enable signal, SAMPLE_EN. Typically the sample period is

2

(N + 1)

F PWM ,

but a custom value can be specified for the synchronous set value in the LPM_COUNTER MegaWizard Plug-In. A PWM with M levels of resolution is made by assigning the synchronous set value to

2

(N + 1)

M1.

Examples where a non-2N resolution would be useful include controlling LED brightness in one percent increments from 0 to 100%, which would require a seven-bit counter with an M of 27. Controlling a servo arm movement from 0 to 245 in 1 increments would require an 8-bit counter with an M of 10. The LPM_ADD_SUB is a binary adder, using the LPM_COUNTER and LPM_FF outputs as the A and B inputs. The LPM_ADD_SUB carry input (CI) is a constant 0, the LPM_ADD_SUB SUM output is not used, and the PWM output (PWM_OUT) is the LPM_ADD_SUB CO. The following three examples explain how this simple structure works for a 4-bit PWM.

When LPM_FF sample is 1, there are 16 additions made as the LPM_COUNTER sequences from 0 to 15. The CO of the adder is 0 for 15 of 16 counts, 0 to 14, and 1 when the count is 15, thus generating a 1/16% duty cycle. When LPM_FF sample is 8, the CO of the adder is 0 for counts 0 to 7, and 1 for the eight remaining counts, 8 to 15, thus generating an 8/16% duty cycle. When LPM_FF sample is 15, the CO of the adder is 0 for only the 0 count, and 1 for the 15 remaining counts, 1 to 15, thus generating a 15/16% duty cycle.

The PWM is very resource efficient. PWMs with a common sample period and resolution can share a single LPM_COUNTER, and a non-2N resolution does not affect efficiency. Table 1 shows the LEs required as a function of bit width.

Altera Corporation

Controlling Analog Output From a Digital CPLD Using PWM

Table 1. PWM LE Requirements Block

LPM_FF LPM_COUNTER LPM_ADD_SUB TOTAL Note: (1) N=log2(Resolution)

First PWM*

N N N 3N

Additional PWM (1)

N 0 N 2N

Even on the smallest MAX IIZ CPLD, the EPM240Z, with 240 LEs, one 8-bit PWM only requires one-tenth of the MAX IIZ resources. Ten 8-bit PWMs require only 168/240 of the MAX IIZ resources.

Conclusion

The PWM is a very powerful tool for converting digital data to analog actions. A MAX IIZ CPLD with PWMs can control all of the analog elements of a system, including light, sound, and motion. The MAX IIZ architecture is well suited to making simple, logic-efficient PWMs, so using the PWM outputs to control analog components like LEDs, speakers, motors, and servos requires only a few passive components.

Further Information

How do digital servos work?: www.servocity.com/html/how_do_servos_work_.html Nyquist frequency: http://en.wikipedia.org/wiki/Nyquist_frequency Sampling Frequency: http://en.wikipedia.org/wiki/Sampling_frequency Literature: MAX II Devices: www.altera.com/literature/lit-max2.jsp Reduce Total System Cost in Portable Applications Using Zero-Power CPLDs: www.altera.com/literature/wp/wp-01001-reduce-total-system-cost-in-portable-apps-using-max.pdf Six Ways to Replace a Microcontroller With a CPLD: www.altera.com/literature/wp/wp-01041-six-ways-to-replace-microcontroller-with-cpld.pdf Using Zero-Power CPLDs to Substantially Lower Power Consumption in Portable Applications: www.altera.com/literature/wp/wp-01042-using-zero-power-cplds-to-lower-power-in-portable.pdf Using LEDs as Light-Level Sensors and Emitters: www.altera.com/literature/wp/wp-01076-led-driver-reduces-power-adjusting-intensity-ambient-light.pdf Developing Multipoint Touch-Screens and Panels With CPLDs: www.altera.com/literature/wp/wp-01086-multipoint-touchscreens-panels-cplds.pdf

Acknowledgements

Rafael Camarota, Non-Volatile Product Line Manager, Low-Cost Products Group, Altera Corporation Judd Heape, Sr. Technical Marketing Manager, Consumer and Automotive Business Unit, Altera Corporation

101 Innovation Drive San Jose, CA 95134 www.altera.com

Copyright 2008 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

S-ar putea să vă placă și

- Altera FPGAs Enable Energy-Efficient Motor Control in Next-Generation Smart Home AppliancesDocument5 paginiAltera FPGAs Enable Energy-Efficient Motor Control in Next-Generation Smart Home Applianceskn65238859Încă nu există evaluări

- Altera A Flexible Architecture For Fisheye Correction in Automotive Rear-View CamerasDocument8 paginiAltera A Flexible Architecture For Fisheye Correction in Automotive Rear-View Cameraskn65238859Încă nu există evaluări

- Altera Power-Optimized Solutions For Telecom ApplicationsDocument9 paginiAltera Power-Optimized Solutions For Telecom Applicationskn65238859Încă nu există evaluări

- Altera 40-Nm FPGAs - Architecture and Performance ComparisonDocument16 paginiAltera 40-Nm FPGAs - Architecture and Performance Comparisonkn65238859Încă nu există evaluări

- Altera Crest Factor Reduction For OFDM-Based Wireless SystemsDocument6 paginiAltera Crest Factor Reduction For OFDM-Based Wireless Systemskn65238859Încă nu există evaluări

- Altera Voltage Regulator Selection For FPGAsDocument8 paginiAltera Voltage Regulator Selection For FPGAsknowhim26002Încă nu există evaluări

- Altera 40-Nm FPGA Power Management and AdvantagesDocument15 paginiAltera 40-Nm FPGA Power Management and Advantageskn65238859Încă nu există evaluări

- Altera Leveraging The 40-Nm Process Node To Deliver The World's Most Advanced Custom Logic DevicesDocument8 paginiAltera Leveraging The 40-Nm Process Node To Deliver The World's Most Advanced Custom Logic Deviceskn65238859Încă nu există evaluări

- Altera Selecting The Ideal FPGA Vendor For Military ProgramsDocument7 paginiAltera Selecting The Ideal FPGA Vendor For Military Programskn65238859Încă nu există evaluări

- Altera Video Processing On FPGAs For Military Electro-Optical - Infrared ApplicationsDocument5 paginiAltera Video Processing On FPGAs For Military Electro-Optical - Infrared Applicationskn65238859Încă nu există evaluări

- Altera Generating Functionally Equivalent FPGAs and ASICs With A Single Set of RTL and Synthesis - Timing ConstraintsDocument11 paginiAltera Generating Functionally Equivalent FPGAs and ASICs With A Single Set of RTL and Synthesis - Timing Constraintskn65238859Încă nu există evaluări

- Altera Radiocomp Remote Radio Heads and The Evolution Towards 4G NetworksDocument5 paginiAltera Radiocomp Remote Radio Heads and The Evolution Towards 4G Networkskn65238859Încă nu există evaluări

- White Paper Developing Multipoint Touch Screens and Panels With CpldsDocument5 paginiWhite Paper Developing Multipoint Touch Screens and Panels With Cpldssan2244Încă nu există evaluări

- Altera Taray Avoiding PCB Design Mistakes in FPGA-Based SystemsDocument5 paginiAltera Taray Avoiding PCB Design Mistakes in FPGA-Based Systemskn65238859Încă nu există evaluări

- Altera Assessing FPGA DSP Benchmarks at 40 NMDocument6 paginiAltera Assessing FPGA DSP Benchmarks at 40 NMkn65238859Încă nu există evaluări

- Altera Using FPGAs To Render Graphics and Drive LCD InterfacesDocument9 paginiAltera Using FPGAs To Render Graphics and Drive LCD Interfaceskn65238859Încă nu există evaluări

- Altera Generating Panoramic Views by Stitching Multiple Fisheye ImagesDocument9 paginiAltera Generating Panoramic Views by Stitching Multiple Fisheye Imageskn65238859Încă nu există evaluări

- Altera FPGAs at 40 NM And) 10 Gbps - Jitter, Signal Integrity, Power, and Process-Optimized TransceiversDocument39 paginiAltera FPGAs at 40 NM And) 10 Gbps - Jitter, Signal Integrity, Power, and Process-Optimized Transceiverskn65238859Încă nu există evaluări

- Altera Six Ways To Replace A Microcontroller With A CPLDDocument8 paginiAltera Six Ways To Replace A Microcontroller With A CPLDkn65238859Încă nu există evaluări

- Altera Simplifying Simultaneous Multimode RRH Hardware DesignDocument13 paginiAltera Simplifying Simultaneous Multimode RRH Hardware Designkn65238859Încă nu există evaluări

- Altera Enabling Ethernet-Over-NG-SONET - SDH - PDH Solutions For MSPP LinecardsDocument4 paginiAltera Enabling Ethernet-Over-NG-SONET - SDH - PDH Solutions For MSPP Linecardskn65238859Încă nu există evaluări

- Altera Using Zero-Power CPLDs To Substantially Lower Power Consumption in Portable ApplicationsDocument7 paginiAltera Using Zero-Power CPLDs To Substantially Lower Power Consumption in Portable Applicationskn65238859Încă nu există evaluări

- Altera Automating DSP Simulation and Implementation of Military Sensor SystemsDocument6 paginiAltera Automating DSP Simulation and Implementation of Military Sensor Systemskn65238859Încă nu există evaluări

- Altera Understanding Metastability in FPGAsDocument6 paginiAltera Understanding Metastability in FPGAskn65238859Încă nu există evaluări

- Altera Implementing A Cost-Effective Human-Machine Interface For Home AppliancesDocument8 paginiAltera Implementing A Cost-Effective Human-Machine Interface For Home Applianceskn65238859Încă nu există evaluări

- Altera FPGA Coprocessing Evolution - Sustained Performance Approaches Peak PerformanceDocument8 paginiAltera FPGA Coprocessing Evolution - Sustained Performance Approaches Peak Performancekn65238859Încă nu există evaluări

- Altera Protecting The FPGA Design From Common ThreatsDocument5 paginiAltera Protecting The FPGA Design From Common Threatskn65238859Încă nu există evaluări

- Altera Reduce Total System Cost in Portable Applications Using MAX II CPLDsDocument6 paginiAltera Reduce Total System Cost in Portable Applications Using MAX II CPLDskn65238859Încă nu există evaluări

- Altera Energy-Aware Appliance Platform - A New Approach To Home Energy ControlDocument8 paginiAltera Energy-Aware Appliance Platform - A New Approach To Home Energy Controlkn65238859Încă nu există evaluări

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (400)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (266)

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (588)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2259)

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (121)

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- Chapter 3D PIC18 Assembly Programming Part DDocument13 paginiChapter 3D PIC18 Assembly Programming Part DAndy WoÎncă nu există evaluări

- MST9220B: General Description FeaturesDocument8 paginiMST9220B: General Description FeaturespepenitoÎncă nu există evaluări

- SCX2 190BB PDFDocument2 paginiSCX2 190BB PDFIvan José Campos MadridÎncă nu există evaluări

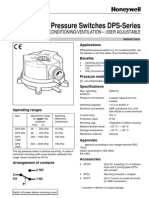

- Honeywell Diff P Switch DPSDocument2 paginiHoneywell Diff P Switch DPSFrinaru CiprianÎncă nu există evaluări

- Manual CRT SS7900 ENG-3Document23 paginiManual CRT SS7900 ENG-3Dante NeroÎncă nu există evaluări

- Liquid Crystals Seminar SMDocument7 paginiLiquid Crystals Seminar SMSmriti100% (1)

- BodyGuard I-Tag For Heavy Equipment r2.6Document7 paginiBodyGuard I-Tag For Heavy Equipment r2.6sarkochileÎncă nu există evaluări

- ABB+In+Brief 2 11Document32 paginiABB+In+Brief 2 11Wasinchai KanjanapanÎncă nu există evaluări

- Hyosung Error Codes PDFDocument14 paginiHyosung Error Codes PDFbudi yonoÎncă nu există evaluări

- BC556, B BC557, A, B, C BC558, B: MccsemiDocument5 paginiBC556, B BC557, A, B, C BC558, B: MccsemiRogerio Morais Do NascimentoÎncă nu există evaluări

- Motivation LetterDocument2 paginiMotivation Letterএফএমসারোয়ারহোসেন100% (1)

- Unisonic Technologies Co., LTD: Voltage Mode PWM Control CircuitDocument7 paginiUnisonic Technologies Co., LTD: Voltage Mode PWM Control CircuitEnica LiviaÎncă nu există evaluări

- Circuit Symbols of Electronic Components - HomeDocument9 paginiCircuit Symbols of Electronic Components - Homesef_razumanÎncă nu există evaluări

- Pe - 1970-12Document102 paginiPe - 1970-12Anonymous kdqf49qbÎncă nu există evaluări

- ABL8MEM24012: Panel Mount DIN Rail MountDocument1 paginăABL8MEM24012: Panel Mount DIN Rail MountSebastian Alexis Muñoz PoveaÎncă nu există evaluări

- TQBM 70159016 D172718DEI 65FT2v01 PDFDocument1 paginăTQBM 70159016 D172718DEI 65FT2v01 PDFAnonymous OM5uU6Încă nu există evaluări

- DA Miseluk TextDocument14 paginiDA Miseluk TextVladimir ĐorđevićÎncă nu există evaluări

- CVA ProDocument1 paginăCVA ProTommy TangÎncă nu există evaluări

- Chapter 3 - Combinational Logic Circuits (Part 1) - Digital ElectronicsDocument12 paginiChapter 3 - Combinational Logic Circuits (Part 1) - Digital ElectronicsRakesh KumarÎncă nu există evaluări

- 5-9 - Autodiagnostico HYUNDAI 360Document12 pagini5-9 - Autodiagnostico HYUNDAI 360Milton IngTec Tecnologia100% (1)

- NUS ME Core Modules 20190925 PDFDocument3 paginiNUS ME Core Modules 20190925 PDFHammadAzizÎncă nu există evaluări

- Budgetary Cost - TNB Sub Station Electrical WorkDocument2 paginiBudgetary Cost - TNB Sub Station Electrical WorkAhmad Hisham Shuhim33% (3)

- 45-53.8 11063344 PDFDocument40 pagini45-53.8 11063344 PDFeng13Încă nu există evaluări

- Cisco: Basic Switch and VLAN Configuration Guide With ExamplesDocument17 paginiCisco: Basic Switch and VLAN Configuration Guide With Examplessmuscat72Încă nu există evaluări

- Arena Details: 1. Death RaceDocument6 paginiArena Details: 1. Death Racemanik_chand_patnaikÎncă nu există evaluări

- Emed ES300 Operation ManualDocument30 paginiEmed ES300 Operation Manualhany madcorÎncă nu există evaluări

- Ieee 1346-1998Document45 paginiIeee 1346-1998pepitorodirguez100% (1)

- Uquran How ToDocument4 paginiUquran How Togw1921Încă nu există evaluări

- Analog and Digital Electronics Lab Manual PDFDocument109 paginiAnalog and Digital Electronics Lab Manual PDFShaun ThomasÎncă nu există evaluări

- 1C - Communication Networks - Circuit SwitchingDocument14 pagini1C - Communication Networks - Circuit SwitchingDang KhueÎncă nu există evaluări