Documente Academic

Documente Profesional

Documente Cultură

9A10504 Linear and Digital IC Applications

Încărcat de

sivabharathamurthyDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

9A10504 Linear and Digital IC Applications

Încărcat de

sivabharathamurthyDrepturi de autor:

Formate disponibile

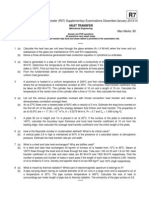

Code: 9A10504

B.Tech III Year II Semester (R09) Regular & Supplementary Examinations, April/May 2013 LINEAR AND DIGITAL IC APPLICATIONS (Common to EEE and MCT) Time: 3 hours Max. Marks: 70 Answer any FIVE questions All questions carry equal marks ***** 1 (a) List out different configurations of differential amplifier. (b) Compare and contrast an ideal op - amp and practical op - amp. (c) List out the AC characteristics of an op - amp and discuss about them. (a) Design a differentiator to differentiate an input signal that varies in frequency from to about . If a sine wave of peak at is applied to this differentiator draw the output waveforms. (b) Design a logarithmic amplifier for positive input voltages in the range to . (a) Draw the block schematic of a PLL describing the function of each block briefly. (b) Explain the different applications of PLL. (a) Design a 4 - input CMOS AND-OR-INVERT gate. Draw the logic diagram and function table. (b) Distinguish between static and dynamic power dissipation of a CMOS circuit. (a) Compare CMOS, TTL and ECL with reference to logic levels, DC noise margin propagation delay and fanout. (b) Design a transistor circuit of 2 - input ECL NOR gate. Explain the operation with the help of function table. (a) Explain structural design elements of VHDL. (b) Explain with example the syntax and the function of the following VHDL statements: (i) Concurrent signal assignment statement (ii) Selected signal assignment statement (iii) Port map (a) Using two 74X138 decoders design a 4 to 16 decoder. (b) Write a data flow style VHDL program for the above design. (a) Explain working of the various programmable logic devices. (b) Differentiate between ripple counter and synchronous counter. Design a 4 - bit counter in both modes and estimate the propagation delay. *****

Code: 9A10504

B.Tech III Year II Semester (R09) Regular & Supplementary Examinations, April/May 2013 LINEAR AND DIGITAL IC APPLICATIONS (Common to EEE and MCT) Time: 3 hours Max. Marks: 70 Answer any FIVE questions All questions carry equal marks ***** 1 (a) Define thermal drift. What is the need for frequency compensation? (b) Explain the DC characteristics of op - amp. (a) Draw the circuit diagram of a two input non inverting type summing amplifier and derive the expression for output voltage. (b) Explain the operation of log amplifier using op - amp. (a) Explain the terms lock range, capture range and pull - in time of a PLL. (b) Design and explain a 555 astable multivibrator to operate at 10 KHz with 40% duty cycle. (a) Explain briefly MOS and CMOS logic families and give different CMOS characteristics. (b) Draw the circuit of CMOS NOR gate and explain its operation. Mention any two points about the advantages of CMOS over the other digital logic families. (a) Design TTL three state NAND gate and explain the operation with the help of functional table. (b) Which is the fastest non - saturated logic gate? Draw the circuit and explain its functions. (a) Explain the difference between function and procedure supported by VHDL. Give the necessary examples. (b) Explain data - flow design elements of VHDL. (a) Give the working principle of analog - multiplexer. Give block diagram of a 16 input analog multiplexer using CMOS gates and explain how it works. (b) Draw the logic diagram of 74X174 IC and explain the operation. Develop the VHDL mode for this IC. (a) Explain the operation of edge triggered T flip - flop. (b) Explain about asynchronous flip flops.

*****

Code: 9A10504

B.Tech III Year II Semester (R09) Regular & Supplementary Examinations, April/May 2013 LINEAR AND DIGITAL IC APPLICATIONS (Common to EEE and MCT) Time: 3 hours Max. Marks: 70 Answer any FIVE questions All questions carry equal marks ***** 1 (a) Give the design procedure of a compensating network for an OP - AMP which uses supply voltages. Assume necessary data. (b) Explain ac analysis of differential amplifier. 2 (a) Describe the principle of operation of precision half wave rectifier with waveforms. (b) Explain the operation of antilog amplifier using op - amp. 3 (a) Explain how a 555 timer in astable mode can be used for FSK generation. (b) Design a PLL circuit using 565 IC to get free running frequency = 4.5 KHz, lock range = 2 KHz, capture range = 100 Hz. Assume supply voltages of are available. Show the circuit diagram. 4 (a) What are the parameters that are necessary to define the electrical characteristics of CMOS circuits? Mention the typical values for a CMOS NAND gate. (b) Compare HC, HCT, VHC and VHCT CMOS logic families with the help of output specifications with from 4.5 to 5.5 V. 5 (a) Explain the features of the TTL logic family. (b) Explain the concept and implementation of ECL logic family. 6 (a) Explain the various data types supported by VHDL. Give the necessary examples. (b) Write a VHDL program to detect prime number of a 8 - bit input. 7 (a) Design a 24 - bit group ripple adder using 74X283 ICs. (b) Explain de - multiplexer in detail. 8 (a) Design an 8 - bit synchronous binary counter with serial enable control. (b) Distinguish between latch and flip - flop. Show the logic diagram for both. Explain the operation with the help of function table.

*****

Code: 9A10504

B.Tech III Year II Semester (R09) Regular & Supplementary Examinations, April/May 2013 LINEAR AND DIGITAL IC APPLICATIONS (Common to EEE and MCT) Time: 3 hours Max. Marks: 70 Answer any FIVE questions All questions carry equal marks ***** 1 (a) Explain how large open circuit voltage gain of an op - amp can be obtained by using cascading of differential amplifier stages. (b) Explain the function of various blocks in block diagram of an op - amp. (a) With suitable circuit diagram explain the operation of a triangular wave generator using a comparator and a integrator. (b) What is an instrumentation amplifier? List any three applications of the instrumentation amplifier. (a) Explain frequency translation and FM detection applications of PLL. (b) Derive an expression for capture range of PLL. (a) Draw the circuit for CMOS OR logic gate and explain its working clearly. (b) Which CMOS or TTL logic family has the strongest output driving capability? Explain. (a) Explain how CMOS - TTL interfacing can be achieved. Give the input and output levels of voltages, explain briefly. (b) Explain low voltage CMOS logic and ECL. (a) Design the logic circuit and write a data - flow style VHDL program for the following function:

(b) Explain the use of packages. Give the syntax and structure of a package in VHDL. 7 (a) Write VHDL program for 8 - bit comparator circuit. Using this entity write VHDL program for 24 bit comparator. (b) Design a 4 - bit carry look ahead adder using gates. (a) Explain with neat sketch how four bits 1110 are serially entered into the shift register. (b) With neat circuit diagram explain a master-slave flip-flop and also draw the timing diagram.

*****

S-ar putea să vă placă și

- SSC Social Textbook (AP)Document100 paginiSSC Social Textbook (AP)sivabharathamurthyÎncă nu există evaluări

- SSC Telugu (FL) (AP)Document232 paginiSSC Telugu (FL) (AP)sivabharathamurthyÎncă nu există evaluări

- Control Systems (CS) Notes As Per JntuaDocument203 paginiControl Systems (CS) Notes As Per Jntuasivabharathamurthy100% (3)

- 9A05707 Software Project ManagementDocument4 pagini9A05707 Software Project ManagementsivabharathamurthyÎncă nu există evaluări

- R7410407 Operating SystemsDocument1 paginăR7410407 Operating SystemssivabharathamurthyÎncă nu există evaluări

- R7410506 Mobile ComputingDocument1 paginăR7410506 Mobile ComputingsivabharathamurthyÎncă nu există evaluări

- 07A4EC01 Environmental StudiesDocument1 pagină07A4EC01 Environmental StudiessivabharathamurthyÎncă nu există evaluări

- R5410201 Neural Networks & Fuzzy LogicDocument1 paginăR5410201 Neural Networks & Fuzzy LogicsivabharathamurthyÎncă nu există evaluări

- R7311006 Process Control InstrumentationDocument1 paginăR7311006 Process Control InstrumentationsivabharathamurthyÎncă nu există evaluări

- Code: R7311306: (Electronics & Control Engineering)Document1 paginăCode: R7311306: (Electronics & Control Engineering)sivabharathamurthyÎncă nu există evaluări

- R7312301 Transport Phenomena in BioprocessesDocument1 paginăR7312301 Transport Phenomena in BioprocessessivabharathamurthyÎncă nu există evaluări

- R7311205 Distributed DatabasesDocument1 paginăR7311205 Distributed DatabasessivabharathamurthyÎncă nu există evaluări

- R7311506 Operating SystemsDocument1 paginăR7311506 Operating SystemssivabharathamurthyÎncă nu există evaluări

- 9A13701 Robotics and AutomationDocument4 pagini9A13701 Robotics and AutomationsivabharathamurthyÎncă nu există evaluări

- R7310506 Design & Analysis of AlgorithmsDocument1 paginăR7310506 Design & Analysis of AlgorithmssivabharathamurthyÎncă nu există evaluări

- R7310406 Digital CommunicationsDocument1 paginăR7310406 Digital CommunicationssivabharathamurthyÎncă nu există evaluări

- 9A14503 Principles of Machine DesignDocument8 pagini9A14503 Principles of Machine DesignsivabharathamurthyÎncă nu există evaluări

- 9A05505 Operating SystemsDocument4 pagini9A05505 Operating SystemssivabharathamurthyÎncă nu există evaluări

- R7310206 Linear Systems AnalysisDocument1 paginăR7310206 Linear Systems AnalysissivabharathamurthyÎncă nu există evaluări

- R7310106 Engineering GeologyDocument1 paginăR7310106 Engineering GeologysivabharathamurthyÎncă nu există evaluări

- 9A02505 Electrical Machines-IIIDocument4 pagini9A02505 Electrical Machines-IIIsivabharathamurthyÎncă nu există evaluări

- R5310204 Power ElectronicsDocument1 paginăR5310204 Power ElectronicssivabharathamurthyÎncă nu există evaluări

- 9A23501 Heat Transfer in BioprocessesDocument4 pagini9A23501 Heat Transfer in BioprocessessivabharathamurthyÎncă nu există evaluări

- R7310306 Heat TransferDocument1 paginăR7310306 Heat Transfersivabharathamurthy100% (1)

- R5310406 Digital CommunicationsDocument1 paginăR5310406 Digital CommunicationssivabharathamurthyÎncă nu există evaluări

- 9A15502 Digital System DesignDocument4 pagini9A15502 Digital System Designsivabharathamurthy100% (1)

- 9A04504 Digital IC ApplicationsDocument4 pagini9A04504 Digital IC ApplicationssivabharathamurthyÎncă nu există evaluări

- 9A03505 Heat TransferDocument4 pagini9A03505 Heat TransfersivabharathamurthyÎncă nu există evaluări

- 9A21506 Mechanisms & Mechanical DesignDocument8 pagini9A21506 Mechanisms & Mechanical DesignsivabharathamurthyÎncă nu există evaluări

- 9A10505 Principles of CommunicationsDocument4 pagini9A10505 Principles of CommunicationssivabharathamurthyÎncă nu există evaluări

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5784)

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (399)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (890)

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (587)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (265)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (344)

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (72)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (119)

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- Iot Lab ManualeditedDocument29 paginiIot Lab ManualeditedprashantÎncă nu există evaluări

- ON Orks: PLT-22 Power Line Transceiver User's GuideDocument128 paginiON Orks: PLT-22 Power Line Transceiver User's Guidefouad abdÎncă nu există evaluări

- Low Noise Amplifier Design and OptimizationDocument57 paginiLow Noise Amplifier Design and OptimizationPranjal JalanÎncă nu există evaluări

- Allen Practice AnalogDocument23 paginiAllen Practice AnalogvarunjothishÎncă nu există evaluări

- IQ4/IO/..: I/O Expansion ModulesDocument12 paginiIQ4/IO/..: I/O Expansion ModulesRaviÎncă nu există evaluări

- Isolated Mosfet Gate Driver PaperDocument6 paginiIsolated Mosfet Gate Driver PapergenwittsÎncă nu există evaluări

- EE215: Fundamentals of Electrical Engineering Lab 4 Time Delay CircuitsDocument6 paginiEE215: Fundamentals of Electrical Engineering Lab 4 Time Delay CircuitsÁo ĐenÎncă nu există evaluări

- EE370 L1 IntroductionDocument38 paginiEE370 L1 IntroductionAnshul GoelÎncă nu există evaluări

- LG 32LF550B LB55HDocument74 paginiLG 32LF550B LB55HMarcio100% (2)

- Two-Level Temperature Switch Circuit With LM358Document10 paginiTwo-Level Temperature Switch Circuit With LM358zigmund zigmundÎncă nu există evaluări

- Effect Pedal GroundingDocument10 paginiEffect Pedal GroundingFooÎncă nu există evaluări

- IC 741 Op Amp Specifications and ApplicationsDocument90 paginiIC 741 Op Amp Specifications and ApplicationsAhmed Al MansurÎncă nu există evaluări

- Class Notes PDFDocument24 paginiClass Notes PDFhariÎncă nu există evaluări

- How to Make a Laser Diode Driver Circuit for Burning PaperDocument5 paginiHow to Make a Laser Diode Driver Circuit for Burning PaperbabalguitarÎncă nu există evaluări

- Experiment No. 3: 1.0 TitleDocument5 paginiExperiment No. 3: 1.0 TitlekalangeÎncă nu există evaluări

- CMOS Analog IC Design For 5G PDFDocument2 paginiCMOS Analog IC Design For 5G PDFshakti sindhuÎncă nu există evaluări

- Very Low Drop Voltage Regulator: DescriptionDocument8 paginiVery Low Drop Voltage Regulator: Descriptionjulio montenegroÎncă nu există evaluări

- Breadboard ProyectsDocument162 paginiBreadboard Proyectssneyderth angelo castro camposÎncă nu există evaluări

- Final-Revise-Research CHALLENGES ENCOUNTERED IN PCB LAYOUTDocument70 paginiFinal-Revise-Research CHALLENGES ENCOUNTERED IN PCB LAYOUTMark Anthony RamosÎncă nu există evaluări

- Motorola Gp328 338 Service ManualDocument272 paginiMotorola Gp328 338 Service Manualhankruan86% (7)

- XTR300EVM User's GuideDocument9 paginiXTR300EVM User's Guideapi-3725139Încă nu există evaluări

- A Project Report ON "Light Sensor": Submitted To: Submitted byDocument27 paginiA Project Report ON "Light Sensor": Submitted To: Submitted bymanvi SinghÎncă nu există evaluări

- Manual Servicio Oximetro Mindray Pm50Document35 paginiManual Servicio Oximetro Mindray Pm50Franz David Bastidas MayaÎncă nu există evaluări

- 5 Pin Interface, Version 2.9, 01.02.2010Document10 pagini5 Pin Interface, Version 2.9, 01.02.2010msalem73Încă nu există evaluări

- OverallDocument14 paginiOverallZac BismonteÎncă nu există evaluări

- DN000092.G S Series BMS Data SheetDocument26 paginiDN000092.G S Series BMS Data SheetReetwan SarkarÎncă nu există evaluări

- TAICDocument8 paginiTAICparthÎncă nu există evaluări

- Digital Electronics RK Kanodia & Ashish MuroliaDocument487 paginiDigital Electronics RK Kanodia & Ashish MuroliaAnkit Choudhary100% (1)

- Moore's Law - SoCDocument35 paginiMoore's Law - SoCbalajibs203285Încă nu există evaluări