Documente Academic

Documente Profesional

Documente Cultură

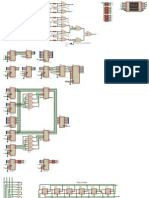

SAP-1 Simple As Possible Computer With Discrete Component RAM

Încărcat de

pong74lsTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

SAP-1 Simple As Possible Computer With Discrete Component RAM

Încărcat de

pong74lsDrepturi de autor:

Formate disponibile

Data

Input

Program

Counter

Data

Output

W-Bus

T1

T2

T3

T4

T5

T6

Address

Input

VCC

U24:A

1

VCC

CLR

?

?

?

?

?

?

2

Cp

Ep

Lm

CE

Li

Ei

La

Ea

Su

Eu

Lb

Lo

SW5

ADR3

ADR2

ADR1

ADR0

Start

Clear/Start

4

6

?

?

?

?

?

?

?

?

?

?

?

?

D7

D6

D5

D4

D3

D2

D1

D0

U24:B

Clear

CLR

VCC

OP0

OP1

OP2

OP3

OP4

OP5

OP6

OP7

W0

W1

W2

W3

W4

W5

W6

W7

PC0

PC1

PC2

PC3

D0

D1

D2

D3

D4

D5

D6

D7

ADR0

ADR1

ADR2

U24:C

9

VCC

8

10

D7

D6

D5

D4

D3

D2

D1

D0

ADR3

ADR2

ADR1

ADR0

ADR3

7400

SW6

5

6

7

8

9

10

11

12

13

14

15

16

VCC

SW1

Low

Single Step

VCC

SW3

OPCode / Data

Switches

12

11

SW4

WEram

ENmar

Write

Memory

13

VCC

Program/Run

SW2: Open=Run Closed=Program

1

2

13

12

U26:A

1

VCC

U26:D

3

2

To program:

1) Switch SW2 marked Run/Program should be DOWN in the program position.

2) Switch SW7 marked Manual/Auto should be UP in the manual position.

3) Use the 4 address and 8 data input switches to enter each line of the program.

Observe the Address and Data Input 7-segment displays to see what is being entered.

4) Press the Write Memory button once to write data to RAM.

SW7

U27:A

U27:B

13

11

Manual

U27:C

U26:B

Auto

U25:B

4

6

10

14

18

20

CLK

Note: The 555 timer circuit has been substituted with

a virtual clock source to speed up the simulation.

U25:B(C)

INIT=LOW

START=0

COUNT=-1

CLOCK=2

PC3

PC2

PC1

PC0

3

4

5

HLT

VCC

Here is a sample test program:

Address Data

0

09

1

1A

2

1b

3

2C

4

E0

5

F0

CLK

12

Manual/Auto

Once data is written, the run the program:

1) Switch the SW2 Run/Program switch UP to the run position.

2) Switch the SW7 Manual/Auto switch DOWN to start the clock.

W7 W6 W5 W4 W3 W2 W1 W0

Cp

74LS107

12

Q

74LS107

CLK

6

12

CLK

2

11

CLK

6

13

CLK

2

13

The program is 10h + 14h + 18h - 20h = 1Ch so the output display should show 1C

and the HLT signal should be active when the program is finished running.

Hopefully it works for you too.

74LS107

J

10

U2:B

CLK

11

10

74LS107

3

U2:A

U1:B

U1:A

9

A

b

C

U25:A

HLT

7400

8

7

6

5

4

3

2

1

OFF

4

3

2

1

ON

ON

OFF

Address

Switches

U24:D

High

SW2

U3:D

U10

CLK

OE1

OE2

E1

E2

MR

D0

D1

D2

D3

CLK

OE1

OE2

E1

E2

MR

D0

D1

D2

D3

U11

74LS173

Accumulator

3

4

5

6

3

4

5

6

Q0

Q1

Q2

Q3

74LS173

Accumulator

Q0

Q1

Q2

Q3

Ep

14

13

12

11

7

1

2

9

10

15

14

13

12

11

11

74LS126

CLK

La

7

1

2

9

10

15

CLK

La

13

10

U3:C

12

U3:B

CLR

U3:A

CLK

Ea

11

12

13

14

D3

D2

D1

D0

U4

Q3

Q2

Q1

Q0

74LS173

Memory Address Register

15

10

9

2

1

7

MR

E2

E1

OE2

OE1

CLK

Ea

Lm

10

10

6

5

4

3

ADR0

ADR1

ADR2

ADR3

13

13

ENmar

11

12

12

13

14

10

11

6

5

3

2

15

1

11

4B

4A

3B

3A

2B

2A

1B

1A

E

A/B

2Y

1Y

4

3Y

9

4Y

74LS126

Accumulator

Output

74LS126

Accumulator

Output

74LS157

2-1 Multiplexer

12

U12:D

U13:D

U5

U49

VCC

6

4

5

E1

E2

E3

13

12

10

Su

13

12

10

Su

5

I0

I1

I2

I3

I4

I5

I6

I7

15

14

13

12

11

10

9

7

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

A

B

C

1

2

3

U15:D

U14:D

74LS86

74LS86

A

B

C

6

4

5

E1

E2

E3

11

11

6

2

15

11

C0

A0

A1

A2

A3

B0

B1

B2

B3

5

3

14

12

C4

9

S0

S1

S2

S3

4

1

13

10

12

13

11

11

74LS126

10

8

4

6

1

3

13

12

10

8

U18:D

74LS126

Eu

15

14

13

12

11

10

9

7

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

C0

4

U52

CE

5

1

74LS138

1

2

3

74LS283

Full Adder

(MSB)

U19:D

E1

E2

E3

U16

Carry

O0

O1

O2

O3

O4

O5

O6

O7

6

4

5

VCC

15

14

13

12

11

10

9

7

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

U17

C4

S0

S1

S2

S3

4

1

13

10

U51

A

B

C

Carry

74LS283

Full Adder

(LSB)

74HCT238

16-byte RAM

Latch Enable Decoder

1

2

3

6

2

15

11

5

3

14

12

Su

E1

E2

E3

I8

I9

I10

I11

I12

I13

I14

I15

B0

B1

B2

B3

15

14

13

12

11

10

9

7

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

A0

A1

A2

A3

A

B

C

6

4

5

WEram

U50

1

2

3

74HCT238

O8

O9

O10

O11

O12

O13

O14

O15

74LS138

16-byte RAM

Output Enable Decoder

CLK

Lb

CLK

Lb

O11

I11

1

11

3

4

7

8

13

14

17

18

O12

I12

1

11

3

4

7

8

13

14

17

18

O13

I13

1

11

3

4

7

8

13

14

17

18

O14

I14

1

11

3

4

7

8

13

14

17

18

O15

I15

1

11

7

1

2

9

10

15

CLK

OE1

OE2

E1

E2

MR

D0

D1

D2

D3

Q0

Q1

Q2

Q3

OP4

OP5

OP6

OP7

OP0

OP1

OP2

OP3

Q

CLK

6

U38:B

74LS107

1

9

Q

CLK

6

12

CLK

2

11

11

12

CLK

11

CLK

6

10

13

10

13

5

10

U31:C

CLR

U31:D

12

13

T6

OE

LE

T4

2

5

6

9

12

15

16

19

T3

T2

T1

U35:E

1

2

U32:A

1

4

5

LDA

ADD

SUB

U35:B

U33:A

OE

LE

D0

D1

D2

D3

D4

D5

D6

D7

2

5

6

9

12

15

16

19

OE

LE

D0

D1

D2

D3

D4

D5

D6

D7

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

2

5

6

9

12

15

16

19

OE

LE

D0

D1

D2

D3

D4

D5

D6

D7

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

2

5

6

9

12

15

16

19

OE

LE

D0

D1

D2

D3

D4

D5

D6

D7

OE

LE

74LS373

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

2

5

6

9

12

15

16

19

10

13

12

10

13

12

10

13

12

11

11

11

U45:B

3

4

5

1

2

13

U45:A

U46:A

U46:B

U47:B

U47:C

U47:F

Li

Ei

La

Ea

U48:A

2

12

CE

U48:B

U47:D

Lm

3

1

U47:E

Su

U47:A

13

12

HLT

U34:A

Cp Ep

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

U44:B

11

2

5

6

9

12

15

16

19

U44:A

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

U43:C

U35:F

10

D0

D1

D2

D3

D4

D5

D6

D7

U33:B

12

13

4

5

U42:D

6

3

4

5

1

2

U41:D

U35:C

6

OE

LE

U40:D

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

10

U39:D

1

2

OE

LE

D0

D1

D2

D3

D4

D5

D6

D7

9

10

4

5

2

5

6

9

12

15

16

19

12

13

2

5

6

9

12

15

16

19

OUT

U32:B

8

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

Control Matrix

U35:A

6

9

10

OE

LE

D0

D1

D2

D3

D4

D5

D6

D7

Instruction Decoder

12

13

2

5

6

9

12

15

16

19

9

10

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

12

D0

D1

D2

D3

D4

D5

D6

D7

U35:D

12

OE

LE

13

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

13

D0

D1

D2

D3

D4

D5

D6

D7

T5

3

4

7

8

13

14

17

18

2

5

6

9

12

15

16

19

12

CLK

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

1

11

O10

I10

3

4

7

8

13

14

17

18

74LS107

1

11

U38:A

74LS107

11

O9

I9

D0

D1

D2

D3

D4

D5

D6

D7

U37:B

74LS107

10

3

4

7

8

13

14

17

18

U37:A

74LS107

1

11

U36:B

74LS107

O8

I8

4

OE

LE

U36:A

3

4

7

8

13

14

17

18

U31:B

1

11

CLK

O7

I7

4

5

3

4

7

8

13

14

17

18

Ring Counter

U31:A

2

1

11

2

5

6

9

12

15

16

19

O6

I6

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

3

4

7

8

13

14

17

18

D0

D1

D2

D3

D4

D5

D6

D7

1

11

74LS173

Output Register

OE

LE

1

2

O5

I5

2

5

6

9

12

15

16

19

3

4

7

8

13

14

17

18

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

1

11

D0

D1

D2

D3

D4

D5

D6

D7

O4

I4

U22

3

4

5

6

Q0

Q1

Q2

Q3

74LS173

Output Register

OE

LE

13

3

4

7

8

13

14

17

18

CLK

OE1

OE2

E1

E2

MR

D0

D1

D2

D3

Q0

Q1

Q2

Q3

3

4

5

6

14

13

12

11

7

1

2

9

10

15

U23

CLK

OE1

OE2

E1

E2

MR

74LS173

Instruction

Register

(Address)

11

1

11

7

1

2

9

10

15

14

13

12

11

7

1

2

9

10

15

CLK

OE1

OE2

E1

E2

MR

D0

D1

D2

D3

Q0

Q1

Q2

Q3

3

4

5

6

11

12

13

14

U9

14

13

12

11

2

5

6

9

12

15

16

19

74LS173

Instruction

Register

(OPCode)

CLK

Lo

CLR

3

4

5

6

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

U8

CLK

Lo

CLR

10

O3

I3

74LS173

B Register

(MSB)

CLK

Ei

Li

D0

D1

D2

D3

OE

LE

D0

D1

D2

D3

D4

D5

D6

D7

CLK

Li

CLR

D3

D2

D1

D0

2

5

6

9

12

15

16

19

15

10

9

2

1

7

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

Q3

Q2

Q1

Q0

3

4

7

8

13

14

17

18

D0

D1

D2

D3

D4

D5

D6

D7

6

5

4

3

1

11

U20

OE

LE

MR

E2

E1

OE2

OE1

CLK

O2

I2

74LS173

B Register

(LSB)

2

5

6

9

12

15

16

19

11

12

13

14

3

4

7

8

13

14

17

18

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

D3

D2

D1

D0

1

11

D0

D1

D2

D3

D4

D5

D6

D7

Q3

Q2

Q1

Q0

O1

I1

U21

OE

LE

6

5

4

3

3

4

7

8

13

14

17

18

2

5

6

9

12

15

16

19

15

10

9

2

1

7

1

11

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

MR

E2

E1

OE2

OE1

CLK

O0

I0

D0

D1

D2

D3

D4

D5

D6

D7

14

13

12

11

U53

3

4

7

8

13

14

17

18

D0

D1

D2

D3

D4

D5

D6

D7

Eu

Lb

Lo

S-ar putea să vă placă și

- SAP-1 Simple As Possible Computer Schematic Diagram - Updated DesignDocument1 paginăSAP-1 Simple As Possible Computer Schematic Diagram - Updated Designpong74lsÎncă nu există evaluări

- ASAP-2 Almost Simple As Possible Computer SchematicDocument1 paginăASAP-2 Almost Simple As Possible Computer Schematicpong74lsÎncă nu există evaluări

- Design and Implementation of Simple As Possible Computer (SAP-1)Document51 paginiDesign and Implementation of Simple As Possible Computer (SAP-1)Miguel San AntonioÎncă nu există evaluări

- Datapaths: Understanding CPU ComponentsDocument30 paginiDatapaths: Understanding CPU ComponentsIqxca AzmYani100% (1)

- Digital Logic Design Lab Manual: Department of Electrical Engineering, Fast-Nu, LahoreDocument115 paginiDigital Logic Design Lab Manual: Department of Electrical Engineering, Fast-Nu, LahoreQasim LodhiÎncă nu există evaluări

- SAP 1 Simple As Possible ComputerDocument51 paginiSAP 1 Simple As Possible ComputerShawon Nazrul Islam80% (5)

- Binary MultiplierDocument14 paginiBinary MultiplierTaruna AggarwalÎncă nu există evaluări

- Sap 1 2Document21 paginiSap 1 2Brandon Maciel50% (2)

- The Single Cycle CPU ProjectDocument16 paginiThe Single Cycle CPU ProjectErik MachorroÎncă nu există evaluări

- Sap 2Document35 paginiSap 2Michael Vincent B. Nierva88% (8)

- Types of Micro OperationsDocument17 paginiTypes of Micro OperationsP Suresh Babu91% (11)

- MicrosequencerDocument38 paginiMicrosequencerJonathan MejiaÎncă nu există evaluări

- Computer OrganizationDocument396 paginiComputer Organizationkanaka raghu sreeramaÎncă nu există evaluări

- Floating Point ALU Using VHDL BlueDocument25 paginiFloating Point ALU Using VHDL BluepaulcbijuÎncă nu există evaluări

- Lab 5 Binary ArithmeticDocument5 paginiLab 5 Binary ArithmeticRifah Shanjida Momo100% (1)

- MicroprocessorDocument2 paginiMicroprocessorKiran TimsinaÎncă nu există evaluări

- VHDL ProgramsDocument10 paginiVHDL ProgramsgyanranjandashÎncă nu există evaluări

- Instructional Tools For Designing and Analysing A Very Simple CPUDocument10 paginiInstructional Tools For Designing and Analysing A Very Simple CPUFrancisco Javier Cesni MaldonadoÎncă nu există evaluări

- Control Unit:: Hardwired vs. Microprogrammed ApproachDocument49 paginiControl Unit:: Hardwired vs. Microprogrammed ApproachskskaundilyaÎncă nu există evaluări

- 4 Bit BCD AdderDocument5 pagini4 Bit BCD Adderjitendra jhaÎncă nu există evaluări

- Unit 5a - CPU DesignDocument64 paginiUnit 5a - CPU DesignMʌŋı ßʌķŞhı100% (1)

- Solution Manual For Assembly Language Programming and Organization of IBM PC PDFDocument129 paginiSolution Manual For Assembly Language Programming and Organization of IBM PC PDFabdul haseebÎncă nu există evaluări

- 16 Micro-Programmed ControlDocument36 pagini16 Micro-Programmed ControlJohn Paul Cordova100% (1)

- IC Lab Manual by Suresh BabuDocument83 paginiIC Lab Manual by Suresh Babunandakishore.nalla92% (13)

- LD ManualDocument89 paginiLD ManualchaitanyaÎncă nu există evaluări

- Programmable Logic Devices 2, TutorialDocument10 paginiProgrammable Logic Devices 2, Tutorialindresh.verma100% (1)

- Cisco Storage Design Fundamentals: Lab GuideDocument96 paginiCisco Storage Design Fundamentals: Lab Guidecdrbc100% (1)

- PLMU Computer Studies Dept SAP-1 modificationDocument17 paginiPLMU Computer Studies Dept SAP-1 modificationJaysen GeronimoÎncă nu există evaluări

- Sap-1 Computer Part1Document56 paginiSap-1 Computer Part1Tawki BakiÎncă nu există evaluări

- 6802 User ManualDocument76 pagini6802 User Manualmaldelrey100% (1)

- Sap 1 Manual NewDocument41 paginiSap 1 Manual NewAlexis John Rubio0% (1)

- SAP (Simple-As-Possible) Computers: 10-1 ArchitectureDocument24 paginiSAP (Simple-As-Possible) Computers: 10-1 ArchitectureAfrahly Afable100% (1)

- CISE 204 Digital System Design Lab Manual PDFDocument44 paginiCISE 204 Digital System Design Lab Manual PDFEng-Mohammed KayedÎncă nu există evaluări

- Lab ManualDocument19 paginiLab ManualSanthi SriÎncă nu există evaluări

- Digital Electronics Lab EE-224-FDocument48 paginiDigital Electronics Lab EE-224-FIshwar Singh ChandraÎncă nu există evaluări

- EXP 6 Serial AdderDocument2 paginiEXP 6 Serial Adderubuntu 13.0450% (2)

- Sap 1Document54 paginiSap 1ICANSAP0% (3)

- Computer ArithmeticDocument26 paginiComputer Arithmeticspweda100% (1)

- Junior Training SheetDocument70 paginiJunior Training SheetJuan Sebastian Hoyos100% (1)

- Mirror AdderDocument51 paginiMirror AdderjeevanprsdÎncă nu există evaluări

- The D Flip FlopDocument7 paginiThe D Flip FlopAlinChanÎncă nu există evaluări

- Pedroni MITPress 2ndedition Solution Samples v3Document25 paginiPedroni MITPress 2ndedition Solution Samples v3Squall_DA0% (1)

- 8051 ProgramsDocument2 pagini8051 ProgramsvipulkondekarÎncă nu există evaluări

- Serial AdderDocument6 paginiSerial AdderPrathap Vuyyuru100% (1)

- Introduction To Cmos Vlsi Design: MIPS Processor ExampleDocument43 paginiIntroduction To Cmos Vlsi Design: MIPS Processor ExampleSurbhi PrasadÎncă nu există evaluări

- Digital Lab Manual V2.1Document120 paginiDigital Lab Manual V2.1Marwan AffandiÎncă nu există evaluări

- A Unified Algorithm For Elementary FunctionsDocument8 paginiA Unified Algorithm For Elementary FunctionsCristo_Alanis_8381Încă nu există evaluări

- Chapter 11 Laboratory ExperimentDocument102 paginiChapter 11 Laboratory ExperimentMrinal TakÎncă nu există evaluări

- Curso Pic24j60Document173 paginiCurso Pic24j60Diojan Torres100% (1)

- Miroprogram Control UnitDocument21 paginiMiroprogram Control UnitSameer SalamÎncă nu există evaluări

- Study Gates, Flip-Flops LabDocument51 paginiStudy Gates, Flip-Flops Labsudipta2580Încă nu există evaluări

- Micro ControllersDocument141 paginiMicro ControllersBiswajit SarkarÎncă nu există evaluări

- Vedic MultiplierDocument14 paginiVedic MultiplierSunay RajÎncă nu există evaluări

- Ti I2cDocument13 paginiTi I2crajkumar_jain4855100% (1)

- SAP-1 Simple As Possible Computer With Microcoded ROMDocument1 paginăSAP-1 Simple As Possible Computer With Microcoded ROMpong74lsÎncă nu există evaluări

- SAP-1 Simple As Possible Computer Schematic DiagramDocument1 paginăSAP-1 Simple As Possible Computer Schematic Diagrampong74ls100% (5)

- Camera module with OV7670 and AL422B FIFODocument1 paginăCamera module with OV7670 and AL422B FIFOMuhammad Alfiansyah100% (3)

- Interrupt Control: Serial I/O ControlDocument15 paginiInterrupt Control: Serial I/O ControlnagpalanishÎncă nu există evaluări

- SAP-1 Simple As Possible Microprocessor - Original DesignDocument1 paginăSAP-1 Simple As Possible Microprocessor - Original DesignFarhan S. Adul100% (1)

- AZ 305T00A ENU Powerpoint 04Document32 paginiAZ 305T00A ENU Powerpoint 04ROTIAR0% (1)

- VPN VimalDocument95 paginiVPN VimalShivraj CyberÎncă nu există evaluări

- Computer Hardware FundamentalsDocument16 paginiComputer Hardware Fundamentalsapi-262742878Încă nu există evaluări

- MS1500L LPR Data Logger: Metal Samples CompanyDocument68 paginiMS1500L LPR Data Logger: Metal Samples CompanyfornowisÎncă nu există evaluări

- Malik Chung ResumeDocument2 paginiMalik Chung Resumeapi-287865827Încă nu există evaluări

- OOPs Lab ManualDocument88 paginiOOPs Lab Manualkingraaja0% (1)

- MYM7 User Manual-SimpleDocument6 paginiMYM7 User Manual-SimpleANTONIO ROSARIO ESCUDEROÎncă nu există evaluări

- CQM1HDocument22 paginiCQM1HJosé Manuel GonzálezÎncă nu există evaluări

- PT10SGDocument68 paginiPT10SGaka.virtuozÎncă nu există evaluări

- What Is OOPDocument11 paginiWhat Is OOPSwarnava SharmaÎncă nu există evaluări

- Video Conferencing Equipment Guide - Compare Solutions & FeaturesDocument20 paginiVideo Conferencing Equipment Guide - Compare Solutions & FeaturesbirukÎncă nu există evaluări

- RealPlayer Log File Installation DetailsDocument33 paginiRealPlayer Log File Installation Detailsjoejoejohn1234567Încă nu există evaluări

- 0700 193 MC ULTIMA X5000 S5000 Accessories Data SheetDocument2 pagini0700 193 MC ULTIMA X5000 S5000 Accessories Data SheetTomislav BrezicÎncă nu există evaluări

- Libro Dspic CompletoDocument250 paginiLibro Dspic CompletoRemigio Clemente Guevara Baculima100% (4)

- 10987C - Performance Tuning and Optimising SQL DatabasesDocument4 pagini10987C - Performance Tuning and Optimising SQL Databasesbhatroopa73Încă nu există evaluări

- Cambridge IGCSE: Computer Science 0478/12Document16 paginiCambridge IGCSE: Computer Science 0478/12Rodolph Smith100% (2)

- INSPECT STATEMENT VERBSDocument23 paginiINSPECT STATEMENT VERBSJayanthudu SaiÎncă nu există evaluări

- Hotel Booking Synopsis Under 40 CharactersDocument9 paginiHotel Booking Synopsis Under 40 CharactersMd Asif AlamÎncă nu există evaluări

- Java Magazine Mar Apr 2019Document104 paginiJava Magazine Mar Apr 2019Kiran KumarÎncă nu există evaluări

- ICT Empowerment Technology Quarter 1 LessonsDocument29 paginiICT Empowerment Technology Quarter 1 LessonsGeminiÎncă nu există evaluări

- Bill Book SystermDocument10 paginiBill Book SystermNiraj MishraÎncă nu există evaluări

- Booth'S Algorithm: MultiplicationDocument6 paginiBooth'S Algorithm: MultiplicationNipun JainÎncă nu există evaluări

- SentrySuite-Installation-Instructions EN PDFDocument22 paginiSentrySuite-Installation-Instructions EN PDFLajoskaÎncă nu există evaluări

- The Hercules S/370, ESA/390, and Z/architecture Systems EmulatorDocument36 paginiThe Hercules S/370, ESA/390, and Z/architecture Systems EmulatorRivo LettoÎncă nu există evaluări

- Data Acquisition Systems: Assignment EC375-Measurements and InstrumentationDocument10 paginiData Acquisition Systems: Assignment EC375-Measurements and InstrumentationAfrasinei Sergiu VladÎncă nu există evaluări

- Intel SSD Toolbox 3 1 Installation Guide 326039-002 Multi-LanguagesDocument96 paginiIntel SSD Toolbox 3 1 Installation Guide 326039-002 Multi-LanguagesLampZOSÎncă nu există evaluări

- Mellanox OFED Linux User Manual v2.3-1.0.1Document207 paginiMellanox OFED Linux User Manual v2.3-1.0.1Jason HlavacekÎncă nu există evaluări

- Router eSIM v1 FaqDocument13 paginiRouter eSIM v1 FaqIlias AhmedÎncă nu există evaluări

- Automatic Plant Watering System Using Ar PDFDocument9 paginiAutomatic Plant Watering System Using Ar PDFsiddhesh keniÎncă nu există evaluări

- 11.4.3.6 Packet Tracer - Troubleshooting Connectivity IssuesDocument3 pagini11.4.3.6 Packet Tracer - Troubleshooting Connectivity IssuesyhonelÎncă nu există evaluări