Documente Academic

Documente Profesional

Documente Cultură

EE 483/EE 580 Course Syllabus Spring 2001: Computer System Architecture: Third Edition

Încărcat de

anilshaw27Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

EE 483/EE 580 Course Syllabus Spring 2001: Computer System Architecture: Third Edition

Încărcat de

anilshaw27Drepturi de autor:

Formate disponibile

EE 483/EE 580 Course Syllabus Spring 2001

Instructor: Office: Phone: E-mail: WWW:

Dr. George Engel EB3043 (618) 650-2806 gengel@ee.siue.edu http://www.ee.siue.edu/~mentor http://www.ee.siue.edu/~mentor

Lectures:

T R

6:00 pm - 7:15 pm

Course Description: Principles of computer design and performance evaluation. Implementation of data and control units. Memory, I/O, bus, and operating system issues. Introduction to hardware description languages (VHDL). Review of current processor architectures. Prerequisites: EE382 or consent of instructor.

Grading: Semester grades will be computed as follows: Exam #1 Exam #2 Exam #3 Lab Exercises and Homework Final Project ............ ............ ............ ............ .............. 20% 20% 20% 20% 20%

Text: Computer System Architecture: Third Edition Morris Mano Prentice Hall, 1993 Optional (Many VHDL Made Easy David Pellerin Prentice Hall, VHDL tutorials exist on the WEB so the book is not mandatory) (I personally like the book!) and Douglas Taylor 1997

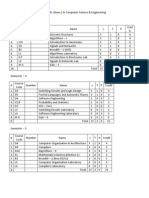

EE483/EE580 Lecture Schedule For Spring 2001

Jan 09 (T)

Ch 1: Review: Combinational and Sequential Logic Design -- Schematic Driven Design --- Introduction to VHDL -Ch 2: Review: Digital Components -- A First Look at VHDL -Ch 3: Review: Number Representations and Systems -- VHDL: Exploring Objects and Data Types -- VHDL: Using Standard Logic Ch 4: Register Transfer and Micro-operations -- VHDL: Understanding Concurrent Statements -- VHDL: Understanding Sequential Statements -- VHDL: Creating Modular Designs -- VHDL: Partitioning Your Design -- VHDL: Writing Test Benches Ch 5: Basic Computer Organization and Design 5.1 Instruction Codes 5.2 Computer Registers Ch 5 5.3 Computer Instructions 5.6 Memory Reference Instructions

Jan 11 (R) Jan 16 (T)

Jan 18 (R)

Jan 23 (T)

Jan 25 (R)

Jan 30 (T) Feb 01 (R)

Ch 5: Basic Computer Organization and Design 5.4 Timing and Control 5.5 Instruction Cycle Ch 5: Basic Computer Organization and Design 5.9 Hardwired Control 5.10 Design of Accumulator Logic Ch 6: Programming the Basic Computer -- EXAM # 1 -Behavioral Level VHDL Model of SEP Ch 7: Microprogrammed Control 7.1 Control Memory 7.2 Address Sequencing Design of Control Unit Ch 7: Microprogrammed Control Nanoprogramming Minimizing the width of control memory Ch 8: CPU 8.2 Register Organization 8.3 Stack Organization Ch 8: CPU 8.4 Instruction Formats 8.5 Addressing Modes Ch 8: CPU 8.6 Data Transfer and Manipulation

Feb 06 (T)

Feb 08 (R) Feb 13 (T) Feb 15 (R) Feb 20 (T)

Feb 22 (R)

Feb 27 (T)

Mar 01 (R)

Mar 06 (T)

Mar 08 (R)

Ch 8:

CPU 8.7 Program Control 8.8 CISC versus RISC

Mar 13 (T) Mar 15 (R) Mar 20 (T)

*** SPRING BREAK *** *** SPRING BREAK *** Ch 9: Pipelining 9.1 Parallel Processing 9.2 Pipeline Concept Ch 9: Pipelining 9.3 Arithmetic Pipeline 9.4 Instruction Pipeline Ch 10: Computer Arithmetic 10.2 Addition and Subtraction 10.3 Multiplication

Mar 22 (R)

Mar 27 (T)

Mar 29 (R) Apr 03 (T) Apr 05 (R)

--

EXAM # 2 -Computer Arithmetic 10.3 Multiplication Computer Arithmetic 10.4 Division 10.5 Floating-point Organization Peripheral Devices I/O Interface Asynchronous Data Transfer

Ch 10: Ch 10:

Apr 10 (T)

Ch 11: I/O 11.1 11.2 11.3

Apr 12 (R)

Ch 11: I/O Organization 11.4 Modes of Transfer 11.5 Priority Interrupt Ch 11: I/O 11.6 11.7 11.8 Organization DMA I/O Processor Serial Communications

Apr 17 (T)

Apr 19 (R)

Ch 12: Memory Organization 12.2 Main Memory 12.3 Auxiliary Memory 12.4 Associative Memory Ch 12: Memory Organization 12.5 Cache Memory 12.6 Virtual Memory Ch 12: Memory Organization 12.6 Virtual Memory 12.7 Memory Management Hardware

Apr 24 (T)

Apr 26 (R)

EE483/EE580 Lab Schedule For Spring 2001

Jan 08 Jan 15 Jan 22

--- NO LABS --Lab #1: Schematic Driven Design: Design Architect and QuickSIM Tutorial Example Lab #2: More Schematic Driven Design: Design Architect and QuickSIM Design ALU described in Mano textbook. Lab #1 should be submitted for grading. Lab #2: More Schematic Driven Design: Design Architect and QuickSIM Continue design of ALU described in Mano textbook. Lab #3: VHDL Design: Qvcom and Qvsim Tutorial Example: 4-bit counter Lab #2 should be submitted for grading. Lab #4: More VHDL Design: Design ALU using VHDL Submit lab #3 for grading. Qvcom and Qvsim

Jan 29 Feb 05

Feb 12

Feb 19 Feb 26 Mar 05

Lab #4: More VHDL Design: Qvcom and Qvsim Finish design of ALU using VHDL Lab # 5: Synthesis using Leonardo circuit synthesizer Submit lab #4 for grading. Lab #6 Exploring SEP operation Modifying the SEP Submit lab #5 for grading. *** SPRING BREAK *** Continue Lab #6 Exploring SEP operation Work on Final Project. Submit lab #6 for grading. Work on Final Project Work on Final Project Work on Final Project Work on Final Project

Mar 12 Mar 19 Mar 26 Apr 02 Apr 09 Apr 16 Apr 23

S-ar putea să vă placă și

- EE2354Document7 paginiEE2354swathi_grenÎncă nu există evaluări

- COA Lab ManualDocument52 paginiCOA Lab Manualprince kumar50% (4)

- CmosDocument23 paginiCmoselumalaianithaÎncă nu există evaluări

- Sem5 EJ5EDocument38 paginiSem5 EJ5EAjit SinghÎncă nu există evaluări

- 2152006Document3 pagini2152006Mohamed Ismail FiazÎncă nu există evaluări

- VHDL SyllabusDocument3 paginiVHDL SyllabusNeerajBooraÎncă nu există evaluări

- EE 421-Digital System Design-Dr. Shahid MasoodDocument4 paginiEE 421-Digital System Design-Dr. Shahid MasoodSher Hassan RazaÎncă nu există evaluări

- Cs 341 Lecture1Document11 paginiCs 341 Lecture1luckyÎncă nu există evaluări

- Ecen 5613 Embedded System DesignDocument11 paginiEcen 5613 Embedded System DesignMehul PatelÎncă nu există evaluări

- Cse Viii Advanced Computer Architectures (06cs81) NotesDocument156 paginiCse Viii Advanced Computer Architectures (06cs81) NotesJupe JonesÎncă nu există evaluări

- Advanced Computer Architecture: 563 L02.1 Fall 2011Document57 paginiAdvanced Computer Architecture: 563 L02.1 Fall 2011bashar_engÎncă nu există evaluări

- Computer Engineering Sem-1Document8 paginiComputer Engineering Sem-1waniasimÎncă nu există evaluări

- Digital Design: Cs/Eee/Ece /instr F215Document34 paginiDigital Design: Cs/Eee/Ece /instr F215SIDDHANT RAVINDRA KULKARNIÎncă nu există evaluări

- Microprocessor TechnologiesDocument3 paginiMicroprocessor Technologiesayushsutariya30Încă nu există evaluări

- MaTLab ProgramingDocument7 paginiMaTLab ProgramingKristen VasquezÎncă nu există evaluări

- The 8051 MicrocontollerDocument212 paginiThe 8051 Microcontollermahmudou100% (1)

- Btech PortionDocument11 paginiBtech PortionNitesh ChhabriaÎncă nu există evaluări

- Lesson PlanDocument6 paginiLesson PlanMeenakshi HnÎncă nu există evaluări

- RP Tip Print NewDocument5 paginiRP Tip Print NewNishant RajÎncă nu există evaluări

- Microprocessor 4th SemDocument316 paginiMicroprocessor 4th SemDaggupatiHarishÎncă nu există evaluări

- 16 Marks Question Bank NewDocument16 pagini16 Marks Question Bank Newsakthivijayan80Încă nu există evaluări

- CAD For VLSIDocument2 paginiCAD For VLSIKapasi TejasÎncă nu există evaluări

- VIT CSE BTech Course PlanDocument76 paginiVIT CSE BTech Course PlanApoorv Krishak50% (2)

- Course OutlineDocument2 paginiCourse OutlineAli Ahmad100% (1)

- CS2252Document6 paginiCS2252Venkat RamananÎncă nu există evaluări

- System On Chip Design and ModellingDocument131 paginiSystem On Chip Design and ModellingGurram KishoreÎncă nu există evaluări

- Department of Computer Science & Engineering: National Institute of Technology, SrinagarDocument71 paginiDepartment of Computer Science & Engineering: National Institute of Technology, SrinagarShaaahidÎncă nu există evaluări

- SoC Design - A ReviewDocument131 paginiSoC Design - A ReviewSambhav VermanÎncă nu există evaluări

- ADvance MIcroprocessor Scheme GTUDocument4 paginiADvance MIcroprocessor Scheme GTUamitcrathodÎncă nu există evaluări

- C Programming for the Pc the Mac and the Arduino Microcontroller SystemDe la EverandC Programming for the Pc the Mac and the Arduino Microcontroller SystemÎncă nu există evaluări

- Software Development for Engineers: C/C++, Pascal, Assembly, Visual Basic, HTML, Java Script, Java DOS, Windows NT, UNIXDe la EverandSoftware Development for Engineers: C/C++, Pascal, Assembly, Visual Basic, HTML, Java Script, Java DOS, Windows NT, UNIXEvaluare: 5 din 5 stele5/5 (1)

- Iit KGP Cse SyllabusDocument47 paginiIit KGP Cse SyllabussayakjuÎncă nu există evaluări

- CSE2006 Syllabus PDFDocument9 paginiCSE2006 Syllabus PDFMohit SinghalÎncă nu există evaluări

- Sem 6Document11 paginiSem 6Brahat SinghÎncă nu există evaluări

- Logic Synthesis and Verification: Course InfoDocument7 paginiLogic Synthesis and Verification: Course InfoManisha JadavÎncă nu există evaluări

- Advanced Computer ArchitectureDocument74 paginiAdvanced Computer ArchitectureMonica ChandrasekarÎncă nu există evaluări

- V.S.B. Engineering College, Karur Department of Information Technology Academic Year: 2016-2017 (EVEN SEMESTER)Document12 paginiV.S.B. Engineering College, Karur Department of Information Technology Academic Year: 2016-2017 (EVEN SEMESTER)mdiÎncă nu există evaluări

- Handbook of CSEDocument24 paginiHandbook of CSEBala KumarÎncă nu există evaluări

- ACA NotesDocument156 paginiACA NotesSharath MonappaÎncă nu există evaluări

- C BookDocument203 paginiC BookChandra ClarkÎncă nu există evaluări

- University of Mumbai University of Mumbai University of MumbaiDocument19 paginiUniversity of Mumbai University of Mumbai University of MumbaiJaya PillaiÎncă nu există evaluări

- Gantt ChartDocument16 paginiGantt Chartsunday_ogunremiÎncă nu există evaluări

- Embeddedsystem Lecture1Document25 paginiEmbeddedsystem Lecture1Ankita SinghÎncă nu există evaluări

- Computer Architecture: FundamentalsDocument36 paginiComputer Architecture: FundamentalsShankarananda SherÎncă nu există evaluări

- Basic Ideas and Definition Major Components of Software/Hardware Computer RevolutionDocument5 paginiBasic Ideas and Definition Major Components of Software/Hardware Computer Revolutionrafi867Încă nu există evaluări

- UT Dallas Syllabus For Ee6302.001 05f Taught by Mehrdad Nourani (Nourani)Document2 paginiUT Dallas Syllabus For Ee6302.001 05f Taught by Mehrdad Nourani (Nourani)UT Dallas Provost's Technology GroupÎncă nu există evaluări

- Q) What Are Algorithms? Q) What Is A Top Down Design?Document15 paginiQ) What Are Algorithms? Q) What Is A Top Down Design?ee1usmanÎncă nu există evaluări

- 492 Processor MemoryDocument11 pagini492 Processor MemorydharanistrikezÎncă nu există evaluări

- Performance of A ComputerDocument83 paginiPerformance of A ComputerPrakherGuptaÎncă nu există evaluări

- Ieee Cas Dallas 111104Document32 paginiIeee Cas Dallas 111104SamÎncă nu există evaluări

- ECE 4680 Computer Architecture and OrganizationDocument15 paginiECE 4680 Computer Architecture and OrganizationNarender KumarÎncă nu există evaluări

- Thesis VHDL PDFDocument6 paginiThesis VHDL PDFmarybrownarlington100% (2)

- Advanced Computer ArchitectureDocument8 paginiAdvanced Computer Architecturett_aljobory3911Încă nu există evaluări

- PG Diploma in Embedded Systems Design (PG-DESD) Course FocusDocument7 paginiPG Diploma in Embedded Systems Design (PG-DESD) Course Focusabhijeetv2Încă nu există evaluări

- Lecture01 s07Document41 paginiLecture01 s07Ali AhmadÎncă nu există evaluări

- Microcontroller Architecture and Organization: Unit IDocument6 paginiMicrocontroller Architecture and Organization: Unit IhemanthdreamzÎncă nu există evaluări

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxDe la EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxEvaluare: 4 din 5 stele4/5 (1)

- 1031 - Application FormDocument3 pagini1031 - Application Formanilshaw27Încă nu există evaluări

- Visitor's VisaDocument2 paginiVisitor's Visaanilshaw27Încă nu există evaluări

- Flower PotDocument4 paginiFlower Potanilshaw27Încă nu există evaluări

- Result WebDocument2 paginiResult Webanilshaw27Încă nu există evaluări

- Ready To Send Revised Sci Comm ProgDocument4 paginiReady To Send Revised Sci Comm Proganilshaw27Încă nu există evaluări

- 24 Sept 2012 ScheduleDocument5 pagini24 Sept 2012 Scheduleanilshaw27Încă nu există evaluări

- CH 17Document7 paginiCH 17anilshaw27Încă nu există evaluări

- 20 Posts Non Technical SpecificationDocument4 pagini20 Posts Non Technical Specificationanilshaw27Încă nu există evaluări

- Personal Computer (Pentium - IV) : Ntroduction Arket OtentialDocument8 paginiPersonal Computer (Pentium - IV) : Ntroduction Arket Otentialanilshaw27Încă nu există evaluări

- Cycle Rickshow Two Wheeler Rep ServicingDocument3 paginiCycle Rickshow Two Wheeler Rep Servicinganilshaw27Încă nu există evaluări

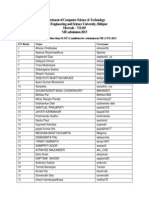

- Department of Computer Science and TechnologyDocument3 paginiDepartment of Computer Science and Technologyanilshaw27Încă nu există evaluări

- FlowerDocument1 paginăFloweranilshaw27Încă nu există evaluări

- PRODUCTS Final 1Document133 paginiPRODUCTS Final 1Soigne ConsultantsÎncă nu există evaluări

- Kmu Cat Rollnoslip 263112Document1 paginăKmu Cat Rollnoslip 263112Saeed AkhtarÎncă nu există evaluări

- Digital Hydraulic Valves Gaining Momentum: Newton, Ma-The Trend Toward De-Centralized Control On The Factory FloorDocument2 paginiDigital Hydraulic Valves Gaining Momentum: Newton, Ma-The Trend Toward De-Centralized Control On The Factory Floorback1949100% (1)

- IBM PowerVM Disk-Tape VirtualizationDocument23 paginiIBM PowerVM Disk-Tape VirtualizationliuylÎncă nu există evaluări

- Philips MMC275Document47 paginiPhilips MMC275videosonÎncă nu există evaluări

- Lab 3 Abowd and Beales Framework FormatDocument2 paginiLab 3 Abowd and Beales Framework FormatPhilipÎncă nu există evaluări

- Tutorial GTK+ 2Document98 paginiTutorial GTK+ 2PoliCamÎncă nu există evaluări

- Total Airport ManagementDocument23 paginiTotal Airport ManagementEM EZÎncă nu există evaluări

- Rig Specifications 750 HP Rompetrol S ADocument8 paginiRig Specifications 750 HP Rompetrol S Achoukri mekahliaÎncă nu există evaluări

- Hosting A Web Server On Raspberry PiDocument7 paginiHosting A Web Server On Raspberry PidgsghsÎncă nu există evaluări

- 5 Day Course Outline of Process Safety Related TopicsDocument3 pagini5 Day Course Outline of Process Safety Related Topicskanakarao1Încă nu există evaluări

- OnGuard 7.3 Data Sheet PDFDocument2 paginiOnGuard 7.3 Data Sheet PDFdune_misterÎncă nu există evaluări

- LH86 ModbusDocument2 paginiLH86 ModbusMarcos Luiz AlvesÎncă nu există evaluări

- Introduction To ProgrammingDocument20 paginiIntroduction To ProgrammingJohnBenedictRazÎncă nu există evaluări

- 2720 Slides5 PDFDocument24 pagini2720 Slides5 PDFFathony IlhamÎncă nu există evaluări

- TK371 Plano ElectricoDocument2 paginiTK371 Plano ElectricoCarlos IrabedraÎncă nu există evaluări

- Official Vizier Calculator PDFDocument3 paginiOfficial Vizier Calculator PDFNurfitri OktaviaÎncă nu există evaluări

- Datasheet External Antenna 2000 - Alpha-Con-V7Document4 paginiDatasheet External Antenna 2000 - Alpha-Con-V7Bravemon23Încă nu există evaluări

- Inclusive Growth With Disruptive Innovations: Gearing Up For Digital DisruptionDocument48 paginiInclusive Growth With Disruptive Innovations: Gearing Up For Digital DisruptionShashank YadavÎncă nu există evaluări

- Assignment On LifiDocument19 paginiAssignment On LifiMushir BakshÎncă nu există evaluări

- Manual SWGR BloksetDocument5 paginiManual SWGR BloksetibrahimÎncă nu există evaluări

- Web Programming Lab Manual 2009Document33 paginiWeb Programming Lab Manual 2009Kumar SaurabhÎncă nu există evaluări

- RMC-90 & RMC-37 Stock Till-18.10.2023Document3 paginiRMC-90 & RMC-37 Stock Till-18.10.2023Balram kumarÎncă nu există evaluări

- Rascal07setupusb KitDocument9 paginiRascal07setupusb KitIndra GunawanÎncă nu există evaluări

- Unit-4 Hadoop Distributed File System (HDFS) : SyllabusDocument17 paginiUnit-4 Hadoop Distributed File System (HDFS) : SyllabusFrost RebbecaÎncă nu există evaluări

- Split Charge InstructionsDocument4 paginiSplit Charge InstructionsAugusto ZanlungoÎncă nu există evaluări

- 4G15 EngineDocument32 pagini4G15 EngineLee Johnston75% (12)

- Bealls List of Predatory PublishersDocument38 paginiBealls List of Predatory PublishersRandy The FoxÎncă nu există evaluări

- Soal Sastra Inggris Mid GenapDocument4 paginiSoal Sastra Inggris Mid Genapsaiful faizinÎncă nu există evaluări

- Latest QA Jobs 01 Apr 2024Document24 paginiLatest QA Jobs 01 Apr 2024arifmohammad7567Încă nu există evaluări