Documente Academic

Documente Profesional

Documente Cultură

8 Mbit / 16 Mbit (x8) Multi-Purpose Flash: SST39LF080 / SST39LF016 / SST39VF080 / SST39VF016

Încărcat de

vetchboyTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

8 Mbit / 16 Mbit (x8) Multi-Purpose Flash: SST39LF080 / SST39LF016 / SST39VF080 / SST39VF016

Încărcat de

vetchboyDrepturi de autor:

Formate disponibile

8 Mbit / 16 Mbit (x8) Multi-Purpose Flash

SST39LF080 / SST39LF016 / SST39VF080 / SST39VF016

Data Sheet

FEATURES:

• Organized as 1M x8 / 2M x8 • Fast Erase and Byte-Program:

• Single Voltage Read and Write Operations - Sector-Erase Time: 18 ms (typical) 1

- Block-Erase Time: 18 ms (typical)

- 3.0-3.6V for SST39LF080/016

- 2.7-3.6V for SST39VF080/016 - Chip-Erase Time: 70 ms (typical)

• Superior Reliability

- Byte-Program Time: 14 µs (typical) 2

- Chip Rewrite Time:

- Endurance: 100,000 Cycles (typical) 15 seconds (typical) for SST39LF/VF080

- Greater than 100 years Data Retention 30 seconds (typical) for SST39LF/VF016

• Low Power Consumption: • Automatic Write Timing

3

- Active Current: 15 mA (typical) - Internal VPP Generation

- Standby Current: 4 µA (typical)

- Auto Low Power Mode: 4 µA (typical)

• End-of-Write Detection 4

- Toggle Bit

• Sector-Erase Capability - Data# Polling

- Uniform 4 KByte sectors • CMOS I/O Compatibility 5

• Block-Erase Capability

• JEDEC Standard

- Uniform 64 KByte blocks

- Flash EEPROM Pinouts and command sets

• Fast Read Access Time: 6

• Packages Available

- 55 ns for SST39LF080/016

- 40-Pin TSOP (10mm x 20mm)

- 70 and 90 ns for SST39VF080/016

- 48-Ball TFBGA (6mm x 8mm) 7

• Latched Address and Data

PRODUCT DESCRIPTION Erase and Program than alternative flash technologies.

The total energy consumed is a function of the applied 8

The SST39LF/VF080 and SST39LF/VF016 devices are voltage, current, and time of application. Since for any

1M x8 / 2M x8 CMOS Multi-Purpose Flash (MPF) given voltage range, the SuperFlash technology uses less

manufactured with SST’s proprietary, high performance current to program and has a shorter erase time, the total 9

CMOS SuperFlash technology. The split-gate cell de- energy consumed during any Erase or Program operation

sign and thick oxide tunneling injector attain better is less than alternative flash technologies. They also

reliability and manufacturability compared with alternate improve flexibility while lowering the cost for program, data, 10

approaches. The SST39LF080/016 write (Program or and configuration storage applications.

Erase) with a 3.0-3.6V power supply. The

The SuperFlash technology provides fixed Erase and

SST39VF080/016 write (Program or Erase) with a 2.7-

Program times, independent of the number of Erase/ 11

3.6V power supply. They conform to JEDEC standard

Program cycles that have occurred. Therefore the sys-

pinouts for x8 memories.

tem software or hardware does not have to be modified

Featuring high performance Byte-Program, the or de-rated as is necessary with alternative flash tech- 12

SST39LF/VF080 and SST39LF/VF016 devices provide nologies, whose Erase and Program times increase

a typical Byte-Program time of 14 µsec. The devices use with accumulated Erase/Program cycles.

Toggle Bit or Data# Polling to indicate the completion of 13

To meet high density, surface mount requirements, the

Program operation. To protect against inadvertent write,

SST39LF/VF080 and SST39LF/VF016 are offered in

they have on-chip hardware and Software Data Protec-

40-pin TSOP and 48-ball TFBGA packaging. See 14

tion schemes. Designed, manufactured, and tested for

Figures 1 and 2 for pinouts.

a wide spectrum of applications, these devices are

offered with a guaranteed endurance of 10,000 cycles.

Device Operation

Data retention is rated at greater than 100 years.

Commands are used to initiate the memory operation

15

The SST39LF/VF080 and SST39LF/VF016 devices are functions of the device. Commands are written to the

suited for applications that require convenient and eco- device using standard microprocessor write se-

nomical updating of program, configuration, or data quences. A command is written by asserting WE# low

16

memory. For all system applications, they significantly while keeping CE# low. The address bus is latched on

improve performance and reliability, while lowering power the falling edge of WE# or CE#, whichever occurs last.

consumption. They inherently use less energy during The data bus is latched on the rising edge of WE# or

CE#, whichever occurs first.

© 2000 Silicon Storage Technology, Inc.The SST logo and SuperFlash are registered trademarks of Silicon Storage Technology, Inc. MPF is a trademark of Silicon Storage Technology, Inc.

396-2 11/00 S71146 1 These specifications are subject to change without notice.

8 Mbit / 16 Mbit Multi-Purpose Flash

SST39LF080 / SST39LF016 / SST39VF080 / SST39VF016

Data Sheet

The SST39LF/VF080 and SST39LF/VF016 also have block size of 64 KByte. The Sector-Erase operation is

the Auto Low Power mode which puts the device in a initiated by executing a six-byte-command sequence

near standby mode after data has been accessed with a with Sector-Erase command (30H) and sector address

valid Read operation. This reduces the IDD active read (SA) in the last bus cycle. The Block-Erase operation is

current from typically 15 mA to typically 4 µA. The Auto initiated by executing a six-byte-command sequence

Low Power mode reduces the typical IDD active read with Block-Erase command (50H) and block address

current to the range of 1 mA/MHz of read cycle time. The (BA) in the last bus cycle. The sector or block address is

device exits the Auto Low Power mode with any address latched on the falling edge of the sixth WE# pulse, while

transition or control signal transition used to initiate the command (30H or 50H) is latched on the rising edge

another Read cycle, with no access time penalty. Note of the sixth WE# pulse. The internal Erase operation

that the device does not enter Auto Low Power mode begins after the sixth WE# pulse. The End-of-Erase

after power-up with CE# held steadily low until the first operation can be determined using either Data# Polling

address transition or CE# is driven high. or Toggle Bit methods. See Figures 9 and 10 for timing

waveforms. Any commands issued during the Sector- or

Read Block-Erase operation are ignored.

The Read operation of the SST39LF/VF080 and

SST39LF/VF016 is controlled by CE# and OE#, both have Chip-Erase Operation

to be low for the system to obtain data from the outputs. The SST39LF/VF080 and SST39LF/VF016 provide a

CE# is used for device selection. When CE# is high, the Chip-Erase operation, which allows the user to erase the

chip is deselected and only standby power is consumed. entire memory array to the “1” state. This is useful when

OE# is the output control and is used to gate data from the the entire device must be quickly erased.

output pins. The data bus is in high impedance state when The Chip-Erase operation is initiated by executing a six

either CE# or OE# is high. Refer to the Read cycle timing byte command sequence with Chip-Erase command

diagram for further details (Figure 3). (10H) at address 5555H in the last byte sequence. The

Erase operation begins with the rising edge of the sixth

Byte-Program Operation WE# or CE#, whichever occurs first. During the Erase

The SST39LF/VF080 and SST39LF/VF016 are pro- operation, the only valid read is Toggle Bit or Data#

grammed on a byte-by-byte basis. The Program operation Polling. See Table 4 for the command sequence, Figure

consists of three steps. The first step is the three-byte load 8 for timing diagram, and Figure 19 for the flowchart. Any

sequence for Software Data Protection. The second step commands issued during the Chip-Erase operation are

is to load byte address and byte data. During the Byte- ignored.

Program operation, the addresses are latched on the

falling edge of either CE# or WE#, whichever occurs last. Write Operation Status Detection

The data is latched on the rising edge of either CE# or The SST39LF/VF080 and SST39LF/VF016 provide two

WE#, whichever occurs first. The third step is the internal software means to detect the completion of a write (Pro-

Program operation which is initiated after the rising edge gram or Erase) cycle, in order to optimize the system Write

of the fourth WE# or CE#, whichever occurs first. The cycle time. The software detection includes two status

Program operation, once initiated, will be completed within bits: Data# Polling (DQ7) and Toggle Bit (DQ6). The End-

20 µs. See Figures 4 and 5 for WE# and CE# controlled of-Write detection mode is enabled after the rising edge of

Program operation timing diagrams and Figure 16 for WE#, which initiates the internal Program or Erase opera-

flowcharts. During the Program operation, the only valid tion.

reads are Data# Polling and Toggle Bit. During the internal

Program operation, the host is free to perform additional The actual completion of the nonvolatile write is asyn-

tasks. Any commands issued during the internal Program chronous with the system; therefore, either a Data#

operation are ignored. Polling or Toggle Bit read may be simultaneous with the

completion of the Write cycle. If this occurs, the system

Sector/Block-Erase Operation may possibly get an erroneous result, i.e., valid data may

The Sector- (or Block-) Erase operation allows the sys- appear to conflict with either DQ7 or DQ6. In order to

tem to erase the device on a sector-by-sector (or block- prevent spurious rejection, if an erroneous result occurs,

by-block) basis. The SST39LF/VF080 and SST39LF/ the software routine should include a loop to read the

VF016 offer both Sector-Erase and Block-Erase mode. accessed location an additional two (2) times. If both

The sector architecture is based on uniform sector size reads are valid, then the device has completed the Write

of 4 KByte. The Block-Erase mode is based on uniform cycle, otherwise the rejection is valid.

© 2000 Silicon Storage Technology, Inc. S71146 396-2 11/00

2

8 Mbit / 16 Mbit Multi-Purpose Flash

SST39LF080 / SST39LF016 / SST39VF080 / SST39VF016

Data Sheet

Data# Polling (DQ7) enabled. See Table 4 for the specific software command

When the SST39LF/VF080 and SST39LF/VF016 are in codes. During SDP command sequence, invalid com-

the internal Program operation, any attempt to read DQ7 mands will abort the device to read mode within TRC.

will produce the complement of the true data. Once the 1

Program operation is completed, DQ7 will produce true Common Flash Memory Interface (CFI)

data. The device is then ready for the next operation. The SST39LF/VF080 and SST39LF/VF016 also contain

During internal Erase operation, any attempt to read DQ7 the CFI information to describe the characteristics of the 2

will produce a ‘0’. Once the internal Erase operation is device. In order to enter the CFI Query mode, the system

completed, DQ7 will produce a ‘1’. The Data# Polling is must write three-byte sequence, same as product ID

valid after the rising edge of fourth WE# (or CE#) pulse for entry command with 98H (CFI Query command) to 3

Program operation. For Sector-, Block- or Chip-Erase, the address 5555H in the last byte sequence. Once the

Data# Polling is valid after the rising edge of sixth WE# (or device enters the CFI Query mode, the system can read

CE#) pulse. See Figure 6 for Data# Polling timing diagram CFI data at the addresses given in tables 5 through 7. 4

and Figure 17 for a flowchart. The system must write the CFI Exit command to return

to Read mode from the CFI Query mode.

Toggle Bit (DQ6) 5

During the internal Program or Erase operation, any con- Product Identification

secutive attempts to read DQ6 will produce alternating 1’s The Product Identification mode identifies the device as

and 0’s, i.e., toggling between 1 and 0. When the internal the SST39LF080, SST39VF080, SST39LF016 and 6

Program or Erase operation is completed, the DQ6 bit will SST39VF016 and manufacturer as SST. This mode may be

stop toggling. The device is then ready for the next opera- accessed by hardware or software operations. The hardware

tion. The Toggle Bit is valid after the rising edge of fourth operation is typically used by a programmer to identify the 7

WE# (or CE#) pulse for Program operation. For Sector-, correct algorithm for the SST39LF/VF080 and SST39LF/

Block- or Chip-Erase, the Toggle Bit is valid after the rising VF016. Users may wish to use the Software Product Identifi-

edge of sixth WE# (or CE#) pulse. See Figure 7 for Toggle cation operation to identify the part (i.e., using the device ID) 8

Bit timing diagram and Figure 17 for a flowchart. when using multiple manufacturers in the same socket. For

details, see Table 3 for hardware operation or Table 4 for

Data Protection software operation, Figure 11 for the Software ID Entry and

The SST39LF/VF080 and SST39LF/VF016 provide both Read timing diagram and Figure 18 for the Software ID Entry

9

hardware and software features to protect nonvolatile data command sequence flowchart.

from inadvertent writes.

TABLE 1: PRODUCT IDENTIFICATION

10

Hardware Data Protection Address Data

Noise/Glitch Protection: A WE# or CE# pulse of less than

5 ns will not initiate a Write cycle. Manufacturer’s ID 0000H BFH 11

Device ID

VDD Power Up/Down Detection: The Write operation is

SST39LF/VF080 0001H D8H

inhibited when VDD is less than 1.5V. 12

SST39LF/VF016 0001H D9H

Write Inhibit Mode: Forcing OE# low, CE# high, or WE#

396 PGM T1.2

high will inhibit the Write operation. This prevents inadvert-

ent writes during power-up or power-down. 13

Product Identification Mode Exit/CFI Mode Exit

In order to return to the standard Read mode, the

Software Data Protection (SDP)

Software Product Identification mode must be exited.

The SST39LF/VF080 and SST39LF/VF016 provide the

Exit is accomplished by issuing the Software ID Exit

14

JEDEC approved Software Data Protection scheme for

command sequence, which returns the device to the

all data alteration operations, i.e., Program and Erase.

Read operation. This command may also be used to

Any Program operation requires the inclusion of the

reset the device to the Read mode after any inadvertent

15

three-byte sequence. The three-byte load sequence is

transient condition that apparently causes the device to

used to initiate the Program operation, providing optimal

behave abnormally, e.g., not read correctly. Please note

protection from inadvertent Write operations, e.g., dur-

that the Software ID Exit/CFI Exit command is ignored 16

ing the system power-up or power-down. Any Erase

during an internal Program or Erase operation. See

operation requires the inclusion of six-byte sequence.

Table 4 for software command codes, Figure 13 for

The SST39LF/VF080 and SST39LF/VF016 devices are

timing waveform and Figure 18 for a flowchart.

shipped with the Software Data Protection permanently

© 2000 Silicon Storage Technology, Inc. S71146 396-2 11/00

3

8 Mbit / 16 Mbit Multi-Purpose Flash

SST39LF080 / SST39LF016 / SST39VF080 / SST39VF016

Data Sheet

FUNCTIONAL BLOCK DIAGRAM

SuperFlash

X-Decoder Memory

Memory

Address Buffer & Latches

Address

Y-Decoder

CE#

OE# Control Logic I/O Buffers and Data Latches

WE#

DQ7 - DQ0

396 ILL B1.2

SST39LF/VF160 SST39LF/VF080 SST39LF/VF080 SST39LF/VF016

A16 A16 1 40 A17 A17

A15 A15 2 39 VSS VSS

A14 A14 3 38 NC A20

A13 A13 4 37 A19 A19

A12 A12 5 36 A10 A10

A11 A11 6 35 DQ7 DQ7

A9 A9 7 34 DQ6 DQ6

A8 A8 8 33 DQ5 DQ5

WE# WE# 9 Standard Pinout 32 DQ4 DQ4

NC NC 10 31 VDD VDD

NC NC 11 Top View 30 VDD VDD

NC NC 12 29 NC NC

A18 A18 13 Die Up 28 DQ3 DQ3

A7 A7 14 27 DQ2 DQ2

A6 A6 15 26 DQ1 DQ1

A5 A5 16 25 DQ0 DQ0

A4 A4 17 24 OE# OE#

A3 A3 18 23 VSS VSS

A2 A2 19 22 CE# CE#

A1 A1 20 21 A0 A0

396 ILL F01.2

FIGURE 1: PIN ASSIGNMENTS FOR 40-PIN TSOP

TOP VIEW (balls facing down) TOP VIEW (balls facing down)

SST39LF/VF080 SST39LF/VF016

6 6

A14 A13 A15 A16 A17 NC A20 VSS A14 A13 A15 A16 A17 NC A20 VSS

5 5

A9 A8 A11 A12 A19 A10 DQ6 DQ7 A9 A8 A11 A12 A19 A10 DQ6 DQ7

4 4

WE# NC NC NC DQ5 NC VDD DQ4 WE# NC NC NC DQ5 NC VDD DQ4

3 3

NC NC NC NC DQ2 DQ3 VDD NC NC NC NC NC DQ2 DQ3 VDD A21

2 2

396 ILL F20.0

396 ILL F21.0

A7 A18 A6 A5 DQ0 NC NC DQ1 A7 A18 A6 A5 DQ0 NC NC DQ1

1 1

A3 A4 A2 A1 A0 CE# OE# VSS A3 A4 A2 A1 A0 CE# OE# VSS

A B C D E F G H A B C D E F G H

FIGURE 2: PIN ASSIGNMENTS FOR 48-BALL TFBGA

© 2000 Silicon Storage Technology, Inc. S71146 396-2 11/00

4

8 Mbit / 16 Mbit Multi-Purpose Flash

SST39LF080 / SST39LF016 / SST39VF080 / SST39VF016

Data Sheet

TABLE 2: PIN DESCRIPTION

Symbol Pin Name Functions

AMS-A0 Address Inputs To provide memory addresses. During Sector-Erase AMS-A12 address 1

lines will select the sector. During Block-Erase AMS-A16 address lines

will select the block.

DQ7-DQ0 Data Input/output To output data during Read cycles and receive input data during Write 2

cycles. Data is internally latched during a Write cycle. The outputs are in

tri-state when OE# or CE# is high.

CE# Chip Enable To activate the device when CE# is low. 3

OE# Output Enable To gate the data output buffers.

WE# Write Enable To control the Write operations.

VDD Power Supply To provide power supply voltage: 3.0-3.6V for SST39LF080/016 4

2.7-3.6V for SST39VF080/016

Vss Ground

NC No Connection Unconnected pins. 5

Note: AMS = Most significant address 396 PGM T2.2

AMS = A19 for SST39LF/VF080 and A20 for SST39LF/VF016.

6

TABLE 3: OPERATION MODES SELECTION

7

Mode CE# OE# WE# A9 DQ Address

Read VIL VIL VIH AIN DOUT AIN 8

Program VIL VIH VIL AIN DIN AIN

Erase VIL VIH VIL X X Sector or block address,

XXH for Chip-Erase 9

Standby VIH X X X High Z X

Write Inhibit X VIL X X High Z/ DOUT X

X X VIH X High Z/ DOUT X 10

Product Identification

Hardware Mode VIL VIL VIH VH Manufacturer's ID (BFH) AMS(2) - A1 = VIL, A0 = VIL 11

Device ID (1) A20(2) - A1 = VIL, A0 = VIH

Software Mode VIL VIL VIH AIN See Table 4

Notes: (1) Device ID D8H for SST39LF/VF080 and D9H for SST39LF/VF016

(2) AMS = Most significant address

396 PGM T3.2

12

AMS = A19 for SST39LF/VF080 and A20 for SST39LF/VF016.

13

14

15

16

© 2000 Silicon Storage Technology, Inc. S71146 396-2 11/00

5

8 Mbit / 16 Mbit Multi-Purpose Flash

SST39LF080 / SST39LF016 / SST39VF080 / SST39VF016

Data Sheet

TABLE 4: SOFTWARE COMMAND SEQUENCE

Command 1st Bus 2nd Bus 3rd Bus 4th Bus 5th Bus 6th Bus

Sequence Write Cycle Write Cycle Write Cycle Write Cycle Write Cycle Write Cycle

Addr(1) Data Addr(1) Data Addr(1) Data Addr(1) Data Addr(1) Data Addr(1) Data

Byte-Program 5555H AAH 2AAAH 55H 5555H A0H WA(3) Data

Sector-Erase 5555H AAH 2AAAH 55H 5555H 80H 5555H AAH 2AAAH 55H SAx(2) 30H

Block-Erase 5555H AAH 2AAAH 55H 5555H 80H 5555H AAH 2AAAH 55H BAx(2) 50H

Chip-Erase 5555H AAH 2AAAH 55H 5555H 80H 5555H AAH 2AAAH 55H 5555H 10H

Software ID Entry 5555H AAH 2AAAH 55H 5555H 90H

CFI Query Entry 5555H AAH 2AAAH 55H 5555H 98H

Software ID Exit/ XXH F0H

CFI Exit

Software ID Exit/ 5555H AAH 2AAAH 55H 5555H F0H

CFI Exit

396 PGM T4.1

Notes: (1) Address format A14-A0 (Hex),

Addresses A15, A16, A17, A18 and A19 are “Don’t Care” for Command sequence for SST39LF/VF080.

Addresses A15, A16, A17, A18, A19 and A20 are “Don’t Care” for Command sequence for SST39LF/VF016.

(2) SAx for Sector-Erase; uses AMS-A12 address lines

BAx, for Block-Erase; uses AMS-A16 address lines

AMS = Most significant address

AMS = A19 for SST39LF/VF080 and A20 for SST39LF/VF016.

(3) WA = Program byte address

(4) Both Software ID Exit operations are equivalent

Notes for Software ID Entry Command Sequence

1. With AMS -A1 = 0; SST Manufacturer's ID = BFH, is read with A0 = 0,

SST39LF/VF080 Device ID = D8H, is read with A0 = 1.

SST39LF/VF016 Device ID = D9H, is read with A0 = 1.

AMS = Most significant address

AMS = A19 for SST39LF/VF080 and A20 for SST39LF/VF016.

2. The device does not remain in Software Product ID Mode if powered down.

TABLE 5: CFI QUERY IDENTIFICATION STRING1 FOR SST39LF/VF080 AND SST39LF/VF016

Address Data Data

10H 51H

11H 52H Query Unique ASCII string “QRY”

12H 59H

13H 01H Primary OEM command set

14H 07H

15H 00H Address for Primary Extended Table

16H 00H

17H 00H Alternate OEM command set (00H = none exists)

18H 00H

19H 00H Address for Alternate OEM extended Table (00H = none exits)

1AH 00H

Note 1: Refer to CFI publication 100 for more details. 396 PGM T5.3

© 2000 Silicon Storage Technology, Inc. S71146 396-2 11/00

6

8 Mbit / 16 Mbit Multi-Purpose Flash

SST39LF080 / SST39LF016 / SST39VF080 / SST39VF016

Data Sheet

TABLE 6: SYSTEM INTERFACE INFORMATION FOR SST39LF/VF080 AND SST39LF/VF016

Address Data Data

1BH 27H1) VDD Min. (Program/Erase) 1

30H(1) DQ7-DQ4: Volts, DQ3-DQ0: 100 millivolts

1CH 36H VDD Max. (Program/Erase)

DQ7-DQ4: Volts, DQ3-DQ0: 100 millivolts 2

1DH 00H VPP min. (00H = no VPP pin)

1EH 00H VPP max. (00H = no VPP pin)

1FH 04H Typical time out for Byte-Program 2N µs (24 = 16 µs) 3

20H 00H Typical time out for min. size buffer program 2N µs (00H = not supported)

21H 04H Typical time out for individual Sector/Block-Erase 2N ms (24 = 16 ms)

22H 06H Typical time out for Chip-Erase 2N ms (26 = 64 ms)

4

23H 01H Maximum time out for Byte-Program 2N times typical (21 x 24 = 32 µs)

24H 00H Maximum time out for buffer program 2N times typical 5

25H 01H Maximum time out for individual Sector/Block-Erase 2N times typical

(21 x 24 = 32 ms)

26H 01H Maximum time out for Chip-Erase 2N times typical (21 x 26 = 128 ms) 6

Note (1) 30H for SST39LF080/016 and 27H for SST39VF080/016 396 PGM T6.1

TABLE 7A: DEVICE GEOMETRY INFORMATION FOR SST39LF/VF080

Address Data Data 7

27H 14H Device size = 2N Bytes (14H = 20; 220 = 1M Bytes)

28H 00H Flash Device Interface description; 0000H = x8-only asynchronous interface

29H 00H

8

2AH 00H Maximum number of byte in multi-byte write = 2N (00H = not supported)

2BH 00H

2CH 02H Number of Erase Sector/Block sizes supported by device

9

2DH FFH Sector Information (y + 1 = Number of sectors; z x 256B = sector size)

2EH 00H y = 255 + 1 = 256 sectors (00FFH = 255)

2FH 10H 10

30H 00H z = 16 x 256 Bytes = 4 KBytes/sector (0010H = 16)

31H 0FH Block Information (y + 1 = Number of blocks; z x 256B = block size)

32H 00H y = 15 + 1 = 16 blocks (000FH = 15) 11

33H 00H

34H 01H z = 256 x 256 Bytes = 64 KBytes/block (0100H = 256)

TABLE 7B: DEVICE GEOMETRY INFORMATION FOR SST39LF/VF016

396 PGM T7a.0 12

Address Data Data

27H 15H Device size = 2N Byte (15H = 21; 221 = 2M Bytes) 13

28H 00H Flash Device Interface description; 0000H = x8-only asynchronous interface

29H 00H

2AH 00H Maximum number of byte in multi-byte write = 2N (00H = not supported) 14

2BH 00H

2CH 02H Number of Erase Sector/Block sizes supported by device

2DH FFH Sector Information (y + 1 = Number of sectors; z x 256B = sector size) 15

2EH 01H y = 511 + 1 = 512 sectors (01FFH = 511)

2FH 10H

30H 00H z = 16 x 256 Bytes = 4 KBytes/sector (0010H = 16) 16

31H 1FH Block Information (y + 1 = Number of blocks; z x 256B = block size)

32H 00H y = 31 + 1 = 32 blocks (001FH = 31)

33H 00H

34H 01H z = 256 x 256 Bytes = 64 KBytes/block (0100H = 256)

396 PGM T7b.1

© 2000 Silicon Storage Technology, Inc. S71146 396-2 11/00

7

8 Mbit / 16 Mbit Multi-Purpose Flash

SST39LF080 / SST39LF016 / SST39VF080 / SST39VF016

Data Sheet

Absolute Maximum Stress Ratings (Applied conditions greater than those listed under “Absolute Maximum Stress

Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device

at these conditions or conditions greater than those defined in the operational sections of this data sheet is not implied.

Exposure to absolute maximum stress rating conditions may affect device reliability.)

Temperature Under Bias ................................................................................................................. -55°C to +125°C

Storage Temperature ...................................................................................................................... -65°C to +150°C

D. C. Voltage on Any Pin to Ground Potential ............................................................................ -0.5V to VDD + 0.5V

Transient Voltage (<20 ns) on Any Pin to Ground Potential ........................................................ -1.0V to VDD + 1.0V

Voltage on A9 Pin to Ground Potential ................................................................................................ -0.5V to 13.2V

Package Power Dissipation Capability (Ta = 25°C) ........................................................................................... 1.0W

Surface Mount Lead Soldering Temperature (3 Seconds) ............................................................................... 240°C

Output Short Circuit Current(1) ................................................................................................................................................................. 50 mA

Note: (1) Outputs shorted for no more than one second. No more than one output shorted at a time.

OPERATING RANGE FOR SST39LF080/016

Range Ambient Temp VDD

Commercial 0°C to +70 °C 3.0 - 3.6V

OPERATING RANGE FOR SST39VF080/016

Range Ambient Temp VDD

Commercial 0°C to +70°C 2.7 - 3.6V

Industrial -40°C to +85°C 2.7 - 3.6V

AC CONDITIONS OF TEST

Input Rise/Fall Time ......... 5 ns

Output Load ..................... CL = 30 pF for SST39LF080/016

........................................ CL = 100 pF for SST39VF080/016

See Figures 14 and 15

© 2000 Silicon Storage Technology, Inc. S71146 396-2 11/00

8

8 Mbit / 16 Mbit Multi-Purpose Flash

SST39LF080 / SST39LF016 / SST39VF080 / SST39VF016

Data Sheet

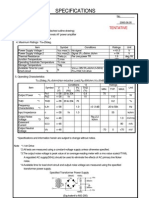

TABLE 8: DC OPERATING CHARACTERISTICS VDD = 3.0-3.6V FOR SST39LF080/016 AND 2.7-3.6V FOR SST39VF080/016

Limits

Symbol Parameter Min Max Units Test Conditions 1

IDD Power Supply Current Address input = VIL/VIH, at f=1/TRC Min.,

VDD=VDD Max.

Read 20 mA CE#=OE#=VIL,WE#=VIH , all I/Os open 2

Program and Erase 25 mA CE#=WE#=VIL, OE#=VIH

ISB Standby VDD Current 20 µA CE#=VIHC, VDD = VDD Max.

IALP Auto Low Power Current 20 µA CE#=VILC, VDD = VDD Max. All 3

inputs = VIHC or VILC WE# = VIHC

ILI Input Leakage Current 1 µA VIN =GND to VDD, VDD = VDD Max.

ILO Output Leakage Current 1 µA VOUT =GND to VDD, VDD = VDD Max. 4

VIL Input Low Voltage 0.8 V VDD = VDD Min.

VILC Input Low Voltage (CMOS) 0.3 V VDD = VDD Max.

5

VIH Input High Voltage 0.7 VDD V VDD = VDD Max.

VIHC Input High Voltage (CMOS) VDD-0.3 V VDD = VDD Max.

VOL Output Low Voltage 0.2 V IOL = 100 µA, VDD = VDD Min. 6

VOH Output High Voltage VDD-0.2 V IOH = -100 µA, VDD = VDD Min.

VH Supervoltage for A9 pin 11.4 12.6 V CE# = OE# =VIL, WE# = VIH

7

IH Supervoltage Current 200 µA CE# = OE# = VIL, WE# = VIH, A9 = VH Max.

for A9 pin

TABLE 9: RECOMMENDED SYSTEM POWER-UP TIMINGS

396 PGM T9.1

8

Symbol Parameter Minimum Units

TPU-READ (1) Power-up to Read Operation 100 µs 9

TPU-WRITE(1) Power-up to Program/Erase 100 µs

Operation

396 PGM T10.1 10

Note: (1) This parameter is measured only for initial qualification and after a design or process change that could affect this parameter.

TABLE 10: CAPACITANCE (Ta = 25 °C, f=1 Mhz, other pins open)

Parameter Description Test Condition Maximum 11

CI/O(1) I/O Pin Capacitance VI/O = 0V 12 pF

CIN(1) Input Capacitance VIN = 0V 6 pF 12

Note: (1) This parameter is measured only for initial qualification and after a design or process change that could affect this parameter.

396 PGM T11.0

TABLE 11: RELIABILITY CHARACTERISTICS 13

Symbol Parameter Minimum Specification Units Test Method

NEND (1) Endurance 10,000 Cycles JEDEC Standard A117

14

TDR(1) Data Retention 100 Years JEDEC Standard A103

VZAP_HBM(1) ESD Susceptibility 2000 Volts JEDEC Standard A114

Human Body Model 15

VZAP_MM(1) ESD Susceptibility 200 Volts JEDEC Standard A115

Machine Model

ILTH(1) Latch Up 100 + IDD mA JEDEC Standard 78 16

396 PGM T12.0

Note: (1) This parameter is measured only for initial qualification and after a design or process change that could affect this parameter.

© 2000 Silicon Storage Technology, Inc. S71146 396-2 11/00

9

8 Mbit / 16 Mbit Multi-Purpose Flash

SST39LF080 / SST39LF016 / SST39VF080 / SST39VF016

Data Sheet

AC CHARACTERISTICS

TABLE 12: READ CYCLE TIMING PARAMETERS

VDD = 3.0-3.6V FOR SST39LF080/016 AND 2.7-3.6V FOR SST39VF080/016

SST39LF080/016-55 SST39VF080/016-70 SST39VF080/016-90

Symbol Parameter Min Max Min Max Min Max Units

TRC Read Cycle Time 55 70 90 ns

TCE Chip Enable Access Time 55 70 90 ns

TAA Address Access Time 55 70 90 ns

TOE Output Enable Access Time 30 35 45 ns

TCLZ(1) CE# Low to Active Output 0 0 0 ns

TOLZ(1) OE# Low to Active Output 0 0 0 ns

TCHZ(1) CE# High to High-Z Output 15 20 30 ns

TOHZ(1) OE# High to High-Z Output 15 20 30 ns

TOH(1) Output Hold from Address 0 0 0 ns

Change

396 PGM T13.2

TABLE 13: PROGRAM/ERASE CYCLE TIMING PARAMETERS

Symbol Parameter Min Max Units

TBP Byte-Program Time 20 µs

TAS Address Setup Time 0 ns

TAH Address Hold Time 30 ns

TCS WE# and CE# Setup Time 0 ns

TCH WE# and CE# Hold Time 0 ns

TOES OE# High Setup Time 0 ns

TOEH OE# High Hold Time 10 ns

TCP CE# Pulse Width 40 ns

TWP WE# Pulse Width 40 ns

TWPH (1) WE# Pulse Width High 30 ns

TCPH (1) CE# Pulse Width High 30 ns

TDS Data Setup Time 30 ns

TDH (1) Data Hold Time 0 ns

TIDA (1) Software ID Access and Exit Time 150 ns

TSE Sector-Erase 25 ms

TBE Block-Erase 25 ms

TSCE Chip-Erase 100 ms

396 PGM T14.0

Note: (1) This parameter is measured only for initial qualification and after the design or process change that could affect this parameter.

© 2000 Silicon Storage Technology, Inc. S71146 396-2 11/00

10

8 Mbit / 16 Mbit Multi-Purpose Flash

SST39LF080 / SST39LF016 / SST39VF080 / SST39VF016

Data Sheet

TRC TAA

1

ADDRESS AMS-0

2

TCE

CE#

TOE

3

OE#

VIH TOLZ TOHZ 4

WE#

TCHZ

TCLZ

TOH

HIGH-Z

5

DQ7-0 HIGH-Z

DATA VALID DATA VALID

Note: AMS = Most significant address 396 ILL F02.1

6

AMS = A19 for SST39LF/VF080 and A20 for SST39LF/VF016.

7

FIGURE 3: READ CYCLE TIMING DIAGRAM

INTERNAL PROGRAM OPERATION STARTS

9

TBP

ADDRESS AMS-0 5555 2AAA 5555 ADDR

10

TAH

TDH

TWP

WE# 11

TAS TWPH TDS

OE# 12

TCH

CE# 13

TCS

DQ7-0 AA 55 A0 DATA 14

SW0 SW1 SW2 BYTE

(ADDR/DATA) 396 ILL F03.1 15

Note: AMS = Most significant address

AMS = A19 for SST39LF/VF080 and A20 for SST39LF/VF016.

16

FIGURE 4: WE# CONTROLLED PROGRAM CYCLE TIMING DIAGRAM

© 2000 Silicon Storage Technology, Inc. S71146 396-2 11/00

11

8 Mbit / 16 Mbit Multi-Purpose Flash

SST39LF080 / SST39LF016 / SST39VF080 / SST39VF016

Data Sheet

INTERNAL PROGRAM OPERATION STARTS

TBP

ADDRESS AMS-0 5555 2AAA 5555 ADDR

TAH

TDH

TCP

CE#

TAS TCPH TDS

OE#

TCH

WE#

TCS

DQ7-0 AA 55 A0 DATA

SW0 SW1 SW2 BYTE

(ADDR/DATA) 396 ILL F04.1

Note: AMS = Most significant address

AMS = A19 for SST39LF/VF080 and A20 for SST39LF/VF016.

FIGURE 5: CE# CONTROLLED PROGRAM CYCLE TIMING DIAGRAM

ADDRESS AMS-0

TCE

CE#

TOEH TOES

OE#

TOE

WE#

DQ7 DATA DATA# DATA# DATA

396 ILL F05.1

Note: AMS = Most significant address

AMS = A19 for SST39LF/VF080 and A20 for SST39LF/VF016.

FIGURE 6: DATA# POLLING TIMING DIAGRAM

© 2000 Silicon Storage Technology, Inc. S71146 396-2 11/00

12

8 Mbit / 16 Mbit Multi-Purpose Flash

SST39LF080 / SST39LF016 / SST39VF080 / SST39VF016

Data Sheet

ADDRESS AMS-0

1

TCE

2

CE#

TOE TOES

TOEH

3

OE#

WE#

4

DQ6

5

TWO READ CYCLES

WITH SAME OUTPUTS

396 ILL F06.1

6

Note: AMS = Most significant address

AMS = A19 for SST39LF/VF080 and A20 for SST39LF/VF016.

7

FIGURE 7: TOGGLE BIT TIMING DIAGRAM

8

TSCE

9

SIX-BYTE CODE FOR CHIP-ERASE

5555 2AAA 5555 5555 2AAA 5555

ADDRESS AMS-0 10

CE# 11

OE#

12

TWP

WE#

13

DQ7-0

AA 55 80 AA 55 10 14

SW0 SW1 SW2 SW3 SW4 SW5 396 ILL F08.1

Note: The device also supports CE# controlled Chip-Erase operation. The WE# and CE# signals are

15

interchangeable as long as minimum timings are met. (See Table 13)

AMS = Most significant address

AMS = A19 for SST39LF/VF080 and A20 for SST39LF/VF016. 16

FIGURE 8: WE# CONTROLLED CHIP-ERASE TIMING DIAGRAM

© 2000 Silicon Storage Technology, Inc. S71146 396-2 11/00

13

8 Mbit / 16 Mbit Multi-Purpose Flash

SST39LF080 / SST39LF016 / SST39VF080 / SST39VF016

Data Sheet

TBE

SIX-BYTE CODE FOR BLOCK-ERASE

5555 2AAA 5555 5555 2AAA BAX

ADDRESS AMS-0

CE#

OE#

TWP

WE#

DQ7-0

AA 55 80 AA 55 50

SW0 SW1 SW2 SW3 SW4 SW5 396 ILL F09.1

Note: The device also supports CE# controlled Block-Erase operation. The WE# and CE# signals are

interchangeable as long as minimum timings are met. (See Table 13)

AMS = Most significant address

AMS = A19 for SST39LF/VF080 and A20 for SST39LF/VF016.

FIGURE 9: WE# CONTROLLED BLOCK-ERASE TIMING DIAGRAM

SIX-BYTE CODE FOR SECTOR-ERASE TSE

5555 2AAA 5555 5555 2AAA SAX

ADDRESS AMS-0

CE#

OE#

TWP

WE#

DQ7-0

AA 55 80 AA 55 30

SW0 SW1 SW2 SW3 SW4 SW5 396 ILL F10.1

Note: The device also supports CE# controlled Sector-Erase operation. The WE# and CE# signals are

interchangeable as long as minimum timings are met. (See Table 13)

AMS = Most significant address

AMS = A19 for SST39LF/VF080 and A20 for SST39LF/VF016.

FIGURE 10: WE# CONTROLLED SECTOR-ERASE TIMING DIAGRAM

© 2000 Silicon Storage Technology, Inc. S71146 396-2 11/00

14

8 Mbit / 16 Mbit Multi-Purpose Flash

SST39LF080 / SST39LF016 / SST39VF080 / SST39VF016

Data Sheet

THREE-BYTE SEQUENCE FOR

SOFTWARE ID ENTRY

1

ADDRESS A14-0 5555 2AAA 5555 0000 0001

2

CE#

3

OE#

TWP TIDA 4

WE#

TWPH

TAA

5

DQ7-0

AA 55 90 BF Device ID

SW0 SW1 SW2

6

Note: Device ID = D9H for SST39LF/VF016

D8H for SST39LF/VF080 396 ILL F11.3

7

FIGURE 11: SOFTWARE ID ENTRY AND READ

8

9

THREE-BYTE SEQUENCE FOR

CFI QUERY ENTRY 10

ADDRESS A14-0 5555 2AAA 5555

11

CE#

12

OE#

TWP TIDA 13

WE#

TWPH 14

TAA

DQ7-0

AA 55 98

SW0 SW1 SW2

15

396 ILL F12.0

16

FIGURE 12: CFI QUERY ENTRY AND READ

© 2000 Silicon Storage Technology, Inc. S71146 396-2 11/00

15

8 Mbit / 16 Mbit Multi-Purpose Flash

SST39LF080 / SST39LF016 / SST39VF080 / SST39VF016

Data Sheet

THREE-BYTE SEQUENCE FOR

SOFTWARE ID EXIT AND RESET

ADDRESS A14-0 5555 2AAA 5555

DQ7-0 AA 55 F0

TIDA

CE#

OE#

TWP

WE#

T WHP

SW0 SW1 SW2

396 ILL F13.0

FIGURE 13: SOFTWARE ID EXIT/CFI EXIT

© 2000 Silicon Storage Technology, Inc. S71146 396-2 11/00

16

8 Mbit / 16 Mbit Multi-Purpose Flash

SST39LF080 / SST39LF016 / SST39VF080 / SST39VF016

Data Sheet

VIHT

1

INPUT VIT REFERENCE POINTS VOT OUTPUT

VILT 2

396 ILL F14.1

3

«

AC test inputs are driven at VIHT (0.9 VDD) for a logic “1” and VILT (0.1 VDD) for a logic “0”. Measurement reference points

for inputs and outputs are VIT (0.5 VDD) and VOT (0.5 VDD). Inputs rise and fall times (10% 90%) are <5 ns.

Note: VIT–VINPUT Test 4

VOT–VOUTPUT Test

VIHT–VINPUT HIGH Test

VILT–VINPUT LOW Test

5

FIGURE 14: AC INPUT/OUTPUT REFERENCE WAVEFORMS

6

7

TO TESTER

8

TO DUT

CL 9

396 ILL F15.1

10

FIGURE 15: A TEST LOAD EXAMPLE

11

12

13

14

15

16

© 2000 Silicon Storage Technology, Inc. S71146 396-2 11/00

17

8 Mbit / 16 Mbit Multi-Purpose Flash

SST39LF080 / SST39LF016 / SST39VF080 / SST39VF016

Data Sheet

Start

Load data: AAH

Address: 5555H

Load data: 55H

Address: 2AAAH

Load data: A0H

Address: 5555H

Load Byte

Address/Byte

Data

Wait for end of

Program (TBP,

Data# Polling

bit, or Toggle bit

operation)

Program

Completed

396 ILL F16.1

FIGURE 16: BYTE-PROGRAM ALGORITHM

© 2000 Silicon Storage Technology, Inc. S71146 396-2 11/00

18

8 Mbit / 16 Mbit Multi-Purpose Flash

SST39LF080 / SST39LF016 / SST39VF080 / SST39VF016

Data Sheet

1

Internal Timer Toggle Bit Data# Polling

Program/Erase

2

Program/Erase Program/Erase

Initiated Initiated Initiated

3

Read byte Read DQ7 4

Wait TBP,

TSCE, TSE

or TBE 5

Read same No Is DQ7 =

Program/Erase byte true data? 6

Completed

Yes

7

No Does DQ6 Program/Erase

match? Completed 8

Yes

9

Program/Erase

Completed

396 ILL F17.0 10

11

12

FIGURE 17: WAIT OPTIONS 13

14

15

16

© 2000 Silicon Storage Technology, Inc. S71146 396-2 11/00

19

8 Mbit / 16 Mbit Multi-Purpose Flash

SST39LF080 / SST39LF016 / SST39VF080 / SST39VF016

Data Sheet

CFI Query Entry Software Product ID Entry Software ID Exit/CFI Exit

Command Sequence Command Sequence Command Sequence

Load data: AAH Load data: AAH Load data: AAH Load data: F0H

Address: 5555H Address: 5555H Address: 5555H Address: XXH

Load data: 55H Load data: 55H Load data: 55H

Wait TIDA

Address: 2AAAH Address: 2AAAH Address: 2AAAH

Load data: 98H Load data: 90H Load data: F0H Return to normal

Address: 5555H Address: 5555H Address: 5555H operation

Wait TIDA Wait TIDA Wait TIDA

Read CFI data Read Software ID Return to normal

operation

396 ILL F18.1

FIGURE 18: SOFTWARE PRODUCT ID/CFI COMMAND FLOWCHARTS

© 2000 Silicon Storage Technology, Inc. S71146 396-2 11/00

20

8 Mbit / 16 Mbit Multi-Purpose Flash

SST39LF080 / SST39LF016 / SST39VF080 / SST39VF016

Data Sheet

Chip-Erase Sector-Erase Block-Erase

Command Sequence Command Sequence Command Sequence 1

Load data: AAH Load data: AAH Load data: AAH

Address: 5555H Address: 5555H Address: 5555H

2

3

Load data: 55H Load data: 55H Load data: 55H

Address: 2AAAH Address: 2AAAH Address: 2AAAH

4

Load data: 80H Load data: 80H Load data: 80H 5

Address: 5555H Address: 5555H Address: 5555H

6

Load data: AAH Load data: AAH Load data: AAH

Address: 5555H Address: 5555H Address: 5555H 7

8

Load data: 55H Load data: 55H Load data: 55H

Address: 2AAAH Address: 2AAAH Address: 2AAAH

9

Load data: 10H Load data: 30H Load data: 50H 10

Address: 5555H Address: SAX Address: BAX

11

Wait TSCE Wait TSE Wait TBE

12

Chip erased Sector erased Block erased

13

to FFH to FFH to FFH

14

396 ILL F19.1

15

FIGURE 19: ERASE COMMAND SEQUENCE

16

© 2000 Silicon Storage Technology, Inc. S71146 396-2 11/00

21

8 Mbit / 16 Mbit Multi-Purpose Flash

SST39LF080 / SST39LF016 / SST39VF080 / SST39VF016

Data Sheet

Device Speed Suffix1 Suffix2

SST39xFxxx - XXX - XX - XX

Package Modifier

I = 40 pins

K = 48 pins

Numeric = Die modifier

Package Type

E = TSOP (10mm x 20mm)

B2 = TFBGA (6mm x 8mm)

Temperature Range

C = Commercial = 0°C to +70°C

I = Industrial = -40°C to +85°C

Minimum Endurance

4 = 10,000 cycles

Read Access Speed

55 = 55 ns

70 = 70 ns

90 = 90 ns

Device Density

080 = 8 Megabit

016 = 16 Megabit

Voltage

L = 3.0-3.6V

V = 2.7-3.6V

SST39LF080 Valid combinations

SST39LF080-55-4C-EI SST39LF080-55-4C-B2K

SST39VF080 Valid combinations

SST39VF080-70-4C-EI SST39VF080-70-4C-B2K

SST39VF080-90-4C-EI SST39VF080-90-4C-B2K

SST39VF080-90-4I-EI SST39VF080-90-4I-B2K

SST39LF016 Valid combinations

SST39VF016-55-4C-EI SST39VF016-55-4C-B2K

SST39VF016 Valid combinations

SST39VF016-70-4C-EI SST39VF016-70-4C-B2K

SST39VF016-90-4C-EI SST39VF016-90-4C-B2K

SST39VF016-90-4I-EI SST39VF016-90-4I-B2K

Example: Valid combinations are those products in mass production or will be in mass production. Consult your SST sales

representative to confirm availability of valid combinations and to determine availability of new combinations.

© 2000 Silicon Storage Technology, Inc. S71146 396-2 11/00

22

8 Mbit / 16 Mbit Multi-Purpose Flash

SST39LF080 / SST39LF016 / SST39VF080 / SST39VF016

Data Sheet

PACKAGING DIAGRAMS

PIN # 1 IDENTIFIER

1.05

0.95 1

.50

BSC

2

.270

.170 3

10.10

9.90

5

18.50 0.15

0.05

18.30

6

0.70

0.50

7

20.20

19.80

Note: 1. Complies with JEDEC publication 95 MO-142 CD dimensions, although some dimensions may be more stringent.

8

2. All linear dimensions are in millimeters (min/max).

3. Coplanarity: 0.1 (±.05) mm. 40.TSOP-EI-ILL.3

40-PIN THIN SMALL OUTLINE PACKAGE (TSOP) 10MM X 20MM 9

SST PACKAGE CODE: EI

10

11

12

13

14

15

16

© 2000 Silicon Storage Technology, Inc. S71146 396-2 11/00

23

8 Mbit / 16 Mbit Multi-Purpose Flash

SST39LF080 / SST39LF016 / SST39VF080 / SST39VF016

Data Sheet

TOP VIEW BOTTOM VIEW

8.00 ± 0.20

5.60

0.80

6 6

5 5

4 4.00 4

3 6.00 ± 0.20 0.80 3

2 2

1 1

0.335 ± 0.035

(48X)

A B C D E F G H H G F E D C B A

A1 CORNER A1 CORNER

SIDE VIEW 1.10 ± 0.10

0.15 48ba TFBGA.B2K.6x8-ILL.1

SEATING PLANE

0.23 ± 0.04

Note: 1. Complies with the general requirements of JEDEC publication 95 MO-210, although some dimensions may be more stringent.

(This specific outline variant has not yet been registered)

2. All linear dimensions are in millimeters (min/max).

3. Coplanarity: 0.1 (±.05) mm.

48-BALL THIN PROFILE FINE-PITCH BALL GRID ARRAY (TFBGA) 6MM X 8MM

SST PACKAGE CODE: B2K

Silicon Storage Technology, Inc. • 1171 Sonora Court • Sunnyvale, CA 94086 • Telephone 408-735-9110 • Fax 408-735-9036

www.SuperFlash.com or www.ssti.com • Literature FaxBack 888-221-1178, International 732-544-2873

© 2000 Silicon Storage Technology, Inc. S71146 396-2 11/00

24

S-ar putea să vă placă și

- Gain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipDe la EverandGain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipÎncă nu există evaluări

- 8 Mbit / 16 Mbit (x8) Multi-Purpose Flash: SST39LF080 / SST39LF016 / SST39VF080 / SST39VF016Document27 pagini8 Mbit / 16 Mbit (x8) Multi-Purpose Flash: SST39LF080 / SST39LF016 / SST39VF080 / SST39VF016Denis DenisovÎncă nu există evaluări

- 39 SF 040Document22 pagini39 SF 040Jordi Arias GarcíaÎncă nu există evaluări

- 39sf010a SSTDocument22 pagini39sf010a SSTluiz_fellipesÎncă nu există evaluări

- 8 Mbit (x8) Multi-Purpose Flash: SST39VF088Document22 pagini8 Mbit (x8) Multi-Purpose Flash: SST39VF088vetchboyÎncă nu există evaluări

- SST 39VF1601Document32 paginiSST 39VF1601rogj19Încă nu există evaluări

- 512 Kbit / 1 Mbit / 2 Mbit / 4 Mbit (x8) Multi-Purpose FlashDocument25 pagini512 Kbit / 1 Mbit / 2 Mbit / 4 Mbit (x8) Multi-Purpose FlashJunaedi AbdillahÎncă nu există evaluări

- 16 Mbit / 32 Mbit / 64 Mbit (x16) Multi-Purpose Flash PlusDocument32 pagini16 Mbit / 32 Mbit / 64 Mbit (x16) Multi-Purpose Flash PlussaikumarÎncă nu există evaluări

- 512 Kbit / 1 Mbit / 2 Mbit / 4 Mbit (x8) Multi-Purpose FlashDocument24 pagini512 Kbit / 1 Mbit / 2 Mbit / 4 Mbit (x8) Multi-Purpose FlashvetchboyÎncă nu există evaluări

- SST26WF064C: 1.8V, 64 Mbit Serial Quad I/O (SQI) Flash MemoryDocument93 paginiSST26WF064C: 1.8V, 64 Mbit Serial Quad I/O (SQI) Flash MemoryManunoghiÎncă nu există evaluări

- 512 Kbit / 1 Mbit / 2 Mbit / 4 Mbit (x8) Small-Sector FlashDocument24 pagini512 Kbit / 1 Mbit / 2 Mbit / 4 Mbit (x8) Small-Sector FlashLuis Paulo JustinoÎncă nu există evaluări

- 1 Mbit SPI Serial Flash: FeaturesDocument28 pagini1 Mbit SPI Serial Flash: FeaturesdavidÎncă nu există evaluări

- 32 Mbit SPI Serial Flash: SST25VF032BDocument33 pagini32 Mbit SPI Serial Flash: SST25VF032Bedward blancoÎncă nu există evaluări

- Ultra Low Power 16 Mbit Serial SPI Page EEPROM With Dual and Quad OutputsDocument63 paginiUltra Low Power 16 Mbit Serial SPI Page EEPROM With Dual and Quad Outputsjosecente123321Încă nu există evaluări

- Datasheet SST40FDocument24 paginiDatasheet SST40FgreemaxÎncă nu există evaluări

- 256 Kbit / 512 Kbit / 1 Mbit / 2 Mbit (x8) Many-Time Programmable FlashDocument28 pagini256 Kbit / 512 Kbit / 1 Mbit / 2 Mbit (x8) Many-Time Programmable FlashvetchboyÎncă nu există evaluări

- Am29F400AT/Am29F400AB: 4 Megabit (524,288 X 8-Bit/262,144 X 16-Bit) CMOS 5.0 Volt-Only, Sector Erase Flash MemoryDocument35 paginiAm29F400AT/Am29F400AB: 4 Megabit (524,288 X 8-Bit/262,144 X 16-Bit) CMOS 5.0 Volt-Only, Sector Erase Flash MemoryAndrey OliveiraÎncă nu există evaluări

- N25Q512A83GSF40FDocument95 paginiN25Q512A83GSF40Fรัศมีเจริญชัย ธีรเมธÎncă nu există evaluări

- Micron Serial NOR Flash Memory: 3V, Multiple I/O, 4KB Sector Erase N25Q128A FeaturesDocument83 paginiMicron Serial NOR Flash Memory: 3V, Multiple I/O, 4KB Sector Erase N25Q128A FeaturesAnalia Madeled Tovar JimenezÎncă nu există evaluări

- 256 Kbit / 512 Kbit / 1 Mbit / 2 Mbit (x8) Many-Time Programmable FlashDocument26 pagini256 Kbit / 512 Kbit / 1 Mbit / 2 Mbit (x8) Many-Time Programmable Flashelias saenzÎncă nu există evaluări

- Ultra Low Power 32-Mbit Serial SPI Page EEPROM With Dual and Quad OutputsDocument70 paginiUltra Low Power 32-Mbit Serial SPI Page EEPROM With Dual and Quad OutputsJuanÎncă nu există evaluări

- Micron Serial NOR Flash Memory: 3V, Multiple I/O, 4KB Sector Erase N25Q064A FeaturesDocument81 paginiMicron Serial NOR Flash Memory: 3V, Multiple I/O, 4KB Sector Erase N25Q064A FeaturesalfredosnÎncă nu există evaluări

- 512 Kbit / 1 Mbit / 2 Mbit / 4 Mbit (x8) Many-Time Programmable FlashDocument16 pagini512 Kbit / 1 Mbit / 2 Mbit / 4 Mbit (x8) Many-Time Programmable FlashvetchboyÎncă nu există evaluări

- General Software FeaturesDocument41 paginiGeneral Software FeaturesNam NhiÎncă nu există evaluări

- ST 27 SF 010Document23 paginiST 27 SF 010joao victorÎncă nu există evaluări

- 2 Mbit SPI Serial Flash: FeaturesDocument27 pagini2 Mbit SPI Serial Flash: FeaturesBrahimiÎncă nu există evaluări

- And The For Reference.: 16 Mbit (2 M X 8-Bit/1 M X 16-Bit), 3 V Boot Sector FlashDocument53 paginiAnd The For Reference.: 16 Mbit (2 M X 8-Bit/1 M X 16-Bit), 3 V Boot Sector FlashRepararelcd LcdÎncă nu există evaluări

- mt25q Qlhs L 128 Aba 0Document93 paginimt25q Qlhs L 128 Aba 0landao.mduÎncă nu există evaluări

- MX25L1605Document45 paginiMX25L1605freddyÎncă nu există evaluări

- SST26VF080A: 2.5V/3.0V 8-Mbit Serial Quad I/O™ (SQI™) Flash MemoryDocument72 paginiSST26VF080A: 2.5V/3.0V 8-Mbit Serial Quad I/O™ (SQI™) Flash MemoryManunoghiÎncă nu există evaluări

- MT25QU512ABB8EDocument88 paginiMT25QU512ABB8Etinig64603Încă nu există evaluări

- 25L3205 MacronixInternationalDocument45 pagini25L3205 MacronixInternationalRavi ChavhanÎncă nu există evaluări

- Ultra Low-Power 8-Mbit Serial SPI Page EEPROM With Dual and Quad OutputsDocument66 paginiUltra Low-Power 8-Mbit Serial SPI Page EEPROM With Dual and Quad Outputsjavielo200322Încă nu există evaluări

- Mt25q QLKT L 01g BBB 0Document95 paginiMt25q QLKT L 01g BBB 0BKMohlmanÎncă nu există evaluări

- Micron Serial NOR Flash Memory: 3V, Multiple I/O, 4KB Sector Erase N25Q256A FeaturesDocument92 paginiMicron Serial NOR Flash Memory: 3V, Multiple I/O, 4KB Sector Erase N25Q256A FeaturesAEÎncă nu există evaluări

- Continuity of SpecificationsDocument61 paginiContinuity of Specificationsshatruddha123Încă nu există evaluări

- 89E516RD2 SiliconStorageTechnology PDFDocument91 pagini89E516RD2 SiliconStorageTechnology PDFKomsan RodkaewÎncă nu există evaluări

- Stm32, The Optimal Platform Choice The Stm32 Key Benefits: 72 MHZ Cortex-M3 Cpu - Wide Selection of DevicesDocument6 paginiStm32, The Optimal Platform Choice The Stm32 Key Benefits: 72 MHZ Cortex-M3 Cpu - Wide Selection of DevicesBa VuVanÎncă nu există evaluări

- En DM00780252Document6 paginiEn DM00780252Adlan MessaoudÎncă nu există evaluări

- Am29LV160D: Data SheetDocument52 paginiAm29LV160D: Data SheetVlad KadastrÎncă nu există evaluări

- Macronix Nbit Memory Family: 64M-Bit (X 1) Cmos Serial Eliteflash MemoryDocument46 paginiMacronix Nbit Memory Family: 64M-Bit (X 1) Cmos Serial Eliteflash MemoryRoger Chavez PachasÎncă nu există evaluări

- 512 Kbit SPI Serial Flash: FeaturesDocument30 pagini512 Kbit SPI Serial Flash: Featuresmahmuod mohamadÎncă nu există evaluări

- Am29F800BT/Am29F800BB: 8 Megabit (1 M X 8-Bit/512 K X 16-Bit) CMOS 5.0 Volt-Only Sector Erase Flash MemoryDocument37 paginiAm29F800BT/Am29F800BB: 8 Megabit (1 M X 8-Bit/512 K X 16-Bit) CMOS 5.0 Volt-Only Sector Erase Flash Memorycj002Încă nu există evaluări

- SST26VF064B SST26VF064BA 2 5V 3 0V 64 Mbit Serial - 2935898Document91 paginiSST26VF064B SST26VF064BA 2 5V 3 0V 64 Mbit Serial - 2935898ManunoghiÎncă nu există evaluări

- JD51单片机sst89e58数据手册Document79 paginiJD51单片机sst89e58数据手册史孟颜Încă nu există evaluări

- 25L1605A MacronixInternationalDocument41 pagini25L1605A MacronixInternationalpapainoelmorreuÎncă nu există evaluări

- Fpga Timeline & Applications: Fpgas Past, Present & FutureDocument39 paginiFpga Timeline & Applications: Fpgas Past, Present & FuturesmsarmadÎncă nu există evaluări

- M25PX80 NOR Serial Flash Embedded MemoryDocument56 paginiM25PX80 NOR Serial Flash Embedded MemoryCompu PluquisÎncă nu există evaluări

- 29F400 PDFDocument35 pagini29F400 PDFAhmad0% (1)

- 29F400Document35 pagini29F400AhmadÎncă nu există evaluări

- MSP430 Datasheet PDFDocument183 paginiMSP430 Datasheet PDFJuan David CarrilloÎncă nu există evaluări

- MX25L8005 MxicDocument41 paginiMX25L8005 Mxicdanehcan graÎncă nu există evaluări

- MX25L8005 MxicDocument42 paginiMX25L8005 MxicAnilVarmaÎncă nu există evaluări

- DatasheetDocument112 paginiDatasheetAntonioPierreÎncă nu există evaluări

- Am29F800B: Continuity of SpecificationsDocument45 paginiAm29F800B: Continuity of SpecificationsAlekseyyyÎncă nu există evaluări

- PM49FL002Document46 paginiPM49FL002asohas77Încă nu există evaluări

- 29F32G08CDocument160 pagini29F32G08CnorgenÎncă nu există evaluări

- 16 Mbit (2 M X 8-Bit/1 M X 16-Bit), 3 V Boot Sector Flash: S29AL016JDocument58 pagini16 Mbit (2 M X 8-Bit/1 M X 16-Bit), 3 V Boot Sector Flash: S29AL016JMurilo Smse SmseÎncă nu există evaluări

- M24128 BW STMicroelectronicsDocument46 paginiM24128 BW STMicroelectronicsupslab upslabÎncă nu există evaluări

- Datasheet PiccoloDocument177 paginiDatasheet PiccoloEric DilgerÎncă nu există evaluări

- 2 X 3 W Dual/Quad Power Amplifier For Car Radio: ProtectionsDocument10 pagini2 X 3 W Dual/Quad Power Amplifier For Car Radio: ProtectionsJosé VidalÎncă nu există evaluări

- Audio Tda8567q Spec enDocument20 paginiAudio Tda8567q Spec envetchboyÎncă nu există evaluări

- 4 X 30W Quad Bridge Car Radio Amplifier: Protections: DescriptionDocument12 pagini4 X 30W Quad Bridge Car Radio Amplifier: Protections: DescriptionvetchboyÎncă nu există evaluări

- Audio Tda8567q Spec enDocument20 paginiAudio Tda8567q Spec envetchboyÎncă nu există evaluări

- Audio Tda8510j Spec enDocument16 paginiAudio Tda8510j Spec envetchboyÎncă nu există evaluări

- Audio Tda8569q Spec enDocument20 paginiAudio Tda8569q Spec envetchboyÎncă nu există evaluări

- CD-R/RW Playback Shock Proof CDP Chipset Specification: (Full Digit LCD Model)Document16 paginiCD-R/RW Playback Shock Proof CDP Chipset Specification: (Full Digit LCD Model)vetchboyÎncă nu există evaluări

- TDA7384A: 4 X 35W Quad Bridge Car Radio AmplifierDocument9 paginiTDA7384A: 4 X 35W Quad Bridge Car Radio AmplifierGerardo Moreno RenteriaÎncă nu există evaluări

- Tda 7313Document15 paginiTda 7313jordachadiÎncă nu există evaluări

- Tda 7296Document14 paginiTda 7296Mayra GonzálezÎncă nu există evaluări

- 4 X 18W Bridge Car Radio Amplifier: Protections: DescriptionDocument10 pagini4 X 18W Bridge Car Radio Amplifier: Protections: DescriptionvetchboyÎncă nu există evaluări

- Digital Controlled Stereo Audio Processor With Loudness: DescriptionDocument14 paginiDigital Controlled Stereo Audio Processor With Loudness: DescriptionvetchboyÎncă nu există evaluări

- Dual Btl/Quad Power Amplifier For Car Radio: ProtectionsDocument14 paginiDual Btl/Quad Power Amplifier For Car Radio: ProtectionsvetchboyÎncă nu există evaluări

- 120V - 100W Dmos Audio Amplifier With Mute/St-By: Multipower BCD TechnologyDocument13 pagini120V - 100W Dmos Audio Amplifier With Mute/St-By: Multipower BCD TechnologyvetchboyÎncă nu există evaluări

- Amplificador 20W RMS TDA2003 Con Placa PCBDocument15 paginiAmplificador 20W RMS TDA2003 Con Placa PCBEnya Andrea Ribba Hernandez100% (5)

- Tda7294 PDFDocument16 paginiTda7294 PDFRoger NunesÎncă nu există evaluări

- Tda 7265 2 x25 WDocument12 paginiTda 7265 2 x25 WJavier CanaviriÎncă nu există evaluări

- 30W Bridge Car Radio Amplifier: DescriptionDocument10 pagini30W Bridge Car Radio Amplifier: DescriptionvetchboyÎncă nu există evaluări

- TDA1554Q 44W Audio AmplifierDocument11 paginiTDA1554Q 44W Audio Amplifiersava7698Încă nu există evaluări

- Tda 7269aDocument7 paginiTda 7269aAlexa DanÎncă nu există evaluări

- TDA 2822M CircuitoDocument11 paginiTDA 2822M CircuitoDATA24Încă nu există evaluări

- 10W Car Radio Audio Amplifier: DescriptionDocument11 pagini10W Car Radio Audio Amplifier: DescriptionvetchboyÎncă nu există evaluări

- Tda 2004Document11 paginiTda 2004Diana Belen Rodriguez HernandezÎncă nu există evaluări

- Audio Tda2002 Spec enDocument2 paginiAudio Tda2002 Spec envetchboyÎncă nu există evaluări

- STK442 110Document4 paginiSTK442 110Ivan AsimovÎncă nu există evaluări

- Description: Angus Electronics Company LimitedDocument9 paginiDescription: Angus Electronics Company LimitedvetchboyÎncă nu există evaluări

- TA2041 Four Channel Class-T Digital Audio Amplifier Using Digital Power Processing (DPP) TechnologyDocument18 paginiTA2041 Four Channel Class-T Digital Audio Amplifier Using Digital Power Processing (DPP) TechnologyvetchboyÎncă nu există evaluări

- Audio Tas5100a Spec enDocument15 paginiAudio Tas5100a Spec envetchboyÎncă nu există evaluări

- Low Power Quad Operational Amplifiers: LM124 LM224 - LM324Document13 paginiLow Power Quad Operational Amplifiers: LM124 LM224 - LM324vetchboyÎncă nu există evaluări

- Description: Angus Electronics Company LimitedDocument13 paginiDescription: Angus Electronics Company LimitedvetchboyÎncă nu există evaluări

- A New Approach To Economic Development in NunavutDocument26 paginiA New Approach To Economic Development in NunavutNunatsiaqNewsÎncă nu există evaluări

- Titanic Is A 1997 American Romantic Disaster Film Directed, Written. CoDocument13 paginiTitanic Is A 1997 American Romantic Disaster Film Directed, Written. CoJeric YutilaÎncă nu există evaluări

- Modicon M580 Quick Start - v1.0 - Training ManualDocument169 paginiModicon M580 Quick Start - v1.0 - Training Manualaryan_iust0% (1)

- Solar Water Pump Supreme RevDocument22 paginiSolar Water Pump Supreme RevBelayneh TadesseÎncă nu există evaluări

- Leadership and FollowershipDocument43 paginiLeadership and FollowershipNishant AgarwalÎncă nu există evaluări

- Chemistry Project On FertilizersDocument24 paginiChemistry Project On FertilizersKamal Thakur75% (4)

- CV HuangfuDocument5 paginiCV Huangfuapi-297997469Încă nu există evaluări

- Operating Temperature Considerations and Performance PDFDocument12 paginiOperating Temperature Considerations and Performance PDFccprado1Încă nu există evaluări

- Expanding UNIT 1 For 2º ESO.-the History of Music NotationDocument1 paginăExpanding UNIT 1 For 2º ESO.-the History of Music NotationEwerton CândidoÎncă nu există evaluări

- Evidence - 3 - Audio - Reading - Technical - Texts - To Pronounce - VocabularyDocument7 paginiEvidence - 3 - Audio - Reading - Technical - Texts - To Pronounce - VocabularyÅďřïàņä Łüćïą HõýöšÎncă nu există evaluări

- Nina Harris Mira Soskis Thalia Ehrenpreis Stella Martin and Lily Edwards - Popper Lab Write UpDocument4 paginiNina Harris Mira Soskis Thalia Ehrenpreis Stella Martin and Lily Edwards - Popper Lab Write Upapi-648007364Încă nu există evaluări

- Labour WelfareDocument250 paginiLabour WelfareArundhathi AdarshÎncă nu există evaluări

- Cambridge AS Business SyllabusDocument2 paginiCambridge AS Business SyllabusEnox ChangÎncă nu există evaluări

- Safety Instrumented Systems SummersDocument19 paginiSafety Instrumented Systems SummersCh Husnain BasraÎncă nu există evaluări

- Exp#4-Gas TurbineDocument9 paginiExp#4-Gas TurbineLilo17xiÎncă nu există evaluări

- Physics - DDPS1713 - Chapter 4-Work, Energy, Momentum and PowerDocument26 paginiPhysics - DDPS1713 - Chapter 4-Work, Energy, Momentum and Powerjimmi_ramliÎncă nu există evaluări

- The Mooladhara ChakraDocument13 paginiThe Mooladhara Chakraimamith100% (1)

- Associate Cloud Engineer - Study NotesDocument14 paginiAssociate Cloud Engineer - Study Notesabhi16101Încă nu există evaluări

- Community Service - Group 3 - Project 2Document24 paginiCommunity Service - Group 3 - Project 2rofiq wibawantoÎncă nu există evaluări

- 2011bibliography Part I (Preparation and Initial Assessment)Document188 pagini2011bibliography Part I (Preparation and Initial Assessment)Espiritu MineralÎncă nu există evaluări

- STIers Meeting Industry ProfessionalsDocument4 paginiSTIers Meeting Industry ProfessionalsAdrian Reloj VillanuevaÎncă nu există evaluări

- WEEK8 VI MAPARAAN WHLP Q2 - March1 4 2021Document8 paginiWEEK8 VI MAPARAAN WHLP Q2 - March1 4 2021Arjay M. VirayÎncă nu există evaluări

- Probability Form 4Document10 paginiProbability Form 4Deen ZakariaÎncă nu există evaluări

- Guideline For Grade and Compensation FitmentDocument5 paginiGuideline For Grade and Compensation FitmentVijit MisraÎncă nu există evaluări

- ESL BOOKS - IELTS Academic Writing Task 1 Vocabulary by ESL Fluency - PreviewDocument7 paginiESL BOOKS - IELTS Academic Writing Task 1 Vocabulary by ESL Fluency - Previewanirudh modhalavalasaÎncă nu există evaluări

- Review of Cyborg BabiesDocument3 paginiReview of Cyborg BabiesNate GreenslitÎncă nu există evaluări

- Transcript Biu2032Document5 paginiTranscript Biu2032Kuna KunavathiÎncă nu există evaluări

- Organisational B.Document62 paginiOrganisational B.Viktoria MolnarÎncă nu există evaluări

- BearingsDocument63 paginiBearingsYeabsraÎncă nu există evaluări

- Work Immersion Plan For Psychology Students in PsychologyDocument2 paginiWork Immersion Plan For Psychology Students in PsychologyJune DelaPaz Baunillo100% (1)