Documente Academic

Documente Profesional

Documente Cultură

Step-ByStep Flyback SMPS Design

Încărcat de

Phạm Văn TưởngDescriere originală:

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Step-ByStep Flyback SMPS Design

Încărcat de

Phạm Văn TưởngDrepturi de autor:

Formate disponibile

Prasun Kulshrestha, Sr. Design Engineer Hardware, Intellect Systems (i) Pvt Ltd.

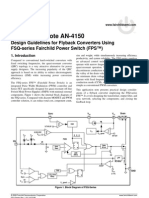

, Nagpur, INDIA Abstract: The approach of this article is to develop a sequential approach of practically designing the SMPS design Which are examined by me for years practically. The aim is to look on ground levels to clear fundamentals intelligence regarding SMPS. I had never seen Easy & step- by-step calculations to ideally decide the nature of SMPS. The Step-by-step calculations illustrated in this article will help you to actually see the practical result on paper before performing it practically. This also include the expertise tips wherever it is desired for either caution or for intelligence. Moreover, when you will make the actual schematic using these calculations, you will just need a perfect guidance for implementing correct component data book. I was also looking to include the probable components that could be referred but finally I am not including it in this. Universal Block Diagram :

Fig: Pras:1 Introduction: Designing the system step-by step could be realized below. Moreover the block diagram above is a selfexplanatory Universal block diagram of SMPS. I had enlisted the Sequential formulas below which will clear the insight towards SMPS. A. Step by step Designing Formulas: If No information is available , just assume Eff=0.75 for low output applications & 0.85 for high voltage applications. 1. Maximum input power: Pin = Po / E ff Put Eff = as discussed above. 2. Load occupying factor: Now, if we have to take multiple outputs from smps,the load occupying factor ( KLn) must be found asKLn=Po(n)/Po Here, Po(n) is the maximum output power for nth output. Usually, if single output from smps is desired, key rule is to consider KL = 1 3. Input capacitor Selection: It is also known as DC link capacitor. The universal approach should be to first recognize the few parameters as : Vac max; Vac min ; switching frequency ; line frequency & output power; This would clear the nature of quality of an ideal SMPS you are looking at. The key rule to decide the value of Dc link capacitor as 2-3 micro farad per watt of input range ( 85-

265vrms) & 1 micro farad per watt of input power of European range ( 195v -265vrms) Also, take my experience suggestion to use DC link capacitor more than 2 micro farad per watt of input range so as to get better quality of DC output. Also, for 230 v mains line, select the capacitor of min 400 v rating. It is because that we may use rectifier device which may multiply the input with the factor of 1.41. 3. Min DC link voltage: Vdc min = sprt( 2* ( v line min )^2-Pin ( 1-Dch )/ Cdc. Fl ) Where , Dch- dc link capacitor charging duty ratio. Dch is 0.2 to 0.25 Dch = t1 /t2 4. Maximum dc link voltage: Vdc max = sqrt (2 )* V line max 5. maximum DC link ripple voltage: Change in Vdc max = sqrt (2) * Vlin min V dc min While calculating this factor, care should be taken as accuracy of this factor affects the system a lot. 6. output reflected voltage: Vro = Dmax* Vdc min / (1- Dmax) 7. Maximum MOSFET voltage : Vds nom = Vdc max +Vro Where Vdc min & Vdc max is already calculated in step 3 & 4. Practical approach key rule: For step 6 & 7; If we decrease the value of Dmax, the voltage stress over MOSFET can be reduced suitably. But this will in turn increase the voltage stress over rectifier diode in the secondary side. So, I would suggest with my experience to Select Dmax as large as possible if the voltage rating of MOSFET allows. 8. Designing The inductance of the transformer primary side Lm: Lm= (Vdc min * Dmax)square / (2 Pin * Fs * Krf) Where Lm- primary inductance F s- switching frequency Krf- ripple factor in full load & min input voltage. Key rule: For discontinuous mode , set krf =1 For continuous mode, set kef < 1 If you are making flyback converter to be operated in CCM mode, just prefer to set krf between 0.25 0.5 for universal input range & krf = 0.4 0.8 for European input range. 9. Ids peak = I edc + ( Change in current / 2) 10. Ids rms = sqrt((3* (Iedc)square + ( change incurrent / 2 )square)Dmax / 3 ) 11. where Iedc = Pin / (Vdc min * Dmax) 12. Also, change in current = Vdc min * D max / (Lm* Fs) 13. Vdc in ccm mode = [1/(sqrt(2*Lm*fs*Pin))-1/Vro]^(-1) Key rule: If the result of equation 13 is in negative value, the converter is always in CCM under full load condition regardless of the input voltage variation. 14. Np (min) =[ Lm* Ilim * 10^(6) / ( Bsat * Ae)] (turns)

Where Ilim pulse by pulse current limit level Ae = cross section area of the core Bsat = saturation flux density in tesla Key rule: if no information is available regarding Bsat,for generalized smps, set Bsat between 0.3 to 0.35 tesla 15. Transformer design n = [Np/Ns1] =[Vrd/ ( V01+Vf1 )] where Np- number of turns of primary side Ns1- number of turns of reference output V01 output voltage VF1 Diode forward voltage drop of the reference output . Key suggestion: Now, determine the proper integer number for NS1 so that resulting Np is larger than Np min Obtained from step 14. 16. The number of turns for the other output , nth output, is determined as: Ns (n) = [ V0 (n) + Vf(n)* Ns1] / [ V01 +Vf1 ] turns 17. The number of turns for V0c winding is determined as : Na = [ Vcc + Vea /( V01 + Vf1 ) ] * Ns1 turns Where Vcc nominal voltage for Vcc. Vfa- Diode forward voltage drop. 18. with determing turns of the primary side, the gap length of the core is obtained as : G = 40* 3.14 * Ae [ {Np^(2)/ 1000Lm}-1/Al ] units in mm Where Al- Al value with no gap in nH/turns^(2) Ae = Cross section area of the core. Np = no. of turns for primary side of the transformer. 19: The RMS current of the nth secondary winding is obtained as : I sec (n)rms = I ds rms sqrt [ (1-Dmax/Dmax)] * Vro * Kln / { Von + Vf n } Where Von output voltage of nth output V fn diode forward voltage drop Kln load occupying factor for nth output defined in equation 2. Key information: The current density is 5A / mm2 when the wire is long (> 1m). when the wire is short with a small number of turns , a current density of 6-10 A/mm is also acceptable. Avoid using wire with a diameter larger than 1mm to avoid severe eddy current losses as well as to make winding easier. For high current output, it is better to use parallel winding with multiple strands of thinner wire to minimize skin effect. 19. The required winding window area is given by : Aw = Ac / Kf Where Ac actual conductor area Kf = Fill factor Key tip: Usually, fill factor is in between 0.2 to 0.25 for single output application. For, multiple output, it is in between 0.15 to 0.2.

20. The maximum voltage & the rms current of the rectifier diode of the nth output are obtained as : Vdn = V0n + Vdc max [ V0n + Vfn ] / Vro 21: Idn rms = Ids rms sqrt ( 1- Dmax /Dmax ) * Vro * Kln/ ( Von + Vfn ) where von output voltage of nth output vfn- diode forward drop. 22. The typical voltage & current margins for rectifier diode are as follows: Vrrm > 1.3 * Vdn 23. I f > 1.5 * I dn rms where , for equation 23 & 23, Vrrm maximum reverse voltage I f average forward current of diode. Trr- maximum reverse recovery time. 24. The ripple current of the nth output capacitor C0n is obtained as : I cap n rms = sqrt [ ( Id n rms) square Io (n)square ] Where Io (n) load current of the nth output Idc n rms equation 21. 25. the voltage ripple on the nth output is given as : change in Von = [Ion/(Con*Fs)] + [ Tds peak * V ro * Rcn * Kln] / [ Von + Vfn ] where: Con- capacitance Ron- effective series resistance ESR, of the nth output capacitor. Ion load current Von- output voltage Vfn diode forward voltage Key tip: IMPORTANT If we use single output capacitor, with high ESR, it is possible to meet ripple specification . If further required, use additional lc filter stages (post filter). When using post filter, be careful not to place the corner frequency too low. Too low corner frequency make the system unstable or limit the control bandwidth. It is typical to set the corner frequency of the post filter around 1/10 to 1/ 5 of the switching frequency. 26: Snubber design designing a snubber circuit is a vast field for calculations & implementations. But, the key formula is as below: Psn = Vsn ^(2)/ Rsn = [ Fs* Lik * (Ids peak)^(2)*Vsn/ (Vsn-Vro) ] Where Ids peak refer equation 9 Fs switching frequency Lik leakage inductance Vsn- snubber capacitance voltage At min i/p v & full load. Vro- reflected output voltage Rsn- snubber resistor Key tip:

Vsn should be greater than Vro & It is typical to set Vsn To be 2 to 2.5 times of Vro. Too small Vsn results in a severe loss in the snubber network as shown in equation 26. The leakage inductance is measured at the switching frequency with all other windings shorted. 27. The maximum ripple of the snubber capacitor voltage is obtained as : Change in Vsn = Vsn1/ ( Csn * Rsn * Fs) Key information: In general, 5 to 10 % ripple is reasonable. Use better quality capacitor, I would recommend it because high voltage spike affects the performance of Capacitor, so poor quality capacitor would be a worst option to use in such case. 28. Snubber capacitor Voltage under maximum input voltage & full load condition is obtained as : Vsn2 = Vro + Sqrt ( (Vro)^(2) + 2 Rsn * Lik * Fs * I ds2 ^ (2) / 2 Where Lik primary side leakage inductance Vro reflected output Voltage Rsn snubber resistor Ids 2 Peak drain current at the maximum input voltage & full load condition. 29: If the converter is operated in CCM mode, at the maximum input voltage & full load condition , for equation 28, I ds2 = [Pin (Vdc max + Vro)/ ( Vdc max * Vro)] + Vdc max * Vro/ [ 2Lm * Fs * ( Vdc max + Vro ) ] 30: If converter is operated in DCM at maximum input voltage & full load condition : Ids2 = Sqrt (2*Pin/ Fs* Lm) 31: Maximum voltage stress on the internal MOSFET is given by : Vds max = Vdc max + Vsn2 Key tip: Check if Vds max is below 90% of the rated voltage of MOSFET Bvdss . The voltage rating of snubber diode should be higher than BVdss. Usually ultra fast diodes with 1A current rating is used for snubber circuit. 32: Feedback calculations 32-A: Please consider few restrictions while calculating feedback elements. The voltage divider network of R1 & R2 should be designed to provide 2.5 to the reference pin of LM431/ Tl 431/ Ka431 Rf = 2.5 * R1/ [V01 2.5] Where Vref = reference output voltage of Lm431. 32-B: The Rbias & Rd used together with the opto coupler & the shunt regular LM431 should be designed to provide proper operating current for the LM431 & to guarantee the full swing of the feedback voltage for switching device used. In general , the minimum cathode voltage & current for the LM431 are 2.5 & 1mA. Respectively. Therefore, Rbias & Rd should be designed to satisfy the following conditions. 32-C

[ Vout-Vop-Vref / Rd ] > Ifb 32-D Vop/ Rbias > 1 mA Where Vout voltage supplying LM431 V op- Opto coupler forward drop 33: The current control factor of Power switch k is defined as : k = Ipk/ Vfb = I over / Vfb sat where , I pk peak drain current Vfb Feedback voltage I over current limit Fbsat feedback saturation voltage typically 2.5 34: For CCM operation, the control to output transfer function of the flyback converter using current mode control is given by : Gvc = [ V01/ V fb ] = [K* Rl*Vdc (Np/NS1)/2V*Ro][ (1+ S/w2)(1-S/w2)/ 1+(S/wp)] where Vdc input voltage Rl effective load resistance of controlled output. The pole & Zeros of step 34 are as : W2 = 1/ RC1* Co1 ; Wr2 = (1-D)^(2)/[D * Lm * (NS1 /Np)^(2) Wp = {1+D/ Rl * Co1} 35: For DCM operation : Gvc = V01/ Vfb = [Vo1/ VFB][ {1+S /w2}/ ( 1+ S/wp ) Where w2 = 1/ Rc1* Co1 Wp = 2/ [ Rc1* Co1 ] 36: The feedback Compensation network transfer function is defined as : Gvc = Vfb = -[Wi/s][ ( 1+s/w2c)/ ( 1+1/Wpc ) ] Where ; Wi= Rb/ [ R1*Rd* Cf ] W2c = 1/ [ (Rf+R1)*Cf] Wpc = 1/ [Rb* Cb] Feedback bias resistor 37: T delay = (Vsd 2.5) Cb/I delay

S-ar putea să vă placă și

- Universal Block DiagramDocument6 paginiUniversal Block Diagramapneetsandhu1234Încă nu există evaluări

- An 4134Document14 paginiAn 4134shri.bhairavkar6977Încă nu există evaluări

- Fly BackDocument20 paginiFly BackĐặng Văn TàiÎncă nu există evaluări

- An 4137Document20 paginiAn 4137Andres RinconÎncă nu există evaluări

- Snubber Circuit Design CalculatorsDocument3 paginiSnubber Circuit Design CalculatorsteomondoÎncă nu există evaluări

- Daycounter Inc - Snubber Circuit Design CalculatorsDocument5 paginiDaycounter Inc - Snubber Circuit Design CalculatorsLaercio Marques100% (1)

- Funcionamiento Del 5Q1265RF en La FuenteDocument19 paginiFuncionamiento Del 5Q1265RF en La FuenteJorge Corrales100% (1)

- Lm5032 Interleaved Boost Converter: D1 L1 Vin VoutDocument12 paginiLm5032 Interleaved Boost Converter: D1 L1 Vin VoutParvesh GautamÎncă nu există evaluări

- Application Note AN-4150: Design Guidelines For Flyback Converters Using FSQ-series Fairchild Power Switch (FPS™)Document16 paginiApplication Note AN-4150: Design Guidelines For Flyback Converters Using FSQ-series Fairchild Power Switch (FPS™)Nagendra ChaitanyaÎncă nu există evaluări

- Chang 09 Med PrimDocument6 paginiChang 09 Med PrimSuselleÎncă nu există evaluări

- The Cmos Inverter: OutlineDocument20 paginiThe Cmos Inverter: OutlinehappyharrÎncă nu există evaluări

- Design Battery ChargerDocument20 paginiDesign Battery Chargeranand_girgaonkar100% (1)

- Flyback Mathcad ExampleDocument13 paginiFlyback Mathcad ExamplePopescu LucianÎncă nu există evaluări

- Tri State InverterDocument18 paginiTri State InverterManasa Upadhyaya100% (1)

- Analysis and Design of Analog IcDocument21 paginiAnalysis and Design of Analog Icshankar100% (1)

- Unit 3Document40 paginiUnit 3Venkat ChadalavadaÎncă nu există evaluări

- Transformer Design Consideration For Off Line Flyback Converters Using Fairchild Power Switch (FPS™)Document10 paginiTransformer Design Consideration For Off Line Flyback Converters Using Fairchild Power Switch (FPS™)StefanvnvÎncă nu există evaluări

- Experiment 3 - Center Tapped Full Wave RectifierDocument6 paginiExperiment 3 - Center Tapped Full Wave RectifierRandred GarciaÎncă nu există evaluări

- An 1024Document19 paginiAn 1024vipulugale100% (1)

- SimlabDocument32 paginiSimlabAkbar AliÎncă nu există evaluări

- Bien AP XungDocument11 paginiBien AP XungVan Thanh TranÎncă nu există evaluări

- Lab 3 Switched Capacitor SimulationDocument28 paginiLab 3 Switched Capacitor SimulationDavid TynanÎncă nu există evaluări

- The Cmos Inverter: Slides Adapted From: N. Weste, D. Harris, CMOS VLSI Design,, 3/e, 2004Document40 paginiThe Cmos Inverter: Slides Adapted From: N. Weste, D. Harris, CMOS VLSI Design,, 3/e, 2004SrasVelÎncă nu există evaluări

- Delay: Minimum Time From The Input Crossing 50% To The OutputDocument12 paginiDelay: Minimum Time From The Input Crossing 50% To The Outputakash bhumiÎncă nu există evaluări

- An 4140Document11 paginiAn 4140ommidbeÎncă nu există evaluări

- Designing DC-DC Converters Based On ZETA TopologyDocument8 paginiDesigning DC-DC Converters Based On ZETA TopologyMayeth MacedaÎncă nu există evaluări

- 5W USB Flyback Design ReviewApplication ReportDocument21 pagini5W USB Flyback Design ReviewApplication ReportleechulmiuÎncă nu există evaluări

- An 4140Document11 paginiAn 4140Anonymous j7toV6z7PÎncă nu există evaluări

- Design Considerations For An LLC Resonant ConverterDocument29 paginiDesign Considerations For An LLC Resonant Converterbacuoc.nguyen356Încă nu există evaluări

- 3 To 8 Decoder in NGSPICEDocument14 pagini3 To 8 Decoder in NGSPICEJaydip FadaduÎncă nu există evaluări

- 3.4.2 Output Capacitor: Out C, Max OutDocument14 pagini3.4.2 Output Capacitor: Out C, Max OutReza RzÎncă nu există evaluări

- Euler's PathDocument10 paginiEuler's PathSatish Kumar0% (1)

- Snubber PDFDocument5 paginiSnubber PDFJ Milk SilvaÎncă nu există evaluări

- Design of First and Second Order Circuits in Time and Frequency DomainDocument40 paginiDesign of First and Second Order Circuits in Time and Frequency DomainsravanÎncă nu există evaluări

- DESIGN Power SupplyDocument2 paginiDESIGN Power SupplyARAVINDÎncă nu există evaluări

- International Refereed Journal of Engineering and Science (IRJES)Document8 paginiInternational Refereed Journal of Engineering and Science (IRJES)www.irjes.comÎncă nu există evaluări

- Chap16 2 CMOS Inverter ModifiedDocument14 paginiChap16 2 CMOS Inverter ModifiedSai Kiran OrugantiÎncă nu există evaluări

- Power Electronics Lab Manual With Orcad Pspice 10.5Document36 paginiPower Electronics Lab Manual With Orcad Pspice 10.5Muhammad Ahtisham Asif100% (2)

- Specifications.: OBJECTIVE: To Design, Simulate and Layout A CMOS Comparator With The GivenDocument10 paginiSpecifications.: OBJECTIVE: To Design, Simulate and Layout A CMOS Comparator With The Givenmxg091000Încă nu există evaluări

- Mathcad - Opamp 1974Document7 paginiMathcad - Opamp 1974Frank KarthikÎncă nu există evaluări

- Chapter Three Design and Analysis of The Various Units of The Circuit 3.1 IntrodutionDocument16 paginiChapter Three Design and Analysis of The Various Units of The Circuit 3.1 Introdutiondamyl4sure9577Încă nu există evaluări

- Power Amplifiers Part 1 Class A: We Have Studied The Design of Small-Signal AmplifiersDocument18 paginiPower Amplifiers Part 1 Class A: We Have Studied The Design of Small-Signal AmplifiersmalamigsajpanÎncă nu există evaluări

- Coen6511 Lecture 9: Digital Circuit HierarchyDocument14 paginiCoen6511 Lecture 9: Digital Circuit Hierarchydeathnote gotÎncă nu există evaluări

- Lab (GPDK)Document49 paginiLab (GPDK)Murali MurariÎncă nu există evaluări

- Experiment No. 05: Simulate I-V Characteristics of PN and Zener Diode Using LtspiceDocument10 paginiExperiment No. 05: Simulate I-V Characteristics of PN and Zener Diode Using LtspicesindhuÎncă nu există evaluări

- Implementation of A High Voltage Power SupplyDocument4 paginiImplementation of A High Voltage Power SupplyJiakeat LiauÎncă nu există evaluări

- Electronics Circuit Design LabDocument34 paginiElectronics Circuit Design Labsrvdhar100% (1)

- A PWM Circuit Using Operational AmplifiersDocument7 paginiA PWM Circuit Using Operational Amplifiershamza abdo mohamoud100% (1)

- PC-EE-504-Module 5 Power Electronics: InvertersDocument39 paginiPC-EE-504-Module 5 Power Electronics: InvertersSanjoy PathakÎncă nu există evaluări

- Switching Power Supply Design: A Concise Practical Handbook: February 2022Document5 paginiSwitching Power Supply Design: A Concise Practical Handbook: February 2022Juan Gil RocaÎncă nu există evaluări

- Switching Power Supply Design: A Concise Practical Handbook: February 2022Document5 paginiSwitching Power Supply Design: A Concise Practical Handbook: February 2022Wolfy gacha elamparoÎncă nu există evaluări

- CMOS Design With Delay ConstraintsDocument22 paginiCMOS Design With Delay ConstraintsKumar Amit VermaÎncă nu există evaluări

- RectifierDocument37 paginiRectifierMahendra Mandalapu MÎncă nu există evaluări

- Department of Electronics & TelecommunicationDocument12 paginiDepartment of Electronics & TelecommunicationMahadevÎncă nu există evaluări

- Vlsi Assign PDFDocument19 paginiVlsi Assign PDFudamtewÎncă nu există evaluări

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2De la EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Încă nu există evaluări

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1De la EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Evaluare: 2.5 din 5 stele2.5/5 (3)

- Influence of System Parameters Using Fuse Protection of Regenerative DC DrivesDe la EverandInfluence of System Parameters Using Fuse Protection of Regenerative DC DrivesÎncă nu există evaluări

- Predicting Temperature Rise of Ferrite Cored TransformersDocument5 paginiPredicting Temperature Rise of Ferrite Cored TransformersPhạm Văn TưởngÎncă nu există evaluări

- (TI) Frequency Response Measurements For Switching Power SuppliesDocument13 pagini(TI) Frequency Response Measurements For Switching Power Suppliesdsshin_psÎncă nu există evaluări

- Implementing Field Oriented Control of A Brushless DC MotorDocument10 paginiImplementing Field Oriented Control of A Brushless DC MotorPhạm Văn TưởngÎncă nu există evaluări

- Final ThesisDocument119 paginiFinal ThesisGüven ÖnbilginÎncă nu există evaluări

- C2000 MCU Real-Time Industrial Control TrainingDocument4 paginiC2000 MCU Real-Time Industrial Control TrainingPhạm Văn TưởngÎncă nu există evaluări

- Filters and Components With Inductance CancellationDocument9 paginiFilters and Components With Inductance CancellationPhạm Văn TưởngÎncă nu există evaluări

- Control of AC-DC Matrix Converter Using Digital PLLDocument6 paginiControl of AC-DC Matrix Converter Using Digital PLLPhạm Văn TưởngÎncă nu există evaluări

- Net Ties and How To Use ThemDocument10 paginiNet Ties and How To Use ThemPhạm Văn TưởngÎncă nu există evaluări

- Practical Thermal Measurements For DC-DC Converter ModulesDocument46 paginiPractical Thermal Measurements For DC-DC Converter ModulesPhạm Văn TưởngÎncă nu există evaluări

- An Introduction To Digital Control of Switching Power ConvertersDocument9 paginiAn Introduction To Digital Control of Switching Power ConvertersPhạm Văn TưởngÎncă nu există evaluări

- Review of Current Regulation Techniques For Three-Phase PWM InvertersDocument9 paginiReview of Current Regulation Techniques For Three-Phase PWM InvertersPhạm Văn TưởngÎncă nu există evaluări

- Digital Power Helps Get Products To Market More QuicklyDocument4 paginiDigital Power Helps Get Products To Market More QuicklyPhạm Văn TưởngÎncă nu există evaluări

- Digital Control of A Single-Phase UPS Inverter For Robust AC-Voltage TrackingDocument11 paginiDigital Control of A Single-Phase UPS Inverter For Robust AC-Voltage TrackingPhạm Văn TưởngÎncă nu există evaluări

- Vector Control of Trapezoidal Back-EMF PM Machines Using Pseudo-Park TransformationDocument5 paginiVector Control of Trapezoidal Back-EMF PM Machines Using Pseudo-Park TransformationPhạm Văn TưởngÎncă nu există evaluări

- Cap-Drop Off-Line Power SupplyDocument19 paginiCap-Drop Off-Line Power SupplypushrajaÎncă nu există evaluări

- A High Ef Ciency, Soft Switching DC-DC Converter With Adaptive Current-Ripple Control For Portable ApplicationsDocument5 paginiA High Ef Ciency, Soft Switching DC-DC Converter With Adaptive Current-Ripple Control For Portable ApplicationsPhạm Văn TưởngÎncă nu există evaluări

- Snvu128 13W Isolated Flyback LED Driver With PFCDocument7 paginiSnvu128 13W Isolated Flyback LED Driver With PFCPhạm Văn TưởngÎncă nu există evaluări

- Slua609 Synchronizing Three or More UCC28950 Phase-ShiftedDocument17 paginiSlua609 Synchronizing Three or More UCC28950 Phase-ShiftedPhạm Văn TưởngÎncă nu există evaluări

- A New Approach For Torque Ripple Minimization in Brushless DC MotorDocument5 paginiA New Approach For Torque Ripple Minimization in Brushless DC MotorPhạm Văn TưởngÎncă nu există evaluări

- Snvu233LM27403EVM Evaluation ModuleDocument31 paginiSnvu233LM27403EVM Evaluation ModulePhạm Văn TưởngÎncă nu există evaluări

- Slaa518a Nine-Axis Sensor Fusion Using The Direction Cosine - BatteryDocument15 paginiSlaa518a Nine-Axis Sensor Fusion Using The Direction Cosine - BatteryPhạm Văn TưởngÎncă nu există evaluări

- Slva498 Implementing A 60-W, End-To-End PoE SystemDocument13 paginiSlva498 Implementing A 60-W, End-To-End PoE SystemPhạm Văn TưởngÎncă nu există evaluări

- Sensorless Speed Control of Brushless DC Motor With Fuzzy Based EstimationDocument7 paginiSensorless Speed Control of Brushless DC Motor With Fuzzy Based EstimationPhạm Văn TưởngÎncă nu există evaluări

- Techniques For Input Ripple Current CancellationDocument9 paginiTechniques For Input Ripple Current CancellationPhạm Văn TưởngÎncă nu există evaluări

- Improved Core-Loss Calculation For Magnetic Components Employed in Power Electronic SystemsDocument11 paginiImproved Core-Loss Calculation For Magnetic Components Employed in Power Electronic SystemsPhạm Văn TưởngÎncă nu există evaluări

- Bpra072 Bpra072 TI Implementation of A Sensorless Speed BLDC Motor With TMS320Document41 paginiBpra072 Bpra072 TI Implementation of A Sensorless Speed BLDC Motor With TMS320Phùng TuấnÎncă nu există evaluări

- Current Control Techniques For Three-Phase Voltage-Source PWM ConvertersDocument13 paginiCurrent Control Techniques For Three-Phase Voltage-Source PWM Convertersedvin_s667100% (1)

- Isolated DC-DC Converters With High-OutputDocument10 paginiIsolated DC-DC Converters With High-OutputPhạm Văn TưởngÎncă nu există evaluări

- Em IDocument62 paginiEm IAiv DeeÎncă nu există evaluări

- Unified Control of Photovoltaic Grid-Connection and Power Quality ManagementsDocument6 paginiUnified Control of Photovoltaic Grid-Connection and Power Quality ManagementsAntar BeddarÎncă nu există evaluări

- ABB Lightning ArrestersDocument4 paginiABB Lightning ArrestersPrashanth ChandrashekarÎncă nu există evaluări

- 1501 - 001 - 06 SafetyDocument35 pagini1501 - 001 - 06 Safetynils_erickssonÎncă nu există evaluări

- SABP004 - Heat Exchanger and H Vessel FoundDocument35 paginiSABP004 - Heat Exchanger and H Vessel FoundgiovanniÎncă nu există evaluări

- Is - Iso 8042 PDFDocument7 paginiIs - Iso 8042 PDFPragna Test HouseÎncă nu există evaluări

- Physics - Problem Law of MotionDocument11 paginiPhysics - Problem Law of MotionLeejo9779Încă nu există evaluări

- EighthGradeApproved7 12 2004 PDFDocument7 paginiEighthGradeApproved7 12 2004 PDFcmnellÎncă nu există evaluări

- Basic Structures of Reality - Essays in Meta-Physics (PDFDrive)Document252 paginiBasic Structures of Reality - Essays in Meta-Physics (PDFDrive)Mulubrhan OkbaiÎncă nu există evaluări

- HV Test of PanelsDocument5 paginiHV Test of PanelsSumit SawaiÎncă nu există evaluări

- 4.3 Examples of Beam Analysis Using The Direct Stiffness Method DDocument1 pagină4.3 Examples of Beam Analysis Using The Direct Stiffness Method DAHMED SHAKERÎncă nu există evaluări

- Dynamic Response of Footing and Machine With Spring Mounting BaseDocument13 paginiDynamic Response of Footing and Machine With Spring Mounting Basejuan carlos molano toroÎncă nu există evaluări

- P6 Mass Lecture 1Document46 paginiP6 Mass Lecture 1Max LeeÎncă nu există evaluări

- Introduction To RelayDocument21 paginiIntroduction To RelayOk SokÎncă nu există evaluări

- (Myschoolchildren) PHY K2,3 Trial SPM 2012 Kelantan W AnsDocument57 pagini(Myschoolchildren) PHY K2,3 Trial SPM 2012 Kelantan W AnsqwerÎncă nu există evaluări

- TLE Review E (Electricity)Document64 paginiTLE Review E (Electricity)Kriselda DryÎncă nu există evaluări

- Elements OF Technology: BearingsDocument12 paginiElements OF Technology: BearingsRAHUL16398100% (1)

- Civil Aviation Previous PaperDocument3 paginiCivil Aviation Previous PaperObaid Rehman100% (1)

- On The Move - Exam Style QsDocument8 paginiOn The Move - Exam Style QsAdam ChiangÎncă nu există evaluări

- Physics Master PDF - JEE Main 2021 - 19 Chapter-WiseDocument1.306 paginiPhysics Master PDF - JEE Main 2021 - 19 Chapter-WiseShubh Agarwal100% (1)

- Gravitation: Important PointsDocument19 paginiGravitation: Important PointsSrinivasu ChintalaÎncă nu există evaluări

- Wavesproblems PDFDocument23 paginiWavesproblems PDFThols TholkapiyanÎncă nu există evaluări

- Electrical Specifications Division 16 SECTION 16120 WIRES AND CABLESDocument11 paginiElectrical Specifications Division 16 SECTION 16120 WIRES AND CABLESeng_asayedÎncă nu există evaluări

- Tneb - 1Document266 paginiTneb - 1Imran ZakirÎncă nu există evaluări

- Chapter 10 - ElectrostaticsDocument8 paginiChapter 10 - ElectrostaticsMary Kate BacongaÎncă nu există evaluări

- Bin and Hopper Design LectureDocument73 paginiBin and Hopper Design LectureGordon NapitupuluÎncă nu există evaluări

- Science and Tech.Document456 paginiScience and Tech.KamalÎncă nu există evaluări

- Phoenix Preparation PackDocument158 paginiPhoenix Preparation Packstimoceiver100% (2)

- SimScale Simulation Features Overview PDFDocument30 paginiSimScale Simulation Features Overview PDFRohith ChakkingalÎncă nu există evaluări

- IT Power & Cooling Cheat Sheet V 2.0Document1 paginăIT Power & Cooling Cheat Sheet V 2.0dglocknerÎncă nu există evaluări