Documente Academic

Documente Profesional

Documente Cultură

CH 3 Problems

Încărcat de

Diogo RodriguesDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

CH 3 Problems

Încărcat de

Diogo RodriguesDrepturi de autor:

Formate disponibile

Problems

19

[2]

S. M. CUK, Modeling, Analysis, and Design of Switching Converters, Ph.D. thesis, California Institute of Technology, November 1976. G. WESTER and R. D. MIDDLEBROOK, Low-Frequency Characterization of Switched DcDc Converters, IEEE Transactions on Aerospace and Electronic Systems, Vol. AES-9, pp. 376385, May 1973. R. D. MIDDLEBROOK and S. M. CUK, Modeling and Analysis Methods for Dc-to-Dc Switching Converters, IEEE International Semiconductor Power Converter Conference, 1977 Record, pp. 90-111.

[3]

[4]

PROBLEMS 3.1 In the buck-boost converter of Fig. 3.30, the inductor has winding resistance RL. All other losses can be ignored. (a) (b) (c) Derive an expression for the nonideal voltage conversion ratio V/Vg. Plot your result of part (a) over the range 0 D 1, for RL/R = 0, 0.01, and 0.05. Derive an expression for the efciency. Manipulate your expression into a form similar to Eq. (3.35) + Vg + L V Fig. 3.30 Nonideal buckboost converter, Problems 3.1 and 3.2. 3.2 The inductor in the buck-boost converter of Fig. 3.30 has winding resistance RL. All other losses can be ignored. Derive an equivalent circuit model for this converter. Your model should explicitly show the input port of the converter, and should contain two dc transformers. In the converter of Fig. 3.31, the inductor has winding resistance RL. All other losses can be ignored. The switches operate synchronously: each is in position 1 for 0 < t < DTs, and in position 2 for DTs < t < Ts. (a) (b) (c) Derive an expression for the nonideal voltage conversion ratio V/Vg. Plot your result of part (a) over the range 0 D 1, for RL/R = 0, 0.01, and 0.05. Derive an expression for the efciency. Manipulate your expression into a form similar to Eq. (3.35) L C

1 2

3.3

Vg

+

2

+ V

1

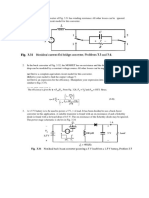

R Fig. 3.31 Nonideal current-fed bridge converter, Problems 3.3 and 3.4. 3.4 The inductor in the converter of Fig. 3.31 has winding resistance RL. All other losses can be ignored. Derive an equivalent circuit model for this converter.

20

Steady-State Equivalent Circuit Modeling, Losses, and Efciency

Q1

L +

Vg

D1

Fig. 3.32 Nonideal buck converter, Problem 3.5. 3.5 In the buck converter of Fig. 3.32, the MOSFET has on-resistance Ron and the diode forward voltage drop can be modeled by a constant voltage source VD. All other losses can be neglected. (a) (b) (c) 3.6 Derive a complete equivalent circuit model for this converter. Solve your model to nd the output voltage V. Derive an expression for the efciency. Manipulate your expression into a form similar to Eq. (3.35).

To reduce the switching harmonics present in the input current of a certain buck converter, an input lter is added as shown in Fig. 3.33. Inductors L1 and L2 contain winding resistances RL1 and RL2, respectively. The MOSFET has on-resistance Ron, and the diode forward voltage drop can be modeled by a constant voltage VD plus a resistor RD. All other losses can be ignored. L1 i1 Vg + C1 RL1 + vC1 Fig. 3.33 Buck converter with input lter, Problem 3.6. (a) (b) (c) Derive a complete equivalent circuit model for this circuit. Solve your model to nd the dc output voltage V. Derive an expression for the efciency. Manipulate your expression into a form similar to Eq. (3.35). D1 Q1 i2 C2 R L2 RL2 + v

3.7

A 1.5 V battery is to be used to power a 5 V, 1 A load. It has been decided to use a buck-boost converter in this application. A suitable transistor is found with an on-resistance of 35 m, and a Schottky diode is found with a forward drop of 0.5 V. The on-resistance of the Schottky diode may be ignored. The power stage schematic is shown in Fig. 3.34. 1A Q1 + Vg 1.5 V +

DTs Ts

Fig. 3.34 Nonideal buck-boost converter powering a 5 V load from a 1.5 V battery, Problem 3.7

100 H

5V

Load

fs = 40 kHz

Problems

21

(a)

Derive an equivalent circuit that models the dc properties of this converter. Include the transistor and diode conduction losses, as well as the inductor copper loss, but ignore all other sources of loss. Your model should correctly describe the converter dc input port. It is desired that the converter operate with at least 70% efciency under nominal conditions (i.e., when the input voltage is 1.5 V and the output is 5 V at 1 A). How large can the inductor winding resistance be? At what duty cycle will the converter then operate? Note: there is an easy way and a not-so-easy way to analytically solve this part. For your design of part (b), compute the power loss in each element. Plot the converter output voltage and efciency over the range 0 D 1, using the value of inductor winding resistance which you selected in part (b). Discuss your plot of part (d). Does it behave as you expect? Explain.

(b)

(c) (d) (e)

For Problems 3.8 and 3.9, a transistor having an on-resistance of 0.5 is used. To simplify the problems, you may neglect all losses other than the transistor conduction loss. You may also neglect the dependence of MOSFET on-resistance on rated blocking voltage. These simplifying assumptions reduce the differences between converters, but do not change the conclusions regarding which converter performs best in the given situations. 3.8 It is desired to interface a 500 V dc source to a 400 V, 10 A load using a dc-dc converter. Two possible approaches, using buck and buck-boost converters, are illustrated in Fig. 3.35. Use the assumptions described above to: (a) (b) (c) Derive equivalent circuit models for both converters, which model the converter input and output ports as well as the transistor conduction loss. Determine the duty cycles that cause the converters to operate with the specied conditions. Compare the transistor conduction losses and efciencies of the two approaches, and conclude which converter is better suited to the specied application. (a) + 500 V (b) 500 V + + 10 A + 400 V + 10 A + 400 V

Fig. 3.35 Problem 3.8: interfacing a 500 V source to a 400 V load, using (a) a buck converter, (b) a buck-boost converter. 3.9 It is desired to interface a 300 V battery to a 400 V, 10 A load using a dc-dc converter. Two possible approaches, using boost and buck-boost converters, are illustrated in Fig. 3.36. Using the assumptions described above (before Problem 3.8), determine the efciency and power loss of each approach. Which converter is better for this application?

S-ar putea să vă placă și

- Chap 03Document23 paginiChap 03Arnab DeÎncă nu există evaluări

- Bipolar Junction Transistor: E B CE CBDocument18 paginiBipolar Junction Transistor: E B CE CBMohammadAshraful100% (1)

- Electrical Machines by Siskind Solutions Book Mediafile Free File SharingDocument3 paginiElectrical Machines by Siskind Solutions Book Mediafile Free File SharingFrancisÎncă nu există evaluări

- Solution Manual For Electronic Devices and Circuit Theory 11th Edition by Boylestad Nashelsky ISBN 0132622262 9780132622264Document31 paginiSolution Manual For Electronic Devices and Circuit Theory 11th Edition by Boylestad Nashelsky ISBN 0132622262 9780132622264lauraÎncă nu există evaluări

- 1 Introduction To Power System AnalysisDocument33 pagini1 Introduction To Power System AnalysisSatta DhillonÎncă nu există evaluări

- EE251 Notes0 - Power System Models PDFDocument123 paginiEE251 Notes0 - Power System Models PDFJovan LabrigasÎncă nu există evaluări

- Ac Apparatus and Devices FinalsDocument2 paginiAc Apparatus and Devices FinalsbigbangÎncă nu există evaluări

- Tutorial CT TransformerDocument4 paginiTutorial CT TransformerKamal NorlieÎncă nu există evaluări

- Syllabus in Electrical Equipment DevicesDocument15 paginiSyllabus in Electrical Equipment Devicesrare machineÎncă nu există evaluări

- Lecture 1 - Mesh and Nodal AnalysisDocument50 paginiLecture 1 - Mesh and Nodal AnalysisCindy KoechÎncă nu există evaluări

- Solution:: KVA IpDocument3 paginiSolution:: KVA IpNoor Mohammed100% (1)

- Pe Chapter 6 DC Ac 1Document32 paginiPe Chapter 6 DC Ac 1Muhammad UsamaÎncă nu există evaluări

- Power Electronics (Ques - Ch2 - Rectifiers) PDFDocument44 paginiPower Electronics (Ques - Ch2 - Rectifiers) PDFmadivala nagaraja0% (1)

- Open-Circuit or No-Load TestDocument13 paginiOpen-Circuit or No-Load TestNANDHAKUMAR AÎncă nu există evaluări

- Electrical Apparatus SyllabusDocument14 paginiElectrical Apparatus SyllabusAndrea AlejandrinoÎncă nu există evaluări

- DC-DC ConvertersDocument30 paginiDC-DC ConvertersTema HassanÎncă nu există evaluări

- حلول سعادات p43-54Document12 paginiحلول سعادات p43-54يمامه انورÎncă nu există evaluări

- Ee 0308 Power System AnalysisDocument115 paginiEe 0308 Power System AnalysisNavneethÎncă nu există evaluări

- MCQ in DC Biasing - BJTsDocument6 paginiMCQ in DC Biasing - BJTsPaolo PerezÎncă nu există evaluări

- Effect of Internal Transistor Capacitances:: At, The Due To, and The Amplifier Response. But The WillDocument46 paginiEffect of Internal Transistor Capacitances:: At, The Due To, and The Amplifier Response. But The WillMuthukrishnan Vijayan VijayanÎncă nu există evaluări

- FET BiasingDocument48 paginiFET Biasingbetteralwz100% (3)

- RLC CircuitsDocument15 paginiRLC CircuitsSasindran SÎncă nu există evaluări

- Introduction To ElectrostaticsDocument38 paginiIntroduction To ElectrostaticsRamon Lopez Lapiña100% (1)

- Chapter21 TransformerDocument25 paginiChapter21 TransformerChin Chee FeeÎncă nu există evaluări

- DistributionsDocument4 paginiDistributionsReparrÎncă nu există evaluări

- Pe SS Final Ex 2010Document4 paginiPe SS Final Ex 2010Saif UddinÎncă nu există evaluări

- Final Exam Part 1 StudentDocument4 paginiFinal Exam Part 1 StudentRJ Balbedina100% (1)

- TransformerDocument29 paginiTransformergolu100% (1)

- Experiment 1 DIRECT - CURRENT INSTRUMENT AND MEASUREMENTSDocument2 paginiExperiment 1 DIRECT - CURRENT INSTRUMENT AND MEASUREMENTSErroll100% (1)

- Problem Statement:: Fig. 1: Zener Diode SymbolDocument10 paginiProblem Statement:: Fig. 1: Zener Diode SymbolTalha JabbarÎncă nu există evaluări

- Syllabus of Power SystemDocument2 paginiSyllabus of Power SystemdhoniÎncă nu există evaluări

- Topic 1: Armature Windings Construction: RulesDocument31 paginiTopic 1: Armature Windings Construction: RulesJhon denverÎncă nu există evaluări

- M Systems: ScilloscopesDocument6 paginiM Systems: ScilloscopesAnkit KumarÎncă nu există evaluări

- PPTDocument28 paginiPPTSri RamÎncă nu există evaluări

- DC Machine Example ProblemsDocument4 paginiDC Machine Example ProblemsFemi Prince0% (1)

- BJT Ac AnalysisDocument18 paginiBJT Ac AnalysisjjeongdongieeÎncă nu există evaluări

- Mesh and Nodal AnalysisDocument33 paginiMesh and Nodal AnalysisBenjamin Konaya Makoni100% (1)

- Sect2-3 PDFDocument10 paginiSect2-3 PDFBlaiseÎncă nu există evaluări

- CH 2 NotesDocument24 paginiCH 2 NotesJahangeer SoomroÎncă nu există evaluări

- Zener Diode and Diode ApplicationDocument62 paginiZener Diode and Diode Applicationnibar dyllanÎncă nu există evaluări

- Problem Set 1Document1 paginăProblem Set 1Chaeyoung YooÎncă nu există evaluări

- EN 206: Power Electronics and Machines: Direct Current (DC) MachinesDocument35 paginiEN 206: Power Electronics and Machines: Direct Current (DC) MachinesJaafar AbbakarÎncă nu există evaluări

- Transformer 1 2Document94 paginiTransformer 1 2Tobi AQWÎncă nu există evaluări

- EE0015 Lab Activity 4Document15 paginiEE0015 Lab Activity 4kyle vicenteÎncă nu există evaluări

- Lecture 6-Magnetic CircuitsDocument49 paginiLecture 6-Magnetic CircuitsMAENYA BRUCE OYONDIÎncă nu există evaluări

- Assignment 6Document4 paginiAssignment 6Nandhalal100% (1)

- Practical TransformerDocument9 paginiPractical TransformerCJP TVÎncă nu există evaluări

- Chapter 3. Circuit Analysis MethodsDocument176 paginiChapter 3. Circuit Analysis MethodsVeryyoga SihombingÎncă nu există evaluări

- Circuit Theory Solved Assignments - Semester Fall 2008Document28 paginiCircuit Theory Solved Assignments - Semester Fall 2008Muhammad Umair100% (3)

- Power Electronics Question Bank PDFDocument56 paginiPower Electronics Question Bank PDFkumar HIMANSHU100% (1)

- Unit 3 - DC - MotorDocument39 paginiUnit 3 - DC - MotordhoniÎncă nu există evaluări

- Power Electronics-3rd ChapterDocument80 paginiPower Electronics-3rd ChapterPasupuleti SivakumarÎncă nu există evaluări

- Chapter 3 Energy of A System ThermoDocument25 paginiChapter 3 Energy of A System ThermoEmadudin AbdulkaderÎncă nu există evaluări

- PeeDocument8 paginiPeeron villanuevaÎncă nu există evaluări

- DC Machines Module 8Document11 paginiDC Machines Module 8Joshua Roberto GrutaÎncă nu există evaluări

- Ee270 HW2Document7 paginiEe270 HW2saiedali2005Încă nu există evaluări

- Assignment 2Document2 paginiAssignment 2Misbah Sajid ChaudhryÎncă nu există evaluări

- Steady-State Equivalent Circuit Modeling, Losses, and EfficiencyDocument3 paginiSteady-State Equivalent Circuit Modeling, Losses, and EfficiencyPreserve OladipoÎncă nu există evaluări

- (ECEN 4797 and ECEN 5797) Two-Transistor Forward Converter: Modeling, Design and SimulationsDocument2 pagini(ECEN 4797 and ECEN 5797) Two-Transistor Forward Converter: Modeling, Design and SimulationsMaharshiGohelÎncă nu există evaluări

- 3 Steady State Equivalent Circuit ModeliDocument23 pagini3 Steady State Equivalent Circuit Modelioreo kooÎncă nu există evaluări

- Change LogDocument2 paginiChange LogDanielDavidBarriosFernándezÎncă nu există evaluări

- TransfDocument1 paginăTransfDiogo RodriguesÎncă nu există evaluări

- Installing Pspice 9.1: Ms Windows 7/8/10 ComputersDocument1 paginăInstalling Pspice 9.1: Ms Windows 7/8/10 ComputersDiogo RodriguesÎncă nu există evaluări

- LicenseDocument7 paginiLicenseAdnan AvdukićÎncă nu există evaluări

- Trabalho Lock inDocument5 paginiTrabalho Lock inDiogo RodriguesÎncă nu există evaluări

- Meu Malvado Favorito 3 DualDocument1 paginăMeu Malvado Favorito 3 DualDiogo RodriguesÎncă nu există evaluări

- Read MeDocument1 paginăRead MeArlynn Russwell Saavedra LeonÎncă nu există evaluări

- © 2000 Prentice Hall Inc.: Figure 3.1 Semiconductor DiodeDocument69 pagini© 2000 Prentice Hall Inc.: Figure 3.1 Semiconductor DiodeBeverly PamanÎncă nu există evaluări

- Common Back Handspring QuestionsDocument3 paginiCommon Back Handspring QuestionsDiogo RodriguesÎncă nu există evaluări

- ChangesDocument12 paginiChangesDiogo RodriguesÎncă nu există evaluări

- LicenseDocument7 paginiLicenseAdnan AvdukićÎncă nu există evaluări

- Synthesis of NetworksDocument50 paginiSynthesis of NetworksJosetheking CrackedsoftwaresÎncă nu există evaluări

- OpAmp F11Document34 paginiOpAmp F11Animesh GhoshÎncă nu există evaluări

- Ece 326 CH 04Document57 paginiEce 326 CH 04venkystyÎncă nu există evaluări

- © 2000 Prentice Hall Inc.: Figure 6.1 AND OperationDocument50 pagini© 2000 Prentice Hall Inc.: Figure 6.1 AND OperationDiogo RodriguesÎncă nu există evaluări

- Sedra - Cap2 - Ece326ch02Document60 paginiSedra - Cap2 - Ece326ch02Diogo RodriguesÎncă nu există evaluări

- ElectronicsDocument43 paginiElectronicsBeverly PamanÎncă nu există evaluări

- Imprimir - BeautyBay - CheckoutDocument2 paginiImprimir - BeautyBay - CheckoutDiogo RodriguesÎncă nu există evaluări

- Figure 1.1 Block Diagram of A Simple Electronic System: An AM RadioDocument40 paginiFigure 1.1 Block Diagram of A Simple Electronic System: An AM RadioDiogo RodriguesÎncă nu există evaluări

- Diploma in Electrical Engg. Semester-5 Power Electronics: Construction of SCRDocument6 paginiDiploma in Electrical Engg. Semester-5 Power Electronics: Construction of SCRDiogo RodriguesÎncă nu există evaluări

- TransfDocument1 paginăTransfDiogo RodriguesÎncă nu există evaluări

- SG3526BDWDocument9 paginiSG3526BDWDiogo RodriguesÎncă nu există evaluări

- Power Supply TemplatesDocument1 paginăPower Supply TemplatesDiogo RodriguesÎncă nu există evaluări

- Tabela Dos Principais TiristoresDocument3 paginiTabela Dos Principais Tiristoresapi-3837584100% (1)

- MikesDocument4 paginiMikesDiogo RodriguesÎncă nu există evaluări

- Bills of MaterialsDocument3 paginiBills of MaterialsDiogo RodriguesÎncă nu există evaluări

- ZH ZhusubaliyevDocument2 paginiZH ZhusubaliyevDiogo RodriguesÎncă nu există evaluări

- CHAPTER 5carlton EquipdocDocument4 paginiCHAPTER 5carlton EquipdocDiogo RodriguesÎncă nu există evaluări

- Week 13 Quiz 2Document1 paginăWeek 13 Quiz 2Diogo RodriguesÎncă nu există evaluări

- EULADocument3 paginiEULADon MihaiÎncă nu există evaluări

- Piyush NTPC Training ReportDocument83 paginiPiyush NTPC Training ReportRavi GuptaÎncă nu există evaluări

- Response - Records - Phase 2Document31 paginiResponse - Records - Phase 2Bob MackinÎncă nu există evaluări

- Dynamic (Vibration) Testing: Design-Certification of Aerospace SystemDocument16 paginiDynamic (Vibration) Testing: Design-Certification of Aerospace SystemCamelia MunteanuÎncă nu există evaluări

- Work With Linked ServersDocument44 paginiWork With Linked ServersioiÎncă nu există evaluări

- Design Simulation Manufacture and Testingof A Free-Piston Stirling Engine - Ivan Niell Deetlefs PDFDocument138 paginiDesign Simulation Manufacture and Testingof A Free-Piston Stirling Engine - Ivan Niell Deetlefs PDFJorge ValianteÎncă nu există evaluări

- Smore StoichiometryDocument4 paginiSmore Stoichiometry임민수Încă nu există evaluări

- Apf188088 enDocument130 paginiApf188088 enJavier LópezÎncă nu există evaluări

- 3674aclio1 PDFDocument81 pagini3674aclio1 PDFmattathiaÎncă nu există evaluări

- Advanced Placement Chemistry: 1991 Free Response QuestionsDocument15 paginiAdvanced Placement Chemistry: 1991 Free Response QuestionsManasÎncă nu există evaluări

- Anionic PolymerizationDocument7 paginiAnionic PolymerizationMuhammad FarooqÎncă nu există evaluări

- RE 10 030/04.99 External Gear Pumps Type G: 2, Series 4XDocument12 paginiRE 10 030/04.99 External Gear Pumps Type G: 2, Series 4XEnayat IzadiÎncă nu există evaluări

- Application of The EN 45545 Standard at SNCF: March 2016Document30 paginiApplication of The EN 45545 Standard at SNCF: March 2016pnagarajjÎncă nu există evaluări

- GT4 Strategy GuideDocument120 paginiGT4 Strategy GuideGiovanni BassiÎncă nu există evaluări

- JavaScript and XHTML DocumentsDocument40 paginiJavaScript and XHTML Documentstech2click100% (3)

- HBN PVC Free Alternatives ChartDocument24 paginiHBN PVC Free Alternatives ChartaggibudimanÎncă nu există evaluări

- Fulcrum Summer IssueDocument20 paginiFulcrum Summer IssuewillwnetÎncă nu există evaluări

- 03 Modern Photoelectric Effect LabDocument3 pagini03 Modern Photoelectric Effect LabJuan David ParraÎncă nu există evaluări

- Solved Problems (1) Draw The Cam Profile For Following ConditionsDocument6 paginiSolved Problems (1) Draw The Cam Profile For Following Conditionsrakesh kumarÎncă nu există evaluări

- Fccu PDFDocument2 paginiFccu PDFSumit KaushikÎncă nu există evaluări

- BoqDocument10 paginiBoqaylateÎncă nu există evaluări

- Gardner Denver S.R.L. Spare Parts Price List Gds 10Document140 paginiGardner Denver S.R.L. Spare Parts Price List Gds 10Tina Manousi100% (2)

- SCB - 9003.a.e Surge ArrestorDocument4 paginiSCB - 9003.a.e Surge ArrestorMichelle WebsterÎncă nu există evaluări

- Bottom Failure - Annex K - en 14015 - Rev 3Document3 paginiBottom Failure - Annex K - en 14015 - Rev 3KP SahuÎncă nu există evaluări

- 7723924w Operators ManualDocument32 pagini7723924w Operators ManualDorothy Mortenson0% (1)

- Honda Fit (Jazz) Front Door Panel Removal & Speaker Replacement Guide With Picture Illustrated InstrDocument1 paginăHonda Fit (Jazz) Front Door Panel Removal & Speaker Replacement Guide With Picture Illustrated InstrcamtomleeÎncă nu există evaluări

- 1.hydraulic Tank and Filter TankDocument1 pagină1.hydraulic Tank and Filter Tankazry_alqadryÎncă nu există evaluări

- Gear Can Be DefinedDocument31 paginiGear Can Be Definedasisha mostÎncă nu există evaluări

- Rigging Guide 2008Document222 paginiRigging Guide 2008Alex1Încă nu există evaluări

- Steel Structures - GeneralDocument16 paginiSteel Structures - Generalonur gunesÎncă nu există evaluări

- 343 - 135 - 278 - 80 7 Stud Vulkollan Drive Wheel - Wet GripDocument1 pagină343 - 135 - 278 - 80 7 Stud Vulkollan Drive Wheel - Wet GripASIFÎncă nu există evaluări