Documente Academic

Documente Profesional

Documente Cultură

Computer Architecture Guide

Încărcat de

Hari PathakTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Computer Architecture Guide

Încărcat de

Hari PathakDrepturi de autor:

Formate disponibile

Computer Architecture

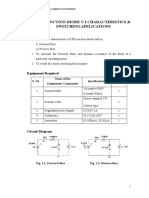

EG 2204 CT Total: 7 hour /week Year: II Lecture: 4 hours/week Semester: II Tutorial: hours/week Practical : 3 hours/week Course Description: This course is an introduction to computer architecture and organization. It covers topics in both the physical design of the computer (organization) and the logical design of the computer (architecture). Course Objectives: After completing this course the student will able to: 1. explain the over view of computer organization 2. explain the principle of CPU system 3. explain the principle of memory system 4. explain the principle of data flow Course Contents: Unit 1. Basic computer architecture: [6] 1.1 Introduction History of computer architecture Overview of computer organization Memory Hierarchy and cache External Memory Organization of hard disk 1.2 Instruction codes Stored program organization-Indirect address Computer Registers Common bus system Computer instruction Instruction set 1.3 Timing and Control-Instruction Cycle: Fetch and decode Limiting errors 1.4 Type of Instruction Register reference Instruction Memory reference instruction Input and output interrupt Unit 2. Micro programmed control: [8] 2.1 Basic Computer Design of Accumulator Control of AC register Adder and logic circuit ALU organization 2.2 Control Memory-Address Sequencing Conditional Branching Mapping of Instruction-Subroutines

2.3 Micro program Symbolic Micro program Binary Micro program 2.4 Design of control unit Basic requirement of control unit Structure of control unit Hard wired control unit Micro program sequencer Unit 3. Central processing Unit: [12] 3.1 General Register Organization: Control word. Stack organization. Instruction Formats-Addressing Modes 3.2 Data transfer and Manipulation: Data Transfer Instructions Data Manipulation Instructions Arithmetic Instructions Logical and Bit Manipulation Instructions Shift Instructions. 3.3 Program control: Status bit conditions Conditional Branch Instructions Subroutine Call and Return Program Interrupt Types of Interrupts. 3.4 Reduced Instruction set Computer (RISC): CISC Characteristics RISC Characteristics Overlapped Register Windows-Berkeley RISC I. Unit 4. Computer arithmetic and memory organization: [10] 4.1 Addition and Subtraction: Hardware Implementation Hardware Algorithm Addition and Subtraction with Signed-2's Complement 4.2 Data Multiplication Algorithms: Booth Multiplication Algorithm Array Multiplier. 4.3 Division Algorithms: Divide overflow Hardware Algorithm Floating Point Arithmetic Operations Basic considerations-Register Configuration 4.4 Memory concept Main Memory Auxiliary Memory Associative Memory: 4.5 Memory Hardware Organisation

Match Logic Read operation and Write operation. Cache memory Associative Mapping Direct Mapping Set-Associative Mapping Writing into Cache-Cache Initialization. Virtual Memory-Address space and Memory space4.6 Address mapping Using Pages Associative Memory page table Page Replacement-Memory Management Hardware Segmented-Page MappingUnit 5. Pipeline, vector processing and multiprocessors: [9] 5.1 Parallel Processing Pipelining-Arithmetic Pipeline-Instruction 5.2 Pipeline Examples Four Segment Instruction Pipeline Data Dependency Handling of Branch Instructions. RISC Pipeline Three Segment Instruction Delayed load-Delayed branch. 5.3 Vector Processing: Vector operations Matrix Multiplication Memory Interleaving Super computers. array processors: Attached Array Processor-SIMD Array processor. Practical: [45] 8085 Assembly Language program: 1. Multi byte Addition and Subtraction Multi byte decimal addition and subtraction 2. Adder and substractor circuit 3. Study of 8259 programmable interrupt controller - Development of interrupt service routine 4. Keyboard/display controller- Keyboard scan- blinking and rolling display 5. Parallel data transfer 6. Study of Microcomputer development system Text books: 1. Morris Mano.M., Computer System architecture, PHI, 1993. Reference books: 1. Hamacher.V.C.,Vranesic.Z.G and Zaky.S.G.,Computer Organisation, McGraw Hill, New York,III Edition,1990. 2. Hayes," Computer System Architecture",Mc Graw Hill,1998.

S-ar putea să vă placă și

- 04-Mentor Server Process MonitoringDocument25 pagini04-Mentor Server Process MonitoringMuoi NguyenÎncă nu există evaluări

- Cross-Layer Resource Allocation in Wireless Communications: Techniques and Models from PHY and MAC Layer InteractionDe la EverandCross-Layer Resource Allocation in Wireless Communications: Techniques and Models from PHY and MAC Layer InteractionÎncă nu există evaluări

- Understanding UMTS Radio Network Modelling, Planning and Automated Optimisation: Theory and PracticeDe la EverandUnderstanding UMTS Radio Network Modelling, Planning and Automated Optimisation: Theory and PracticeMaciej NawrockiÎncă nu există evaluări

- CAMEL: Intelligent Networks for the GSM, GPRS and UMTS NetworkDe la EverandCAMEL: Intelligent Networks for the GSM, GPRS and UMTS NetworkEvaluare: 2 din 5 stele2/5 (1)

- Wireless Technology (Includes Practicals)Document2 paginiWireless Technology (Includes Practicals)Dreamtech Press0% (1)

- Chapter 2 on Wireless LANs and PANsDocument37 paginiChapter 2 on Wireless LANs and PANsAntony PandiarajanÎncă nu există evaluări

- Presentation RF Optimization and PlanningDocument12 paginiPresentation RF Optimization and PlanningMohammad AshrafÎncă nu există evaluări

- Mobile Terminal Receiver Design: LTE and LTE-AdvancedDe la EverandMobile Terminal Receiver Design: LTE and LTE-AdvancedÎncă nu există evaluări

- Fundamentals of Cellular Network Planning and Optimisation: 2G/2.5G/3G... Evolution to 4GDe la EverandFundamentals of Cellular Network Planning and Optimisation: 2G/2.5G/3G... Evolution to 4GÎncă nu există evaluări

- WI MAX TechnologyDocument25 paginiWI MAX TechnologyGatlat Deng PuochÎncă nu există evaluări

- Making Telecoms Work: From Technical Innovation to Commercial SuccessDe la EverandMaking Telecoms Work: From Technical Innovation to Commercial SuccessÎncă nu există evaluări

- DSP Processors and ArchitecturesDocument2 paginiDSP Processors and ArchitecturesVemuganti RahulÎncă nu există evaluări

- CCS7 (Common Channel Signaling Number 7)Document16 paginiCCS7 (Common Channel Signaling Number 7)Michella Y0% (1)

- Wireless and Mobile CommunicationDocument26 paginiWireless and Mobile CommunicationSrinidhi BheesetteÎncă nu există evaluări

- Dipole Simulation Using ANSYS EDTDocument37 paginiDipole Simulation Using ANSYS EDTNix FaineÎncă nu există evaluări

- Question BankDocument5 paginiQuestion BankSwati AgarwalÎncă nu există evaluări

- Guide To CDMA Network Planning and Optimization - 20030115-B-1.0Document41 paginiGuide To CDMA Network Planning and Optimization - 20030115-B-1.0Nazer ElhamÎncă nu există evaluări

- Wireless & Mobile Comm CLOs GCUFDocument1 paginăWireless & Mobile Comm CLOs GCUFTayyab HasanÎncă nu există evaluări

- WCDMA Drive Test AnalysisDocument61 paginiWCDMA Drive Test AnalysiskarthikiwsÎncă nu există evaluări

- CH 21 Network Layer Address Mapping Error Reporting and Multicasting Multiple Choice Questions and Answers PDFDocument10 paginiCH 21 Network Layer Address Mapping Error Reporting and Multicasting Multiple Choice Questions and Answers PDFGayle LokeshÎncă nu există evaluări

- Mobile Transport LayerDocument18 paginiMobile Transport LayervalansterÎncă nu există evaluări

- Virtualization Enterprise Assignment 2Document2 paginiVirtualization Enterprise Assignment 2Rao Hammad ArshadÎncă nu există evaluări

- Atm Vs TDMDocument2 paginiAtm Vs TDMjsdoodnathÎncă nu există evaluări

- Ad Hoc Wireless NetworksDocument34 paginiAd Hoc Wireless Networksmurugan18Încă nu există evaluări

- UNIT II - Multi Core ArchitectureDocument102 paginiUNIT II - Multi Core ArchitectureVivek DubeyÎncă nu există evaluări

- Network Technologies and TCP/IP: Biyani's Think TankDocument78 paginiNetwork Technologies and TCP/IP: Biyani's Think TankDhruv Sharma100% (1)

- QoS LTE IEEE16mDocument16 paginiQoS LTE IEEE16mBityong Yusuf AutaÎncă nu există evaluări

- Resource Allocation in Hierarchical Cellular Systems PDFDocument216 paginiResource Allocation in Hierarchical Cellular Systems PDFOliver Pantoja CassolaÎncă nu există evaluări

- Huawei-WCDMA Radio Network Performance Management TrainingDocument2 paginiHuawei-WCDMA Radio Network Performance Management TrainingGauravSwami100% (1)

- CNS Important questions by TIE review teamDocument3 paginiCNS Important questions by TIE review team1JS19CS188 Vijay NaikÎncă nu există evaluări

- Network devices and their functions for CCNA examDocument5 paginiNetwork devices and their functions for CCNA examlvsaru50% (2)

- Network Field Tests: Walk & Drive Test GuideDocument23 paginiNetwork Field Tests: Walk & Drive Test Guide2000omotoÎncă nu există evaluări

- 1st 5G Algorithm Innovation Competition-EnV1.0 - SCMADocument31 pagini1st 5G Algorithm Innovation Competition-EnV1.0 - SCMAMohamed Abdel MonemÎncă nu există evaluări

- Technology Evaluation A Complete Guide - 2019 EditionDe la EverandTechnology Evaluation A Complete Guide - 2019 EditionÎncă nu există evaluări

- Computer Network SyllabusDocument4 paginiComputer Network SyllabusSanjay ShresthaÎncă nu există evaluări

- XDSL IntroductionDocument25 paginiXDSL IntroductionYunes Hasan Ahmed Ali100% (1)

- Technical, Commercial and Regulatory Challenges of QoS: An Internet Service Model PerspectiveDe la EverandTechnical, Commercial and Regulatory Challenges of QoS: An Internet Service Model PerspectiveÎncă nu există evaluări

- The Main Components of a Computer NetworkDocument17 paginiThe Main Components of a Computer NetworkpratikjaiÎncă nu există evaluări

- GCF CC 3501 (Changes Highlighted)Document80 paginiGCF CC 3501 (Changes Highlighted)ajit_balyan2003Încă nu există evaluări

- Admission Control in GPRS-EDGEDocument10 paginiAdmission Control in GPRS-EDGEVivek UttamÎncă nu există evaluări

- Lecture 05Document24 paginiLecture 05Abdul Ghani Khan100% (1)

- Hybrid WirelessDocument3 paginiHybrid WirelessHemant TulsaniÎncă nu există evaluări

- LteDocument15 paginiLteNishank Pandya100% (1)

- Web Technology - A Computer Science PerspectiveDocument105 paginiWeb Technology - A Computer Science PerspectivesharmilaÎncă nu există evaluări

- Unit2 - Basic Computer Organization and DesignDocument46 paginiUnit2 - Basic Computer Organization and Designaswini kurraÎncă nu există evaluări

- Optical NetworksDocument46 paginiOptical NetworksJaviÎncă nu există evaluări

- OPNET 14.5 Installation For WindowsDocument4 paginiOPNET 14.5 Installation For Windowscgbfish100% (2)

- VLSI Architecture and FPGA Implementation of Image Enhancement Algorithms For Medical ImagesDocument11 paginiVLSI Architecture and FPGA Implementation of Image Enhancement Algorithms For Medical ImagesParmeet Kumar100% (1)

- Fundamentals of Network Planning and Optimisation 2G/3G/4G: Evolution to 5GDe la EverandFundamentals of Network Planning and Optimisation 2G/3G/4G: Evolution to 5GÎncă nu există evaluări

- FCN SampleDocument5 paginiFCN SampleRoshun GeorgeÎncă nu există evaluări

- 3-Chapter - 10 - RTOS - Task CommunicationDocument9 pagini3-Chapter - 10 - RTOS - Task CommunicationBhuvana GowdaÎncă nu există evaluări

- UPTU Power Electronics NotesDocument225 paginiUPTU Power Electronics NotesZiya0% (1)

- Viettel PresentationDocument25 paginiViettel PresentationDuy NguyenÎncă nu există evaluări

- Datasheet - PDF 2 TriacDocument3 paginiDatasheet - PDF 2 TriacFlabio OliveiraÎncă nu există evaluări

- Variable speed drive ATV12 - 1.5kW - 2hp - 200..240V - 3ph - with heat sinkDocument11 paginiVariable speed drive ATV12 - 1.5kW - 2hp - 200..240V - 3ph - with heat sinkLeví StrataÎncă nu există evaluări

- SCADADocument16 paginiSCADAbalak88Încă nu există evaluări

- Memory Test Updated V3 ReducedDocument96 paginiMemory Test Updated V3 ReducedKruthi SubramanyaÎncă nu există evaluări

- IntroductionDocument53 paginiIntroductionTrọng QuảngÎncă nu există evaluări

- Data Sheet 7KG9501-0AA01-2AA1: Measuring FunctionsDocument4 paginiData Sheet 7KG9501-0AA01-2AA1: Measuring FunctionsPằngPằngChiuChiuÎncă nu există evaluări

- Communication & Control Software For UTD2000 - 3000 Series Oscilloscopes User Manual V1.0Document28 paginiCommunication & Control Software For UTD2000 - 3000 Series Oscilloscopes User Manual V1.0Damir MiletaÎncă nu există evaluări

- Window Function ComparisonsDocument7 paginiWindow Function ComparisonsHaripriya RadhakrishnanÎncă nu există evaluări

- Datasheet Phoenix Inverter 180VA 1200VA EN 1 PDFDocument2 paginiDatasheet Phoenix Inverter 180VA 1200VA EN 1 PDFMcciuken DanielÎncă nu există evaluări

- South Tse Tank Addc Electrical Drawing Approval (1) ..Document1 paginăSouth Tse Tank Addc Electrical Drawing Approval (1) ..Swami NathanÎncă nu există evaluări

- Semiconductor Devices and Circuits LaboratoryDocument53 paginiSemiconductor Devices and Circuits LaboratoryKaryampudi RushendrababuÎncă nu există evaluări

- SECTION 15180 BMS and Automatic ControlsDocument32 paginiSECTION 15180 BMS and Automatic ControlskdpmansiÎncă nu există evaluări

- Rtos ProjectDocument19 paginiRtos Projectsreelekha9Încă nu există evaluări

- Double-Transceiver Unit (DTRU)Document26 paginiDouble-Transceiver Unit (DTRU)Harsh PathakÎncă nu există evaluări

- Multiplexing and Demultiplexing ExplainedDocument16 paginiMultiplexing and Demultiplexing ExplainedHarsh IsamaliaÎncă nu există evaluări

- Nemo OutdoorDocument30 paginiNemo OutdoorhoabichcaÎncă nu există evaluări

- MC9S12DG128 FreescaleSemiconductorDocument595 paginiMC9S12DG128 FreescaleSemiconductorChristiam OrtegaÎncă nu există evaluări

- Occupational Code:: Ict Hns3Document6 paginiOccupational Code:: Ict Hns3Alem GirmaÎncă nu există evaluări

- GSM Frame Structure-Finalwith GraphsDocument28 paginiGSM Frame Structure-Finalwith GraphsMohammed Fabin100% (1)

- DatasheetDocument7 paginiDatasheetDarcio TolottiÎncă nu există evaluări

- 8 Series Type Test Report EMI Power Frequency Immunity Test IEC60255-22-7: 2003Document11 pagini8 Series Type Test Report EMI Power Frequency Immunity Test IEC60255-22-7: 2003andrez880103Încă nu există evaluări

- OJT Weekly Report Edit For HardboundDocument8 paginiOJT Weekly Report Edit For HardboundveliantmÎncă nu există evaluări

- Assignment # 2Document1 paginăAssignment # 2Mod454Încă nu există evaluări

- Basic Principles of Fiber Optic CommunicationDocument3 paginiBasic Principles of Fiber Optic CommunicationHumayra Anjumee100% (2)

- Performance Evaluation of 6T, 7T & 8T SRAM at 180 NM TechnologyDocument7 paginiPerformance Evaluation of 6T, 7T & 8T SRAM at 180 NM TechnologyDr-Sanjeev KashyapÎncă nu există evaluări

- Walk-Through Metal Detector Installation ManualDocument44 paginiWalk-Through Metal Detector Installation ManualErick Navarrete50% (2)

- Omnet Tutorial PDFDocument63 paginiOmnet Tutorial PDFSatya VeniÎncă nu există evaluări

- RN-AC106-3A: Low Frequency Accelerometer, Side Connector, 500 MV/GDocument1 paginăRN-AC106-3A: Low Frequency Accelerometer, Side Connector, 500 MV/GkylegazeÎncă nu există evaluări