Documente Academic

Documente Profesional

Documente Cultură

Apuntes de Electronica Digital y Memorias

Încărcat de

junixlpDescriere originală:

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Apuntes de Electronica Digital y Memorias

Încărcat de

junixlpDrepturi de autor:

Formate disponibile

1.- INTRODUCCIN.

1.1.- Circuitos secuenciales.

En los circuitos combinacionales las salidas son funciones que dependen nicamente de las entradas actuales al circuito. Pero sin embargo, en muchos sistemas digitales sto no es suficiente, siendo necesario adems circuitos capaces de almacenar informacin, puesto que en ellos las salidas no quedan definidas nicamente por las entradas actuales, sino que dependen tambin de cules fueron los valores de stas en el pasado. Se trata de los circuitos secuenciales. Ejemplos de la utilizacin de circuitos secuenciales podemos encontrarlos en la vida diaria: relojes digitales, sistemas de control de semforos en carretereas y lneas frreas, marcadores (deportes), anuncios sobre arrays de leds... Todos estos sistemas se caracterizan porque pueden ser descritos utilizando el llamado modelo de Huffman. Se trata de un modelo estructural que permite la descripcin de un circuito secuencial genrico. Segn el modelo, el circuito consta de dos partes: un circuito combinacional C y un conjunto de elementos de memoria M, como muestra la figura 1.1. Pues bien, el valor de las salidas zi depende, a travs de la funcin de salida que implementa el circuito combinacional, no slo de los valores actuales de las entradas xi, sino tambin del contenido actual de los elementos de momoria, En estos elementos, lo que se almacena es el llamado estado actual del sistema secuencial, que puede considerarse como su registro histrico, ya que da cuenta de su evolucin anterior. El paso desde el estado actual del sistema a un estado siguiente, viene a su vez definido por la llamada funcin de transicin de estados, que tambin depender no slo de los valores actuales de las entradas, sino tambin del propio estado actual.

Figura 1.1: Modelo de Huffman para un circuito secuencial. Centrndonos en la arquitectura de los computadores, componentes bsicos como los registros, memorias y la unicad de control, constituyen circuitos secuenciales, aunque de muy diverso grado de complejidad.

1.1.1.- Los biestables. Clasificacin.

Las clulas elementales de memoria de los circuitos secuenciales se denominan biestables o Flip-Flop. Se caracterizan por ser capaces de adoptar dos estados estables, que se corresponden a los niveles lgicos "0" y "1", que perduran en el tiempo de un modo indefinido, aunque haya desaparecido la excitacin que los origin. Es decir: son capaces de memorizar un bit de informacin. Una estructura con puertas lgicas que consigue el propsito anterior, es sencillamente la de la ligura 1.2. Se trata de dos inversores realimentados cuyas salidas definen las dos salidas complementarias Q y Q'. Este biestable elemental tiene nicamente dos posibilidades de almacenamiento: estado 0 (Q=O) y estado 1 (Q=1). Obsrvese que la realimentacin entre las salidas y las entradas de los inversores garantiza la permanencia de la informacin almacenada (memorizada) en todo momento del funcionamiento electrnico normal (tensin y corrientes de alimentacin adecuadas). Esto no ocurre en los sistemas combinacionales, donde la informacion a la salida de las puertas se desvirta necesariamente al eliminar las excitaciones de entrada.

Figura 1.2: Estructura bsica de memorizacin de un biestable. Al objeto de poder modificar el estado de los biestables, se hace necesario aadir algunas entradas externas al ncleo de memorizacin que se acaba de introducir. Reciben el nombre de lgica de disparo del biestable, y su valor determina el valor dle Q. Atendiendo a la lgica de disparo se puede efectuar una primera clasificacin de los biestables: RS, JK, D, T. Adems, si la actuacin de las entradas de la lgica de disparo se sincroniza con una seal externa de reloj que fija los instantes en los que se producen los cambios de estado, se habla de biestables sncronos (en caso contrario, biestables asncronos). En el caso de los biestables sncronos, otra clasificacin habitual recoge la forma en la que la lgica de disparo afecta al nuevo estado en sincronismo con la onda cuadrada de la seal de reloj. Se trata del tipo de disparo del biestable, que bsicamente puede ser por nivel de tensin o por flanco. En la figura 1.4 Qt indica estado anterior y indica flanco ascendente, es decir, el paso de la informacin ocurre cuando la seal de control pasa de 0 a 1.

Figura 1.3: Biestable disparado por nivel.

Figura 1.4: Biestable disparado por flanco. A las seales de control de los biestables disparados por flanco se les llama CK (Clock). Estas seales son generalmente peridicas (aunque pueden no serlo) y gobiernan la transicin de un estado a otro. Son seales de "sincronismo" que miden el tiempo del circuito. La sincronizacin es la tcnica principal para hacer evolucionar un circuito secuencial. En los biestables disparados por flanco puede haber tambin seales asncronas que hay que tener en cuenta, es decir, seales no relacionadas con las seales temporales de sincronismo. Por ejemplo, al ltimo biestable podemos aadir dos entradas asincronas de reset CLR y set PRE. El objetivo de estas seales, es que al tener estos dispositivos informacin almacenada que en un momento dado puede ser desconocida, se hace necesario el poderlos inicializar a un valor conocido. As con la seal CLEAR ponemos a 0 la salida y con la seal PRE a 1. A continuacin pasaremos a comentar y repasar los modelos elementales de biestables y la representacin funcional de los mismos.

Biestable RS.

Es la clula ms elemental. Su inconveniente es que la combinacin 11 no es estable (si fuera R'S' la combinacion no estable seria la 00). Por ejemplo en la figura 1.5 se presenta un biestable RS con control (latch, del ingls cerrojo):

Figura 1.5: Biestable RS con control. (*): no estable.

Biestable JK.

El biestable JK (con control tipo latch) parte del elemento anterior, y por medio de una realimentacin adicional consigue evitar la indeterminacin de la combinacin 11, provocando en este caso un cambio de estado. El elemento ms utilizado en la prctica es el denominado biestable JK controlado por flanco o diseo en maestro-esclavo. En la figura 1.6 se muestra el caso de que el flanco de disparo fuera el de bajada ( ).

Figura 1.6: Biestable JK controlado por flanco de bajada (

).

Este tipo de biestables controlados por flanco se disean a partir de dos biestables elementales RS sin entrada de control, conectados en cascada, ms cierta lgica combinacional, como se muestra en la figura 1.7. Uno de los biestables trabaja como maestro, y el otro como esclavo. Cuando CK est a 1, la informacin de entrada pasa al biestable maestro, mientras que el esclavo permanece cerrado, con lo que la salida no sufre variacin. Cuando CK baja a 0 (flanco de bajada), la informacin del maestro pasa al esclavo y se cierra el maestro, con lo cual, los datos que en este instante estn en la entrada no pueden progresar, mientras que los datos que captur el maestro y que ahora se transfieren al esclavo, son los que aparecen a la salida. Cuando CK vuelva a pasar a 1, se cerrar el esclavo con la informacin transferida anteriormente del maestro y que ser la que est presente en la salida, y ste se volver a abrir. Luego la transferencia completa de la informacin, desde la entrada a la salida, slo tendr lugar durante los flancos de bajada de la seal CK.

Figura 1.7: Estructura biestable JK maestro-esclavo.

Biestable D.

El biestable tipo D se suele implementar a partir de un JK. As a partir del JK controlado por flanco de bajada, se puede disear un D controlado por flanco de bajada. En la figura 1.8 se muestra un biestable D junto con su comportamiento.

Figura 1.8: Biestable D controlado por flanco de bajada (

).

Biestable T.

Se disea a partir de un biestable D , realimentando la salida Q a la entrada D. El comportamiento de este biestable se caracteriza porque con cada flanco de reloj cambia (le estado, efecto de la realimentacin introducida.

Figura 1.9: Biestable T controlado por flanco de bajada (

).

Las implementaciones reales de todos estos biestables elementales en MSI buscan bsicamente eficiencia en cuanto al nmero de puertas lgicas y por lo tanto de TRT's que se emplean, pero el principio de diseo es el mismo: realimentacin para atrapar la informacin en el dispositivo.

1.1.2.- Registros.

Un registro es un circuito secuencial sncrono capaz de almacenar varios bits de informacin. El formato de esta informacin puede ser de dos tipos: serie o paralelo. Se dice que el formato es serie cuando los bits se transfieren uno a continuacin del otro por una misma lnea. Por el contrario un formato es paralelo cuando se intercambian todos los bits al mismo tiempo, utilizando un nmero de lneas de transferencia igual al nmero de bits. Atendiendo por tanto al formato de la informacin, los registros se pueden clasificar

en:

- Entrada paralelo, salida paralelo, tambien llamado registro paralelo. - Entrada serie, salidada serie. Son los tambien llamados registros serie o de desplazamiento (o Shift Register), puesto que los bits se desplazan en serie a travs de los biestables. - Entrada serie, salida paralelo. - Entrada paralelo, salida serie.

1.1.3.- Contadores.

Un contador es un circuito secuencial capaz de almacenar, en binario natural o cualquier otro cdigo, el numero de impulsos que recibe por una lnea de entrada. Entre sus aplicaciones ms importantes se encuentran la de divisor de frecuencia (de los impulsos de entrada), control de tiempos, generacin de direcciones en sistemas de memoria o secuenciador en unidades de control. Se emplean tres tipos de estructuras para implementar un contador: - contador asincrono. - contador sincrono. - contador basado en registros de desplazamientos.

1.2.- Funciones de soporte de la informacin. 1.2.1.- Memoria.

Se denomina memoria a todo dispositivo que mantenga constancia de lo ocurrido en el pasado. El elemento bsico de la memoria digital es el biestable, capaz de almacenar un bit. Agrupando biestables se construyen los registros, capaces de almacenar hasta una palabra. Pero en muchas ocasiones se requiere almacenar cientos, miles, millones de palabras. Esta funcin de almacenamiento masivo de informacin la realizan los elementos llamados memorias, que en muchas ocasiones se implementan agrupando registros.

Jerarquas de Memorias.

Los sistemas computadores contienen diversos dispositivos para almacenar las instrucciones y datos que se requieren en su operaclon. Sera deseable que la transferencia entre el procesador y la memoria fuera tal que el procesador operase aproximadamente a su mxima velocidad. Desafortunadamente, las memorias que funcionan a velocidades comparables a las de los procesadores son muy caras. No es viable emplear una nica memoria con un slo tipo de tecnologa. Por eso, la informacin almacenada se distribuye de forma compleja en una variedad de memorias diferentes. La memoria de un sistema computador se puede dividir en tres grupos principales, atendiendo a su jerarqua:

Memoria interna.

Esta constituida por los registros internos de la CPU, y su cometido es el almacenamiento temporal de instrucciones y datos. Se caracteriza por una alta velocidad de funcionamiento y su ubicacin interna en el procesador.

Memoria central (o principal).

Est dedicada al almacenamiento de programas y datos durante el funcionamiento del computador. Se trata de una memoria relativamente grande y rpida. La tecnologa usual utilizada en su construccin es la semiconductora, a partir de circuitos integrados. Incluye las memorias RAM y ROM.

Memoria secundaria.

Se emplea para el almacenamiento de programas del sistema y grandes ficheros. Su capacidad es mucho mayor que las anteriores, aunque es ms lenta y el acceso por parte de la CPU se realiza indirectamente, con la memoria central como elemento intermedio.

1.2.2.- Memorias RAM.

La agrupacin de registros da lugar a estructuras que se suelen denominar RAM (Random Access Memory o memorias de acceso aleatorio), llamadas as puesto que en cualquier momento se puede acceder a cualquiera de sus registros o posiciones, tanto para leer, como para escribir.

1.2.3.- Memorias ROM.

Otro tipo de memorias de acceso aleatorio, pero que slo permiten la lectura y no la escritura son las llamadas ROM (Read Only Memory). El contenido de la memoria es fijo e inalterable y queda fijado en el momento de la fabricacin.

S-ar putea să vă placă și

- Control neuronal y difuso para sistemas fotovoltaicosDe la EverandControl neuronal y difuso para sistemas fotovoltaicosÎncă nu există evaluări

- Sistemas SecuencialesDocument13 paginiSistemas SecuencialesMeliandÎncă nu există evaluări

- Practica Del SemaforoDocument14 paginiPractica Del SemaforoCristian EscobarÎncă nu există evaluări

- GogogogoDocument18 paginiGogogogoJose Angel LeonÎncă nu există evaluări

- Circuitos Combinacionales y SecuancialesDocument39 paginiCircuitos Combinacionales y SecuancialesJosé Miguel AvalosÎncă nu există evaluări

- Basculas Sincronas y AsincronasDocument11 paginiBasculas Sincronas y Asincronastitominas7511Încă nu există evaluări

- Aplicaciones de Los Circuitos SecuencialesDocument6 paginiAplicaciones de Los Circuitos SecuencialesAndy Barraza0% (1)

- Diseo Digital 3Document13 paginiDiseo Digital 3reyna isabel cob gomezÎncă nu există evaluări

- Sistemas Digitales Tema 12Document27 paginiSistemas Digitales Tema 12Dione Huaman Borda100% (1)

- Actividad de Aprendizaje 3. Análisis y Diseño de CircuitosDocument9 paginiActividad de Aprendizaje 3. Análisis y Diseño de CircuitosMiguel ÁngelÎncă nu există evaluări

- Bie StablesDocument18 paginiBie Stableslady67lauraÎncă nu există evaluări

- 03 - Circuitos Digitales (Secuenciales)Document47 pagini03 - Circuitos Digitales (Secuenciales)Juan Manuel AlmironÎncă nu există evaluări

- Cto. SecuencialDocument32 paginiCto. SecuencialAlonso HernándezÎncă nu există evaluări

- Puertas LogicasDocument18 paginiPuertas LogicasBadass OverPowerÎncă nu există evaluări

- 4.4 MultivibradoresDocument33 pagini4.4 MultivibradoresIvanna LemusÎncă nu există evaluări

- Circuitos Logicos SecuencialesDocument17 paginiCircuitos Logicos SecuencialesalfredotoxquiÎncă nu există evaluări

- BiestablesDocument21 paginiBiestablesFRanco FigueroaÎncă nu există evaluări

- Diseño Secuencial MsiDocument36 paginiDiseño Secuencial MsiAldhair AlvarezÎncă nu există evaluări

- Sistemas Electricos y ElectronicosDocument7 paginiSistemas Electricos y ElectronicosCristian LopezÎncă nu există evaluări

- Teoría Circuitos SecuencialesDocument17 paginiTeoría Circuitos SecuencialesLuisma_plasenciaÎncă nu există evaluări

- 10nFORTINOnOPCIRCDIGIT 896363d1a941438Document11 pagini10nFORTINOnOPCIRCDIGIT 896363d1a941438Dayana ArmendárizÎncă nu există evaluări

- Tcedd U3Document8 paginiTcedd U3Hector LopezÎncă nu există evaluări

- Sistemas Secuenciales AsincronosDocument13 paginiSistemas Secuenciales AsincronosCATHERINE RIVAS RODRIGUEZÎncă nu există evaluări

- Documento 70Document4 paginiDocumento 70Angel Emilio RosarioÎncă nu există evaluări

- Circuito Logico Secuenciales-Sistemas DigitalesDocument11 paginiCircuito Logico Secuenciales-Sistemas DigitalesJesusÎncă nu există evaluări

- Sistemas Eléctricos y Electrónicos Tarea 2Document11 paginiSistemas Eléctricos y Electrónicos Tarea 2Cristian LopezÎncă nu există evaluări

- LAB 07 - Aplicaciones Con Flip FlopsDocument9 paginiLAB 07 - Aplicaciones Con Flip FlopsYhojan Kennedy Flores ChipanaÎncă nu există evaluări

- 8-Sistemas Secuenciales SincronosDocument60 pagini8-Sistemas Secuenciales SincronosJose Luis Lobo Lara100% (1)

- Contadores y RegistrosDocument35 paginiContadores y RegistrosDanitza Llanos TorresÎncă nu există evaluări

- I. Resumen Teórico: A) Circuitos SecuencialesDocument24 paginiI. Resumen Teórico: A) Circuitos SecuencialesAnonymous UI7JawqÎncă nu există evaluări

- Flip Flop JKDocument6 paginiFlip Flop JKMigue PicazoÎncă nu există evaluări

- LAB 07 - Aplicaciones Con Flip FlopsDocument9 paginiLAB 07 - Aplicaciones Con Flip FlopsAntony GarambelÎncă nu există evaluări

- Latch's y Flip-FlopDocument21 paginiLatch's y Flip-FlopWilmar Yovany RojasÎncă nu există evaluări

- Sistemas Secuenciales SincronosDocument59 paginiSistemas Secuenciales SincronosCamilo RoncancioÎncă nu există evaluări

- EtcDocument34 paginiEtcSonia JiangÎncă nu există evaluări

- Un Circuito Secuencial Puede Entenderse Simplemente Como Un Circuito Combinacional en El Cuallas Salidas Dependen Tanto de Las Entradas Como de Las Salidas en Instantes AnterioresDocument5 paginiUn Circuito Secuencial Puede Entenderse Simplemente Como Un Circuito Combinacional en El Cuallas Salidas Dependen Tanto de Las Entradas Como de Las Salidas en Instantes AnterioresNeiry FrancoÎncă nu există evaluări

- Unidad 2 - Biestables - ResumenDocument30 paginiUnidad 2 - Biestables - Resumennicolas franco CarrizoÎncă nu există evaluări

- Circuitos SecuencialesDocument5 paginiCircuitos SecuencialesJuan BagurÎncă nu există evaluări

- Diseño SincronoDocument13 paginiDiseño SincronoJosé Luis DelpieroÎncă nu există evaluări

- Electrónica DigitalDocument13 paginiElectrónica DigitalgeorgeÎncă nu există evaluări

- Teoría de Autómatas SincronosDocument23 paginiTeoría de Autómatas SincronosJorge D. NontolÎncă nu există evaluări

- Maquinas de Estados Mealy VHDLDocument20 paginiMaquinas de Estados Mealy VHDLFrancisco Javier Herrera Hernandez60% (5)

- Electrónica Industrial - P8 - 1Document10 paginiElectrónica Industrial - P8 - 1ROCIO DE LOS ANGELES JUAREZ GARCIAÎncă nu există evaluări

- Flip FlopsDocument7 paginiFlip FlopsJuan LainaÎncă nu există evaluări

- Bies TableDocument8 paginiBies TableZarate BismkÎncă nu există evaluări

- Digital TLMXDocument39 paginiDigital TLMXPaul Granados R.Încă nu există evaluări

- UT 03 Analisis de Circuitos Secuenciales by FranDocument11 paginiUT 03 Analisis de Circuitos Secuenciales by FranFrancisco BaenaÎncă nu există evaluări

- Diseño Lògico Secuencial Con VHDLDocument23 paginiDiseño Lògico Secuencial Con VHDLjuanjnv2Încă nu există evaluări

- Diagrama de Estado y Tabla de EstadoDocument9 paginiDiagrama de Estado y Tabla de EstadoErick AlexanderÎncă nu există evaluări

- Trabajo Investigación Tema 4 (N°c.18500311)Document32 paginiTrabajo Investigación Tema 4 (N°c.18500311)Jason ClementeÎncă nu există evaluări

- 6Document8 pagini6Percy Flores MoralesÎncă nu există evaluări

- Evaluacion #2, Electricidad y ElectronicaDocument16 paginiEvaluacion #2, Electricidad y ElectronicaÁlvaro Adrián Bahamonde BahamondeÎncă nu există evaluări

- Circuitos SecuencialesDocument9 paginiCircuitos SecuencialesVitore MorleoneÎncă nu există evaluări

- Equipo 3Document26 paginiEquipo 3Marcos FelixÎncă nu există evaluări

- Unidad 3 - SecuencialesDocument28 paginiUnidad 3 - SecuencialesLoreley DominguezÎncă nu există evaluări

- Circuitos SecuencialesDocument9 paginiCircuitos SecuencialesBryanÎncă nu există evaluări

- AP Divisor de Frecuencia y Máquinas de EstadoDocument8 paginiAP Divisor de Frecuencia y Máquinas de EstadoRonny AuccapiñaÎncă nu există evaluări

- LAB 07 - Aplicaciones Con Flip FlopsDocument11 paginiLAB 07 - Aplicaciones Con Flip Flopsjorge.portugalÎncă nu există evaluări

- Ejercicios de Integrales de Línea, Superficie y VolumenDe la EverandEjercicios de Integrales de Línea, Superficie y VolumenEvaluare: 4 din 5 stele4/5 (2)

- Transformador Trifasico 100kva 22 9cst 0 4kv OnanDocument3 paginiTransformador Trifasico 100kva 22 9cst 0 4kv OnanMiku HatsuneÎncă nu există evaluări

- Patología Del ConcretoDocument10 paginiPatología Del ConcretoJose Francisco Delgado MiteÎncă nu există evaluări

- Actas de Observaciones de Recepcion de Obra La Union Leticia Saneamiento ChiclayoDocument3 paginiActas de Observaciones de Recepcion de Obra La Union Leticia Saneamiento Chiclayonilton cerronÎncă nu există evaluări

- Catalogo Peak Tour 2013 - Equipaje, Mochilas, Porta Laptops, CosmetiquerasDocument40 paginiCatalogo Peak Tour 2013 - Equipaje, Mochilas, Porta Laptops, CosmetiquerasKristophe Al TziganiÎncă nu există evaluări

- PRO - pall.06.REG.20 Formato de Check List EscaleraDocument1 paginăPRO - pall.06.REG.20 Formato de Check List EscaleraALDOÎncă nu există evaluări

- Sesion 1 ECOSISTEMADocument5 paginiSesion 1 ECOSISTEMApatitavdÎncă nu există evaluări

- Atención A La Diversidad Desde La Programación de AulaDocument13 paginiAtención A La Diversidad Desde La Programación de AulaLeti AquinoÎncă nu există evaluări

- Analisis de Las Cadenas Productivas AgroindustrialesDocument25 paginiAnalisis de Las Cadenas Productivas AgroindustrialesRudimar PetterÎncă nu există evaluări

- Xat 2 Awg Cu 15kv t1 NC 100% Rev0 (Px70)Document2 paginiXat 2 Awg Cu 15kv t1 NC 100% Rev0 (Px70)Charity HerreraÎncă nu există evaluări

- Inspeccion Centros de TransformacionDocument6 paginiInspeccion Centros de TransformacionEdward Antonio Hernandez CorredorÎncă nu există evaluări

- La Mente Del Estratega. Kenichi Ohmae. - Dr. Freddy William Castillo PalaciosDocument28 paginiLa Mente Del Estratega. Kenichi Ohmae. - Dr. Freddy William Castillo PalaciosRogers M Gonzalez UÎncă nu există evaluări

- Ficha Técnica de Un AnimalDocument2 paginiFicha Técnica de Un AnimalBrenda Alejandra AlfonzoÎncă nu există evaluări

- Tarea 3 - Informe Estrategias de La Producción - Trabajo - Juan - José - Rojas - Tarea - 3 - 212028 - 10 PDFDocument13 paginiTarea 3 - Informe Estrategias de La Producción - Trabajo - Juan - José - Rojas - Tarea - 3 - 212028 - 10 PDFRojas Juanjose100% (4)

- Manual TC L42e5lDocument80 paginiManual TC L42e5lErick Verastegui OlivaresÎncă nu există evaluări

- Guia para Plan de Protección AmbientalDocument6 paginiGuia para Plan de Protección AmbientalMacarena Andrea FaundezÎncă nu există evaluări

- Édula de Identificación Socioeconómica: SolicitanteDocument4 paginiÉdula de Identificación Socioeconómica: SolicitanteAlan ZambranoÎncă nu există evaluări

- Carretera Culiacan NavolatoDocument14 paginiCarretera Culiacan NavolatoAlejandra GastelumÎncă nu există evaluări

- Bases Maraton Fotografico - 1 3735778 - 20220610223257Document3 paginiBases Maraton Fotografico - 1 3735778 - 20220610223257Beatriz MartínÎncă nu există evaluări

- Caso TrovatoDocument4 paginiCaso Trovatodaniel_paganettiÎncă nu există evaluări

- Ruta de Aprendizaje U1-1ergrado-Comu-S8 PDFDocument9 paginiRuta de Aprendizaje U1-1ergrado-Comu-S8 PDFJorge LopezÎncă nu există evaluări

- Taller - Textos DescriptivosDocument3 paginiTaller - Textos DescriptivosIsrael MadariagaaÎncă nu există evaluări

- Causas de Accidentes en RobotsDocument4 paginiCausas de Accidentes en RobotsThiago Rj100% (1)

- Kaeser - Almacenamiento AireDocument7 paginiKaeser - Almacenamiento AireDiego Resendiz GomezÎncă nu există evaluări

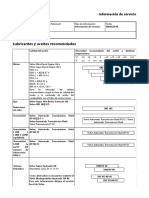

- Lubricantes Volvo L70FDocument2 paginiLubricantes Volvo L70FDiego Gonzalez BuendiaÎncă nu există evaluări

- Manual Javascript PDFDocument121 paginiManual Javascript PDFMario AlbertoÎncă nu există evaluări

- Tasacion de Predio Calle Alto Lima #1286Document5 paginiTasacion de Predio Calle Alto Lima #1286Cesar QAÎncă nu există evaluări

- Cep 20230630 085902218104318138Document1 paginăCep 20230630 085902218104318138FdoÎncă nu există evaluări

- Matriz de Requisitos Legales y ReglamentariosDocument2 paginiMatriz de Requisitos Legales y ReglamentariosIrazi DiazÎncă nu există evaluări

- Etp-009-Identificacion de Instls FijasDocument20 paginiEtp-009-Identificacion de Instls FijasPaola GamasÎncă nu există evaluări

- Guia de RemisionDocument1 paginăGuia de RemisionLeomir GuerraÎncă nu există evaluări