Documente Academic

Documente Profesional

Documente Cultură

HEF4093B

Încărcat de

Fady HachemDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

HEF4093B

Încărcat de

Fady HachemDrepturi de autor:

Formate disponibile

1.

General description

The HEF4093B is a quad two-input NAND gate. Each input has a Schmitt trigger circuit.

The gate switches at different points for positive-going and negative-going signals. The

difference between the positive voltage (V

T+

) and the negative voltage (V

T

) is defined as

hysteresis voltage (V

H

).

It operates over a recommended V

DD

power supply range of 3 V to 15 V referenced to V

SS

(usually ground). Unused inputs must be connected to V

DD

, V

SS

, or another input.

2. Features and benefits

Schmitt trigger input discrimination

Fully static operation

5 V, 10 V, and 15 V parametric ratings

Standardized symmetrical output characteristics

Specified from 40 C to +85 C and 40 C to +125 C

Complies with J EDEC standard J ESD 13-B

3. Applications

Wave and pulse shapers

Astable multivibrators

Monostable multivibrators

4. Ordering information

HEF4093B

Quad 2-input NAND Schmitt trigger

Rev. 8 21 November 2011 Product data sheet

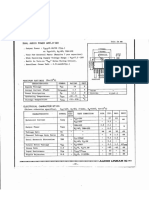

Table 1. Ordering information

All types operate from 40 C to +125 C

Type number Package

Name Description Version

HEF4093BP DIP14 plastic dual in-line package; 14 leads (300 mil) SOT27-1

HEF4093BT SO14 plastic small outline package; 14 leads; body width 3.9 mm SOT108-1

HEF4093B All information provided in this document is subject to legal disclaimers. NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 8 21 November 2011 2 of 15

NXP Semiconductors HEF4093B

Quad 2-input NAND Schmitt trigger

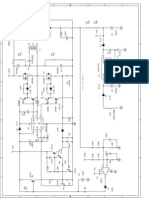

5. Functional diagram

6. Pinning information

6.1 Pinning

Fig 1. Functional diagram Fig 2. Logic diagram (one gate)

001aag104

1

1A

2

1B

5

2A

6

2B

8

3A

9

3B

12

4A

13

4B

3

4

10

11

1Y

2Y

3Y

4Y

001aag105

nA

nB

nY

Fig 3. Pin configuration

HEF4093B

1A V

DD

1B 4B

1Y 4A

2Y 4Y

2A 3Y

2B 3B

V

SS

3A

001aag106

1

2

3

4

5

6

7 8

10

9

12

11

14

13

HEF4093B All information provided in this document is subject to legal disclaimers. NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 8 21 November 2011 3 of 15

NXP Semiconductors HEF4093B

Quad 2-input NAND Schmitt trigger

6.2 Pin description

7. Functional description

[1] H =HIGH voltage level; L =LOW voltage level.

8. Limiting values

[1] For DIP14 packages: above T

amb

=70 C, P

tot

derates linearly with 12 mW/K.

[2] For SO14 packages: above T

amb

=70 C, P

tot

derates linearly with 8 mW/K.

Table 2. Pin description

Symbol Pin Description

1A to 4A 1, 5, 8, 12 input

1B to 4B 2, 6, 9, 13 input

1Y to 4Y 3, 4, 10, 11 output

V

DD

14 supply voltage

V

SS

7 ground (0 V)

Table 3. Function table

[1]

Input Output

nA nB nY

L L H

L H H

H L H

H H L

Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to V

SS

= 0 V (ground).

Symbol Parameter Conditions Min Max Unit

V

DD

supply voltage 0.5 +18 V

I

IK

input clamping current V

I

<0.5 V or V

I

>V

DD

+0.5 V - 10 mA

V

I

input voltage 0.5 V

DD

+0.5 V

I

OK

output clamping current V

O

<0.5 V or V

O

>V

DD

+0.5 V - 10 mA

I

I/O

input/output current - 10 mA

I

DD

supply current - 50 mA

T

stg

storage temperature 65 +150 C

T

amb

ambient temperature 40 +125 C

P

tot

total power dissipation T

amb

=40 C to +125 C

DIP14

[1]

- 750 mW

SO14

[2]

- 500 mW

P power dissipation per output - 100 mW

HEF4093B All information provided in this document is subject to legal disclaimers. NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 8 21 November 2011 4 of 15

NXP Semiconductors HEF4093B

Quad 2-input NAND Schmitt trigger

9. Recommended operating conditions

10. Static characteristics

Table 5. Recommended operating conditions

Symbol Parameter Conditions Min Max Unit

V

DD

supply voltage 3 15 V

V

I

input voltage 0 V

DD

V

T

amb

ambient temperature in free air 40 +125 C

Table 6. Static characteristics

V

SS

= 0 V; V

I

= V

SS

or V

DD

; unless otherwise specified.

Symbol Parameter Conditions V

DD

T

amb

= 40 C T

amb

= +25 C T

amb

= +85 C T

amb

= +125 C Unit

Min Max Min Max Min Max Min Max

V

OH

HIGH-level

output voltage

,I

O

, <1 A 5 V 4.95 - 4.95 - 4.95 - 4.95 - V

10 V 9.95 - 9.95 - 9.95 - 9.95 - V

15 V 14.95 - 14.95 - 14.95 - 14.95 - V

V

OL

LOW-level

output voltage

,I

O

, <1 A 5 V - 0.05 - 0.05 - 0.05 - 0.05 V

10 V - 0.05 - 0.05 - 0.05 - 0.05 V

15 V - 0.05 - 0.05 - 0.05 - 0.05 V

I

OH

HIGH-level

output current

V

O

=2.5 V 5 V - 1.7 - 1.4 - 1.1 - 1.1 mA

V

O

=4.6 V 5 V - 0.64 - 0.5 - 0.36 - 0.36 mA

V

O

=9.5 V 10 V - 1.6 - 1.3 - 0.9 - 0.9 mA

V

O

=13.5V 15 V - 4.2 - 3.4 - 2.4 - 2.4 mA

I

OL

LOW-level

output current

V

O

=0.4 V 5 V 0.64 - 0.5 - 0.36 - 0.36 - mA

V

O

=0.5 V 10 V 1.6 - 1.3 - 0.9 - 0.9 - mA

V

O

=1.5 V 15 V 4.2 - 3.4 - 2.4 - 2.4 - mA

I

I

input leakage

current

15 V - 0.1 - 0.1 - 1.0 - 1.0 A

I

DD

supply current all valid input

combinations;

I

O

=0 A

5 V - 0.25 - 0.25 - 7.5 - 7.5 A

10 V - 0.5 - 0.5 - 15.0 - 15.0 A

15 V - 1.0 - 1.0 - 30.0 - 30.0 A

C

I

input

capacitance

- - - 7.5 - - - - pF

HEF4093B All information provided in this document is subject to legal disclaimers. NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 8 21 November 2011 5 of 15

NXP Semiconductors HEF4093B

Quad 2-input NAND Schmitt trigger

11. Dynamic characteristics

[1] Typical value of the propagation delay and output transition time can be calculated with the extrapolation formula (C

L

in pF).

Table 7. Dynamic characteristics

T

amb

= 25 C; C

L

= 50 pF; t

r

= t

f

s 20 ns; wave forms see Figure 4; test circuit see Figure 5; unless otherwise specified.

Symbol Parameter Conditions V

DD

Extrapolation formula

[1]

Min Typ Max Unit

t

PHL

HIGH to LOW

propagation delay

nA or nB to nY 5 V 63 ns +(0.55 ns/pF)C

L

- 90 185 ns

10 V 29 ns +(0.23 ns/pF)C

L

- 40 80 ns

15 V 22 ns +(0.16 ns/pF)C

L

- 30 60 ns

t

PLH

LOW to HIGH

propagation delay

nA or nB to nY 5 V 58 ns +(0.55 ns/pF)C

L

- 85 170 ns

10 V 29 ns +(0.23 ns/pF)C

L

- 40 80 ns

15 V 22 ns +(0.16 ns/pF)C

L

- 30 60 ns

t

THL

HIGH to LOW output

transition time

nY to LOW 5 V 10 ns +(1.00 ns/pF)C

L

- 60 120 ns

10 V 9 ns +(0.42 ns/pF)C

L

- 30 60 ns

15 V 6 ns +(0.28 ns/pF)C

L

- 20 40 ns

t

TLH

LOW to HIGH output

transition time

nA or nB to

HIGH

5 V 10 ns +(1.00 ns/pF)C

L

- 60 120 ns

10 V 9 ns +(0.42 ns/pF)C

L

- 30 60 ns

15 V 6 ns +(0.28 ns/pF)C

L

- 20 40 ns

Table 8. Dynamic power dissipation

V

SS

= 0 V; t

r

= t

f

s 20 ns; T

amb

= 25 C.

Symbol Parameter V

DD

Typical formula where:

P

D

dynamic power

dissipation

5 V P

D

=1300 f

i

+E(f

o

C

L

) V

DD

2

(W) f

i

=input frequency in MHz;

f

o

=output frequency in MHz;

C

L

=output load capacitance in pF;

E(f

o

C

L

) =sum of the outputs;

V

DD

=supply voltage in V.

10 V P

D

=6400 f

i

+E(f

o

C

L

) V

DD

2

(W)

15 V P

D

=18700 f

i

+E(f

o

C

L

) V

DD

2

(W)

HEF4093B All information provided in this document is subject to legal disclaimers. NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 8 21 November 2011 6 of 15

NXP Semiconductors HEF4093B

Quad 2-input NAND Schmitt trigger

12. Waveforms

Measurement points are given in Table 9.

Logic levels: V

OL

and V

OH

are typical output voltage levels that occur with the output load.

t

r

, t

f

=input rise and fall times.

Fig 4. Propagation delay and output transition time

001aag197

input

output

t

PLH

t

PHL

0 V

V

I

V

M

V

M

V

OH

V

OL

t

TLH

t

THL

90 %

10 %

10 %

90 %

t

r

t

f

Table 9. Measurement points

Supply voltage Input Output

V

DD

V

M

V

M

5 V to 15 V 0.5V

DD

0.5V

DD

Test data given in Table 10.

Definitions for test circuit:

DUT =Device Under Test.

C

L

=load capacitance including jig and probe capacitance.

R

T

=termination resistance should be equal to the output impedance Z

o

of the pulse generator.

Fig 5. Test circuit

V

DD

V

I

V

O

001aag182

DUT

C

L R

T

G

Table 10. Test data

Supply voltage Input Load

V

DD

V

I

t

r

, t

f

C

L

5 V to 15 V V

SS

or V

DD

s 20 ns 50 pF

HEF4093B All information provided in this document is subject to legal disclaimers. NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 8 21 November 2011 7 of 15

NXP Semiconductors HEF4093B

Quad 2-input NAND Schmitt trigger

13. Transfer characteristics

Table 11. Transfer characteristics

V

SS

= 0 V; T

amb

= 25 C; see Figure 6 and Figure 7.

Symbol Parameter Conditions V

DD

Min Typ Max Unit

V

T+

positive-going threshold voltage 5 V 1.9 2.9 3.5 V

10 V 3.6 5.2 7 V

15 V 4.7 7.3 11 V

V

T

negative-going threshold voltage 5 V 1.5 2.2 3.1 V

10 V 3 4.2 6.4 V

15 V 4 6.0 10.3 V

V

H

hysteresis voltage 5 V 0.4 0.7 - V

10 V 0.6 1.0 - V

15 V 0.7 1.3 - V

Fig 6. Transfer characteristic Fig 7. Waveforms showing definition of V

T+

and V

T

(between limits at 30 % and 70 %) and V

H

001aag107

V

O

V

I

V

H

V

T+

V

T 001aag108

V

O

V

I V

H

V

T+

V

T

HEF4093B All information provided in this document is subject to legal disclaimers. NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 8 21 November 2011 8 of 15

NXP Semiconductors HEF4093B

Quad 2-input NAND Schmitt trigger

a. V

DD

=5 V; T

amb

=25 C b. V

DD

=10 V; T

amb

=25 C

c. V

DD

=15 V; T

amb

=25 C

Fig 8. Typical drain current as a function of input

V

I

(V)

0 5 2.5

001aag109

200

100

I

DD

(A)

0

V

I

(V)

0 10 5

001aag110

1000

500

I

DD

(A)

0

V

I

(V)

0 20 10

001aag111

2000

1000

I

DD

(A)

0

HEF4093B All information provided in this document is subject to legal disclaimers. NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 8 21 November 2011 9 of 15

NXP Semiconductors HEF4093B

Quad 2-input NAND Schmitt trigger

14. Application information

Some examples of applications for the HEF4093B are:

Wave and pulse shapers

Astable multivibrators

Monostable multivibrators

If a Schmitt trigger is driven via a high-impedance (R >1 kO), then it is necessary to

incorporate a capacitor C with a value of ; otherwise oscillation can occur

on the edges of a pulse.

C

p

is the external parasitic capacitance between inputs and output; the value depends on

the circuit board layout.

Remark: The two inputs may be connected together, but this will result in a larger

through-current at the moment of switching.

T

amb

=25 C.

Fig 9. Typical switching levels as a function of supply voltage

V

DD

(V)

2.5 17.5 12.5 7.5 5 15 10

001aag112

5

10

V

I

(V)

0

V

T+

V

T

Fig 10. Astable multivibrator Fig 11. Schmitt trigger driven via a

high-impedance input

001aag113

V

DD

V

DD

1

2

3

7

14

C

p

R

C

001aag114

V

DD

V

DD

1

2

3

7

14

C

C

P

------

V

DD

V

SS

V

H

------------------------- >

HEF4093B All information provided in this document is subject to legal disclaimers. NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 8 21 November 2011 10 of 15

NXP Semiconductors HEF4093B

Quad 2-input NAND Schmitt trigger

15. Package outline

Fig 12. Package outline SOT27-1 (DIP14)

UNIT

A

max.

1 2 (1) (1)

b

1

c D

(1)

Z

E e M

H

L

REFERENCES

OUTLINE

VERSION

EUROPEAN

PROJECTION

ISSUE DATE

IEC JEDEC JEITA

mm

inches

DIMENSIONS (inch dimensions are derived from the original mm dimensions)

SOT27-1

99-12-27

03-02-13

A

min.

A

max.

b

max.

w M

E

e

1

1.73

1.13

0.53

0.38

0.36

0.23

19.50

18.55

6.48

6.20

3.60

3.05

0.254 2.54 7.62

8.25

7.80

10.0

8.3

2.2 4.2 0.51 3.2

0.068

0.044

0.021

0.015

0.77

0.73

0.014

0.009

0.26

0.24

0.14

0.12

0.01 0.1 0.3

0.32

0.31

0.39

0.33

0.087 0.17 0.02 0.13

050G04 MO-001 SC-501-14

M

H

c

(e )

1

M

E

A

L

s

e

a

t

i

n

g

p

l

a

n

e

A

1

w M

b

1

e

D

A

2

Z

14

1

8

7

b

E

pin 1 index

0 5 10 mm

scale

Note

1. Plastic or metal protrusions of 0.25 mm (0.01 inch) maximum per side are not included.

DIP14: plastic dual in-line package; 14 leads (300 mil) SOT27-1

HEF4093B All information provided in this document is subject to legal disclaimers. NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 8 21 November 2011 11 of 15

NXP Semiconductors HEF4093B

Quad 2-input NAND Schmitt trigger

Fig 13. Package outline SOT108-1 (SO14)

UNIT

A

max.

A

1

A

2

A

3

b

p

c D

(1)

E

(1) (1)

e H

E

L L

p

Q Z y w v

REFERENCES

OUTLINE

VERSION

EUROPEAN

PROJECTION

ISSUE DATE

IEC JEDEC JEITA

mm

inches

1.75

0.25

0.10

1.45

1.25

0.25

0.49

0.36

0.25

0.19

8.75

8.55

4.0

3.8

1.27

6.2

5.8

0.7

0.6

0.7

0.3

8

0

o

o

0.25 0.1

DIMENSIONS (inch dimensions are derived from the original mm dimensions)

Note

1. Plastic or metal protrusions of 0.15 mm (0.006 inch) maximum per side are not included.

1.0

0.4

SOT108-1

X

w M

A

A

1

A

2

b

p

D

H

E

L

p

Q

detail X

E

Z

e

c

L

v M A

(A )

3

A

7

8

1

14

y

076E06 MS-012

pin 1 index

0.069

0.010

0.004

0.057

0.049

0.01

0.019

0.014

0.0100

0.0075

0.35

0.34

0.16

0.15

0.05

1.05

0.041

0.244

0.228

0.028

0.024

0.028

0.012

0.01

0.25

0.01 0.004

0.039

0.016

99-12-27

03-02-19

0 2.5 5 mm

scale

SO14: plastic small outline package; 14 leads; body width 3.9 mm SOT108-1

HEF4093B All information provided in this document is subject to legal disclaimers. NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 8 21 November 2011 12 of 15

NXP Semiconductors HEF4093B

Quad 2-input NAND Schmitt trigger

16. Revision history

Table 12. Revision history

Document ID Release date Data sheet status Change notice Supersedes

HEF4093B v.8 20111121 Product data sheet - HEF4093B v.7

Modifications: Table 6: I

OH

minimum values changed to maximum

HEF4093B v.7 20100901 Product data sheet - HEF4093B v.6

HEF4093B v.6 20091202 Product data sheet - HEF4093B v.5

HEF4093B v.5 20090728 Product data sheet - HEF4093B v.4

HEF4093B v.4 20080612 Product data sheet - HEF4093B_CNV v.3

HEF4093B_CNV v.3 19950101 Product specification - HEF4093B_CNV v.2

HEF4093B_CNV v.2 19950101 Product specification - -

HEF4093B All information provided in this document is subject to legal disclaimers. NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 8 21 November 2011 13 of 15

NXP Semiconductors HEF4093B

Quad 2-input NAND Schmitt trigger

17. Legal information

17.1 Data sheet status

[1] Please consult the most recently issued document before initiating or completing a design.

[2] The term short data sheet is explained in section Definitions.

[3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status

information is available on the Internet at URL http://www.nxp.com.

17.2 Definitions

Draft The document is a draft version only. The content is still under

internal review and subject to formal approval, which may result in

modifications or additions. NXP Semiconductors does not give any

representations or warranties as to the accuracy or completeness of

information included herein and shall have no liability for the consequences of

use of such information.

Short data sheet A short data sheet is an extract from a full data sheet

with the same product type number(s) and title. A short data sheet is intended

for quick reference only and should not be relied upon to contain detailed and

full information. For detailed and full information see the relevant full data

sheet, which is available on request via the local NXP Semiconductors sales

office. In case of any inconsistency or conflict with the short data sheet, the

full data sheet shall prevail.

Product specification The information and data provided in a Product

data sheet shall define the specification of the product as agreed between

NXP Semiconductors and its customer, unless NXP Semiconductors and

customer have explicitly agreed otherwise in writing. In no event however,

shall an agreement be valid in which the NXP Semiconductors product is

deemed to offer functions and qualities beyond those described in the

Product data sheet.

17.3 Disclaimers

Limited warranty and liability Information in this document is believed to

be accurate and reliable. However, NXP Semiconductors does not give any

representations or warranties, expressed or implied, as to the accuracy or

completeness of such information and shall have no liability for the

consequences of use of such information.

In no event shall NXP Semiconductors be liable for any indirect, incidental,

punitive, special or consequential damages (including - without limitation - lost

profits, lost savings, business interruption, costs related to the removal or

replacement of any products or rework charges) whether or not such

damages are based on tort (including negligence), warranty, breach of

contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason

whatsoever, NXP Semiconductors aggregate and cumulative liability towards

customer for the products described herein shall be limited in accordance

with the Terms and conditions of commercial sale of NXP Semiconductors.

Right to make changes NXP Semiconductors reserves the right to make

changes to information published in this document, including without

limitation specifications and product descriptions, at any time and without

notice. This document supersedes and replaces all information supplied prior

to the publication hereof.

Suitability for use NXP Semiconductors products are not designed,

authorized or warranted to be suitable for use in life support, life-critical or

safety-critical systems or equipment, nor in applications where failure or

malfunction of an NXP Semiconductors product can reasonably be expected

to result in personal injury, death or severe property or environmental

damage. NXP Semiconductors accepts no liability for inclusion and/or use of

NXP Semiconductors products in such equipment or applications and

therefore such inclusion and/or use is at the customers own risk.

Applications Applications that are described herein for any of these

products are for illustrative purposes only. NXP Semiconductors makes no

representation or warranty that such applications will be suitable for the

specified use without further testing or modification.

Customers are responsible for the design and operation of their applications

and products using NXP Semiconductors products, and NXP Semiconductors

accepts no liability for any assistance with applications or customer product

design. It is customers sole responsibility to determine whether the NXP

Semiconductors product is suitable and fit for the customers applications and

products planned, as well as for the planned application and use of

customers third party customer(s). Customers should provide appropriate

design and operating safeguards to minimize the risks associated with their

applications and products.

NXP Semiconductors does not accept any liability related to any default,

damage, costs or problem which is based on any weakness or default in the

customers applications or products, or the application or use by customers

third party customer(s). Customer is responsible for doing all necessary

testing for the customers applications and products using NXP

Semiconductors products in order to avoid a default of the applications and

the products or of the application or use by customers third party

customer(s). NXP does not accept any liability in this respect.

Limiting values Stress above one or more limiting values (as defined in

the Absolute Maximum Ratings System of IEC 60134) will cause permanent

damage to the device. Limiting values are stress ratings only and (proper)

operation of the device at these or any other conditions above those given in

the Recommended operating conditions section (if present) or the

Characteristics sections of this document is not warranted. Constant or

repeated exposure to limiting values will permanently and irreversibly affect

the quality and reliability of the device.

Terms and conditions of commercial sale NXP Semiconductors

products are sold subject to the general terms and conditions of commercial

sale, as published at http://www.nxp.com/profile/terms, unless otherwise

agreed in a valid written individual agreement. In case an individual

agreement is concluded only the terms and conditions of the respective

agreement shall apply. NXP Semiconductors hereby expressly objects to

applying the customers general terms and conditions with regard to the

purchase of NXP Semiconductors products by customer.

No offer to sell or license Nothing in this document may be interpreted or

construed as an offer to sell products that is open for acceptance or the grant,

conveyance or implication of any license under any copyrights, patents or

other industrial or intellectual property rights.

Export control This document as well as the item(s) described herein

may be subject to export control regulations. Export might require a prior

authorization from competent authorities.

Document status

[1][2]

Product status

[3]

Definition

Objective [short] data sheet Development This document contains data from the objective specification for product development.

Preliminary [short] data sheet Qualification This document contains data from the preliminary specification.

Product [short] data sheet Production This document contains the product specification.

HEF4093B All information provided in this document is subject to legal disclaimers. NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 8 21 November 2011 14 of 15

NXP Semiconductors HEF4093B

Quad 2-input NAND Schmitt trigger

Non-automotive qualified products Unless this data sheet expressly

states that this specific NXP Semiconductors product is automotive qualified,

the product is not suitable for automotive use. It is neither qualified nor tested

in accordance with automotive testing or application requirements. NXP

Semiconductors accepts no liability for inclusion and/or use of

non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in

automotive applications to automotive specifications and standards, customer

(a) shall use the product without NXP Semiconductors warranty of the

product for such automotive applications, use and specifications, and (b)

whenever customer uses the product for automotive applications beyond

NXP Semiconductors specifications such use shall be solely at customers

own risk, and (c) customer fully indemnifies NXP Semiconductors for any

liability, damages or failed product claims resulting from customer design and

use of the product for automotive applications beyond NXP Semiconductors

standard warranty and NXP Semiconductors product specifications.

17.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks

are the property of their respective owners.

18. Contact information

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

NXP Semiconductors HEF4093B

Quad 2-input NAND Schmitt trigger

NXP B.V. 2011. All rights reserved.

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 21 November 2011

Document identifier: HEF4093B

Please be aware that important notices concerning this document and the product(s)

described herein, have been included in section Legal information.

19. Contents

1 General description . . . . . . . . . . . . . . . . . . . . . . 1

2 Features and benefits . . . . . . . . . . . . . . . . . . . . 1

3 Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

4 Ordering information . . . . . . . . . . . . . . . . . . . . . 1

5 Functional diagram . . . . . . . . . . . . . . . . . . . . . . 2

6 Pinning information . . . . . . . . . . . . . . . . . . . . . . 2

6.1 Pinning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

6.2 Pin description . . . . . . . . . . . . . . . . . . . . . . . . . 3

7 Functional description . . . . . . . . . . . . . . . . . . . 3

8 Limiting values. . . . . . . . . . . . . . . . . . . . . . . . . . 3

9 Recommended operating conditions. . . . . . . . 4

10 Static characteristics . . . . . . . . . . . . . . . . . . . . . 4

11 Dynamic characteristics . . . . . . . . . . . . . . . . . . 5

12 Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

13 Transfer characteristics . . . . . . . . . . . . . . . . . . 7

14 Application information. . . . . . . . . . . . . . . . . . . 9

15 Package outline . . . . . . . . . . . . . . . . . . . . . . . . 10

16 Revision history . . . . . . . . . . . . . . . . . . . . . . . . 12

17 Legal information. . . . . . . . . . . . . . . . . . . . . . . 13

17.1 Data sheet status . . . . . . . . . . . . . . . . . . . . . . 13

17.2 Definitions. . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

17.3 Disclaimers. . . . . . . . . . . . . . . . . . . . . . . . . . . 13

17.4 Trademarks. . . . . . . . . . . . . . . . . . . . . . . . . . . 14

18 Contact information. . . . . . . . . . . . . . . . . . . . . 14

19 Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

S-ar putea să vă placă și

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- Androgen DeprivationDocument8 paginiAndrogen DeprivationFady HachemÎncă nu există evaluări

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5795)

- DC DC Converter BOMDocument1 paginăDC DC Converter BOMFady HachemÎncă nu există evaluări

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- An920 DDocument40 paginiAn920 DFady HachemÎncă nu există evaluări

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- TA7230PDocument4 paginiTA7230PFady HachemÎncă nu există evaluări

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (588)

- AN954Document14 paginiAN954Fady HachemÎncă nu există evaluări

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (74)

- BD438Document5 paginiBD438Fady HachemÎncă nu există evaluări

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- Application Note AN4105Document23 paginiApplication Note AN4105Fady HachemÎncă nu există evaluări

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (895)

- 2N60 PDFDocument7 pagini2N60 PDFFady HachemÎncă nu există evaluări

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- Prot BRD CMDocument1 paginăProt BRD CMFady HachemÎncă nu există evaluări

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (400)

- Very Good: L 535.9 H The Core Is..Document1 paginăVery Good: L 535.9 H The Core Is..Fady HachemÎncă nu există evaluări

- Ir 21531Document1 paginăIr 21531Fady HachemÎncă nu există evaluări

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (345)

- Fly Back ConverterDocument1 paginăFly Back ConverterFady HachemÎncă nu există evaluări

- Smps v2.1 SCHDocument1 paginăSmps v2.1 SCHFady Hachem0% (1)

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- Byv52 200Document7 paginiByv52 200Fady HachemÎncă nu există evaluări

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- SMPS SchematicDocument1 paginăSMPS SchematicFady HachemÎncă nu există evaluări

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2259)

- Application Note AN4105Document23 paginiApplication Note AN4105Fady HachemÎncă nu există evaluări

- Plagiarism Scan Report: Plagiarism Unique Plagiarized Sentences Unique SentencesDocument2 paginiPlagiarism Scan Report: Plagiarism Unique Plagiarized Sentences Unique Sentencesshreya100% (1)

- Akamai Performance Matters Key Consumer Insights EbookDocument32 paginiAkamai Performance Matters Key Consumer Insights EbookAnand SeshadriÎncă nu există evaluări

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (266)

- 2015 - Jan Meeting - SAP GRC Access Control Framework - Sangram DashDocument15 pagini2015 - Jan Meeting - SAP GRC Access Control Framework - Sangram Dashvgudi7Încă nu există evaluări

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- Search WaterDocument2 paginiSearch WaterThinkDefenceÎncă nu există evaluări

- Printed Circuit Board Manufacturing ProcessDocument2 paginiPrinted Circuit Board Manufacturing ProcessDipesh AggarwalÎncă nu există evaluări

- AAL-ICQCC-2021, Team PragathiDocument42 paginiAAL-ICQCC-2021, Team PragathiAnirudh Shenoy KÎncă nu există evaluări

- Enhancements List RVT 2015 UR5 ForR2Document6 paginiEnhancements List RVT 2015 UR5 ForR2Luca BrandiÎncă nu există evaluări

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- Unit I Management Information Systems (MIS) : Other NamesDocument6 paginiUnit I Management Information Systems (MIS) : Other Namesfelix777sÎncă nu există evaluări

- WEDDING RATE - Felfest UI - 2019 PDFDocument2 paginiWEDDING RATE - Felfest UI - 2019 PDFNurulWardhani11Încă nu există evaluări

- FB6 VV 2 KV SKCQZACdDocument14 paginiFB6 VV 2 KV SKCQZACdpranablahon42Încă nu există evaluări

- Republic of Indonesia Ministry of Transportation: Moored Balloons, Kites, Unmanned Rockets and Unmanned Free BalloonsDocument12 paginiRepublic of Indonesia Ministry of Transportation: Moored Balloons, Kites, Unmanned Rockets and Unmanned Free BalloonsastriwiditakÎncă nu există evaluări

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (121)

- Elevator Shaft VentilationDocument2 paginiElevator Shaft VentilationRachel Dollison100% (2)

- Mitutoyo - Katalog USA-1005Document580 paginiMitutoyo - Katalog USA-1005D.T.Încă nu există evaluări

- Innovating High Availability With Cluster Shared VolumesDocument44 paginiInnovating High Availability With Cluster Shared Volumesgoldseeva1Încă nu există evaluări

- CV EngDocument1 paginăCV EngViktor HeÎncă nu există evaluări

- Backup LogDocument82 paginiBackup Logนิด นิตาÎncă nu există evaluări

- Tyler Scott - Professional PortfolioDocument7 paginiTyler Scott - Professional Portfolioapi-266320901Încă nu există evaluări

- Sport KingDocument7 paginiSport KingPoorti GargÎncă nu există evaluări

- 255.woodworking IndustryDocument7 pagini255.woodworking IndustryGian Luca Riva RiquelmeÎncă nu există evaluări

- Design TransferDocument5 paginiDesign Transferazamyn100% (2)

- Apqp (Concept Explanation)Document6 paginiApqp (Concept Explanation)mierulsÎncă nu există evaluări

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- Portable Appliance Testing: Safety Guide 12Document20 paginiPortable Appliance Testing: Safety Guide 12Keith1186Încă nu există evaluări

- Handbook Oxford OM PDFDocument27 paginiHandbook Oxford OM PDFSantiago RobledoÎncă nu există evaluări

- Brochure Service Offer For Generators 2915825200 English PDFDocument12 paginiBrochure Service Offer For Generators 2915825200 English PDFLuis Alberto Perez ParedesÎncă nu există evaluări

- Working Method For Piping Installation - Add Method For Boom Lift 227KgDocument58 paginiWorking Method For Piping Installation - Add Method For Boom Lift 227KgPhát NguyễnÎncă nu există evaluări

- Franchising Vs LicensingDocument29 paginiFranchising Vs LicensingMarcela Bumbu-Cervinschi100% (1)

- Item Item Description Market Price: Classification: InternalDocument3 paginiItem Item Description Market Price: Classification: InternalHesham TaherÎncă nu există evaluări

- 650COMP 09 Rev01FAADocument56 pagini650COMP 09 Rev01FAAlalo7772100% (1)

- e-GMAT+ Applicant Lab - RESUME WRITING WebinarDocument51 paginie-GMAT+ Applicant Lab - RESUME WRITING WebinarRonBÎncă nu există evaluări

- Seminar On Split Cavity MouldDocument43 paginiSeminar On Split Cavity MouldasgrutuÎncă nu există evaluări