Documente Academic

Documente Profesional

Documente Cultură

UNIT1

Încărcat de

Azliana Mohd TaibDescriere originală:

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

UNIT1

Încărcat de

Azliana Mohd TaibDrepturi de autor:

Formate disponibile

SEQUENTIAL LOGIC

E2064/1/1

Unit 1

SEQUENTIAL LOGIC

E2064/1/2

UNIT 1

Sequential Logic

OBJECTIVES

General Objective

Know and apply the type of the flip-flops, truth table, symbols, and timing diagram of the flip-flops.

Specific Objectives

At the end of this unit, you should be able to:

construct the SR flip-flop by using NOR gate and NAND gate. draw the symbol and create a truth table for SR flip-flop. draw the timing diagram for the SR flip-flop and sketch the output for this flip-flop. draw the symbol; create a truth table and timing diagram for the clocked SR flip-flop. draw clocked SR flip-flop with Preset and Clear control input. draw the symbol, truth table and timing diagram for clocked SR flip-flop. draw the symbol, truth table and timing diagram for JK, T and D flip-flop. construct a T and a D flip-flop using a JK flip-flop. draw the symbol, truth table and timing diagram for MASTER/SLAVE JK flip-flop. state the applications of JK flip-flop, T flip-flop and D flip-flop.

SEQUENTIAL LOGIC

E2064/1/3

INPUT INPUT

1.0 INTRODUCTION

Sequential logic is a form of binary circuit design that employs one or more inputs and one or more outputs, whose states are related by defined rules that depend, in part, on previous states. Each of the inputs and output(s) can attain either of two states: logic 0 (low) or logic 1 (high). A common example of a circuit employing sequential logic is the flip-flop, also called a bistable gate. A simple flip-flop has two stable states. The flip-flop maintains its states indefinitely until an input pulse called a trigger is received. If a trigger is received, the flip-flop outputs change their states according to defined rules, and remain in those states until another trigger is received. There are several different kinds of flip-flop circuits, with designators such as D, T, J-K, and R-S. Flip-flop circuits are interconnected to form the logic gates that comprise digital integrated circuits (ICs) such as memory chips and microprocessors. Sequential logic differs from combinational logic. In the latter scheme, the output states depend only on the input states at a specific moment in time, and not on previous states.

SEQUENTIAL LOGIC

E2064/1/4

1.1 Basic Flip-flop circuit

A flip-flop circuit can be constructed from two NAND gates or NOR gates. These flip-flops are shown in Figure 1.1 and Figure 1.3. Each flip-flop has two outputs, Q and

Q

, and two inputs, Set and Reset. This type of flip-flop is = 0, it is in set state (or logic 1). When Q= 0,

Q

referred to as an SR flip-flop or SR latch. The flip-flop in Figure 1.1 has two useful states. When Q= 1 and and

Q Q

= 1, it is in clear state. The outputs Q and

are complements of each

other and are referred to as the normal and complement outputs respectively. The binary state of the flip-flop is taken to be the value of the normal output. When logic 1 is applied to both of the set and reset inputs in Figure 1.1, both Q and

Q

outputs go to logic 0. This condition violates the fact that both

outputs are complements of each other. In normal operation this condition must be avoided by making sure that 1s are not applied to both inputs simultaneously.

R (re s e t )

S (s e t ) Figure 1.1: NOR gate SR latch

S 0 0 1 1

R Q 0 0 1 0 0 1 1 1

1 1 0 1

OPERATION No change Reset Set Invalid

SEQUENTIAL LOGIC

E2064/1/5

Table 1.1: Truth table for NOR gate SR latch

SEQUENTIAL LOGIC

E2064/1/6

SET

RESET

Q Invalid

Figure 1.2: Timing diagram of NOR gate SR latch

S (s e t )

R (re s e t ) Figure 1.3: NAND gate SR latch

S 0 0 1 1

R Q 0 1 1 1 0 0 1 0

1 0 1 1

OPERATION Invalid Set Reset No change

Table 1.2: Truth table for NAND gate SR latch

SET

RESET

Q Invalid

Figure 1.4: Timing diagram of NAND gate SR latch

The NAND basic flip-flop circuit in Figure 1.3 operates with inputs normally at 1 unless the state of the flip-flop has to be changed. A logic 0 applied

SEQUENTIAL LOGIC

E2064/1/7

momentarily to the set input causes Q go to logic 1 and

to logic 0, putting

the flip-flop in the set state. When both inputs go to logic 0, both outputs go to logic 1. This condition should be avoided in normal operation.

1.2 Clocked SR Flip-Flop

Two different methods for constructing a SR flip-flop were discussed in section 1.1. The addition of two AND gates at the S and R inputs as shown in Figure 1.5 will result in a flip-flop that can be enabled or disabled. When the ENABLE input is low, the AND gate outputs must both be low and changes in neither S nor R will have any effect on the flip-flop output Q. The clocked SR flip-flop shown in Figure 1.5 consists of a basic NOR flipflop and two AND gates. The outputs of the two AND gates remain at logic 0 as long as the clock pulse (or CP) is logic 0, regardless of the S and R input values. When the clock pulse goes to logic 1, information from the S and R inputs passes through to the basic flip-flop. With both S= 1 and R= 1, the occurrence of a clock pulse causes both outputs to momentarily go to logic 0. When the clock pulse is removed, the state of the flip-flop is indeterminate, i.e., either state may result, depending on whether the set or reset input of the flip-flop remains logic 1 longer than the transition to logic 0 at the end of the pulse.

R (re s e t ) Q

C P

( c lo c k p u ls e )

S (s e t ) Figure 1.5: Logic circuit of clocked SR Flip-flop

SEQUENTIAL LOGIC

E2064/1/8

Q 0 0 0 0 1 1 1 1

S 0 0 1 1 0 0 1 1

R Q(t+1) 0 0 1 0 0 1 1 Invalid 0 1 1 0 0 1 1 Invalid

Table 1.3: Truth table for the clocked SR flip-flop

Example 1.1 Determine the Q and output waveforms of the flip-flop in figure (a) below for

the S, R, and CLK inputs in figure (b). Assume that the positive edge-triggered flip-flop is initially RESET.

(a)

SEQUENTIAL LOGIC

E2064/1/9

Solution to Example 1.1 1. 2. 3. 4. 5. 6. At clock pulse 1, S is LOW and R is LOW, so Q does not change. At clock pulse 2, S is LOW and R is HIGH, so Q remains LOW (RESET). At clock pulse 3, S is HIGH and R is LOW, so Q goes HIGH (SET). At clock pulse 4, S is LOW and R is HIGH, so Q goes LOW (RESET). At clock pulse 5, S is HIGH and R is LOW, so Q goes HIGH (SET). At clock pulse 6, S is HIGH and R is LOW, so Q stays HIGH. is easily found since it is simply the complement of Q.

Q

Once Q is determined,

The resulting waveforms for Q and waveforms in figure (b).

are shown in figure (c) for the input

1.3 Clocked SR Flip-flop with Preset and Clear Input Control

Most integrated circuit flip-flops also have asynchronous inputs. These are inputs that affect the state of the flip-flop independent of the clock. They are normally labeled preset (PRE) and clear (CLR). An active level on the preset input will SET the flip-flop, and an active level on the clear input will RESET it. A logic symbol for a SR flip-flop with preset and clear inputs is shown in Figure 1.6. These inputs are active-LOW, as indicated by the bubbles. These preset and clear inputs must both be kept HIGH for synchronous operation.

PRE

S R

Q Q

C LR

Figure 1.6: Logic symbol of the SR flip-flop with Preset and Clear input control

SEQUENTIAL LOGIC

E2064/1/10

Input Output Asynchronous Synchronous Mode Preset Clear S R CLK Q (t+1) Asynchronous set 0 1 x x x 1 Asynchronous reset 1 0 x x x 0 No change 1 1 0 0 1 No change Reset 1 1 0 1 1 0 Set 1 1 1 0 1 1 Invalid 1 1 1 1 1 Invalid

Table 1.4: Truth table for active-LOW SR flip-flop with Preset and Clear input control

P re s e t C le a r

In v a lid

Figure 1.7: Timing diagram of the SR flip-flop

The highest reward for a mans toil is not what he gets for it, but The highest reward for a mans toil is not what he gets for it, but when he becomes by it. when he becomes by it. - John Ruskin - John Ruskin

SEQUENTIAL LOGIC

E2064/1/11

SEQUENTIAL LOGIC

E2064/1/12

Activity 1A

TEST YOUR UNDERSTANDING BY ANSWERING THE FOLLOWING QUESTIONS. 1.1 If an SR latch has a 1 on the S input and a 0 on the R input and then the S input goes to 0, the latch will be (a) set 1.2 (b) reset (c) invalid (d) clear

The invalid state of an SR latch occurs when (a) S= 1, R= 0 (c) S= 1, R= 1 (b) S=0, R= 1 (d) S= 0, R= 0

1.3

The purpose of the clock input to a flip-flop is to (a) clear the device (b) set the device

(c) always cause the output change states (d) cause the output to assume a state dependent on the controlling inputs.

SEQUENTIAL LOGIC

E2064/1/13

1.4

Develop the truth table for the active-HIGH input SR latch in figure below.

R (re s e t ) Q

S (s e t )

1.5

How does a JK flip-flop differ from an SR flip-flop in its basic operation?

SEQUENTIAL LOGIC

E2064/1/14

Feedback To Activity 1A

1.1 1.2 1.3

(a) (c) (d) S 0 0 1 1 R Q 0 0 1 0 0 1 1 1

Q

1 1 0 1

OPERATION No change Reset Set Invalid

1.4

1.5

The JK flip-flop does not have an invalid state as compared to the SR flip-flop.

SEQUENTIAL LOGIC

E2064/1/15

INPUT INPUT

1.4 JK Flip-flop

A JK flip-flop is a refinement of the SR flip-flop in that the indeterminate state of the SR type is defined in the JK type. Inputs J and K behave like inputs S and R to set and clear the flip-flop (note that in a JK flip-flop, the letter J is for set and the letter K is for clear). When logic 1 inputs are applied to both J and K simultaneously, the flip-flop switches to its complement state, i.e., if Q=1, it switches to Q= 0 and vice versa. A clocked JK flip-flop is shown in Figure 1.8. Output Q is ANDed with K and CP inputs so that the flip-flop is cleared during a clock pulse only if Q was previously 1. Similarly, output

Q

is ANDed with J and CP inputs so that the flipQ

flop is set with a clock pulse only if

was previously 1.

Note that because of the feedback connection in the JK flip-flop, a CP signal which remains a 1 (while J = K = 1) after the outputs have been complemented once will cause repeated and continuous transitions of the outputs. To avoid this, the clock pulses must have time duration less than the propagation delay through the flip-flop. The restriction on the pulse width can be eliminated with a master-slave or edge-triggered construction.

SEQUENTIAL LOGIC

E2064/1/16

K

C P

Figure 1.8: Logic circuit of the JK flip-flop

J

C P

Q Q

Figure 1.9: Logic symbol of the JK flip-flop

Q 0 0 0 0 1 1 1 1

J 0 0 1 1 0 0 1 1

K 0 1 0 1 0 1 0 1

Q (t+1) 0 0 1 1 1 0 1 0

Table 1.5: Truth table for the clocked JK flip-flop

C LK

Figure 1.10: Timing diagram of the JK flip-flop

SEQUENTIAL LOGIC

E2064/1/17

Example 1.2 The waveforms in figure (a) below are applied to the J, K, and clock inputs are indicated. Determine the Q output, assuming that the flip-flop is initially RESET.

Solution to Example 1.2

SEQUENTIAL LOGIC

E2064/1/18

1. First, since this is a negative edge-triggered flip-flop, as indicated by the bubble at the clock input, the Q output will change only on the negativegoing edge of the clock pulse. 2. At the first clock pulse, both J and K are HIGH; and because this is a toggle condition, Q goes HIGH. 3. At clock pulse 2, a no-change condition exists on the inputs, keeping Q at a HIGH level. 4. When clock pulse 3 occurs, J is LOW and K is HIGH, resulting in a RESET condition; Q goes LOW. 5. At clock pulse 4, J is HIGH and K is LOW, resulting in a SET condition; Q goes HIGH. 6. A SET condition still exists on J and K when clock pulse 5 occurs, so Q will remain HIGH. The resulting Q waveform is indicated in figure (b).

SEQUENTIAL LOGIC

E2064/1/19

1.5 T Flip-Flop

The toggle, or T, flip-flop is a bistable device that changes state on command from a common input terminal. The standard symbol for a T FF is illustrated in Figure 1.11. The T input may be preceded by an inverter. An inverter indicates a FF will toggle on a HIGH-to-LOW transition of the input pulse. The absence of an inverter indicates the FF will toggle on a LOW-to-HIGH transition of the pulse. The most commonly used T FFs are J-K FFs wired to perform a toggle function as shown in Figure 1.12.

T

Q Q

J K

Q Q

C LK

Figure 1.11: Logic symbol of the T flip-flop

T

C P

Figure 1.12: Logic circuit of the T flip-flop

SEQUENTIAL LOGIC

E2064/1/20

Q 0 0 1 1

T 0 1 0 1

Q (t+1) 0 1 1 0

Table 1.6: Truth table for the T flip-flop

The timing diagram in Figure 1.13 shows the toggle input and the resulting outputs. We will assume an initial condition (T0) of Q being LOW and Q being HIGH. At T1, the toggle changes from a LOW to a HIGH and the device changes state; Q goes HIGH and Q goes LOW. The outputs remain the same at T 2 since the device is switched only by a LOW-to-HIGH transition. At T 3, when the toggle goes HIGH, Q goes LOW and Q goes HIGH; they remain that way until T 5.

Figure 1.13: Timing diagram of T flip-flop

SEQUENTIAL LOGIC

E2064/1/21

Between T1 and T5, two complete cycles of T occur. During the same time period, only one cycle is observed for Q or Q. Since the output cycle is one-half the input cycle, this device can be used to divide the input by 2.

1.6 D Flip-Flop

The D FF is a two-input FF. The inputs are the data (D) input and a clock (CLK) input. The clock is a timing pulse generated by the equipment to control operations. The D FF is used to store data at a predetermined time and hold it until it is needed. This circuit is sometimes called a delay FF. In other words, the data input is delayed up to one clock pulse before it is seen in the output. The D flip-flop shown in Figure 1.14 is a modification of the clocked SR flip-flop. The D input goes directly into the S input and the complement of the D input goes to the R input. The D input is sampled during the occurrence of a clock pulse. If it is 1, the flip-flop is switched to the set state (unless it was already set). If it is 0, the flip-flop switches to the clear state.

D Q

C P

( c lo c k p u ls e )

Figure 1.14: Logic circuit of the D flip-flop

CLK

Q Q

C P

J K

Q Q

Figure 1.15: Logic symbol of the D flip-flop

CLK 0 0

D Q Operation 1 0 start 1 1 store 1 0 Q no change 0 0 store 0

SEQUENTIAL LOGIC

E2064/1/22

Depending on the circuit design, the clock (CLK) can be a square wave, a constant frequency, or asymmetrical pulses. In this example the clock (CLK) input will be a constant input at a given frequency. This frequency is determined by the control unit of the equipment. The data (D) input will be present when there is a need to store information. Notice in the Truth Table that output Q reflects the D input only when the clock transitions from 0 to 1 (LOW to HIGH). Let's assume that at T0, CLK is 0, D is 1, and Q is 0. Input D remains at 1 for approximately 2 clock pulses. At T1, when the clock goes to 1, Q also goes to 1 and remains at 1 even though D goes to 0 between T 2 and T3. At T3, the positive-going pulse of the clock causes Q to go to 0, reflecting the condition of D. The positive-going clock pulse at T5 causes no change in the output because D is still LOW. Between T5 and T6, D goes HIGH, but Q remains LOW until T7 when the clock goes HIGH.

Table 1.7: Truth table for the D flip-flop

Figure 1.16: Timing diagram of D flip-flop

The key to understand the output of the D FF is to remember that the data (D) input is seen in the output only after the clock has gone HIGH.

SEQUENTIAL LOGIC

E2064/1/23

1.7 Master/Slave JK Flip-flop

Another class of flip-flop is the master/slave. Although this type of flip-flop has largely been replaced by the edge-triggered devices, a limited selection is still available from IC manufacturers and you may encounter this type of flip-flop in some existing equipment. The logic symbol of master/slave JK flip-flop is shown Figure 1.17. The truth table operation is the same as that for the edge-triggered JK flip-flop except for the way it is clocked. Internally, though, it is different. This type of flip-flop is composed of two sections, the master section and the slave section. The master section is basically a gated latch, and the slave section is the same except that it is clocked on the inverted clock pulse and is controlled by the outputs of the master section rather than by the external JK inputs.

PR E

J

C LK

Q Q

C LR

Figure 1.17: Circuit diagram and logic symbol of master/slave JK flip-flop

SEQUENTIAL LOGIC

E2064/1/24

Any input to the master-slave flip-flop at J and K is first seen by the master FF part of the circuit while CLK is High (=1). This behavior effectively "locks" the input into the master FF. An important feature here is that the complement of the CLK pulse is fed to the slave FF. Therefore the outputs from the master FF are only "seen" by the slave FF when CLK is Low (=0). Therefore on the High-to-Low CLK transition the outputs of the master are fed through the slave FF. This means that the at most one change of state can occur when J= K= 1 and so oscillation between the states Q= 0 and Q= 1 at successive CLK pulses does not occur. Inputs Outputs Operations K CLK Q Q 0 1 Q0 Q 0 No change 1 1 0 1 Reset 0 1 1 0 Set 1 1 Q 0 Q0 Toggle

J 0 0 1 1

C L KTable 1.8: Truth table for the master/slave JK flip-flop J

Figure 1.18: Timing diagram of master/slave JK flip-flop

SEQUENTIAL LOGIC

E2064/1/25

1.8 Applications

In this section, several general applications of flip-flops are discussed to give you a basic idea of how they can be used. In Unit 2 and 3 there are detailed coverage of flip-flop applications in counters and registers.

1.8.1 Counting

A common application of flip-flops is in digital counter, which is covered in detailed in next unit. The concept is illustrated in Figure 1.19. The flip-flops are negative edge-triggered JKs. Both flip-flops are initially Reset. Flip-flop A toggles on the negative-going transition of each clock pulse. The Q output of flip-flop A clocks flip-flop B, so each time QA makes a HIGH-to-LOW transition, flip-flop B toggles. The resulting QA and QB waveforms are shown in the Figure 1.20. Observe the sequence of QA and QB in Figure 1.19. Prior to clock pulse 1, QA= 0 and QB= 0; after clock pulse 1, QA= 1 and QB= 0; after clock pulse 2, QA= 0 and QB= 1; and after clock pulse 3, QA= 1 and QB= 1. If we take QA as the least significant bit, a 2-bitbinary sequence is produced as the flip-flops are clocked. This binary sequence repeats every four clock pulses, as shown in the timing diagram of Figure 1.20. Thus, the flip-flops are counting in sequence from 0 to 3 (00,01,10,11) and then recycling back to 0 to begin the sequence again.

Q

H IG H A

J

CLK

Q Q

J K

Q Q

F lip -flo p A

F lip -flo p B

Figure 1.19: Flip-flops used to generate a binary count sequence. Two repetitions (00, 01, 10, 11) are shown.

SEQUENTIAL LOGIC

E2064/1/26

C L K

Q A

Q B

0 0

0 1

1 0

1 1

0 0

0 1

1 0

1 1

Binary sequence

Binary sequence

Figure 1.20: Timing diagram of a 2-bit counter

1.8.2 Frequency Division

Another application of a flip-flop is dividing (reducing) the frequency of a periodic waveform. When a pulse waveform is applied to the clock input of a T flip-flop that is connected to HIGH (T= 1), the Q output is a square wave with one-half the frequency of the clock input. Thus, a single flip-flop can be applied as a divide-by-2 device, as is illustrated in Figure 1.21. As you can see, the flipflop changes state on each triggering clock edge (positive edge-triggered in this case). This results in an output that changes at half the frequency of the clock waveform.

H IG H

Q Q

CLK

Figure 1.21: The T flip-flop as a divide-by-2 device

SEQUENTIAL LOGIC

E2064/1/27

C LK

Figure 1.22: Timing diagram of the 1-bit frequency divider

Example 1.3 Develop the f out waveform for the circuit in figure below when an 8kHz square wave input is applied to the clock input of flip-flop A.

Solution to Example 1.3 The three flip-flops are connected to divide the input frequency by eight ( 2 3 = 8) and the f out waveform is shown in figure below. Since these are positive edgetriggered flip-flops, the outputs change on the positive-going clock edge. There is one output pulse for every eight input pulses, so the output frequency is 1kHz. Waveforms of Q A and Q B are also shown.

SEQUENTIAL LOGIC

E2064/1/28

1.8.3 Parallel Data Storage

Another important application of flip-flops in digital systems is to store several bits of data from parallel lines simultaneously in a group of flip-flops. This operation is illustrated in Figure 1.23 using three flip-flops. Each of the three parallel data lines is connected to the D input of a flip-flop. The clock inputs of the flip-flops are connected together, so that each flip-flop is triggered by the same clock pulse. In this example, positive edge-triggered flip-flops are used, so the data on the D inputs are stored simultaneously by the flip-flops on the positive edge of the clock, as indicated in the timing diagram in Figure 1.24. We assume all the flip-flops are initially resets.

D D

D

C LK

D

D Q Q

Q Q

Q Q

Figure 1.23: Circuit of a basic register for parallel data storage

C LK

Q Q Q

Initial condition

Data stored

Figure 1.24: Timing diagram of a basic register

SEQUENTIAL LOGIC

E2064/1/29

This group of three flip-flops is an example of a basic register used for data storage. In digital systems, data are normally stored in groups of bits that represent numbers, codes, or other information. Registers are covered in detail in Unit 3.

The virtue of all achievements is victory over oneself. Those who The virtue of all achievements is victory over oneself. Those who know this can never know defeat know this can never know defeat - A.J. Cronin - A.J. Cronin

SEQUENTIAL LOGIC

E2064/1/30

Activity 1B

LETS TRY TO ANSWER THE QUESTIONS BELOW..! 1.6 A feature that distinguishes the JK flip-flop from the SR flip-flop is the (a) toggle condition (c) type of clock 1.7 (b) preset input (d) clear input

A flip-flop is in the toggle condition when (a) J= 1, K= 0 (c) J= 0, K= 0 (b) J=0, K= 1 (d) J= 0, K= 1

1.8

For an edge-triggered D flip-flop, (a) a change in the state of the flip-flop can occur only at a clock pulse edge (b) the state that the flip-flop goes to depends on the D input (c) the output follows the input at each clock pulse (d) all of these answers.

SEQUENTIAL LOGIC

E2064/1/31

1.9

Describe the basic difference between pulse-triggered and edge-triggered flip-flops.

1.10

Suppose that the D input of a flip-flop changes from LOW to HIGH in the middle of a positive-going clock pulse. i. ii. Describe what happens if the flip-flop is a positive edge-triggered type. Describe what happens if the flip-flop is a pulse-triggered master/slave type.

SEQUENTIAL LOGIC

E2064/1/32

Feedback To Activity 1B

1.6 1.7 1.8 1.9

(a) (b) (d) In the pulse-triggered flip-flop (master/slave), a data bit goes into the master section on the leading edge of a clock pulse and is transferred to the output (slave) on the trailing edge. In the edge-triggered flip-flop, a data bit goes into the flip-flop and appears on the output on the same clock edge.

1.10

(a) Nothing happens for the positive edge-triggered flip-flop. (b) The output of a of a pulse-triggered master/slave flip-flop will change.

SEQUENTIAL LOGIC

E2064/1/33

KEY FACTS

1. A NAND latch and a NOR latch are simple flip-flops that respond to logic levels on their SET and CLEAR inputs. 2. Clearing (resetting) a flip-flop means that its output ends up in the Q= 0 /

Q

= 1 state. Setting a flip-flop means that it ends up in the Q= 1 /

=0

state. 3. Clocked flip-flops have a clock input (CLK, CP, CK ) that is edge-triggered, meaning that it triggers the flip-flop on a positive-going transition (PGT) or a negative-going transition (NGT). 4. Edge-triggered (clocked) flip-flops can be triggered to a new state by the active state edge of the clock input according to the state of the flip-flops synchronous control inputs (S,R or J, K or D). 5. Most clocked flip-flops also have asynchronous inputs that can set or clear the flip-flop independent of the clock input. 6. The D latch is a modified NAND latch that operates like a D flip-flop except that it is not edge-triggered. 7. Some of the principal uses of flip-flops include data storage and transfer, data shifting, counting and frequency division.

SEQUENTIAL LOGIC

E2064/1/34

SELF-ASSESSMENT 1

Question 1-1 a. Assuming that Q= 0 initially, apply the x and y waveforms of figure below to the SET and CLEAR inputs of a NAND latch, and determine the Q and

Q

waveforms.

b. Invert the x and y waveforms of figure in Question 1-1(a), apply them to the SET and CLEAR inputs of a NOR latch, and determine the Q and waveforms. Assume that Q= 0 initially. c. The waveforms of figure in Question 1-1(a) are connected to the circuit of figure below. Assume that Q= 0 initially, and determine the Q waveform.

x y

Q

S R

Q Q

SEQUENTIAL LOGIC

E2064/1/35

Question 1-2 a. List the conditions necessary for a positive-edge-triggered JK flip-flop with active-LOW asynchronous inputs to toggle to its opposite state. b. For a positive edge-triggered JK flip-flop with inputs as shown in figure below, determine the Q output relative to the clock. Assume that Q starts LOW.

C LK

c. For a negative edge-triggered JK flip-flop with inputs as shown in figure below, sketch the Q output waveform relative to the clock. Assume that Q starts LOW.

C LK J

SEQUENTIAL LOGIC

E2064/1/36

Feedback To Self-Assessment 1

Answer for Question 1-1 a.

X

b. c.

Same as (a) above.

y z

SEQUENTIAL LOGIC

E2064/1/37

Answer for Question 1-2 a. b.

C LK

J= K= 1,

PRE =CLR =

1, and a PGT at CLK.

J K

c.

C LK J

Teachers open the door, but you must enter by yourself. Teachers open the door, but you must enter by yourself. - Chinese proverb - Chinese proverb

S-ar putea să vă placă și

- Advance Laptop Chip Level Repair Engineering Training CourseDocument15 paginiAdvance Laptop Chip Level Repair Engineering Training CourseSanjeewa Silva50% (4)

- Electrical Power and Machines IntroductionDocument7 paginiElectrical Power and Machines Introductionshakeeb mana0% (1)

- Expt 5.2Document6 paginiExpt 5.2Joel CatapangÎncă nu există evaluări

- Control SCR firing angle using gate resistorDocument12 paginiControl SCR firing angle using gate resistorplokplokplokÎncă nu există evaluări

- MCQ in DC Biasing - BJTsDocument6 paginiMCQ in DC Biasing - BJTsPaolo PerezÎncă nu există evaluări

- EEET 205 Lab - 102Document53 paginiEEET 205 Lab - 102Franch Maverick Arellano LorillaÎncă nu există evaluări

- Acdc - Synchronous Motor - Lecture Notes 9Document19 paginiAcdc - Synchronous Motor - Lecture Notes 9Cllyan Reyes100% (1)

- Thyristor ReportDocument9 paginiThyristor ReportDhaval GamiÎncă nu există evaluări

- Impedance of RL Circuits: Series RL Circuits: Experiment No. 2Document16 paginiImpedance of RL Circuits: Series RL Circuits: Experiment No. 2NicoÎncă nu există evaluări

- 16FUSB Project - 1.2Document16 pagini16FUSB Project - 1.2Emanuel Paz100% (2)

- Microprocessors 8086 (Notes)Document29 paginiMicroprocessors 8086 (Notes)Aravindha BhatÎncă nu există evaluări

- ADE Lab Manual - Analog Part PDFDocument21 paginiADE Lab Manual - Analog Part PDFJk RinkuÎncă nu există evaluări

- Experiment 1Document6 paginiExperiment 1Jomel JomelÎncă nu există evaluări

- Ec8361-Adc Lab ManualDocument118 paginiEc8361-Adc Lab ManualmuminthajÎncă nu există evaluări

- Assignment 1Document6 paginiAssignment 1Dr.Hesham El-BadawyÎncă nu există evaluări

- Chapter 8 Manual OgataDocument53 paginiChapter 8 Manual OgataKalim UllahÎncă nu există evaluări

- MSDFFDocument20 paginiMSDFFShweta KumariÎncă nu există evaluări

- Experiment 1 - Single Phase TransformerDocument9 paginiExperiment 1 - Single Phase TransformerKhairul Islam HimelÎncă nu există evaluări

- ECS332 2015 Postmidterm HWDocument69 paginiECS332 2015 Postmidterm HWDeadpool 001Încă nu există evaluări

- Performance Evaluation of 6T, 7T & 8T SRAM at 180 NM TechnologyDocument7 paginiPerformance Evaluation of 6T, 7T & 8T SRAM at 180 NM TechnologyDr-Sanjeev KashyapÎncă nu există evaluări

- Auto TransformerDocument5 paginiAuto TransformerAugy HaerudyÎncă nu există evaluări

- Exercises For Lecture 5-6-7 - SOLUTIONDocument8 paginiExercises For Lecture 5-6-7 - SOLUTIONLam Pham Phuoc Loc100% (1)

- Determine System Stability with Nyquist CriterionDocument25 paginiDetermine System Stability with Nyquist CriterionHosein KerdarÎncă nu există evaluări

- Wien Bridge Oscillator Using OpampDocument4 paginiWien Bridge Oscillator Using OpampVishesh Kumar SinghÎncă nu există evaluări

- Transformers to Convert Three-Phase Power to Two-Phase Power RatingsDocument1 paginăTransformers to Convert Three-Phase Power to Two-Phase Power RatingsToper GarciaÎncă nu există evaluări

- DLD Lab Manual 7 FlipFlopsDocument6 paginiDLD Lab Manual 7 FlipFlopsHanzala NasirÎncă nu există evaluări

- Flipflops: Technical Seminar ReportDocument16 paginiFlipflops: Technical Seminar ReportrachitÎncă nu există evaluări

- Experiment:-7 Aim: To Study The Operation of Resistance Firing Circuit Using R, RC & UJT Firing Module. ApparatusDocument6 paginiExperiment:-7 Aim: To Study The Operation of Resistance Firing Circuit Using R, RC & UJT Firing Module. ApparatusNikhil BindalÎncă nu există evaluări

- Lab Session 2: Mathematical Modeling and Solving Differential Equations in MATLABDocument36 paginiLab Session 2: Mathematical Modeling and Solving Differential Equations in MATLABmuhammadÎncă nu există evaluări

- PTDU Lab No. 10 Study of Real Time Operation of Bus Bars Abdul Wahab Nasir (02) Bsee 16-20Document2 paginiPTDU Lab No. 10 Study of Real Time Operation of Bus Bars Abdul Wahab Nasir (02) Bsee 16-20Ali ArshadÎncă nu există evaluări

- AC BridgeDocument5 paginiAC Bridgesuvarnalatha devarakondaÎncă nu există evaluări

- Chapter 3 Energy of A System ThermoDocument25 paginiChapter 3 Energy of A System ThermoEmadudin AbdulkaderÎncă nu există evaluări

- LIC Lab ManualDocument65 paginiLIC Lab ManualBala Subramanian0% (1)

- Transient Behavior and Initial ConditionsDocument20 paginiTransient Behavior and Initial ConditionsTanuja VÎncă nu există evaluări

- CH-2-DC MachineDocument83 paginiCH-2-DC MachineÙm ØrthøbøyÎncă nu există evaluări

- AC Quantities ExplainedDocument7 paginiAC Quantities Explainedsrinivas100% (1)

- Pitch Factor N Distribution FactorDocument5 paginiPitch Factor N Distribution FactorKim KeatÎncă nu există evaluări

- Magnetically Coupled Circuits PDFDocument21 paginiMagnetically Coupled Circuits PDFOrlando100% (1)

- DC-DC ConvertersDocument30 paginiDC-DC ConvertersTema HassanÎncă nu există evaluări

- Diode Clippers: 1. Positive Clipper and Negative ClipperDocument6 paginiDiode Clippers: 1. Positive Clipper and Negative ClipperBibek ThapaÎncă nu există evaluări

- AC-DC Converter - DDocument39 paginiAC-DC Converter - DBishnu100% (1)

- Op-Amps As Ac Amplifers: Capacitor-Coupled Voltage FollowerDocument7 paginiOp-Amps As Ac Amplifers: Capacitor-Coupled Voltage FollowerNisha Kotyan G RÎncă nu există evaluări

- Power Electronics-3rd ChapterDocument80 paginiPower Electronics-3rd ChapterPasupuleti SivakumarÎncă nu există evaluări

- TransformerDocument29 paginiTransformergolu100% (1)

- Reference: OPAMP and Linear Integrated Circuits by Ramakant A. Gayakwad, PHIDocument27 paginiReference: OPAMP and Linear Integrated Circuits by Ramakant A. Gayakwad, PHIchandra prakash purbiaÎncă nu există evaluări

- 16x2 LCDDocument3 pagini16x2 LCDShailesh Ranaware0% (1)

- Transformer 1 2Document94 paginiTransformer 1 2Tobi AQWÎncă nu există evaluări

- 12V To 120V DC - DC Converter Using Power Electronics For Higher Efficiency and Reliable OperationDocument23 pagini12V To 120V DC - DC Converter Using Power Electronics For Higher Efficiency and Reliable OperationRaghav ChawlaÎncă nu există evaluări

- 1 (1) 4Document10 pagini1 (1) 4Angga SeptianÎncă nu există evaluări

- IE LAB3 MalibiranDocument10 paginiIE LAB3 MalibiranMary Jane MalibiranÎncă nu există evaluări

- ECA II Version 3 Lab Manual 2021Document152 paginiECA II Version 3 Lab Manual 2021Souban JavedÎncă nu există evaluări

- Cap 5Document29 paginiCap 5deberes ucacueÎncă nu există evaluări

- Polar & Nyquist Plots MCQDocument18 paginiPolar & Nyquist Plots MCQRajeev Singh BishtÎncă nu există evaluări

- Induction Motor Model Example SolutionDocument8 paginiInduction Motor Model Example SolutionJocel GuzmanÎncă nu există evaluări

- Circuit Analysis 1: Capacitors and InductorsDocument25 paginiCircuit Analysis 1: Capacitors and InductorsSharifah Azma100% (1)

- EEM328 Electronics Laboratory - Report4 - BJT BiasingDocument4 paginiEEM328 Electronics Laboratory - Report4 - BJT Biasingdonatello84Încă nu există evaluări

- IC 741 Op-Amp Tutorial and CharacteristicsDocument5 paginiIC 741 Op-Amp Tutorial and CharacteristicsBenÎncă nu există evaluări

- AparatusDocument187 paginiAparatusNorman Jay GarciaÎncă nu există evaluări

- 8086 Pin DiagramDocument18 pagini8086 Pin DiagramAkash MittalÎncă nu există evaluări

- Clippers and ClamersDocument15 paginiClippers and ClamersThilaga MohanÎncă nu există evaluări

- Topic 5 - Flip Flops Sequential CircuitsDocument16 paginiTopic 5 - Flip Flops Sequential CircuitsShivneet KumarÎncă nu există evaluări

- 06 - DFC10093 (Subchapter 2.3)Document23 pagini06 - DFC10093 (Subchapter 2.3)Navinaash Chanthra SegaranÎncă nu există evaluări

- Chapter 2.2Document15 paginiChapter 2.2OzzyÎncă nu există evaluări

- Inovasi PBS Eng 1 05Document1 paginăInovasi PBS Eng 1 05kenggeÎncă nu există evaluări

- Inovasi PBS Eng 1 007Document1 paginăInovasi PBS Eng 1 007kenggeÎncă nu există evaluări

- Inovasi PBS Eng 1 006Document1 paginăInovasi PBS Eng 1 006kenggeÎncă nu există evaluări

- Inovasi PBS Eng 1 01Document1 paginăInovasi PBS Eng 1 01kenggeÎncă nu există evaluări

- Special Me: Sing Along With The Teacher. Then Sing in GroupsDocument1 paginăSpecial Me: Sing Along With The Teacher. Then Sing in GroupskenggeÎncă nu există evaluări

- Special Me: Sing Along With The Teacher. Then Sing in GroupsDocument1 paginăSpecial Me: Sing Along With The Teacher. Then Sing in GroupskenggeÎncă nu există evaluări

- Bi Band 4 SKDocument5 paginiBi Band 4 SKamelia_rodzmanÎncă nu există evaluări

- Aoptrr: Rearrange The Letters To Form Word. Then Read The Word AloudDocument1 paginăAoptrr: Rearrange The Letters To Form Word. Then Read The Word Aloudمحمد أمير أمين الدينÎncă nu există evaluări

- Inovasi PBS Eng 1 05Document1 paginăInovasi PBS Eng 1 05kenggeÎncă nu există evaluări

- Eksna 4. God: Spell Correctly. Then Read AloudDocument1 paginăEksna 4. God: Spell Correctly. Then Read AloudkenggeÎncă nu există evaluări

- Eksna 4. God: Spell Correctly. Then Read AloudDocument1 paginăEksna 4. God: Spell Correctly. Then Read AloudkenggeÎncă nu există evaluări

- English Year 1 Name: - Date: - Let's Trace. A)Document15 paginiEnglish Year 1 Name: - Date: - Let's Trace. A)baksiÎncă nu există evaluări

- Aoptrr: Rearrange The Letters To Form Word. Then Read The Word AloudDocument1 paginăAoptrr: Rearrange The Letters To Form Word. Then Read The Word Aloudمحمد أمير أمين الدينÎncă nu există evaluări

- Inovasi PBS Eng 1 01Document1 paginăInovasi PBS Eng 1 01kenggeÎncă nu există evaluări

- Inovasi PBS Eng 1 007Document1 paginăInovasi PBS Eng 1 007kenggeÎncă nu există evaluări

- Test 1Document10 paginiTest 1watieupsi5230100% (4)

- Special Me: Sing Along With The Teacher. Then Sing in GroupsDocument1 paginăSpecial Me: Sing Along With The Teacher. Then Sing in GroupskenggeÎncă nu există evaluări

- Test 1Document10 paginiTest 1watieupsi5230100% (4)

- Bi Band 2 SKDocument15 paginiBi Band 2 SKamelia_rodzmanÎncă nu există evaluări

- Bi Band 3 SKDocument11 paginiBi Band 3 SKamelia_rodzmanÎncă nu există evaluări

- Bbpp-Motivation Chapter 7Document12 paginiBbpp-Motivation Chapter 7Azliana Mohd TaibÎncă nu există evaluări

- 2882 User Manual10Document17 pagini2882 User Manual10Azliana Mohd TaibÎncă nu există evaluări

- Intrumen Pentaksiran English Year 1Document6 paginiIntrumen Pentaksiran English Year 1Nur AzidahÎncă nu există evaluări

- Bi Band 4 SKDocument5 paginiBi Band 4 SKamelia_rodzmanÎncă nu există evaluări

- English Year 1 Examination/ TestDocument8 paginiEnglish Year 1 Examination/ TestShe KazumiÎncă nu există evaluări

- Heartpouch PDFDocument1 paginăHeartpouch PDFAzliana Mohd TaibÎncă nu există evaluări

- Bbpp1103: Management Principles: Chapter 11: Innovation and ChangesDocument12 paginiBbpp1103: Management Principles: Chapter 11: Innovation and ChangesAzliana Mohd TaibÎncă nu există evaluări

- Bbpp1103 Chapter 10Document14 paginiBbpp1103 Chapter 10Azliana Mohd TaibÎncă nu există evaluări

- 3 - Limit and Reed SwitchesDocument27 pagini3 - Limit and Reed SwitchesAzliana Mohd TaibÎncă nu există evaluări

- BBPP1103 LEADERSHIP APPROACHESDocument13 paginiBBPP1103 LEADERSHIP APPROACHESAzliana Mohd TaibÎncă nu există evaluări

- CMOS Transmission Gate OperationDocument15 paginiCMOS Transmission Gate OperationGaurav MehraÎncă nu există evaluări

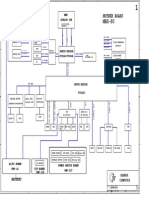

- Ifc228 LCD Main SCH 500Document15 paginiIfc228 LCD Main SCH 500khafjiÎncă nu există evaluări

- Digital Electronics ProjectDocument14 paginiDigital Electronics ProjectSana KhanÎncă nu există evaluări

- Computer Organization and Architecture: Chapter FiveDocument23 paginiComputer Organization and Architecture: Chapter FiveZerihun BekeleÎncă nu există evaluări

- Placa Base Asus P5GC-MX-1333Document92 paginiPlaca Base Asus P5GC-MX-1333Infonova RuteÎncă nu există evaluări

- Clock DistributionDocument52 paginiClock Distributiontejanossam100% (1)

- Sony-Ne5-Mb-3e Sony SCHEMATICDocument31 paginiSony-Ne5-Mb-3e Sony SCHEMATICvideosonÎncă nu există evaluări

- Chapter - 1: Ece Department, AcoeDocument55 paginiChapter - 1: Ece Department, AcoeSana SriRamyaÎncă nu există evaluări

- DatasheetDocument2 paginiDatasheetSai Krishna BangaruÎncă nu există evaluări

- Lecture02 - The 8086 Microprocessor ArchitectureDocument53 paginiLecture02 - The 8086 Microprocessor ArchitectureBarkhad MohamedÎncă nu există evaluări

- Designing a Basic MicroprocessorDocument53 paginiDesigning a Basic Microprocessordany rushwilleÎncă nu există evaluări

- 8 Bit Risc Processor PresentationDocument36 pagini8 Bit Risc Processor PresentationSantanu KumarÎncă nu există evaluări

- Edge vs Level Triggering: What's the DifferenceDocument3 paginiEdge vs Level Triggering: What's the DifferenceNaganithesh GhattamaneniÎncă nu există evaluări

- Commodorediagnostic781220Document16 paginiCommodorediagnostic781220a sÎncă nu există evaluări

- HBM Memory Controller v1.0Document94 paginiHBM Memory Controller v1.0RKavyaÎncă nu există evaluări

- Lab MC P1 1618200Document17 paginiLab MC P1 1618200luis gonzalezÎncă nu există evaluări

- Neon MNC Model: SpecificationDocument1 paginăNeon MNC Model: SpecificationYosep PermanaÎncă nu există evaluări

- DS14 Choose The Right Buck Converter For Your USB 3.1 Type C Powered DevicesDocument3 paginiDS14 Choose The Right Buck Converter For Your USB 3.1 Type C Powered DevicesCloue DeriadaÎncă nu există evaluări

- Pc16550D Universal Asynchronous Receiver/Transmitter With FifosDocument22 paginiPc16550D Universal Asynchronous Receiver/Transmitter With FifosRichard FergusonÎncă nu există evaluări

- ZedBoard Boot Guide IDS14 1 v1 1 PDFDocument38 paginiZedBoard Boot Guide IDS14 1 v1 1 PDFSoba TristaDvaÎncă nu există evaluări

- Dac 606 Dac 606e PDFDocument2 paginiDac 606 Dac 606e PDFPhilippe Ribeiro100% (1)

- Datasheet Eprom ST 95080 95160 95320 95640Document20 paginiDatasheet Eprom ST 95080 95160 95320 95640Patrick Roncato BritoÎncă nu există evaluări

- Power On Sequence GuideDocument8 paginiPower On Sequence GuidedraÎncă nu există evaluări

- ADE Lab ManualDocument59 paginiADE Lab ManualShreevas NandanÎncă nu există evaluări

- Silicon-on-Ferroelectric Insulator Field-Effect Transistor: Review ArticleDocument10 paginiSilicon-on-Ferroelectric Insulator Field-Effect Transistor: Review ArticleBryanÎncă nu există evaluări

- JNTUK UCE Narasaraopet III B.Tech II Sem Results Apr 2019Document49 paginiJNTUK UCE Narasaraopet III B.Tech II Sem Results Apr 2019UCEN CIVILÎncă nu există evaluări

- Rohini 74049417647Document5 paginiRohini 74049417647Aakash SharmaÎncă nu există evaluări