Documente Academic

Documente Profesional

Documente Cultură

Cerradura Digital

Încărcat de

Cristhian Llecllish ObregonDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Cerradura Digital

Încărcat de

Cristhian Llecllish ObregonDrepturi de autor:

Formate disponibile

PROYECTO DE SITEMAS DIGITALES CERRADURA DIGITAL

Introduccin: Las cerraduras digitales son muy usadas actualmente por su fcil configuracin y manejo. En este proyecto implementaremos un Sistema Digital de una cerradura digital programable en la inicializacin, esta cerradura constara de 4 dgitos que pueden ser del 0 al 9 o los otros valores arrojados por el decodificador que los veremos ms adelante. Materiales: 4 Displays de 7 segmentos nodo comn. 1 CI 74LS04 (6 inversores simples). 1 CI 74LS08 (4 compuertas AND de 2 entradas). 1 CI 74LS32 (4 compuertas OR de 2 entradas). 4 CI 74LS47 (Codificador BCD a 7-segmentos, con salidas a colector abierto (Display nodo comn)). 4 CI 74LS85 (Comparador de magnitud de 4 bits). 1 CI 74LS90 (Contador BCD de 4 bits). 4 CI 74LS273 (8 registros tipo D con borrado). 1 CI MM74C922 (Codificador de teclado matricial 4x4). 2 Capacitores electrolticos de 1uF y 1 de 10uF. Leds de colores para simular seales. Resistencias de 330 Ohm. 1 Teclado matricial numrico de 4x4.

Diseo:

U20 U22 U23

U21

10 12 13 15 9 11 14 1 2 3 4 A0 A1 A2 A3 B0 B1 B2 B3 A<B A=B A>B QA<B QA=B QA>B QA<B QA=B QA>B 74LS85 7 6 5 QA<B QA=B QA>B 7 6 5 74LS85 7 6 5 10 12 13 15 9 11 14 1 2 3 4 A0 A1 A2 A3 B0 B1 B2 B3 A<B A=B A>B A0 A1 A2 A3 B0 B1 B2 B3 A<B A=B A>B 10 12 13 15 9 11 14 1 2 3 4 74LS85

A0 A1 A2 A3 B0 B1 B2 B3 A<B A=B A>B

QA<B QA=B QA>B

7 6 5

10 12 13 15 9 11 14 1 2 3 4

74LS85

U20(A=B)

D1

LED-GREEN

U7

U6

U2

U1

U25

QA QB QC QD QE QF QG 13 12 11 10 9 15 14

7 1 2 6 4 5 3 A B C D BI/RBO RBI LT 74LS47 QA QB QC QD QE QF QG A B C D BI/RBO RBI LT 74LS47 74LS47 QA QB QC QD QE QF QG A B C D BI/RBO RBI LT

A B C D BI/RBO RBI LT

QA QB QC QD QE QF QG

13 12 11 10 9 15 14

7 1 2 6 4 5 3

13 12 11 10 9 15 14

7 1 2 6 4 5 3

13 12 11 10 9 15 14

7 1 2 6 4 5 3

U10

74LS47

U8

U3

3 4 7 8 13 14 17 18 11 1

D0 D1 D2 D3 D4 D5 D6 D7 CLK MR 74LS273

Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

2 5 6 9 12 15 16 19

3 4 7 8 13 14 17 18 11 1

D0 D1 D2 D3 D4 D5 D6 D7 CLK MR 74LS273

3 4 7 8 13 14 17 18 D0 D1 D2 D3 D4 D5 D6 D7 11 1 CLK MR 74LS273 CLK MR 74LS273 Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 11 1

2 5 6 9 12 15 16 19

3 4 7 8 13 14 17 18 D0 D1 D2 D3 D4 D5 D6 D7 Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

2 5 6 9 12 15 16 19

Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

2 5 6 9 12 15 16 19

U9:A

1 3 2 74LS32 14 1

U18

CKA CKB

U19:A

1 3 2 R0(1) R0(2) R9(1) R9(2) 74LS90 74LS08 2 3 6 7

Q0 Q1 Q2 Q3

12 9 8 11

C1 U4

KBM OSC DA OE 1uF C A B C D 17 16 15 14 12 13 6 5 10uF 11 10 8 7 X1 X2 X3 X4 A

7

B

8 4 1

D

9 5 2

ON C

1

C2

6 3 0

2

1 2 3 4 Y1 Y2 Y3 Y4 MM74C922

C3

1uF NOT

=

3

+

4

Funcionamiento: El circuito al iniciarse muestra todos los Displays en cero, luego el usuario tecleara una combinacin de 4 dgitos cualesquiera, los cuales quedaran grabados en registro de 4x4 bits formado por dos CI 74LS273, luego solo al volver a poner la misma combinacin y en el mismo orden se encender el led que abrir la puerta

1) Entrada y codificacin de datos:

C1 U4

11 10 8 7 X1 X2 X3 X4 KBM OSC DA OE A B C D 6 5 12 13 17 16 15 14 10uF A

7 4 1

ON C

1

8 5 2 0

2

9 6 3 =

3

C2

1uF

1 2 3 4

Y1 Y2 Y3 Y4 MM74C922

C3

1uF NOT

+

4

La entrada de datos se hace a travs de un teclado matricial de 4x4 y su respectivo codificador el CI MM74C922 configurado de la manera asncrona. Los dos capacitores electrolticos estn conectados a las entradas KBM (Key Bounce Elimination) y OSC (Oscilator) segn lo indica el datasheet donde si OSC es C, entonces KBM es 10C, estas son para eliminar el rebote producidos por los pulsadores del teclado matricial, para este caso utilizaremos 10uF para KBM y 1uF para OSC. Adems las salidas de DA (Data Aviable) y OE (Output Enable) estn configuradas de la siguiente manera: DA genera un tren de impulsos por cada vez que se presiona una tecla del teclado y con un inversor es usada para el clock del sistema, esto es para darle un atraso para poder cargar los flip flops antes del cambio de estado. Este mismo tren de impulsos invertido es usado para alimentar a OE, que se activa a nivel bajo, con un condensador de 1uF como un inicializador del circuito, para eliminar otras seales e iniciar siempre en cero.

2) Decodificacin y visualizacin:

U7

7 1 2 6 4 5 3 A B C D BI/RBO RBI LT 74LS47 QA QB QC QD QE QF QG 13 12 11 10 9 15 14 7 1 2 6 4 5 3

U6

A B C D BI/RBO RBI LT 74LS47 QA QB QC QD QE QF QG 13 12 11 10 9 15 14 7 1 2 6 4 5 3

U2

A B C D BI/RBO RBI LT 74LS47 Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 2 5 6 9 12 15 16 19 QA QB QC QD QE QF QG 13 12 11 10 9 15 14 7 1 2 6 4 5 3

U1

A B C D BI/RBO RBI LT 74LS47 QA QB QC QD QE QF QG 13 12 11 10 9 15 14

U8

3 4 7 8 13 14 17 18 11 1 D0 D1 D2 D3 D4 D5 D6 D7 CLK MR 74LS273 Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 2 5 6 9 12 15 16 19

U3

3 4 7 8 13 14 17 18 11 1 D0 D1 D2 D3 D4 D5 D6 D7 CLK MR 74LS273

U9:A

1 3 2 74LS32

Para la visualizacin se usan 4 Displays de 7 segmentos nodo comn con sus respectivos decodificadores 74LS47 en donde las U2 entradas LT (Lamp Test) y BI/RBO (Blanking Input o Ripple Blanking Output) los vamos a desactivar (se activan a nivel bajo) por lo que los conectamos a Vcc y solo dejamos activado RBI (Ripple Blanking Input) U3 en nivel bajo. En este decodificador ingresaremos valores arrojados por el teclado matricial que van de 0 al 15 dando las siguientes visualizaciones en los Displays para su uso como la clave:

7 1 2 6 4 5 3 A B C D BI/RBO RBI LT QA QB QC QD QE QF QG 13 12 11 10 9 15 14 74LS47 3 4 7 8 13 14 17 18 11 1 D0 D1 D2 D3 D4 D5 D6 D7 Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 2 5 6 9 12 15 16 19 CLK MR 74LS273

Para el corrido de los nmeros en los Displays utilizaremos flip flops tipo D en el integrado 74LS273 configurados como un registro de 4x4 en donde en el cambio de estado se van pasando el dato de 4 bits en paralelo, para ello conectamos la U3 3 2 D0 Q0 salida Q0 del primer flop flop a la entrada D4 (primera 4 5 D1 Q1 7 6 D2 Q2 entrada) del segundo flip flop (recordando que el CI 8 9 D3 Q3 13 12 D4 Q4 14 15 74LS273 es un ctuple flip flop D). El clock de estos CI D5 Q5 17 16 D6 Q6 18 19 son conectados a la salida del inversor del tren de D7 Q7 11 pulsos DA del CI MM74C922 haciendo que corra la CLK 1 MR informacin de Display a Display con el pulso de 74LS273 presionar una tecla en el teclado.

3) Registro y guardado de clave:

U25

3 4 7 8 13 14 17 18 11 1 D0 D1 D2 D3 D4 D5 D6 D7 CLK MR 74LS273 11 1 Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 2 5 6 9 12 15 16 19

U10

3 4 7 8 13 14 17 18 D0 D1 D2 D3 D4 D5 D6 D7 CLK MR 74LS273 Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 2 5 6 9 12 15 16 19

U9:A

1 3 2 74LS32 2 3 6 7 14 1

U18

CKA CKB Q0 Q1 Q2 Q3 12 9 8 11

U19:A

1 3 2 74LS08

R0(1) R0(2) R9(1) R9(2) 74LS90

Para el guardado de la clave se utiliza un registro de flip flops tipo D de 4x4 en el integrado 74LS273 similar al anterior solo que esta vez se registran solo 4 datos de todo el tren de pulsos generado por el CI MM74C922. Estos datos, al cortar el clock en el 5to periodo, quedan almacenados en los flip flops para su posterior comparacin. El primer CI 74LS273 est conectado a la entrada del codificador del primer Display y su conexin en paralelo con los otros CI 74LS273 hace que as como en la parte de visualizacin tambin los datos corran de un flip flop a otro. Para que solo almacene los cuatro primeros dgitos es necesario un contador bcd de 4 bits, el CI 74LS90, en donde segn su configuracin en el datasheet, la salida Q0 tiene que ser conectada con el CKB para un conteo ascendente. Tambin las entradas R0 (1), R0 (2), R9 (1) y R9 (2) que asen referencia a Master Reset y Master Set respectivamente se desactivan ponindolas en nivel bajo, basta solo con poner tres de ellas cualquiera. La lgica combinacional que hace que el CI 74LS90 solo deje pasar 4 pulsos esta dado por dos compuertas lgicas: 1 compuerta AND (CI 74LS08) y 1 compuerta OR (CI 74LS32) y est dada por: Q3 Q2 Q1 Q0 A 0 0 0 0 Pasa el dato 0 0 0 1 0 0 0 1 0 0 0 0 1 1 0 0 1 0 0 0 0 1 0 1 1

A=Q0+Q2 Pasa el dato: es para cargar el flip flop con el primer dato Y este A pasa por la compuerta OR, junto con el Clock donde: Clock A 0 1 CLK A 1

Con el nivel alto se corta el clock hasta un nuevo reinicio de todo el sistema.

4) Comparacin de datos:

U20

10 12 13 15 9 11 14 1 2 3 4 A0 A1 A2 A3 B0 B1 B2 B3 A<B A=B A>B 74LS85 U20(A=B) 10 12 13 15 9 11 14 1 2 3 4

U21

A0 A1 A2 A3 B0 B1 B2 B3 A<B A=B A>B 74LS85 10 12 13 15 9 11 14 1 2 3 4

U22

A0 A1 A2 A3 B0 B1 B2 B3 A<B A=B A>B 74LS85 10 12 13 15 9 11 14 1 2 3 4

U23

A0 A1 A2 A3 B0 B1 B2 B3 A<B A=B A>B 74LS85

QA<B QA=B QA>B

7 6 5

QA<B QA=B QA>B

7 6 5

QA<B QA=B QA>B

7 6 5

QA<B QA=B QA>B

7 6 5

D1

LED-GREEN

Por ltimo en la comparacin de datos se utilizan 4 CI 74LS85 que son comparadores de 4 bits de magnitud configurados en cascada utilizando los 4 nmeros de 4 bits como si fueran uno solo de 16 bits y comparndolo de igual manera con el otro. Para la configuracin en cascada se conectan las salidas A=B a las siguientes entradas A=B del siguiente CI. Un led con una resistencia colocado en la salida del ltimo CI comparador se enciende cuando la clave ingresada es igual a la almacenada

U1

7 1 2 6 4 5 3 A B C D BI/RBO RBI LT 74LS47 QA QB QC QD QE QF QG 13 12 11 10 9 15 14

U23

10 12 13 15 9 11 14 1 2 3 4 A0 A1 A2 A3 B0 B1 B2 B3 A<B A=B A>B 74LS85

QA<B QA=B QA>B

7 6 5

D1

LED-YELLOW

R1

330R

U25

3 4 7 8 13 14 17 18 11 1 D0 D1 D2 D3 D4 D5 D6 D7 CLK MR 74LS273 Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 2 5 6 9 12 15 16 19

S-ar putea să vă placă și

- MicrochipMBA v3Document8 paginiMicrochipMBA v3Julio ContrerasÎncă nu există evaluări

- 5 S' en Llavero ItpDocument4 pagini5 S' en Llavero ItpIsaac GallardoÎncă nu există evaluări

- Especiales Reguladas NIC7766829 7998570589Document2 paginiEspeciales Reguladas NIC7766829 7998570589Jesidt PizarroÎncă nu există evaluări

- Manual de Operación Gasificador BelonioDocument11 paginiManual de Operación Gasificador Belonioalexaira villamilÎncă nu există evaluări

- Informe LubricantesDocument11 paginiInforme LubricantesEmmanuel Eliseo Zárate MartínezÎncă nu există evaluări

- Ley de Fomento A La Innovacion y Manufactura de Tecnologias PDF 1Document9 paginiLey de Fomento A La Innovacion y Manufactura de Tecnologias PDF 1Tecnología & Soluciones LegalesÎncă nu există evaluări

- Formato Presentación Curso Soldadura - Incatal 2023Document16 paginiFormato Presentación Curso Soldadura - Incatal 2023Enzo DiazÎncă nu există evaluări

- Ficha de Identificación 22 - 23 TALAVERADocument2 paginiFicha de Identificación 22 - 23 TALAVERAJose Alejandro Altamirano RamirezÎncă nu există evaluări

- Derivación de Funciones Compuestas e ImplícitasDocument43 paginiDerivación de Funciones Compuestas e ImplícitasEsteban LopezÎncă nu există evaluări

- S09.s1 - Continuidad 2022Document22 paginiS09.s1 - Continuidad 2022Rodolfo Toro QuiroZÎncă nu există evaluări

- Technical Data Sheet Krystol Repair Grout SpanishDocument2 paginiTechnical Data Sheet Krystol Repair Grout SpanishYatsen Jepthe Maldonado SotoÎncă nu există evaluări

- S06 PLC S7 1200 Temporizadores-Secuencia-ForzadaDocument34 paginiS06 PLC S7 1200 Temporizadores-Secuencia-ForzadaAntonio Berrospi ZarateÎncă nu există evaluări

- Cálculo de Fusibles para Cuchillas Desconectadoras A 15kVDocument19 paginiCálculo de Fusibles para Cuchillas Desconectadoras A 15kVMANUEL ROMERO MINAÎncă nu există evaluări

- Trabajo de Contraloria (Luis Ernesto Encarnacion)Document16 paginiTrabajo de Contraloria (Luis Ernesto Encarnacion)Carlos David A. MartinezÎncă nu există evaluări

- Emotron Product Leaflet - Variable Speed Drives VSA VSC - 01 3962 04 SpanishDocument12 paginiEmotron Product Leaflet - Variable Speed Drives VSA VSC - 01 3962 04 SpanishCARLOSM1234Încă nu există evaluări

- Cómo Hacer Una Guitarra de Cartón Paso A PasoDocument3 paginiCómo Hacer Una Guitarra de Cartón Paso A PasoJose Sandoval100% (1)

- Especificaciones Tecnicas Estad Yana Columna PascoDocument38 paginiEspecificaciones Tecnicas Estad Yana Columna Pascoalienes0% (1)

- Ciencia y Tecnologia Como Asunto PolíticoDocument8 paginiCiencia y Tecnologia Como Asunto PolíticoMariangel Belandria100% (1)

- Gallina de Pascua - Tejiendo Perú PDFDocument9 paginiGallina de Pascua - Tejiendo Perú PDFGermanPersicoÎncă nu există evaluări

- Trabajo de R2Document36 paginiTrabajo de R2eduinÎncă nu există evaluări

- Acfrogd8bvosfx7kzgw6 22fnszf1 Dabirm0h 8oaoyuqauzuytf6e3b92vqtgtuqhi6pbam6xqqyihzje7u 2l5m6b6enqg0gsjr7mdfdec5telxkes6ose9fqeg119uoubbyzvvapoelazdq7Document200 paginiAcfrogd8bvosfx7kzgw6 22fnszf1 Dabirm0h 8oaoyuqauzuytf6e3b92vqtgtuqhi6pbam6xqqyihzje7u 2l5m6b6enqg0gsjr7mdfdec5telxkes6ose9fqeg119uoubbyzvvapoelazdq7MrMattafixÎncă nu există evaluări

- IAE-D112-06669-SP - El Incendio de Mann GulchDocument4 paginiIAE-D112-06669-SP - El Incendio de Mann GulchIsabella B.GÎncă nu există evaluări

- Ecuaciones HiperbolicasDocument16 paginiEcuaciones HiperbolicasgiovannyÎncă nu există evaluări

- Actividad Duracion 1. Implementación de Modulo Gestión de Eventos ItopDocument6 paginiActividad Duracion 1. Implementación de Modulo Gestión de Eventos ItopCristian ArellanoÎncă nu există evaluări

- 17 - Tarea No.1Document56 pagini17 - Tarea No.1Eduardo SolorzanoÎncă nu există evaluări

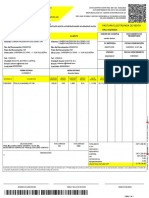

- Factura Electronica de Venta NAC 60249306Document1 paginăFactura Electronica de Venta NAC 60249306Gilgal ImpresionesÎncă nu există evaluări

- Evidencias DescripcionDocument8 paginiEvidencias Descripcionfaxima123Încă nu există evaluări

- 1.1a Funcion Del RouterDocument4 pagini1.1a Funcion Del RouterPedro GilÎncă nu există evaluări

- LoopDocument1 paginăLoopJosé Ricardo Rivera MontenegroÎncă nu există evaluări

- Proyecto Educativo Dia de La Ciencia y Tecnologia 20231Document4 paginiProyecto Educativo Dia de La Ciencia y Tecnologia 20231geovana mercedes ramirezÎncă nu există evaluări