Documente Academic

Documente Profesional

Documente Cultură

PHase Locked Loop

Încărcat de

RF_RAJATitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

PHase Locked Loop

Încărcat de

RF_RAJADrepturi de autor:

Formate disponibile

Design How-To

Charge-Pump Phase-Locked Loop--A Tutorial--Part I

1. Introduction

The phase-locked loop (PLL) is one of the key building blocks in many communication systems; providing a means for maintaining timing integrity and clock synchronization. The PLL can be used in various applications such as timing extraction from data streams, jitter mitigation and frequency synthesis.1,4,7

In this article, we describe the fundamental properties of a charge-pump PLL (CP-PLL). The CP-PLL derives its name from the fact that the phase detector (PD) output is a current source as opposed to a voltage source and "pumps" current into and out of the loop-filter. This form of PLL is popular because it is adaptable to integration in microcircuit devices. Therefore we focus the discussion on methods suitable for ASIC design. We provide mathematical models to study key parameters affecting the loop-bandwidth, peaking, jitter, noise and transient response.

2. Overview The basic PLL (Fig. 2-1) consists of four fundamental components: * Phase detector, PD * Loop-filter, z(s) * Voltage Controlled Oscillator, VCO * Divider, (1/n) The phase detector (PD) compares the input signal fi with a reference, or feedback signal fr, to produce an error signal error signal e that is proportional to the phase difference between fiand fr.

The loop-filter extracts the low frequency content z of the phase error signal e, which is fed to a voltage-controlled oscillator (VCO). The VCO produces an output frequency v proportional to the low frequency error signal z. The output signal v is typically divided by a 1/n counter producing the reference signal r.

The reference signal fr is fed back to the phase detector, forming a closed-loop system. Using negative feedback, the loop ensures that the input frequency fi equals the reference frequency r and also that the phase of i and r are fixed with respect to each other. However, the absolute phase difference between i and rneed not be zero. Note the divider inside the loop serves as a frequency multiplier. The output may be taken from either v or rtherefore the output frequency is given by (2.1) A modification to the basic PLL is obtained by inserting an additional divide by m counter outside the loop (Fig 2-2).

Unlike the n divider inside the loop, the m divider outside the loop acts as a frequency divider. By adjusting n and m you can obtain afractional rate frequency multiplier suitable for frequency synthesis. The output frequency is given by.

The charge-pump PLL (CP-PLL) is an extension of the basic PLL requiring the addition of a charge-pump between the phase detector and loop-filter. A specific embodiment (Fig 2-3) uses a three-state phase detector (3PD) which is used for the analysis going forward. Each of the blocks is discussed in the following sections.

3. PLL Components

3.1. Voltage Controlled Oscillator

One implementation of the VCO (Fig. 3.1) suitable for ASIC design consists of a series connected Voltage to Current Converter (V2CC) and a Current Controlled Oscillator (CCO).

The V2CC takes the control voltage vc and converts it to a proportional bias current ibias. The bias current is fed to the CCO which generates an output frequency proportional to the bias current. A representative implementation of a V2CC is shown in Fig. 3-2. The operational amplifier adjusts the gate voltage of Q1 such that the current flowing through Q1 is

The current mirror consisting of Q2 and Q3 develops the Pbias andNbias voltages respectively. These bias voltages are used to set the bias current in the CCO.

The VCO and CCO gains are defined respectively as

The CCO may be implemented as a simple ring oscillator (Fig. 3-3). The ring oscillator consists of n series-connected delay cells with the output of the last cell fed back to the input of the first.5,6

According to the Barkhausen criteria10 the ring will oscillate if: (1) the total magnitude of the gain around the loop is unity and (2) the total phase shift is zero or an integer multiple of 2pi radians at the oscillation frequency. In practical applications, the total loop gain should be slightly larger than unity to ensure positive feedback is maintained in the presence of device variations.

When the gain is larger than unity, the oscillation amplitude will be limited by the onset of device nonlinearity. In the case of the inverter, the nonlinearity acts as a hard limiter. It is clear that the total gain for n inverters is greater than unity. Each stage provides pi/n phase shift and so it requires two passes through the ring to acquire the necessary 2pi radian phase shift. Therefore, the frequency of oscillation is6

In order to establish a variable delay element responsive to the VCO control voltage, the delay for each cell can be made to depend on the amount of current used to bias the cells. One method known as a Current-Starved Inverter is shown in Fig 3.55.

The NBIAS and PBIAS voltages generated from the V2CC block, establishes the cell bias current for the N and P devices respectively. The cell delay is determined by the bias current IBIAS, the output capacitance Cx and the Schmidt trigger thresholds vth

An alternative version of a current-starved inverter operating directly from the control voltage vc, is shown in Fig. 3-75 The control voltage sets the reference current for Q1 and Q2 The bias currents for Q4 and 3 are mirrored from Q1 and Q2 respectively. The bias current in Q3 and Q4 may be scaled up or down with respect to the reference current in Q1 and Q2.

If the propagation delay of the Schmidt trigger is much less than the delay Td, then the cell delay is approximately6.

From

which

the

oscillator

frequency

is

Equations (3.7) and (3.8) indicate that when the bias current is increased the delay decreases and the oscillator frequency increases. When the bias current is decreased the delay increases and the oscillator frequency decreases. The output of the loop-filter z(t) is the control voltage vc for the VCO. The VCO clock frequency v is proportional to the control signal therefore

The proportionality constant kv is the VCO gain constant (radians/voltsec). Since frequency is the time-rate-of-change of phase, then the output phase of the VCO is proportional to the integral of frequency, thus

3.2. Charge-Pump The charge-pump (Fig 3-8) consists of a set of current sources with magnitudes of IP1 and IP2 amps respectively. In most cases the current sources are symmetrical thus IP1 = IP2 = IP.

One source is connected to the positive supply rail while the other is connected to the negative supply rail. The sources are separated by two switches S1 and S2. The output of the phase detector provides the gating signals U (up) and D (down) which turn on S1 and S2 respectively. The phase detector is designed such that switches are never on simultaneously.When U is high and D is low then S1 is on and S2 is off which causes current to flow out of the pump and into the loop-filter.

When U is low and D is high then Q1 is off and Q2 is on which causes current to flow out of loop-filter and into the pump. A representative CMOS charge-pump circuit is shown in Fig. 3-9and is similar to the output stage of the current starved inverter (Fig 35). The VPBIAS and VNBIAS voltages set the positive and negative chargepump currents respectively.3,5

3.3. Loop-Filter The loop-filter is typically a simple passive filter (Fig. 3-10). The purpose of the loop-filter is to average the phase-error signal from the 3PD.

Where

The significance of the loop-filter regarding loop-stability and steadystate tracking error is discussed in section 4.2. 3.4. Three-State Phase Detector The 3-state phase detector (3PD) is a finite state machine with three defined states labeled S1, S2 and S3. The rising edges of theR and V inputs denoted by R and V respectively cause the 3PD to transition from one state to another based on the following state diagram (Fig. 3-11).

Note that U and D are never in the "on" or "1"state simultaneously.

The pulse width t is proportional to the relative phase difference between R and V. If the phase of R leads V (Figure 3-12) then the pulses will appear on the U output and the sign of t is positive. If the phase of R lags V then the pulses appear on the Douput and the sign is negative (Fig. 3-13).

The U signal causes pump current to be positive for a duration of tseconds and the D signal causes positive pump to be negative for a duration of t seconds. Therefore we can express the output of the phase detector and charge-pump as a single variable

A simple implementation of a 3-state phase detector and charge-pump is shown in Fig. 3-15. The phase detector consists of a pair of D-Flip Flops and an AND gate. The summing node subtracts theD signal from the U signal providing the polarity for t and the multiplier modulates the pump current Ip with t to generate the pump current ip.

As discussed previously, the 3PD generates an error signal eproportional to the phase difference between the input and reference clocks.

The proportionality constant kd is the phase detector constant. In the case of a charge-pump PD the units are amps/radian (if the PD is a voltage source the units are volts/radian). The phase detector gain including the charge-pump is determined as follows: The on-time for either U or D is

From which the phase detector constant (amp/rad) is3

The phase detector average output current iavg as a function of phase error e, is shown in Fig 3-16. The slope between -2pi and 2pi is linear and corresponds to the phase detector gain kd given by (3.19). For 0 < e < 2pi, the arrow indicates that the VCO will tend to drive the phase error towards zero by increasing the VCO frequency (down hill). For -2pi < e < 0, the arrow indicates that the VCO will tend to drive the phase error towards zero by decreasing the VCO frequency (up hill).

In addition to functioning as a phase detector, the 3PD also operates as a frequency detector; a characteristic not shared by some other types of phase detectors (e.g., XOR type). This feature is useful since it aids in frequency acquisition and also prevents the loop from locking to higher order harmonics of the input clock. To illustrate the frequency detecting ability we consider two cases.

If the R frequency is higher than the V frequency, the rising edges of R will appear to walk to the left with respect to V (Fig. 3-17), forcing the 3PD to toggle between states S2 and S3. This causes pulses to appear on the U output of the PD. The resulting average pump current is positive (into the loop-filter) resulting in an increase in the VCO frequency.

Case 2: R < V If the R frequency is lower than the V frequency, the rising edges of R will appear to walk to the right with respect to V (Fig.3-18), forcing the 3PD to toggle between states S1 and S2. This causes pulses to appear on the D output of the PD. The resulting average pump current is negative (out of the loop-filter) resulting in a decrease in the VCO frequency.

S-ar putea să vă placă și

- RF - WSN PaperDocument10 paginiRF - WSN PaperRF_RAJAÎncă nu există evaluări

- Optics & Laser Technology: Xin Li, Jing Ma, Siyuan Yu, Liying Tan, Tao ShenDocument3 paginiOptics & Laser Technology: Xin Li, Jing Ma, Siyuan Yu, Liying Tan, Tao ShenRF_RAJAÎncă nu există evaluări

- Microelectronics Journal: S. Toofan, A.R. Rahmati, A. Abrishamifar, G. Roientan LahijiDocument4 paginiMicroelectronics Journal: S. Toofan, A.R. Rahmati, A. Abrishamifar, G. Roientan LahijiRF_RAJAÎncă nu există evaluări

- Fso RF - Out RXRDocument11 paginiFso RF - Out RXRRF_RAJAÎncă nu există evaluări

- Draw Shape 2Document1 paginăDraw Shape 2RF_RAJAÎncă nu există evaluări

- 1 s2.0 S002626920800222X MainDocument6 pagini1 s2.0 S002626920800222X MainRF_RAJAÎncă nu există evaluări

- Free Space Optics ResearchDocument6 paginiFree Space Optics ResearchRF_RAJAÎncă nu există evaluări

- RR1Document1 paginăRR1RF_RAJAÎncă nu există evaluări

- RF Design TutorialDocument4 paginiRF Design TutorialRF_RAJAÎncă nu există evaluări

- MNAI Cadence Step by Step PDFDocument55 paginiMNAI Cadence Step by Step PDFRF_RAJAÎncă nu există evaluări

- Analysis, Design, and Optimization of Spiral Inductors and Transformers For Si RF IC'sDocument12 paginiAnalysis, Design, and Optimization of Spiral Inductors and Transformers For Si RF IC'sRF_RAJAÎncă nu există evaluări

- Full Text 01Document70 paginiFull Text 01RF_RAJAÎncă nu există evaluări

- GSML RFICDocument9 paginiGSML RFICRF_RAJAÎncă nu există evaluări

- DST Daad PPP 2014 EnglDocument6 paginiDST Daad PPP 2014 EnglramuÎncă nu există evaluări

- Oa 2 PDFDocument4 paginiOa 2 PDFRF_RAJAÎncă nu există evaluări

- DST ANR Joint Call For Pre Proposals PDFDocument2 paginiDST ANR Joint Call For Pre Proposals PDFRF_RAJAÎncă nu există evaluări

- Tutorial 6 2013w PDFDocument4 paginiTutorial 6 2013w PDFRF_RAJAÎncă nu există evaluări

- S Parameter BasicsDocument20 paginiS Parameter BasicsMihailÎncă nu există evaluări

- A 500Μw 2.4Ghz Cmos Subthreshold Mixer For Ultra Low Power ApplicationsDocument4 paginiA 500Μw 2.4Ghz Cmos Subthreshold Mixer For Ultra Low Power ApplicationsRF_RAJAÎncă nu există evaluări

- Acprcalc PDFDocument6 paginiAcprcalc PDFRF_RAJAÎncă nu există evaluări

- Analog Electronics - Part1 PDFDocument20 paginiAnalog Electronics - Part1 PDFRF_RAJAÎncă nu există evaluări

- Esl Ic 10 10 26 PDFDocument12 paginiEsl Ic 10 10 26 PDFRF_RAJAÎncă nu există evaluări

- (RFD0505) Advances in Handset Antenna DesignDocument4 pagini(RFD0505) Advances in Handset Antenna DesignAbhinav RaiÎncă nu există evaluări

- ISSCC2010 AdvanceProgram PDFDocument84 paginiISSCC2010 AdvanceProgram PDFRF_RAJAÎncă nu există evaluări

- Wlan ThesisDocument0 paginiWlan ThesisRF_RAJAÎncă nu există evaluări

- DRDO ER ProjectFormDocument7 paginiDRDO ER ProjectFormRF_RAJAÎncă nu există evaluări

- Virtuoso Neocircuit: Circuit Sizing and OptimizationDocument4 paginiVirtuoso Neocircuit: Circuit Sizing and OptimizationRF_RAJAÎncă nu există evaluări

- Cadence NeocircuitDocument3 paginiCadence NeocircuitRF_RAJAÎncă nu există evaluări

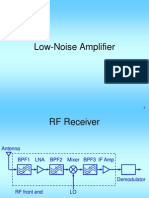

- Low Noise AmplifierDocument115 paginiLow Noise AmplifierRF_RAJAÎncă nu există evaluări

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (399)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (266)

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (588)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2259)

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (121)

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- API TutorialDocument22 paginiAPI TutorialKomarudinÎncă nu există evaluări

- Advanced Math2022fullDocument240 paginiAdvanced Math2022fullMọt PhimÎncă nu există evaluări

- Barnes en Bloor - NieuwDocument14 paginiBarnes en Bloor - NieuwpietpaaltjenÎncă nu există evaluări

- Symbols of Oil Gas PipingDocument3 paginiSymbols of Oil Gas PipingDelvin Davis M0% (1)

- Electrolysis 4.1Document42 paginiElectrolysis 4.1Maham khanÎncă nu există evaluări

- AI CalculatorDocument41 paginiAI CalculatorAneeza zafarÎncă nu există evaluări

- From External Alarm 17pli061 Asam - Asam - JorongDocument4 paginiFrom External Alarm 17pli061 Asam - Asam - JorongAMSARAH BR MUNTHEÎncă nu există evaluări

- Remote Terminal Viewer Software Release Note 1101192-A: © Foxboro Australia 2000 ACN 000 522 26Document16 paginiRemote Terminal Viewer Software Release Note 1101192-A: © Foxboro Australia 2000 ACN 000 522 26Mochamad EffendiÎncă nu există evaluări

- Chapter 3 Soil Mechanics Part IIDocument34 paginiChapter 3 Soil Mechanics Part IImmÎncă nu există evaluări

- Act MCQDocument10 paginiAct MCQKARTHICKÎncă nu există evaluări

- Surgical Sutures: Suture SizeDocument7 paginiSurgical Sutures: Suture SizeMei PayumoÎncă nu există evaluări

- DMSM10 Espinosa Fiche de Stage Parachute GBDocument2 paginiDMSM10 Espinosa Fiche de Stage Parachute GBHasan Junaid HashamÎncă nu există evaluări

- Lecture 2 - Inverse Laplace TransformsDocument3 paginiLecture 2 - Inverse Laplace TransformsAmirah MapandiÎncă nu există evaluări

- 1 Routing Tables ExplainedDocument8 pagini1 Routing Tables ExplainedallandonaldÎncă nu există evaluări

- Samsung Scala2-Amd r1.0 SchematicsDocument55 paginiSamsung Scala2-Amd r1.0 SchematicsJunioÎncă nu există evaluări

- Price DeterminationDocument2 paginiPrice DeterminationSikander BehalÎncă nu există evaluări

- Ambit ManiforlDocument6 paginiAmbit Maniforlmd_taheriÎncă nu există evaluări

- Dental CementDocument74 paginiDental CementAisha samreenÎncă nu există evaluări

- Neural-Network-Based Maximum Power Point Tracking Methods For Photovoltaic Systems Operating Under Fast Changing EnvironmentsDocument12 paginiNeural-Network-Based Maximum Power Point Tracking Methods For Photovoltaic Systems Operating Under Fast Changing EnvironmentsAbderrezak BadjiÎncă nu există evaluări

- s10763 017 9799 1 PDFDocument19 paginis10763 017 9799 1 PDFJoy PascoÎncă nu există evaluări

- LiftCell User ManualDocument4 paginiLiftCell User ManualEdini ZenaÎncă nu există evaluări

- Physics Lab ReportDocument3 paginiPhysics Lab ReportReysa Gabrielle PileÎncă nu există evaluări

- Annexure 1 - Technical Bid Analysis For Emergency Relief ValveDocument1 paginăAnnexure 1 - Technical Bid Analysis For Emergency Relief ValveNikhil KarkeraÎncă nu există evaluări

- DS350 Tadano Faun 1368Document61 paginiDS350 Tadano Faun 1368Mohamed Harb100% (2)

- TacheometryDocument6 paginiTacheometryregieÎncă nu există evaluări

- Phy Interface Pci Express Sata Usb31 Architectures Ver43 PDFDocument99 paginiPhy Interface Pci Express Sata Usb31 Architectures Ver43 PDFRaj Shekhar ReddyÎncă nu există evaluări

- Implementation of Integrated OBD-II Connector Whith External NetworkDocument7 paginiImplementation of Integrated OBD-II Connector Whith External NetworkKelvin PárragaÎncă nu există evaluări

- All About FTP Must ReadDocument7 paginiAll About FTP Must ReadPINOY EUTSECÎncă nu există evaluări

- Digital Control System Analysis and Design 4th Edition by Phillips ISBN Solution ManualDocument46 paginiDigital Control System Analysis and Design 4th Edition by Phillips ISBN Solution Manualraymond100% (23)