Documente Academic

Documente Profesional

Documente Cultură

Introsduccion Boole Deusto

Încărcat de

Bhily QuipoDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Introsduccion Boole Deusto

Încărcat de

Bhily QuipoDrepturi de autor:

Formate disponibile

INTRODUCCIN: En este presente trabajo presentaremos un software BOOLE-DEUSTO de anlisis y diseo de sistemas digitales combinacionales y secuenciales a nivel de bit.

Este software est orientado a las necesidades del alumno y el profesor, sobre todo en los primeros pasosde su aprendizaje. BOOLE est orientado a una disciplina denominada genricamente sistemas Digitales, que consta de tres grandes temas: Fundamentos de Sistemas Digitales: Codificacin, lgebra de Boole y representacin de sistemas digitales. Anlisis y diseo de sistemas conbinacionales; a nivel de bit y de palabra. Anlisis y diseo de sistemas secuenciales: A nivel de bit y de palabras. El profesor en clases enuncia el mtodo a aplicar y completar algn ejemplo. El alumno en casa debe consolida lo aprendido, complementando nuevos ejercicios. El papel de un entorno educativo en este escenario es doble: Comprobar que los resultados obtenidos por el alumno est bien. Mostrar al alumno como se aplica un mtodo; recordarle los pasos. Para que el entorno lleve a cabo con xito su trabajo debe tener una serie de caractersticas: a) b) c) d) e) completo: debe completar el mayor nmero posible de mtodos. utilizable: debe adaptarse a los conocimientos y posibilidades del alumno. Amigable: debe ser fcil e intuitivo de usar y visualizar en los resultados. Didctico: debe mostrar todos los pasos que le llevan a un resultado. Instalable: debe ser fcil de instalarlo.

En no pocas ocasiones los entornos computacionales no ayudan al alumno; es ms, le confunden, generando frustracin y desconocimiento. A nuestro parecer es mejor no utilizar un entorno computacional si ste es inadecuado. Estudiemos a la luz de los puntos anteriores la idoneidad didctica de los entornos profesionales como OrCAD, MAX PLUS II, XILINX Foundation, Electronic WorkBench, etc. En primer lugar recordemos que estos entornos son profesionales; su objetivo es ayudar en el diseo de circuitos electrnicos, no ayudar al alumno. Veamos algunas de sus caractersticas: No le interesan los mtodos, le interesan sus resultados: los circuitos electrnicos. Sus usuarios finales son los profesionales. Su uso es tan potente como complicado. No son didcticos; slo buscan los resultados. Son difciles de instalar. Son generalmente caros.

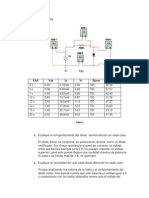

Resulta tan evidente como sencillo que los objetivos de los entornos profesionales estn alejados de las necesidades del profesor y del alumno en el aula. La tabla (1) compara ambos entornos, resaltando las diferencias. Tabla (1) ENTORNO BOOLE-DEUSTO Didctico Necesidades del alumno Hasta nivel de bit Proyectos sencillos El alumno controla a la herramienta Interesa el proceso Es gratis y de libre distribucin No tiene simulacin temporal No permite la captura grfica de un circuito ENTORNOS PROFESIONALES Profesional Necesidades del profesional Hasta nivel de sistema Proyectos complejos El usuario es dirigido por la herramienta Interesa el resultado Costo generalmente elevado S tiene simulacin temporal Permite la captura grfica de un circuito

Todo lo anterior viene a fortalecer la necesidad de un entorno completo y didctico en la disciplina de sistemas digitales: BOOLE-DEUSTO 1) ASPECTOS BSICOS DE USO DEL BOOLE-DEUSTO: Los aspectos bsicos son: Los sistemas han de ser secuenciales o combinacionales, pero siempre a nivel de bit. Los sistemas combinacionales tienen como ncleo a la tabla de verdad, mientras que los secuenciales son autmatas. Los sistemas combinacionales tienen como mximo 10 variables de entrada. Los sistemas combinacionales soportan como mximo y en principio. Los nombres de las variables pueden ser cambiados. Los autmatas pueden ser de Moore o de Mealy. Al describir un sistema hay que empezar dndole nombre e indicando el nmero de variables de entrada y de salida. Al salir de una pantalla de captura de datos hay que pulsar siempre Evaluar (y Salir) para que los datos sean actualizados. Las funciones se cargan y se visualizan de una en una, utilizando la barra de desplazamiento. Las tablas de verdad y diagramas de Veitch-Karnaugh no deben tener huecos (se puede utilizar la opcin Completar). Se pueden imprimir los resultados tanto para sistemas secuenciales como combinacionales. Los elementos grficos (circuitos lgicos y diagramas de transicin de estados) pueden ser copiados al portapapeles, y de l a cualquier documento. Todo sistema, ya sea combinacional o secuencial, puede ser guardado y cargado como un fichero.

Las pantallas que tengan alguna complicacin disponen de Ayuda. 2) INSTALACIN Y USO: Para instalar BOOLE bastar con copiar el ejecutable, o con copiar y descomprimir el fichero ZIP. La instalacin no puede ser ms sencilla, de hecho fue un requisito a la hora de disear el entorno. De este modo el alumno le basta con crear una carpeta (o no), copiar el programa, hacer doble clic sobre l y empezar a trabajar 3) SISTEMAS COMBINACIONALES CON BOOLE: Antes de pasar a BOOLE, recordemos qu es disear. El diseo de un sistema combinacional pasa por varias fases: Leer y entender el enunciado. Determinar las variables de entrada y salida. Obtener de la tabla de verdad. Obtener las formas normales de cada variable de salida. Obtener los diagramas de Veitch-Karnaugh de cada salida. Simplificar cada V-K, obteniendo la expresin simplificada. Opcionalmente, reescribir la expresin anterior desde las puertas NAND o NOR. Obtener el circuito lgico. Implementar el circuito digital con circuitos integrados. Probar el circuito implementado. Los dos primeros pasos deben ser dados por el alumno/profesor, y los dos ltimos quedan fuera del BOOLE; pertenecen al laboratorio, con programas como Electronic WorkBench, OrCAD, etc. Centrmonosmediante un ejemplo en los seis pasos restantes. 4.1. EJEMPLO 01 DE SISTEMA COMBINACIONAL: El ejercicio que se propone consiste en disear el circuito transcodificador de BCD puro a BCD Aiken. Las variables de entrada son cuatro, las mismas que de salida. As pues la tabla de verdad a completar tendr 16 filas y cuatro salidas.

Figura 13.3

Una vez declarado el sistema, el alumno debe describirlo. La figura 13.3 muestra todas las opciones que ofrece BOOLE; en este caso optaremos por la opcin Tabla de Verdad Manual. Al activar esta opcin el alumno ver las 16 filas ordenadas, debiendo escribir l las salidas mediante clics de ratn. Al ponerse encima de una casilla, cada clic de ratn cambia el valor booleano. Adems no hay que cumplimentar toda la tabla, se pueden escribir slo los 1s y rellenar automticamente el resto con 0s, o escribir slo los 1s y 0s y rellenar el resto con condiciones libres.

Si el alumno quisiera, podra cambiar el sistema borrando los nmeros de F1 y escribiendo otros nuevos. Pero sigamos con el sistema tal y como lo hemos descrito al principio. Si despus de pulsar Salir en la anterior figura, el alumno pulsara V-K en la pantalla principal. Para ver los V-K de las restantes salidas, bastar con pulsar en la barra de desplazamiento. Adems de la opcin V-K el alumno dispone de V-K 2; con esta opcin obtendra un V-K ordenado de distinta manera (segn el cdigo Gray). De esta forma BOOLE busca adaptarse a las necesidades de los distintos profesores y alumnos. Del anterior V-K tiene por objetivo facilitar la simplificacin visual de la funcin y Expr. SOP Simplificada en la pantalla principal de la figura 13.3, el alumno obtendr las expresiones simplificadas de cada una de las salidas. Dichas expresiones lo sern en forma de suma de productos (SOP), aunque tambin podra haber optado por POS. Las expresiones obtenidas son mnimas necesariamente (el algoritmo implementado es recursivo y exacto), aunque el conjunto no tiene por qu serlo, es decir, simplifica cada funcin por separado. Muestra la expresin mnima de la salida 2 (para ver el resto pulsaremos en la barra de desplazamiento). Llegado a este punto el alumno habr completado todo el proceso de diseo paso por paso. Aunque si hubiera querido tambin habra podido introducir la tabla de verdad y seguidamente pulsar Expr. SOP Simplificada, ahorrndose los pasos intermedios; actitud que se debe evitar mientras se est aprendiendo a disear. Antes de pasar a disear otro sistema combinacional, el alumno podr guardar el sistema, imprimir los resultados obtenidos u obtener el cdigo correspondiente al sistema en OrCAD-PLD. 4.2. EJEMPLO 2 DE SISTEMA COMBINACIONAL: En este caso se va a disear con BOOLE un codificador 8:3 con prioridad. La figura 13.13 declara al sistema por su nombre y nmero de variables de entrada y salida. Pantalla principal al completo Optaremos en este caso por describir el sistema con Tabla de Verdad Compacta, en este caso el alumno es responsable de la entrada y la salida. A cambio puede asociar condiciones libres en la entrada, es decir, escribir varias filas en una sola. De este modo en vez de responder a 256 filas, el alumno escribir solamente 8. Esta opcin es muy cmoda (y peligrosa) en determinadas ocasiones. Si al utilizar esta opcin y las condiciones libres, el alumno no escribiera todas las filas BOOLE las tomara como condiciones libres, 0s 1s, segn lo elegido en la parte

superior de la figura. Una vez cargado el sistema, el alumno puede pasar por todas las fases del ejemplo anterior o activar directamente Expr. SOP Expresin SOP Simplificada Circuito Lgico AND-OR Los ejemplos han permitido describir los pasos a dar para disear un sistema combinacional. Ahora bien la parte combinacional del entorno BOOLE permite otros usos de gran valor didctico, como se ve a continuacin. 4.3. ANLISIS DE SISTEMAS COMBINACIONALES: En el caso de sistemas combinacionales, y en general, se puede decir que analizar es seguir el camino inverso de disear, es decir, dado un circuito o unas ecuaciones obtener su tabla de verdad para comprobar su idoneidad. El primer caso queda fuera de los objetivos del BOOLE, (cae dentro de los entornos profesionales: Electronic WorkBench, OrCAD, etc.), mientras que el segundo s es contemplado por BOOLE. Por ejemplo, el alumno puede comprobar si las expresiones por l obtenidas se comportan como un circuito de complemento a 9 (C3-0) para una entrada BCD (E3-0). C3= (~E3*~E2*~E1) C1= (E1) C2= (E2*~E1)+ (~E2*E1) C0= (~E0) Para comprobar dichas ecuaciones, el alumno habr declarado el sistema con su nombre, 4 entradas y otras tantas salidas, y seguidamente activar Expresin Booleana. Para introducir las expresiones booleanas habr que seguir las indicaciones que aparecen en la Ayuda de la pantalla. Introducidas una a una las cuatro funciones (utilizando la barra de desplazamiento). Captura de Expresin Booleana Despus de pulsar Evaluar y Salir el alumno volver a la pantalla principal, donde al activar Tabla de Verdad Manual obtendr la tabla correspondiente a dichas ecuaciones, comprobando su validez. Tabla de Verdad del sistema BOOLE permite otros caminos de anlisis, bastar con que el alumno introduzca el sistema mediante una tcnica de representacin y active otra para observar el resultado. De hecho, y visto as, anlisis y diseo se distinguen en el punto de vista, y no en los mtodos o tcnicas de representacin utilizadas. 4.4. SIMPLIFICACIN DE FUNCIONES: En el proceso de aprendizaje del alumno un paso costoso para l es aprender a simplificar funciones booleanas. El mtodo en s no es difcil de explicar, aunque s lo es su aplicacin. Como mtodo heurstico que es, slo se aprende practicando: dada una funcin, el alumno la simplifica y comprueba su acierto. Visto desde el punto de vista de la clase, el profesor explica los pasos, completa algn ejercicio y deja el resto del trabajo al alumno. En este escenario BOOLE es de gran ayuda tanto para el profesor como para el alumno. Si el alumno eligiera en la pantalla de sistema combinacionales la opcin Modo Aprendizaje (una vez dado nombre y declarado el nmero de variables de entrada y

salida), vera que aparecen el V-K del sistema cargado y una lnea para que escriba la expresin que l cree mnima. BOOLE analiza lo introducido, indicando al alumno: la expresin es incorrecta (no se corresponde con el V-K), la expresin es correcta pero no mnima (se corresponde con el V-K pero no es todo lo mnima que se puede) la expresin es correcta y mnima (acierto).

Como se puede ver en las figuras, BOOLE no muestra el resultado correcto, slo informa al alumno de lo correcto de su opcin. Si quisiera ver el resultado, debera volver a la pantalla principal y activar Expr. SOP Simplificada. 4.5. METODOLOGA BOOLEANA: A la hora de disear o analizar se aplican mtodos para pasar de una representacin a otra, y as disear es proceder de una forma ordenada en estas transformaciones. Sin embargo, muchas veces antes de que el alumno d estos pasos ordenados los practica por separado. Por ejemplo: Obtener la forma normal de una tabla de verdad, y viceversa. Obtener el diagrama de V-K de una tabla de verdad, y viceversa. Obtener el diagrama de V-K de una forma normal, y viceversa. Obtener la suma de minitrminos (o producto de maxitrminos) de una tabla de verdad, y viceversa. Obtener la expresin NAND/NOR de una expresin SOP o POS. La obtencin del circuito lgico de una expresin booleana. Todas las anteriores transformaciones (y otras) son contempladas por BOOLE, sin ms que introducir el sistema y pulsar la opcin deseada. Es bajo este uso cuando toma sentido la idea de Calculadora Booleana asociada a BOOLE (adems de ser una herramienta de anlisis y diseo). Con estos sencillos ejemplos queda claro que BOOLE es un excelente compaero del alumno en sus primeros pasos metodolgicos, cuando se acerca por primera vez al lgebra de Boole y las representaciones booleanas. Es probable que este inters del alumno sea poco duradero en el tiempo (se aprende rpido), pero intenso.

4) SISTEMAS SECUENCIALES CON BOOLE: BOOLE permite analizar y disear sistemas secuenciales a nivel de bit, llamados tambin autmatas. En este caso BOOLE no permite modificar el sistema en cualquiera de las fases. Las fases de diseo de un autmata son: Leer y entender el enunciado. Obtener diagrama de transicin de estados (DTE), ya sea MOORE o MEALY, indistintamente. Obtener la tabla de transicin de estados de salidas. Obtener la tabla de codificacin de estados. Obtener la tabla codificada de transicin de estados y salidas. Obtener la tabla de excitacin de Biestables D o J-K, indistintamente. Obtener los diagramas de V-K de cada JK o D y de cada salida.

Obtener las expresiones mnimas de las entradas de los biestables (J-K o D) y de las salidas. Implementar el circuito digital correspondiente con circuitos integrados. Probar el circuito implementado. Al igual que para sistemas conbinacionales, los dos primeros pasos y los dos ltimos no son contemplados por BOOLE, el resto s.

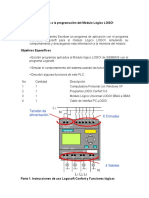

El circuito a disear debe comportarse como un sumador serie. El sistema recibe en serie dos entradas A y B y Ofrece tambin en serie en la salida la suma de dichas entradas. Lo primero que se debe hacer es: Hacer clic en la opcin Sistema secuencial Autnomas, de acuerdo a la siguiente figura:

Despus se ver la siguiente imagen, que ser la mesa de trabajo:

Dentro de la cual hay un cuadradito con las flechas y el crculo, puede estar fuera de la mesa detrabajo, pero se puede seleccionar y arrastrar de nuevo a la mesa. Seguidamente se debe declarar el autmata a disear. Para ello se despliega el men ARCHIVO, y en l se elige la opcin NUEVO, Donde aparece la siguiente de la figura:

El autmata a disear tiene dos entradas y una salida, y ser descrito como Moore. Pulsando Aceptar, BOOLE vuelve a mostrar la mesa de trabajo. Un autmata tiene estados, transiciones, entradas y salidas, as BOOLE ofrece el crculo (estado) y la flechapequea (transiciones). La flecha grande sirve para seleccionar un estado o una transicin, por ejemplo, lo primero es situar los cuatro estados del autmata, seleccionando el crculo y haciendo simplemente clic con elratn en la posicin deseada. As se obtiene la siguiente figura:

Para pasar de flecha grande a pequea o crculo basta con ir al cuadrado y seleccionar con el ratn. Si al situar un estado quisiramos moverlo bastara con seleccionarlo en modo flecha grande (las dos opciones de antes) y moverlo a la nueva posicin. Para borrar un estado habr que seleccionarlo en modo flecha grande y luego pulsar el botn derecho. parece lgico seguir con la asignacin de las salidas a cada estado (por ser un autmata de Moore). Los estados son cuatro S0C0, S1C0, S0C1 y S1C1, el primero es cuando la suma es 0 y el acarreo de salida tambin, el resto de estados se entienden del mismo modo. Para asignar la salida al estado habr que seleccionarlo en modo flecha grande y hacer doble clic sobre el estado. Al hacer esto aparece una pantalla en la que se escribir el nombre del estado y las salidas a los estados.

Figura Etiquetado de un estado Moore

Figura Estados de Moore etiquetados Para dibufar las transiciones simplemente basta con seleccionar la flecha pequea, hacer clic en el estado origen y clic en el estado destino; dibujando BOOLE la transicin. Para hacer un autolazo basta con hacer los dos clics en el mismo estado. Acabado este paso el autmata ser el de la siguiente figura:

Figura Autmata con transiciones Al situar las transiciones pueden darse dos situaciones incmodas: que una transicin quede encima de otra o que no se vea la punta de flecha de la transicin, en ambos casos la solucin pasa por mover las transiciones. En el primer caso, basta con estar en modo flecha grande, seleccionar garrar la punta de flecha (la flecha del autolazo es un cuadrado) y arrastrarla. En el segundo caso, habr que pasar a modo flecha grande, seleccionar el estado destino y moverlo, pues la punta de flecha estar debajo de l. Una vez que la flecha est a la vista, se procede como en el prrafo anterior.

Antes de disear se pueden activar dentro del men Resultados las opciones Verificar Correccin y Verificar Completitud, que nos indican si hemos olvidado alguna transicin, o si alguna de ellas est duplicada. En el men de Resultados podemos ver las opciones del diseo: simular el autmata, intentar reducir el autmata, obtener el autmata de Mealy equivalente y disear el autmata. BOOLE ofrece todas las tablas del diseo y las expresiones mnimas obtenidas en una sola pantalla, la que aparece en la Tabla de Excitacin de Biestables la q minscula representan al estado actual,mientras que Q mayscula representa al estado futuro, es decir, Q(t) y Q(t+1) o Q(t-1)y Q(t). Para ver el circuito lgico bastar con ir al men Circuito y elixir el biestable deseado Siguiendo estos pasos se habr podido obtener no slo el circuito lgico, sino que habr observado los distintos pasos. Adems se puede guardar el autmata, puede imprimir los resultados,puede copiar el DTE al portapapeles y puede obtener el correspondiente programa en OrCADPLD. El autmata de Mealy es capaz de detectar las secuencias 1010 110 permitiendo solapamientos y cambios entre secuencia. Dispone de una entrada serie y de una salida que indica si se ha detectado una de las dos secuencias. Se puede intentar reducir el anterior autmata de 6 estados. Basta con seleccionar Reduccin en el men Resultados. BOOLE muestra una pantalla en la que elegir si quiere ver los pasos de la reduccin o slo ver los resultados .Si el alumno, si optara por la primera opcin, deber guiar el proceso con sucesivos clics de ratn sobre Continuar, y as ir viendo cmo se completa la tabla de reduccin. Tras varios clics BOOLE ofrece el resultado de la posible reduccin, que en este caso deja al autmata en cuatro estados. Si tras la reduccin, se optara por Cambiar, el propio BOOLE sustituir el DTE antiguo por el nuevo, quedando ste a la vista. Si hiciera se podra reordenar o modificar lo dibujado por BOOLE. Por ltimo, y al igual que en los combi nacionales, BOOLE permite obtener el programa en OrCAD-PLD listo para ser compilado, simulado y grabado

5.2. Simulacin de autmatas El diseo de autmatas puede llegar a complicarse, siendo en estos casos muy tiles una herramienta de simulacin como la que presentamos. Una vez que el alumno ha introducido el DTE que l cree correcto puede simularlo, y as comprobar su validez. En este caso el alumno deber preparar un juego de ensayo de forma meticulosa, contemplando el mayor nmero de situaciones sin llegar a eternizarse. 5.2.1 simulaciones de batch Si el alumno dentro del men Resultados eligiera Simulacin Batch.En ella el alumno indicar cul va a ser el estado inicial y cuntos casos se van a simular (este nmero puede cambiar). En cada fila el alumno escribir el valor de las entradas, del reloj y del reset. Por ejemplo, en la primera fila activaremos el reset, en la segunda activaremos el clk con los valores 0 y 1 en las entradas, y as sucesivamente. Destacan en la simulacin las filas 5, 6 y 7, pues en ellas cambian las entradas, pero no hay clk.

Hay que ser cuidadoso a la hora de simular y leer la simulacin, teniendo en cuenta que: Al llegar a una fila (en azul), sta muestra su estado actual, su salida actual y cul va a ser su prximo estado (cuando se haga clic y haya clk). Una fila no es procesada hasta no pulsar Siguiente, es decir, la salida que se ve en cada fila es la de la fila anterior. No debe de verse la salida escrita en una fila como el resultado de procesar su entrada, sino como el resultado de procesar la anterior entrada. Esto puede parecer incmodo, pero resulta ms real y potente a la hora de plantear simulaciones donde la entrada cambia entre flancos.

5.2.2 simulacin interactiva En este caso el proceso es ms flexible para el alumno; l no tiene por qu preparar antes la secuencia de entrada, sino que la puede ir improvisando sobre la marcha. En la pantalla se ven varios elementos que hay que manejar con cuidado. Por ejemplo, lo primero que har el alumno ser pulsar Reset, luego escribir una entrada y pulsar Aplicar, con lo que la entrada pasa al DTE (lo que se ve en la parte grfica de la pantalla) y finalmente har clic sobre clk para que el autmata pase al nuevo estado (si as se desea). El desarrollo de la simulacin es interactivo, pero es guardada por BOOLE en un fichero .log, de modo que el alumno puede recuperar y revisar lo simulado bien para estudiarlo, imprimirlo o guardarlo (activando Ver log). 5.2.3 Comparacin simulacin interactiva vs batch Muchas veces al simular queremos que la entrada cambie con el flanco, lo que en principio no es real. Lo normal es primero cambiar la entrada y luego generar el flanco, de esta forma en el momento del flanco se procesa la entrada ya estabilizada. Vista la situacin anterior desde BOOLE hay que tener en cuenta que: En la simulacin interactiva primero se cambia la entrada y luego se genera el clk (Aplicar y clk), lo que asegura que el ritmo de la simulacin es controlado por el usuario, En la simulacin batch se puede forzar que el cambio de la entrada coincida con el flanco, ahora bien el usuario debe recordar que el efecto de dicha entrada no ser visto hasta pulsar Siguiente.

6 COMENTARIOS El entorno BOOLE ha sido diseado y programado durante cinco aos por sus autores, Jess Sanz Martnez y Javier Garca Zuba, y por alumnos de la Facultad de Informtica de la Universidad de Deusto (ESIDE), destacando entre este ltimo Borja Sotomayor. Se han utilizado la tecnologa orientada objetos, el lenguaje de programacin C++ y la librera STL. El resultado final tiene en este momento ms de 20.000 lneas de cdigo (excluyendo comentarios y lneas en blanco), lo que da una idea de la complejidad del entorno. BOOLE ha sido presentado en cuatro congresos nacionales e internacionales, y ha recibido el Premio al Mejor Equipo Software en el IV Congreso de Tecnologas Aplicadas a la Enseanza de la Electrnica, TAEE 2000, celebrado en Barcelona en septiembre del ao 2000. El entorno ha sido probado insistentemente por sus autores, sus alumnos (700 alumnos al ao de ingeniera informtica e industrial), otros profesores (Alfonso Barba y Jos Antonio Aranguren) y por otros colaboradores externos (gracias especialmente a Mariano Barrn y Javier Martnez), pero esto no es bice para que no aparezcan nuevos errores y comentarios

S-ar putea să vă placă și

- Conexión SQL SERVER & C# (Manual para principiantes)De la EverandConexión SQL SERVER & C# (Manual para principiantes)Evaluare: 1 din 5 stele1/5 (1)

- Gaboo24 PDFDocument4 paginiGaboo24 PDFMa Antonieta GalindoÎncă nu există evaluări

- Guía de uso en Matlab en el desarrollo de modelos de volatilidadDe la EverandGuía de uso en Matlab en el desarrollo de modelos de volatilidadÎncă nu există evaluări

- Sistemas Secuenciales Con Boole-DeustoDocument9 paginiSistemas Secuenciales Con Boole-DeustoTomas Sanchez TronoÎncă nu există evaluări

- Manual Boole Deusto DTEDocument10 paginiManual Boole Deusto DTERobert RoigÎncă nu există evaluări

- Manual - Boole 8 14Document7 paginiManual - Boole 8 14Gean Pierre Medina palacinÎncă nu există evaluări

- Practica 3 - 7 Segmentos KarnaughDocument6 paginiPractica 3 - 7 Segmentos Karnaughprofeitm100% (4)

- Guia de Laboratorio Arquitectura de Maq 1Document5 paginiGuia de Laboratorio Arquitectura de Maq 1David Alexander GutierrezÎncă nu există evaluări

- Guia de Septimo de Tecnologia Tarde Primer PeriodoDocument12 paginiGuia de Septimo de Tecnologia Tarde Primer PeriodoRolando De la Hoz SantanderÎncă nu există evaluări

- DiagrFlujo ProgramacionCDocument153 paginiDiagrFlujo ProgramacionCKevin ZaldañaÎncă nu există evaluări

- PLC Direct Logic05 - Prof. Faletti - 2012Document16 paginiPLC Direct Logic05 - Prof. Faletti - 2012Forumsur ArgentinaÎncă nu există evaluări

- Practica PLC 5Document19 paginiPractica PLC 5Agustin GalettoÎncă nu există evaluări

- Curso de Visual Foxpro ObjetosDocument40 paginiCurso de Visual Foxpro ObjetosvmasiasÎncă nu există evaluări

- Práctica LOGODocument17 paginiPráctica LOGOAlejandro GomezÎncă nu există evaluări

- Programacion Estructurada PDFDocument47 paginiProgramacion Estructurada PDFMiguel Dextre100% (1)

- Manual EMUDocument19 paginiManual EMUAndres SaniÎncă nu există evaluări

- Texto Apoyo C# PDFDocument115 paginiTexto Apoyo C# PDFdaniel sarzuriÎncă nu există evaluări

- Manual de LingoDocument79 paginiManual de LingoIvan FloresÎncă nu există evaluări

- Guía y Practico N°1 3ro Div 1era-3ra-4ta-6taDocument4 paginiGuía y Practico N°1 3ro Div 1era-3ra-4ta-6taFlorencia Gutierrez NietoÎncă nu există evaluări

- Manual - Boole 15 17Document3 paginiManual - Boole 15 17Gean Pierre Medina palacinÎncă nu există evaluări

- ALGORITMOSDocument11 paginiALGORITMOSRiveraÎncă nu există evaluări

- Programación de C++Document11 paginiProgramación de C++David GamboaÎncă nu există evaluări

- AlgebratorDocument8 paginiAlgebratormeryÎncă nu există evaluări

- 1ACT - Apuntes Hoja de CálculoDocument20 pagini1ACT - Apuntes Hoja de CálculoamparoÎncă nu există evaluări

- Manual Programacion M - EZPLC - Soft Esp.Document4 paginiManual Programacion M - EZPLC - Soft Esp.Hector AdamesÎncă nu există evaluări

- Métodos Numéricos - Comandos BásicosDocument31 paginiMétodos Numéricos - Comandos BásicosDiplomados ESGOBÎncă nu există evaluări

- 2 AlgoritmosDocument8 pagini2 AlgoritmosSergio Suárez RiesgoÎncă nu există evaluări

- MetradosecbDocument25 paginiMetradosecbMichael EduÎncă nu există evaluări

- Electrónica Digital - Manual de PrácticasDocument67 paginiElectrónica Digital - Manual de PrácticasSrebritoÎncă nu există evaluări

- Texto Apoyo C#Document116 paginiTexto Apoyo C#ept90327Încă nu există evaluări

- Tutorial Cupl UnDocument26 paginiTutorial Cupl UnHenry Takahashi GonzalezÎncă nu există evaluări

- Guia de Laboratorio Arquitectura de Maq 1Document4 paginiGuia de Laboratorio Arquitectura de Maq 1Josarelys GomezÎncă nu există evaluări

- Lenguaje de Descripción de HardwareDocument4 paginiLenguaje de Descripción de HardwareAlejandro G. EscandonÎncă nu există evaluări

- Sqltools Tutorial SPDocument13 paginiSqltools Tutorial SPEdwin CalleÎncă nu există evaluări

- FEM 49 para HPDocument84 paginiFEM 49 para HPBryanyMariaÎncă nu există evaluări

- 2012II+Manual-Uso Del MatlabDocument174 pagini2012II+Manual-Uso Del MatlabChelvis REÎncă nu există evaluări

- Algoritmos y ProgramasDocument14 paginiAlgoritmos y ProgramasRonald Âþâzâ100% (1)

- Guia de EagleDocument8 paginiGuia de EagleChrisÎncă nu există evaluări

- Manual Teclado PantallaDocument10 paginiManual Teclado PantallaLuis AlbertoÎncă nu există evaluări

- Laboratorio 1Document12 paginiLaboratorio 1Carolina Boza QuispeÎncă nu există evaluări

- FME09Document2 paginiFME09Jenny VelasquezÎncă nu există evaluări

- Practica 1 PLCDocument30 paginiPractica 1 PLCJonathan VázquezÎncă nu există evaluări

- Labcontrol p04 SL s0217 MJVDocument8 paginiLabcontrol p04 SL s0217 MJVSantiago CarmonaÎncă nu există evaluări

- SCILABDocument15 paginiSCILABJimmy Cervantes LivonÎncă nu există evaluări

- Tutorial Marcas de Ciclo STEP 7Document33 paginiTutorial Marcas de Ciclo STEP 7davidvh22Încă nu există evaluări

- Examen Teorico Delenguajes de ProgramacionDocument4 paginiExamen Teorico Delenguajes de ProgramacionDaNiElItO OffiCiAl FtÎncă nu există evaluări

- Capítulo 2Document9 paginiCapítulo 2Fernando AndresÎncă nu există evaluări

- Introducción A La Programación, 2022-1 Nota de Clase 04: Metodología de Solución de ProblemasDocument9 paginiIntroducción A La Programación, 2022-1 Nota de Clase 04: Metodología de Solución de ProblemasManuel Soto RomeroÎncă nu există evaluări

- Uso de - RSLogix EmulateDocument65 paginiUso de - RSLogix EmulateHelmer RamosÎncă nu există evaluări

- Sisco 2 PDFDocument11 paginiSisco 2 PDFDaniel Vargas OropezaÎncă nu există evaluări

- 8.hoja de Cálculo, Funciones Comunes, Fecha y HoraDocument10 pagini8.hoja de Cálculo, Funciones Comunes, Fecha y HoraBetty TANANTAÎncă nu există evaluări

- Sesión 01 - Introducción A Microsoft ExcelDocument18 paginiSesión 01 - Introducción A Microsoft ExcelRuben Angel Gilio MaguiñaÎncă nu există evaluări

- PytonDocument44 paginiPytonGabrielÎncă nu există evaluări

- FP Guio Ün Pra Ücticas Sesio Ün 1Document28 paginiFP Guio Ün Pra Ücticas Sesio Ün 1CARLOSÎncă nu există evaluări

- Taller de Cracking Desde Cero Por Karmany y ShaddyDocument22 paginiTaller de Cracking Desde Cero Por Karmany y ShaddyAristides RengelÎncă nu există evaluări

- Documento CADE - SIMUDocument4 paginiDocumento CADE - SIMUronyeÎncă nu există evaluări

- Guia Extraordinario ProgramacionDocument14 paginiGuia Extraordinario ProgramacionAntoÎncă nu există evaluări

- Soluciones Examen 20110609 SO Junio Segunda ParteDocument5 paginiSoluciones Examen 20110609 SO Junio Segunda Partefortino_sanchezÎncă nu există evaluări

- Dise Ñ o Comb I NacionalDocument15 paginiDise Ñ o Comb I NacionalWilmer Rueda RamosÎncă nu există evaluări

- Manual Uso Docente Matematica 2 SecDocument112 paginiManual Uso Docente Matematica 2 SecGloria100% (1)

- Ing Control I Cap 4Document29 paginiIng Control I Cap 4Bhily QuipoÎncă nu există evaluări

- 8216 8297 1 PB PDFDocument7 pagini8216 8297 1 PB PDFBhily QuipoÎncă nu există evaluări

- Controles PIDDocument8 paginiControles PIDNeztor MelgarejoÎncă nu există evaluări

- Ing Control I Cap 3Document16 paginiIng Control I Cap 3Bhily QuipoÎncă nu există evaluări

- Cont Digital Cap 1Document12 paginiCont Digital Cap 1Bombonzhitoh Zhokolate TelloÎncă nu există evaluări

- Ing Control I Cap 2Document14 paginiIng Control I Cap 2Bhily QuipoÎncă nu există evaluări

- HistoriaDocument1 paginăHistoriaBhily QuipoÎncă nu există evaluări

- Mapa Del LenguajeDocument1 paginăMapa Del LenguajeBhily QuipoÎncă nu există evaluări

- Triptico Lengua y SociedadDocument2 paginiTriptico Lengua y SociedadBhily QuipoÎncă nu există evaluări

- Monografia de DomoticaDocument20 paginiMonografia de DomoticaBhily QuipoÎncă nu există evaluări

- Arquitectura Renacentista ItalianaDocument1 paginăArquitectura Renacentista ItalianaBhily QuipoÎncă nu există evaluări

- Esta Di SticaDocument30 paginiEsta Di SticaBhily QuipoÎncă nu există evaluări

- ATOMOSDocument2 paginiATOMOSBhily QuipoÎncă nu există evaluări

- Aplicación de Las E.DDocument4 paginiAplicación de Las E.DBhily QuipoÎncă nu există evaluări

- Principio de ArquimidesDocument8 paginiPrincipio de ArquimidesBhily QuipoÎncă nu există evaluări

- Dilatacion de LiquidosDocument9 paginiDilatacion de LiquidosBhily QuipoÎncă nu există evaluări

- Monografia de EstadisticaDocument13 paginiMonografia de EstadisticaBhily QuipoÎncă nu există evaluări

- Documentos AdministrativosDocument14 paginiDocumentos AdministrativosBhily Quipo100% (1)

- Aplicacion de IntegralesDocument12 paginiAplicacion de IntegralesBhily QuipoÎncă nu există evaluări

- Curriculum Alex 2014Document2 paginiCurriculum Alex 2014Bhily QuipoÎncă nu există evaluări

- Practica 2Document0 paginiPractica 2Bhily QuipoÎncă nu există evaluări

- Tema 5Document17 paginiTema 5María Alejandra Zapata MendozaÎncă nu există evaluări

- Polarización DirectaDocument3 paginiPolarización DirectaBhily QuipoÎncă nu există evaluări

- Teoria y Practica de Diodos ZenerDocument6 paginiTeoria y Practica de Diodos ZenerHugo PazÎncă nu există evaluări

- Informe de Mapas de KarnaughDocument11 paginiInforme de Mapas de KarnaughBhily Quipo100% (1)

- Teoria y Practica de Diodos ZenerDocument6 paginiTeoria y Practica de Diodos ZenerHugo PazÎncă nu există evaluări

- Colis I OnesDocument8 paginiColis I OnesBhily QuipoÎncă nu există evaluări

- Segunda Ley de NewtonDocument8 paginiSegunda Ley de NewtonBhily QuipoÎncă nu există evaluări

- Guia 2 - AD - 2016Document4 paginiGuia 2 - AD - 2016Erick CatalanÎncă nu există evaluări

- La Ventana Como CuadroDocument7 paginiLa Ventana Como CuadroabresesamoÎncă nu există evaluări

- Pedagogia Ignaciana y Conciencia Emocion PDFDocument150 paginiPedagogia Ignaciana y Conciencia Emocion PDFunmasallaÎncă nu există evaluări

- Lentes Convergentes, Relación Imagen - ObjetoDocument24 paginiLentes Convergentes, Relación Imagen - ObjetoMauricio BenaventeÎncă nu există evaluări

- Planificación Antropología - (Cuatrimestral)Document7 paginiPlanificación Antropología - (Cuatrimestral)Archivos ImportantesÎncă nu există evaluări

- 1ra Monografia PilotesDocument5 pagini1ra Monografia PilotesiovicadÎncă nu există evaluări

- Zarco Agustinos El EscorialDocument429 paginiZarco Agustinos El EscorialJosé Manuel BonéÎncă nu există evaluări

- Unidad 2 Tipos de AvisosDocument2 paginiUnidad 2 Tipos de AvisosNoelia RojasÎncă nu există evaluări

- Act 3 CompletaDocument15 paginiAct 3 CompletaSantiago MarzalÎncă nu există evaluări

- Reseña Opcional Julián Alberto Liévano CelisDocument2 paginiReseña Opcional Julián Alberto Liévano Celisjulian levanoÎncă nu există evaluări

- Solucion Guia EticaDocument22 paginiSolucion Guia EticaYuliana GomezÎncă nu există evaluări

- Enseñanzas Cruciales en La Parábola de Los Dos Hijos PDFDocument3 paginiEnseñanzas Cruciales en La Parábola de Los Dos Hijos PDFPablo Chavarría MartínezÎncă nu există evaluări

- El Documental Como GeneroDocument10 paginiEl Documental Como GeneroEldiablo SantosÎncă nu există evaluări

- Asesinos SerialesDocument55 paginiAsesinos SerialesLenni Solano Campos100% (1)

- Preguntas Clave para La Enseñanza FilosóficaDocument11 paginiPreguntas Clave para La Enseñanza FilosóficaAlejandro GodoyÎncă nu există evaluări

- Emma Goldman Individuo Sociedad y EstadoDocument13 paginiEmma Goldman Individuo Sociedad y EstadoDaniel Tapia Arellano100% (1)

- Antecedentes y Escuela Clasica de AdmDocument13 paginiAntecedentes y Escuela Clasica de Admmarlen perezÎncă nu există evaluări

- La Autonomia PrivadaDocument8 paginiLa Autonomia PrivadaJuliana ForondaÎncă nu există evaluări

- Capponi Pedofilia PDFDocument5 paginiCapponi Pedofilia PDFAlexandra Romero VillaÎncă nu există evaluări

- Ensayo Herman Heriberto Sánchez CuevasDocument17 paginiEnsayo Herman Heriberto Sánchez CuevasHeri Sanchez CuevasÎncă nu există evaluări

- Anam Cara - El Libro de La Sabiduria Celta (Odonohue J)Document147 paginiAnam Cara - El Libro de La Sabiduria Celta (Odonohue J)Joaquin GonzalezÎncă nu există evaluări

- Perfil Psicologico Del Agresor en Actos de Violencia FamiliarDocument13 paginiPerfil Psicologico Del Agresor en Actos de Violencia FamiliarDaniel Villalvarosales100% (2)

- DemocraciaDocument2 paginiDemocraciaAlberto Delahoz Delahoz0% (1)

- Hombre Pobre, Hombre Rico, Gran Hombre, Jefe: Tipos Políticos en Melanesia y Polinesia Por Marshall SahlinsDocument3 paginiHombre Pobre, Hombre Rico, Gran Hombre, Jefe: Tipos Políticos en Melanesia y Polinesia Por Marshall SahlinsDanna Nadda0% (2)

- Monografia Redes SocialesDocument27 paginiMonografia Redes SocialesManuelFernandoMontoyaÎncă nu există evaluări

- Nace o Se HaceDocument14 paginiNace o Se HaceDaniella AraujoÎncă nu există evaluări

- ETICA EMPRESARIAL Evaluación Final - Escenario 8 - INTENTO 1Document13 paginiETICA EMPRESARIAL Evaluación Final - Escenario 8 - INTENTO 1MALUMAR0% (1)

- Pasos para La Planificación AnualDocument3 paginiPasos para La Planificación Anualfabiobar097188Încă nu există evaluări

- Teoría Estructuralista de La AdministraciónDocument3 paginiTeoría Estructuralista de La AdministraciónSrBilly OréÎncă nu există evaluări

- Cabala Articulo Laitman 2Document45 paginiCabala Articulo Laitman 2Nano AriaÎncă nu există evaluări