Documente Academic

Documente Profesional

Documente Cultură

Lab Format

Încărcat de

Noor AfiqDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Lab Format

Încărcat de

Noor AfiqDrepturi de autor:

Formate disponibile

1

DECLARATION

We declare that this report entitled Design of Voltage Divider BJT Transistor Network is the result of our own laboratory session except as cited in the references. The report has not been accepted for any subject and is not concurrently submitted in candidature of any other subject

Group Members: 1. 2. 3. 4.

Matrix No. :

Signature:

Date:

TABLE OF CONTENTS

CHAPTER

TITTLE

PAGE

DECLARATION TABLE OF CONTENTS

1 2

INTRODUCTION 1.1 1.2 Objectives Equipment

4 4 4

LITERATURE REVIEW

METHODOLOGY 3.1 Flowchart

9 10

4.1 4.2

Discussion and Suggestion Conclusion

12 12

REFERENCES Appendices 13

CHAPTER 1

INTRODUCTION

1.1

OBJECTIVES

By finishing this laboratory exercise, students are expected to gain the following skills:

1. Ability to design a stable voltage-divider bias BJT transistor configuration.

1.2

EQUIPMENT

1. Digital Multimeter 2. Resistor 3. Transistor: 2N3904 4. DC Power Supply 5. Breadboard 6. Wires

CHAPTER 2

LITERATURE REVIEW

A BJT is comprised basically of three doped semiconductor regions forming two p-n junctions connected back to back. The three semiconductor regions are identified as: the Base (B), the collector (C), and the emitter (E). The labelling codes "npn" and "pnp" identify the doping the three semiconductor regions that make up a BJT: npn implies n-type doping of the collector and emitter and p-type doping of the base; pnp implies the inverse. While the collector and emitter are always of the same doping type, the doping concentrations may be different in those two regions. The operation of a BJT depends on both electron and hole conduction. Depending on the bias of each of the two p-n junctions, the BJT operates in one of four distinct regions as shown below.

In many applications, the BJT is used in a common-emitter configuration. The EbersMoll model, used in PSpice, is used by SPICE to model common-emitter BJT circuits to model the transistor circuit in all operating regions. In linear applications, BJT circuits must be designed so that the transistor operates in the forward-active region. In order to insure operation in the forward-active region, the transistor is biased at a quiescent operating point, commonly called the Q-point, based on the DC conditions of the BJT. The quiescent point is determined by the transistor input and output characteristics and the applied currents and voltages. The quiescent point is defined by the BJT DC quantities VBE, IB, VCE, and IC . These points may be determined through the use of load-line analysis and design methods. The biasing configurations that are to be investigated are the fixed-bias and self-bias circuits shown in Figures below, respectively.

For the Q-point in the forward active region, VBE = 0.7V. In order design and analyze a biased circuit, we require the BJT F for finding the base current from the collector current (or viseversa). For the Fixed-Bias circuit shown in Figure above, the base-emitter KVL analysis yields

and the collector-emitter KVL analysis yields

Use the relationship and Q-points.

to solve for appropriate

and

values given

The Self-Bias circuit in Figure above requires conversion of the subcircuit connected to the base of the BJT to be converted to the Thevenin equivalent circuit for ease of design and analysis. Below shows the transformation of the self-bias circuit using Thevenin equivalents.

So the Base-Emitter KVL equation for the Thevenin Equivalent circuit is:

Note also that This equation may simplify design when analyzing the Base-Emitter KVL loop.

CHAPTER 3

METHODOLOGY

10

Figure above shows the connection of voltage-divider bias circuit for BJT. We construct the circuit above using 2N3904 transistor in a simulation such Multisim or Proteus. This simulation will determine the value of VRE, VR2, VTH, VB, and VE after we have calculated the value af all resistor manually. We will employ the design rule that =100 and = 0.1 .

1. For the given specification, the required value of RC for the voltagedivider configuration in the Figure was calculated. 2. Using = 0.1 = 1.5V; the value of RE is calculated as required. > 10 will result in = = + . The value of

3. Assuming

R1 and R2 were calculated manually as well. 4. Using any suitable simulation and theory, Table 1 was completed.

3.1

FLOWCHART

Pre Lab session.

Acknowle dge the formulae of voltage divider

Calculate the value of all resistor.

The calculated value of resistor was recorded.

Use multisim to simulate the experiment

The values of the result were recorded.

11

Construct circuit for voltage-divider bias of transistor 2N3904

Record the required value measured and fill in Table 3

Calculate the ratio as indication of the relative stability of the design.

Calculate and complete Table 4.

Come with a discussion, precaution and suggestion

Conclude the experiment

12

CHAPTER 4

4.1

Discussion and Suggestion:

____________________________________________________________________ ____________________________________________________________________ ____________________________________________________________________ ____________________________________________________________________ ____________________________________________________________________ ____________________________________________________________________ ____________________________________________________________________ ____________________________________________________________________ ____________________________________________________________________ ____________________________________________________________________ ____________________________________________________________________

4.2

Conclusion:

____________________________________________________________________ ____________________________________________________________________ ____________________________________________________________________ ____________________________________________________________________ ____________________________________________________________________ ____________________________________________________________________ ____________________________________________________________________

13

REFERENCES

http://en.wikipedia.org/wiki/Bipolar_transistor_biasing http://www.wisc-online.com/Objects/ViewObject.aspx?ID=SSE1302

14

Appendices

From multisim software

S-ar putea să vă placă și

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (399)

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (587)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2219)

- Electronic Technician Level 1 All 7 Books Learn Electronics Series by Some Wanke PDFDocument475 paginiElectronic Technician Level 1 All 7 Books Learn Electronics Series by Some Wanke PDFS C Charles100% (2)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (890)

- Transformer Daily Check ListDocument3 paginiTransformer Daily Check ListVatsavai Appala Narasimha Raju43% (7)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (73)

- Solera Opus v1.2.0 Error ListDocument3 paginiSolera Opus v1.2.0 Error ListMickey A CouvertierÎncă nu există evaluări

- C POWER ACB Manual PDFDocument172 paginiC POWER ACB Manual PDFVishab Fred80% (5)

- Practical Guide To Iec 60601Document28 paginiPractical Guide To Iec 60601CALIDAD METROMEDICA E.UÎncă nu există evaluări

- Eto Coc Written Examination Questions & Answers Part-1: by Minbox - February 11, 2020Document15 paginiEto Coc Written Examination Questions & Answers Part-1: by Minbox - February 11, 2020Gokul RajÎncă nu există evaluări

- Reciprocating Compressor CalculationDocument10 paginiReciprocating Compressor CalculationVIJAYIOCLÎncă nu există evaluări

- IEEE Device Numbers & Functions GuideDocument2 paginiIEEE Device Numbers & Functions GuideIman MukherjeeÎncă nu există evaluări

- SOLUCIONARIO SISTEMAS DE POTENCIA Analisis y Diseño Duncan GloverDocument432 paginiSOLUCIONARIO SISTEMAS DE POTENCIA Analisis y Diseño Duncan GloverLissette Salinas75% (12)

- Transmittal Letter Foreign WorkersDocument1 paginăTransmittal Letter Foreign WorkersNoor AfiqÎncă nu există evaluări

- Micro Hydro Power PlantDocument18 paginiMicro Hydro Power PlantNoor AfiqÎncă nu există evaluări

- Basic Logic Design and I/O Interface with DE2 BoardDocument11 paginiBasic Logic Design and I/O Interface with DE2 BoardNoor AfiqÎncă nu există evaluări

- Lab1 Lab1Document17 paginiLab1 Lab1Noor AfiqÎncă nu există evaluări

- Prosedur Kalibrasi Ellman RFDocument13 paginiProsedur Kalibrasi Ellman RFSBA KALIBRASIÎncă nu există evaluări

- 9124Document31 pagini9124srukeer100% (1)

- Network Speed Dome & PTZ Camera Installation Manual - V1.0.0Document29 paginiNetwork Speed Dome & PTZ Camera Installation Manual - V1.0.0paulwaveÎncă nu există evaluări

- Industrial Drive Suggestion 5th Sem.Document5 paginiIndustrial Drive Suggestion 5th Sem.ripeji2314Încă nu există evaluări

- What is an electrostatic shieldDocument3 paginiWhat is an electrostatic shieldsujaraghupsÎncă nu există evaluări

- 220kV Algarrobal Substation Design & EquipmentDocument10 pagini220kV Algarrobal Substation Design & Equipmentcesar pozoÎncă nu există evaluări

- Circuit Design - Time Borrowing and Time StealingDocument5 paginiCircuit Design - Time Borrowing and Time StealingarunsrlÎncă nu există evaluări

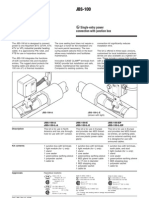

- Raychem R10 - JBS 100Document2 paginiRaychem R10 - JBS 100gregoiarÎncă nu există evaluări

- Robocolor ControllerDocument8 paginiRobocolor ControllerLeonardo SoutoÎncă nu există evaluări

- LAB-Models 2100 and 2100S Manual-ABDocument16 paginiLAB-Models 2100 and 2100S Manual-ABkevin diazÎncă nu există evaluări

- Antenna Engineering by HaytDocument4 paginiAntenna Engineering by HaytKhajavali ShaikÎncă nu există evaluări

- P14NZ MC en 9Document39 paginiP14NZ MC en 9danushka prasadÎncă nu există evaluări

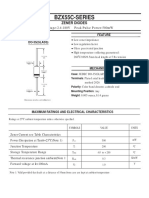

- T1 Datasheet DZ BZX55C-SeriesDocument3 paginiT1 Datasheet DZ BZX55C-SeriesAlex GrigorieÎncă nu există evaluări

- A User S Guide To Electrical Ppe Based On Nfpa 70 e Ray A. Jones and Jae G. Jones PDFDocument88 paginiA User S Guide To Electrical Ppe Based On Nfpa 70 e Ray A. Jones and Jae G. Jones PDFJairo FlechasÎncă nu există evaluări

- Chapter 3-3 Signal Processing Elemnt Part ThreeDocument43 paginiChapter 3-3 Signal Processing Elemnt Part Threedan gÎncă nu există evaluări

- Viewsonic VA2026W1Document79 paginiViewsonic VA2026W1Raul AlfaroÎncă nu există evaluări

- Solar-Powered Battery Charging With Highly Efficient Buck ConverterDocument20 paginiSolar-Powered Battery Charging With Highly Efficient Buck ConverterSusanÎncă nu există evaluări

- 11KV Single Breaker Panel OfferDocument2 pagini11KV Single Breaker Panel OfferSharafatÎncă nu există evaluări

- Sony dcr-hc23 hc24 hc26 hc35 Level2 Ver1.4Document72 paginiSony dcr-hc23 hc24 hc26 hc35 Level2 Ver1.4bero64Încă nu există evaluări

- TJ-450 Automatic Hot Stamping Machine ManualDocument23 paginiTJ-450 Automatic Hot Stamping Machine ManualFer AyalaÎncă nu există evaluări

- Common Network CablesDocument14 paginiCommon Network Cablesmarlon felizardoÎncă nu există evaluări

- Selected Problems SolutionsDocument11 paginiSelected Problems SolutionsKatherine ButlerÎncă nu există evaluări

- Sufi 1111Document39 paginiSufi 1111abdul basitÎncă nu există evaluări